Provided by the author(s) and University College Dublin Library in accordance with publisher policies. Please cite the published version when available.

| Title                        | A High-Precision Time Skew Estimation and Correction Technique for Time-Interleaved ADCs                                                                                                                                                                                                                                                                                                        |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors(s)                   | Salib, Armia; Flanagan, Mark F.; Cardiff, Barry                                                                                                                                                                                                                                                                                                                                                 |

| Publication date             | 2019-10                                                                                                                                                                                                                                                                                                                                                                                         |

| Publication information      | IEEE Transactions on Circuits and Systems I: Regular Papers, 66 (10): 3747-3760                                                                                                                                                                                                                                                                                                                 |

| Publisher                    | IEEE                                                                                                                                                                                                                                                                                                                                                                                            |

| Item record/more information | http://hdl.handle.net/10197/11137                                                                                                                                                                                                                                                                                                                                                               |

| Publisher's statement        | © 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. |

| Publisher's version (DOI)    | 10.1109/tcsi.2019.2915282                                                                                                                                                                                                                                                                                                                                                                       |

## Downloaded 2022-08-28T00:21:25Z

The UCD community has made this article openly available. Please share how this access benefits you. Your story matters! (@ucd\_oa)

# A High-Precision Time Skew Estimation and Correction Technique for Time-Interleaved ADCs

Armia Salib, Student Member, IEEE, Mark F. Flanagan, Senior Member, IEEE, and Barry Cardiff, Member, IEEE

Abstract—This paper presents an all-digital background calibration technique for the time skew mismatch in time-interleaved ADCs (TIADCs). The technique jointly estimates all of the time skew values by processing the outputs of a bank of correlators. A low-complexity sampling sequence intervention technique, suitable for successive approximation register (SAR) ADC architectures, is proposed to overcome the limitations associated with blind estimation. A two-stage digital correction mechanism based on the Taylor series is proposed to satisfy the target high precision correction. A quantitative study is performed regarding the requirements imposed on the digital correction circuit in order to satisfy the target performance and yield, and a corresponding filter design method is proposed which is tailored to meet these requirements. Mitchell's logarithmic multiplier is adopted for implementation of the principal multipliers in both the estimation and correction mechanisms, leading to a 25% area and power reduction in the estimation circuit. The proposed calibration is synthesized using a TSMC 28nm HPL process targeting a 2.4GHz sampling frequency for an 8 sub-ADC system. The calibration block occupies 0.03mm<sup>2</sup> and consumes 11mW. The algorithm maintains the SNDR above 65dB for a sinusoidal input within the target bandwidth.

*Index Terms*—Time skew, TIADC, background, digital calibration, blind estimation, sampling sequence intervention, coarse correction.

## I. INTRODUCTION

THE analogue to digital converter (ADC) is an essential component in any modern communication system, which is used to link the analogue world to the digital domain. The high demand for throughput in these systems adds more challenges to the ADC design in terms of its sampling rate and resolution. One of the design tools used to accommodate these challenges is to employ a time-interleaved ADC (TIADC) architecture. However, the performance of a TIADC system is usually limited by the mismatches which exist among the sub-ADCs. This creates the need to compensate the effect of these mismatches through calibration.

The main sources of the mismatches include offset, gain, time skew and bandwidth, which occur due to process, voltage and temperature variations [1]. In this work we focus on background digital calibration for time skew mismatch under the assumption that the input samples to this calibration process are free from other sources of mismatch.

Estimating the time skew via sensing the cross-correlation between the sub-ADCs output is introduced in [2] targeting a TIADC system with two sub-ADCs. Since then, many algorithms have been proposed to extend this idea to a larger number of sub-ADCs, e.g., [1], [3]–[8]. In [3], [4], [6], the number of sub-ADCs is required to be a power of 2, and the calibration process is done over a number of stages, where the selected reference ADC(s) are changed during those stages. In all stages except the final one, the crosscorrelation is measured between non-consecutive sub-ADCs, and the proportionality constant linking to the time skew can be either positive or negative depending on the input signal characteristics, i.e., the adaptation direction cannot be identified directly, which adds a burden on the estimation algorithm to determine it.

The time skew mismatch can be corrected in digital domain where finite impulse response (FIR) filters are usually used, as they can have a linear phase response. The filter coefficients can be time skew dependent, for example knowing the time skew values, the filter coefficients are obtained using Neville's algorithm in [9], or using the coefficients of an all pass filter with a fractional delay in [2], also, an adaptive filter system is used in [10] to obtain those coefficients. Since both the coefficients and the input are changing during run time for these approaches, the implementation of the filter multipliers is inefficient, which affects both area utilization and power consumption; also, obtaining these coefficients adds extra overhead to the circuit.

Differentiator FIR filters with constant coefficients are suggested in [5], [8], [11], [12] to guarantee the efficiency of the filter implementation, where these approaches are based on the Taylor series. However, using the Taylor series requires the filter input to be uniformly sampled, which is not satisfied in the existence of time skew; this degrades the system performance especially at large input frequencies, as will be described later in Subsection V-A.

The time skew calibration can be either [8] feed-forward (open-loop) with digital correction, e.g., [5], [7], [8], or feed-backward (closed-loop), e.g., [1], [2], [4], [9], [10], [13]–[16]. In the former, the estimation mechanism uses uncalibrated samples, which allows to avoid the possibility of system instability in the feed-backward approaches; however, it requires high-precision calculations including divisions and multiplications. Also, the estimated values are inaccurate in the existence of large time skew values due to ignoring the

This publication has emanated from research supported in part by S3group, Dublin, Ireland, and in part by a research grant from Science Foundation Ireland (SFI), and is co-funded under the European Regional Development Fund under Grant Number 13/RC/2077.

The authors are with the School of Electrical and Electronic Engineering, University College Dublin, Dublin, Ireland (e-mail: armia.salibfarag@ucdconnect.ie; mark.flanagan@ieee.org; barry.cardiff@ucd.ie).

second and higher order effects of the time skew mismatch. The feed-forward algorithms can offer fast estimation for simple sinusoidal input signals; however, their convergence speed can be comparable with other feed-backward calibration algorithms when a practical band-limited random input is used, where the randomness of the input decreases the precision of the estimates as we illustrate in Section VIII.

In feed-backward calibration, the time skew estimation mechanism is fed by the calibrated samples, and the estimates are updated via measuring the uncompensated time skews residues. Unlike feed-forward calibration, feed-backward calibration is not sensitive to the second and higher order effects of the time skew, since the residues diminish on convergence; this allows introducing further approximation to the estimation mechanism without affecting the overall performance. An example for an approximation in feed-backward calibration is to replace each multiplier in the cross-correlation based estimation by a mean-absolute difference [4].

In this paper, we propose an high precision blind calibration algorithm for time skew mismatch in TIADCs consisting of all digital estimation and correction blocks arranged in a closed-loop architecture. The estimation block performs joint estimation of all of the time skew values using the measured cross-correlations between the outputs of adjacent sub-ADCs. In contrast to other methods, our scheme explicitly estimates the slope of the autocorrelation function, facilitating fast convergence and making the feed-backward mechanism less susceptible to stability issues. Additionally, we outline some of the problems associated with blind estimation in general and propose a novel sampling sequence intervention method, suitable for SAR ADCs, that mitigates many of these problems. The proposed correction block is a two stage Taylor series approach composed of a low-complexity coarse correction followed by a fine correction stage. We develop a statistical approach to analyze the various error terms in the correction mechanism, and these are then used to constrain the parameters of the design in order to achieve the desired bandwidth and manufacturing yield whilst ensuring that any resulting distortions are below the quantization noise level. Incorporated into this methodology is a fixed point filter design approach that ensures the constraints are met. Simplified hardware implementations for the principal multipliers in both the estimation and correction sides are also presented.

This paper is organized as follows. Section II provides an overview of the proposed calibration algorithm. Section III describes in detail the blind time skew estimation mechanism. A sampling intervention mechanism is proposed in Section IV to relax the limitations associated with blind estimation. Section V highlights the proposed digital correction technique, and Section VI quantifies the constraints on the filters used in the digital correction to satisfy the target yield and performance. In Section VII, simplified hardware implementations for the main multipliers used in both the correction and estimation parts are proposed. Simulation results are presented in Section VIII, accompanied by area utilization and power consumption results for the hardware implementation. Finally, conclusions

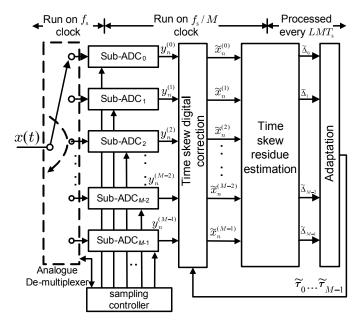

Fig. 1: Block diagram of the proposed time skew calibration.

are drawn in Section IX.

#### II. TIME SKEW CALIBRATION

Figure 1 shows a block diagram for the proposed time skew calibration algorithm for a TIADC system that has an aggregated sampling rate  $f_s$ , and consists of M slower sub-ADCs each with sampling rate  $f_s/M$ .

Let x(t) be the analogue input to the TIADC system, which is sampled every  $T_s \triangleq 1/f_s$  [sec], and  $y_n^{(m)}$  denote the  $n^{\text{th}}$ output of the  $m^{\text{th}}$  sub-ADC (m = 0, 1, ..., M - 1). Assuming that the system suffers only from time skew, we have

$$y[nM+m] \triangleq y_n^{(m)} \triangleq x\big((nM+m+\tau_m)T_{\rm s}\big),\qquad(1)$$

where  $\tau_m$  is the time skew associated with the  $m^{\text{th}}$  sub-ADC normalized to  $T_{\text{s}}$ , and y[.] is the aggregated discrete-time ADC output. Each time skew  $\tau_m$  can be modeled using a Gaussian distribution with mean zero and standard deviation  $\sigma_{\tau}$  based on the manufacturing process.

The ADC output  $y_n^{(m)}$  is processed by the 'Time skew digital correction' block depicted in Figure 1 to compensate the estimated time skew mismatch, which is denoted by  $\tilde{\tau}_m$  for the  $m^{\text{th}}$  sub-ADC. Assuming an ideal application of the estimates  $\tilde{\tau}_m$ , the correction block output can be written as

$$\tilde{x}[nM+m] \triangleq \tilde{x}_n^{(m)} \triangleq x\big((nM+m+\Delta_m)T_{\rm s}\big), \quad (2)$$

where

$$\Delta_m \triangleq \tau_m - r - \tilde{\tau}_m \tag{3}$$

is the time skew *residue* for the  $m^{\text{th}}$  sub-ADC, and r is a timing reference. The timing reference r is imposed by the calibration mechanism. Its value can be selected arbitrarily; however, as described in Subsection III-C, a constraint is placed on its selection in order to relax the requirements on the correction mechanism.

The corrected samples  $\tilde{x}_n^{(m)}$  are processed by the 'Time skew residue estimation' block to produce  $\tilde{\Delta}_m$ , an estimate of  $\Delta_m$ . Using  $\tilde{\Delta}_m$ , we update the estimated time skew via

$$\tilde{\tau}_m \leftrightarrow \tilde{\tau}_m + \mu \tilde{\Delta}_m, \quad 0 \le m < M,$$

(4)

where all  $\tilde{\tau}_m$  are initialized to zero at the start of the calibration, and  $\mu$  is the least-mean-squares (LMS) adaptation step size which is chosen to be less than 1 to avoid system instability.

The estimated time skew values  $\tilde{\tau}_m$  are fed back to the 'Time skew digital correction' block forming a closed-loop. Upon convergence, all  $\Delta_m$  become small, and the  $\tilde{\tau}_m$  become close to the values  $\dot{\tau}_m$ , which, using (3), are given by

$$\dot{\tau}_m \stackrel{\Delta}{=} \tilde{\tau}_m \big|_{\Delta_m = 0} = \tau_m - r. \tag{5}$$

While the exposition throughout this paper is general, we consider a particular TIADC system for illustration purposes in our discussions. This TIADC system consists of M = 8 SAR sub-ADCs with N = 12-bit resolution. The target ADC bandwidth is  $\beta = 88\%$  of the Nyquist frequency. The system suffers from time skew mismatch having a Gaussian distribution with standard deviation  $\sigma_{\tau} = 0.01$ . The target yield is  $\eta = 98\%$ , i.e., all performance constraints are required to be satisfied for at least  $\eta$  of the fabricated ADCs.

### **III. TIME SKEW ESTIMATION**

For ease of notation, we define  $\tilde{x}_n^{(M)} \triangleq \tilde{x}_{n+1}^{(0)}$  and  $\Delta_M \triangleq \Delta_0$ . We define the autocorrelation function of x(t) as  $R_{xx}(\tau) = \mathbb{E}(x(t)x(t-\tau))$ , where  $\mathbb{E}(X)$  is the expectation of X. We compute M estimates of  $R_{xx}(\tau)$  in the vicinity of  $\tau = T_s$ , each denoted by  $c_m$ , as follows

$$c_{m} \triangleq \frac{1}{L} \sum_{n=0}^{L-1} \tilde{x}_{n}^{(m+1)} \tilde{x}_{n}^{(m)}, \quad \forall 0 \le m \le M-1,$$

$$= \frac{1}{L} \sum_{n=0}^{L-1} x \left( (nM+m+1+\Delta_{m+1})T_{s} \right) x \left( (nM+m+\Delta_{m})T_{s} \right),$$

(7)

where L is selected to be a large integer, and we have used (2) to formulate (7). Comparing (7) to the definition of  $R_{xx}(\tau)$ , we can approximate  $c_m$  to

$$c_m \approx R_{\rm xx} \left( \left( 1 + \Delta_{m+1} - \Delta_m \right) T_{\rm s} \right), \quad 0 \le m < M.$$

(8)

This approximation is due to the discrete and finite nature of the summation. It is assumed for this work that the input signal, x(t), is such that the approximation holds. This is the case for overwhelmingly many input signals; however, as outlined in Section IV, there are some exceptions.

Using the Taylor series expansion for the right-hand side of (8) around  $T_s$ , a first-order approximation for  $c_m$  is given by

$$c_m \approx R_{\rm xx}(T_{\rm s}) + T_{\rm s} \frac{dR_{\rm xx}(T_{\rm s})}{d\tau} (\Delta_{m+1} - \Delta_m), \qquad (9)$$

where  $\frac{dR_{sx}(T_s)}{d\tau}$  is the derivative of the autocorrelation function evaluated at  $\tau = T_s$ . Using (9), the differences between adjacent  $c_m$  are given by

$$e_m \triangleq c_m - c_{m-1} \tag{10}$$

$$\approx -T_s \frac{dR_{xx}(T_s)}{d\tau} (-\Delta_{m-1} + 2\Delta_m - \Delta_{m+1}) \qquad (11)$$

where  $c_{-1} \triangleq c_{M-1}$  and  $\Delta_{-1} \triangleq \Delta_{M-1}$ .

Here, we can notice that  $e_m$  does not depend only on  $\Delta_m$ , but also on  $\Delta_{m-1}$  and  $\Delta_{m+1}$ ; therefore, we should not attempt to use  $e_m$  to adapt  $\Delta_m$  directly. A similar observation was made independently in [8], [16] and [1].

Writing (11) in matrix form, we obtain

$$\mathbf{e} \approx -T_{\mathrm{s}} \frac{dR_{\mathrm{xx}}(T_{\mathrm{s}})}{d\tau} \mathbf{U} \mathbf{\Delta},$$

(12)

where  $\mathbf{e} \triangleq \{e_m\}$  and  $\mathbf{\Delta} \triangleq \{\Delta_m\}$  are  $M \times 1$  vectors, and U is an  $M \times M$  circulant matrix given by

$$\mathbf{U} = \begin{bmatrix} 2 & -1 & 0 & \dots & 0 & 0 & -1 \\ -1 & 2 & -1 & \dots & 0 & 0 & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \dots & -1 & 2 & -1 \\ -1 & 0 & 0 & \dots & 0 & -1 & 2 \end{bmatrix}_{M \times M}$$

(13)

Given the observation vector  $\mathbf{e}$ , we seek  $\Delta$  satisfying (12), we elaborate on the process used to achieve this target in the following subsections.

## A. Estimation of the derivative of the autocorrelation function

Many calibration algorithms (e.g., those proposed in [4], [15]) ignore the estimation of the term  $\frac{dR_{xx}(T_s)}{d\tau}$ , assuming only that this term is always negative, which is correct for a band-limited input; hence, this term does not affect the adaptation *direction* of the estimation process. However, it makes the convergence speed dependent on the input signal. Also, its estimation is required to guarantee the stability of the calibration mechanism [8] given that  $\mu$  in (4) is less than 1. This term can be written as [1]

$$T_{\rm s}\frac{dR_{\rm xx}(T_{\rm s})}{d\tau} = -T_{\rm s} \operatorname{E}\left(x(t)x'\left((t-T_{\rm s})\right)\right),\tag{14}$$

where x'(.) is the first order time derivative of the input. For the applications that do not use digital correction, an approximated value for  $x'(t - T_s)$  can be simply calculated using a subtractor as in [1]. However, the signal derivative is calculated with high precision for time skew correction as illustrated in Section V, which enables us to estimate  $T_s \frac{dR_{xx}(T_s)}{d\tau}$  via

$$T_{\rm s} \frac{dR_{\rm xx}(T_{\rm s})}{d\tau} \approx -\left[\frac{1}{L} \sum_{n=0}^{L-1} \tilde{x}[nM+1] y'[nM]\right]_2, \qquad (15)$$

where y'[.] is the output of the first order differentiator filter in the correction mechanism (depicted in Figure 5). Here,  $\lceil X \rceil_2$ denotes the smallest power of two greater than or equal to X; this approximation replaces the division needed to evaluate  $\Delta$ by a simple bit-shift operation. Note that this simplification is feasible since a feed-backward calibration is used.

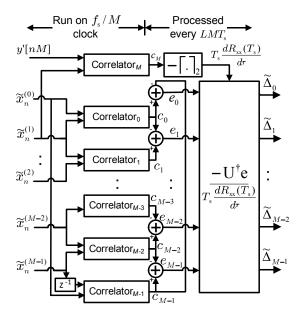

Fig. 2: Block diagram of the proposed time skew estimation.

### B. Overall solution

Using (12), we obtain a solution for  $\Delta$ , an estimate of  $\Delta$ , according to

$$\tilde{\mathbf{\Delta}} \approx -\left(T_{\rm s} \frac{dR_{\rm xx}(T_{\rm s})}{d\tau}\right)^{-1} \mathbf{U}^{\dagger} \mathbf{e},\tag{16}$$

where  $\mathbf{U}^{\dagger}$  is the precomputed pseudo inverse of  $\mathbf{U}$  that can be obtained using the computations in Appendix A. This estimate is then used to adapt each  $\tilde{\tau}_m$  using (4).

Figure 2 shows a block diagram of the proposed time skew estimation. It consists of M + 1 correlators; the first M of these are used to compute e using (6) and (10), and the  $M^{\text{th}}$  correlator is used in estimating  $T_s \frac{dR_{\text{sx}}(T_s)}{d\tau}$  according to (15). All e are processed jointly to estimate the time skew residues  $\tilde{\Delta}$  via (16).

## C. Timing reference

In Appendix A, we showed that the computed  $\Delta$  via (16) has a zero mean, i.e.,

$$\sum_{n=0}^{M-1} \tilde{\Delta}_m = 0. \tag{17}$$

This fact, when considered in the context of the update equation (4), allows us to further conclude that the sum of the  $\tilde{\tau}_m$  remains constant throughout the adaptation process. In particular, since all  $\tilde{\tau}_m$  are initialized to zero, it always holds during the adaptation process that

$$\sum_{m=0}^{M-1} \tilde{\tau}_m = 0.$$

(18)

Summing (3) for all  $m \in \{0, ..., M-1\}$  while replacing  $\Delta_m$  with its estimate  $\tilde{\Delta}_m$  and using (17) and (18), we find that the pseudo inverse procedure indirectly implies the constraint

$$r = \frac{1}{M} \sum_{i=0}^{M-1} \tau_i = \bar{\tau}.$$

(19)

Thus by (5), we have

$$\dot{\tau}_m|_{r=\bar{\tau}} = \frac{M-1}{M} \tau_m - \frac{1}{M} \sum_{\substack{i=0\\i \neq m}}^{M-1} \tau_i,$$

(20)

which has mean zero, and its variance can be expressed as

$$\sigma_{\tau}^2 \big|_{r=\bar{\tau}} = \left(1 - \frac{1}{M}\right) \sigma_{\tau}^2.$$

<sup>(21)</sup>

Many estimation algorithms, e.g., [2]–[4], [11], [14], [15], [17]–[20], choose the first sub-ADC as a timing reference, i.e.,  $r = \tau_0$ , which, recalling (5), results in the following variance

$$\sigma_{\tau}^2 \big|_{r=\tau_0} = 2\sigma_{\tau}^2. \tag{22}$$

Compared to this work, these approaches require a larger dynamic range for the time skew correction circuits, and impact adversely the digital correction accuracy due to the reduction in the reliability of the used approximations for large time skew values.

#### **IV. SAMPLING SEQUENCE INTERVENTION**

In blind estimation techniques, it is generally assumed that the input signal is wide sense stationary, and the statistical characteristics for each sub-ADC output are the same in the absence of mismatches. This assumption is used in many algorithms available in the literature, e.g., [2]–[5], [8], [14]– [16], which is valid for a wide range of input signals; however, it is inaccurate for a number of 'pathological' input types, here, we list two [1]:

- An input signal containing multiple frequency components, some of which appear in the frequency locations of the spurs of any of the input components. In this case, the blind estimator cannot differentiate between the input signal and the spurs generated by the time skew, and the statistical characteristics for each sub-ADC output are different even in the absence of any mismatches. Note that this situation can occur for any arbitrary frequency.

- A special case for the previously discussed pathological input type can occur when the input signal contains one or more components at any of the frequencies k fs/2M for k ∈ {0,..., M-1}, where the spurs of those components coincide with themselves. In [2] and [14], a notch filter before the estimation mechanism is used to remove these components and avoid this problem. However, this solution is not suitable for the generalized pathological input type previously discussed.

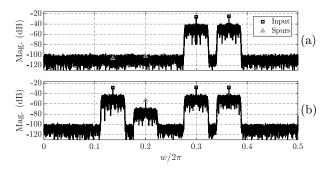

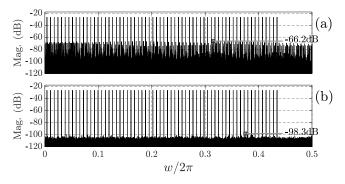

Blind estimation techniques can be misled when the input signal contains components that resemble these pathological signal types, which causes performance degradation. To demonstrate this limitation, we used an M = 2 TIADC system with an input signal consisting of two amplitude modulated (AM) channels whose carrier frequencies are located at  $\frac{373}{512}\pi$  and  $\frac{307}{512}\pi$ . Figure 3a depicts the output power spectral density (PSD) after using the proposed calibration method, where we can notice that the unwanted spurs are brought down to the noise floor. However, after adding another AM channel

Fig. 3: Illustration of the effect of the problematic components on blind estimation: (a) without and (b) with problematic components.

with carrier frequency  $\frac{139}{512}\pi$  (which is at the spur location of  $\frac{373}{512}\pi$ ), the time skew calibration causes significant performance degradation as can be seen in Figure 3b. Note that, due to the incorrect estimation, there is an in-band interference in the AM channels in addition to the visible high spurs in Figure 3b. This problem decreases the robustness of the blind estimation techniques, thus making them unsuitable for applications requiring general-purpose ADCs.

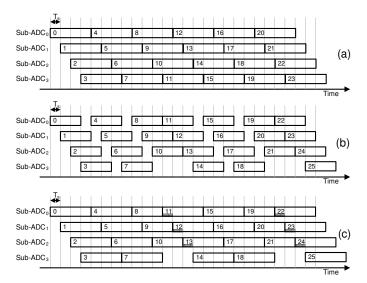

Figure 4a shows the timing diagram for the conventional sampling sequence with M = 4. In the presence of problematic components, the statistical characteristics for each sub-ADC's output can be different, which misleads the blind estimation. This limitation can be relaxed by letting each sub-ADC experiences input samples that would be sampled by other sub-ADCs if the conventional sampling sequence was used. To achieve this with only a minor penalty in area and power, we introduce a minor intervention to the TIADC's sampling sequence, whereby the 'analogue de-multiplexer' and the 'sampling controller' blocks shown in Figure 1 both skip a sub-ADC every L aggregated samples [1]. This change is particularly suitable for TIADC systems with a ring divider clocking architecture, e.g., [13], [21], where altering the ring divider circuit enables changing the sampling sequence without affecting the time skew mismatch.

Figure 4b shows the corresponding timing diagram using the proposed sampling sequence intervention with L = 11, where a complete conversion cycle is required to be finished within  $(M - 1)T_s$ , thus tightening the constraints on the analogue circuit. It can be noticed that the samples with indices greater than L - 1 and up to ML - 1 are sampled by different sub-ADCs when the sampling sequences depicted in Figures 4a and 4b are compared. Note that the total number of samples needed to estimate all  $c_m$  using (6) is ML, and it contains exactly M intervention events.

However, in this work we target a SAR sub-ADC architecture, where the time of a complete conversion cycle is divided into smaller periods to resolve each decision bit. That allows forcing an *early termination* for the conversion cycle without losing the previously acquired decision bits. Through exploiting this early termination, we can design the sub-ADCs to perform a complete conversion within  $MT_s$ , and the conversion time is shortened by  $T_s$  when a sampling sequence intervention occurs. This period corresponds to 1/M

Fig. 4: Timing diagrams for the sampling sequence for a TIADC system having M = 4 sub-ADCs with: (a) conventional sampling sequence, (b) sampling sequence intervention with a  $(M - 1)T_s$  conversion cycle, and (c) sampling sequence intervention with a  $MT_s$  conversion cycle, modified from [1].

of the complete conversion time, i.e., approximately  $\lceil N/M \rceil$  bits are lost in each early terminated sample. Figure 4c shows the proposed timing diagram when early termination is used. Each skipping event leads to forcing an early termination for M - 1 samples, which are partially shaded in Figure 4c.

Note that for a large M, only a small fraction of the ADC output word is missed when early termination is forced. In practice, L is selected to be a large integer, e.g.,  $L = 2^{13}$  is used in the results presented in Section VIII. This makes the overall performance degradation due to the early termination events negligible.

#### V. DIGITAL CORRECTION

For the purpose of the development and analysis of the digital correction algorithm, we assume that the time skew estimation has correctly converged, i.e.,  $\tilde{\tau}_m = \dot{\tau}_m = \tau_m - r$ . In this case, we can reconstruct a time skew corrected version of  $\tilde{x}$  from the ADC output y using a Q-term Taylor series approximation [11], [12]

$$\tilde{x}[n] \approx y[n] - \sum_{q=1}^{Q} \frac{(h_{d,q} * y)[n]}{q!} (\dot{\tau}[n])^{q},$$

(23)

where \* is the convolution operator,  $\dot{\tau}[n] \triangleq \dot{\tau}_{(n \mod M)}^{1}$ , and  $h_{d,q}$  is the impulse response of a non-causal<sup>2</sup> (zero delay)  $q^{\text{th}}$  order differentiator filter whose ideal frequency response is

$$\bar{H}_{\mathrm{d},q}(w) = (jw)^q,\tag{24}$$

where  $w \in [0, \pi]$  is the normalized angular frequency.

<sup>1</sup>This relationship does not consider the effect of the sampling sequence intervention proposed in Section IV.

<sup>&</sup>lt;sup>2</sup>Without loss of generality, we ignore the effect of the filter group delay on the frequency response in this analysis, unless stated otherwise. Implementations must use causal filters in conjunction with appropriate matching delays, resulting in an overall group delay.

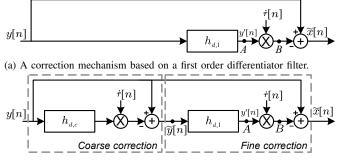

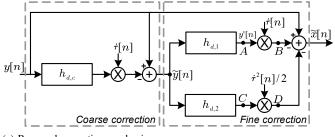

(b) A correction mechanism based on a first order differentiator filter and a coarse correction stage.

(c) Proposed correction mechanism.

Fig. 5: Block diagram for the digital correction.

The approximation in (23) is due to the following reasons:

- in the presence of time skew mismatch, the input is not uniformly sampled;

- 2) the truncation of the Taylor series to finitely Q terms;

- 3) truncation of the  $q^{\text{th}}$  order differentiator filter to  $L_q$  coefficients, which leads to deviations from (24). For example, the authors of [11] used (for odd  $L_1$ )

$$h_{d,1}[k] = \begin{cases} 0, & k = 0\\ \frac{(-1)^k}{k}, & \text{otherwise,} \end{cases} \quad |k| \le \frac{L_1 - 1}{2}. \quad (25)$$

In the following subsections, we propose a two-stage digital correction architecture to reduce the effect of the non-uniform sampling, and we investigate the impact of the choice of Q.

#### A. Two-stage correction

Figure 5a depicts<sup>3</sup> the conventional digital correction mechanism. In Appendix B, we show that some distortion is introduced to the output of this mechanism due to the nonuniformly sampled input. To reduce this distortion, we propose a two-stage digital correction process, where first a *coarse* Taylor series based correction is applied to reduce the time skews seen by a second, more accurate, *fine* correction stage as shown in Figure 5b.

The coarse correction stage consists of a simplified firstorder differentiator filter,  $h_{d,c}$ , implemented as an antisymmetric FIR structure guaranteeing a *purely imaginary* frequency response,  $H_{d,c}(w)$ , i.e., it has an ideal phase response, and it only deviates from the ideal in its magnitude response.

In Appendix B, we showed that the inclusion of the coarse correction block leads to scaling the distortion by a factor of  $|\nu_{d,c}(w)|/w$  where  $\nu_{d,c}(w) \triangleq (jw - H_{d,c}(w))/j$  is the error in the magnitude response of the filter  $h_{d,c}$ . The distortion is scaled down when  $|\nu_{d,c}(w)| < w$  which is generally satisfied for almost all w as discussed in Section VIII. In this work, we use a 9 tap (each tap represented with 4 bits) coarse differentiator filter.

## B. Higher order correction terms

In the previous subsection, we only considered first order correction schemes, essentially we let Q = 1 in (23). However, it can be the case that the higher order error terms can also have a significant impact on the system performance. Motivated by this, we now perform a statistical analysis of the higher order error terms with a view to assessing their impact in meeting the target ADC performance metrics.

For a selected Q in (23), the error in the approximation is dominated by the  $(Q + 1)^{\text{th}}$  term in the Taylor series. For a full-scale sinusoidal input with frequency w, the error in the  $m^{\text{th}}$  sub-ADC calibrated output is also sinusoidal and its amplitude can be expressed as

$$\varepsilon_Q = 2^{N-1} \frac{(w\dot{\tau}_m)^{Q+1}}{(Q+1)!}.$$

(26)

We need to choose Q such that the power of the induced error is below the quantization noise power level for at least  $\eta$  of the sub-ADCs, i.e.,  $P(\varepsilon_Q^2/2 < 1/12) \ge \eta$  where P(X) is the probability of an event X. Using the maximum supported input frequency,  $w = \beta \pi$ , this may be expressed as

$$\mathbf{P}\left(\frac{\varepsilon_Q^2}{2} < \frac{1}{12}\right) = \mathbf{P}\left(|\dot{\tau}_m| < \Lambda\right) = \operatorname{erf}\left(\frac{\Lambda}{\sigma_\tau \sqrt{2(1 - \frac{1}{M})}}\right) \ge \eta, \quad (27)$$

where

$$\Lambda = \frac{1}{\beta \pi} \left( \sqrt{\frac{2}{3}} \frac{(Q+1)!}{2^N} \right)^{\frac{1}{Q+1}},$$

(28)

erf(.) is the error function, and we have used the assumption that  $\dot{\tau}_m$  is normally distributed with variance given in (21).

Using Q = 1,  $P(\varepsilon_1^2/2 < 1/12) = 0.56$ , i.e., only 56% of the sub-ADCs will satisfy the suggested design constraint, which of course lies below the target yield  $\eta$ . Similarly, setting Q = 2, we find that the target performance can be satisfied in 99.996% of the parts.

Based on this calculations, the need for a second order correction scheme is clear, and forms the basis of our proposed calibration scheme in Figure 5c. This scheme is based on the first order correction of Figure 5b with the addition of a second order differentiator,  $h_{d,2}$ , whose output is used to cancel the second order error term.

To reduce the system latency, we suggest to design  $h_{d,2}$  as a single filter instead of using two cascaded first order differentiators as done in [12]. Note that the design requirements on  $h_{d,2}$  are less stringent than on  $h_{d,1}$ , because its output is scaled by  $\dot{\tau}_m^2/2$  compared to  $\dot{\tau}_m$  on the first order correction branch. Furthermore,  $h_{d,2}$  does not have any phase discontinuities simplifying its design compared to  $h_{d,1}$ . In the next section, we will discuss the design methodology of these filters.

<sup>&</sup>lt;sup>3</sup>The figure does not show the matching delays needed to align the inputs of the addition and multiplication blocks to match the filters' group delay.

#### VI. FINE DIFFERENTIATOR FILTER DESIGN

In this section, we provide design methods for the two fine differentiator filters  $h_{d,1}$  and  $h_{d,2}$  such that the required yield  $\eta$  and the target performance can be achieved.

We define  $\nu_{d,q}(w) \triangleq |\bar{H}_{d,q}(jw) - H_{d,q}(jw)|$  to be the error in the magnitude response of the  $q^{\text{th}}$  order differentiator filter where  $H_{d,q}$  is the frequency response of  $h_{d,q}$ , and  $\bar{H}_{d,q}(jw)$ is the ideal frequency response defined in (24). We note that the actual FIR implementation for these filters can have ideal phase response, and only suffers from magnitude error. That is because of using symmetric and anti-symmetric filter coefficients for even and odd q respectively.

We define  $\xi_{d,q}(w)$  as the upper bound for  $\nu_{d,q}(w)$  which guarantees that the power of the total distortion induced in the correction mechanism is less than the quantization noise power for at least a fraction  $\eta$  of the ADC instances, where a sinusoidal signal with frequency  $|w| \leq \beta \pi$  is used as an input.

In the following subsections, we evaluate  $\xi_{d,q}(w)$ , which will then be used in Subsection VI-C and Appendix C to complete the design of  $h_{d,1}$  and  $h_{d,2}$ . Finally, in Subsection VI-D, we demonstrate the complexity of the correction mechanism for different system specifications.

## A. Limiting $\nu_{d,1}(w)$

Using a full-scale sinusoidal input having frequency  $|w| \leq \beta \pi$ , the distortion at Node A in Figure 5c due to the magnitude response mismatch of  $h_{d,1}$  is a sinusoid with amplitude  $2^{N-1}\nu_{d,1}(w)$ . Accordingly at Node B, the distortion induced in the corrected output of the  $m^{\text{th}}$  sub-ADC using (23) has amplitude  $2^{N-1}\nu_{d,1}(w) \dot{\tau}_m$ . To satisfy the target performance and yield  $\eta$ , we need to limit the average power of this distortion over the M sub-ADCs to be less than the quantization noise power for at least  $\eta$  of the ADCs, i.e.,

$$\mathbf{P}\left(\frac{\left(2^{N-1}\nu_{d,1}(w)\right)^{2}}{2M}\sum_{m=0}^{M-1}\dot{\tau}_{m}^{2}\leq\frac{1}{12}\right)\geq\eta,\qquad(29)$$

where  $\sum_{m=0}^{M-1} \dot{\tau}_m^2 / \sigma_{\dot{\tau}}^2$  is a random variable that has a chisquared distribution with M degrees of freedom. Using the inverse of the cumulative distribution function of a chi-squared random variable, we can write (29) as

$$\frac{\mathcal{Z}_{M/2}^{-1}(\eta) \left(2^{N-1}\nu_{\mathsf{d},1}(w)\right)^2 \sigma_{\tau}^2}{M} \le \frac{1}{12},\tag{30}$$

where  $\mathcal{Z}_{M/2}^{-1}(.)$  is the inverse of the regularized lower incomplete gamma function with shape parameter M/2.

Rearranging (30) and using (21), we obtain the following design criterion for the differentiator filter

$$\nu_{d,1}(w) \le \frac{1}{2^N \sigma_\tau} \sqrt{\frac{M}{3(1 - \frac{1}{M}) \mathcal{Z}_{M/2}^{-1}(\eta)}} = \xi_{d,1}(w), \ \forall |w| \le \beta \pi,$$

(31)

i.e., to satisfy the target yield and performance constraints, we need  $\nu_{d,1}(w) \leq \xi_{d,1}(w)$ . Note that the upper bound  $\xi_{d,1}(w)$  is independent of w.

The example specification in Section II requires  $\nu_{d,1}(w) \leq 0.0141$ . We further note that had we used a reference timing  $r = \tau_0$ , we would have to replace the  $1 - \frac{1}{M}$  factor in (31) with 2, as per (22), tightening the constraint to  $\nu_{d,1} \leq 0.0094$ .

## B. Limiting $\nu_{d,2}(w)$

A similar approach can be used to constrain  $\nu_{d,2}(w)$  to limit the total distortion power induced by  $h_{d,1}$  and  $h_{d,2}$  magnitude errors to be lower than the quantization noise power. We let the distortion power budget allocated for the filter  $h_{d,2}$  be  $\left(\xi_{d,1}^2(w) - \nu_{d,1}^2(w)\right) / \left(12\xi_{d,1}^2(w)\right)$ . Then, we can express the required constraint as

$$\mathbf{P}\left(\frac{\left(2^{N-1}\nu_{\mathbf{d},2}(w)\right)^{2}}{8M}\sum_{m=0}^{M-1}\dot{\tau}_{m}^{4} \leq \frac{\xi_{\mathbf{d},1}^{2}(w) - \nu_{\mathbf{d},1}^{2}(w)}{12\xi_{\mathbf{d},1}^{2}(w)}\right) \geq \eta,\tag{32}$$

which can be reformulated as

$$\nu_{d,2}(w) \le \frac{\sqrt{8M\left(\xi_{d,1}^2(w) - \nu_{d,1}^2(w)\right)}}{2^N \sigma_\tau^2 (1 - \frac{1}{M})\xi_{d,1}(w)\sqrt{3\kappa}} = \xi_{d,2}(w), \; \forall |w| \le \beta\pi,$$

(33)

where  $\kappa$  is chosen such that  $P(\sum_{m=0}^{M-1} \dot{\tau}_m^4 / \sigma_{\dot{\tau}}^4 < \kappa) = \eta$ .

## C. Filter design

Trimming the number of taps in  $h_{d,1}$  produces a large error (i.e., ripples) in its magnitude response, violating the constraint in (31). To reduce these ripples, [8] suggests to multiply the coefficients obtained from (25) by a Hanning window. Also, [7] proposes to use a Blackman window for the same purpose.

The Parks-McClellan differentiator design algorithm [22] was used to design the differentiator filters in [12] and [23]. This method minimizes the relative error in the frequency response of the filter, i.e,  $\nu_{d,1}/|\bar{H}_{d,1}|$ . However, the Parks-McClellan method is suboptimal for the design problem at hand, since in this application we focus on minimizing  $\nu_{d,1}$ . Also, the filter response will suffer from further distortion after the obtained coefficients are quantized to a limited number of bits for the hardware realization.

This creates a need for a design method that is tailored to satisfy this application's needs while directly providing a quantized version of the coefficients and satisfying the system level design constraints. This design method is described in Appendix C.

## D. Correction complexity versus system specifications

In the previous subsections, we defined the constraints on the proposed correction mechanism for an N-bit TIADC consisting of M sub-ADCs, each suffering from time skew mismatch having a Gaussian distribution with standard deviation  $\sigma_{\tau}$ . Those constraints are derived such that for at least a fraction  $\eta$  of the ADC instances, the induced distortion in the corrected output is below the quantization noise for a sinusoidal input within a bandwidth  $\beta$ .

The system specifications, i.e., N, M,  $\eta$ ,  $\beta$  and  $\sigma_{\tau}$ , affect the order of correction, Q, the number of filter taps,  $L_q$ , and the coefficient bit-width,  $W_q$ , for each filter. The correction

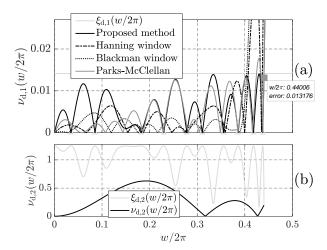

Fig. 6: Magnitude response error for (a) filter  $h_{d,1}$  with  $L_1 = 25$  and  $W_1 = 10$ , designed using different methods, and (b) filter  $h_{d,2}$  with  $L_2 = 5$  and  $W_2 = 4$ .

order Q is chosen such that (27) is satisfied. The first and second derivative filters are designed to satisfy the constraints in (31) and (33) respectively. These filters are designed using the method described in Appendix C.

For our example specification in Section II, we obtain a filter  $h_{d,1}$  with  $L_1 = 25$  and  $W_1 = 10$  (including the sign bit). Figure 6a depicts  $\nu_{d,1}(w)$  for a filter  $h_{d,1}$  with  $L_1 = 25$  10-bit taps designed by various methods, we note that the filter obtained using the proposed design method satisfies the design requirement in (31), which is marked as a light gray horizontal line. This is in contrast with the responses obtained using window functions and the Parks-McClellan algorithm, which would not satisfy the design constraint.

Similarly,  $h_{d,2}$  was designed using the proposed design method with  $L_2 = 5$  and  $W_2 = 4$ . Figure 6b depicts  $\nu_{d,2}$  for this filter.

Note that the constraints in (31) and (33) are tightened with increasing  $\eta$ , complicating the filters' design. Similarly, increasing the bandwidth,  $\beta$ , over which the constraint in (31) is to be applied causes an increase in the filter's complexity due to the discontinuity in its response at  $w = \pi$ , making a 100% bandwidth operation not possible for any reasonable constraint. These phenomena can be observed through the different specification examples in Table I where it is clear that the complexity increases with both  $\eta$  and  $\beta$ .

On the other hand, we note that both constraints in (31) and (33) are relaxed as M increases, thus reducing the complexity (for a fixed  $T_s$ ). This can also be seen in Table I.

#### VII. LOW-COMPLEXITY MULTIPLIERS

Each correlator depicted in Figure 2 contains a multiplier, which is known to be both power and area hungry. The output of each of these multipliers is averaged over a large number of samples and is used in a feedback calibration loop, which allows simplifying the multiplier's hardware implementation at the expense of its accuracy [1].

TABLE I: Design values for different system specifications.

| N                 | $\sigma_{\tau}$  | β   | $\eta$ | M  | $\hat{Q}$ | $L_1$ | $W_1$ | $L_2$ | $W_2$ |

|-------------------|------------------|-----|--------|----|-----------|-------|-------|-------|-------|

|                   |                  | 88% | 98%    | 16 | 1         | 11    | 8     | N/A   |       |

|                   |                  |     |        | 8  | 1         | 13    | 6     |       | N/A   |

|                   |                  |     | 99.5%  | 16 | 1         | 13    | 6     |       |       |

| 8 $0.01T_{\rm s}$ | $0.01T_{2}$      |     |        | 8  | 1         | 13    | 6     |       |       |

|                   | 0.0115           | 92% | 98%    | 16 | 1         | 17    | 7     |       |       |

|                   |                  |     |        | 8  | 1         | 17    | 7     |       |       |

|                   |                  |     | 99.5%  | 16 | 1         | 17    | 7     |       |       |

|                   |                  |     |        | 8  | 1         | 17    | 13    |       |       |

| 12                | $0.005T_{\rm s}$ | 88% | 98%    | 16 | 2         | 21    | 9     | 5     | 4     |

|                   |                  | 88% | 98%    | 16 | 2         | 25    | 10    | 5     | 4     |

| 12                | $0.01T_{ m s}$   |     |        | 8  | 2         | 25    | 10    | 5     | 4     |

|                   |                  |     | 99.5%  | 16 | 2         | 25    | 10    | 5     | 9     |

|                   |                  |     |        | 8  | 2         | 25    | 11    | 7     | 7     |

|                   |                  | 92% | 98%    | 16 | 2         | 37    | 10    | 5     | 8     |

|                   |                  |     |        | 8  | 2         | 37    | 11    | 7     | 7     |

|                   |                  |     | 99.5%  | 16 | 2         | 37    | 11    | 7     | 7     |

|                   |                  |     |        | 8  | 2         | 37    | 12    | 9     | 10    |

The multiplication operation of the two unsigned inputs a and b can be converted into

$$y = a \times b = 2^{\log_2 a + \log_2 b}.$$

(34)

The base-2 logarithmic operation can be approximated to

$$\log_2 a \approx \lfloor \log_2 a \rfloor + \zeta_1 (a \, 2^{-\lfloor \log_2 a \rfloor} - 1), \tag{35}$$

where  $\zeta_1(.)$  is a correction function selected in order to give the required logarithmic approximation accuracy,  $\lfloor . \rfloor$  is the floor operator, and  $\lfloor \log_2 a \rfloor$  can be easily evaluated by looking for the leading '1' in the binary representation of *a*. Similarly, the exponential operation can be approximated to

$$2^{c} \approx 2^{\lfloor c \rfloor} + 2^{\lfloor c \rfloor} \zeta_{e}(c - \lfloor c \rfloor), \tag{36}$$

where  $\zeta_{e}(.)$  is a correction function.

In Mitchell's logarithmic multiplier [24], linear interpolation is used for both the exponential and logarithmic approximations, i.e.,  $\zeta_{l}(x) = \zeta_{e}(x) = x$ . This is the approximation that our design uses for the multipliers in the correlators indexed 0 through M - 1 in Figure 2. For the  $M^{\text{th}}$  correlator we let  $\zeta_{l}(x) = \zeta_{e}(x) = 0$ , because only an approximate value for  $T_{s} \frac{dR_{sx}(T_{s})}{d\tau}$  is required.

Accurate approximations are needed for the three multipliers depicted in Figure 5c, in these cases we use  $\zeta_{\rm I}(x) = x + c_{\rm I}(\lfloor 32x \rfloor)$  and  $\zeta_{\rm e}(x) = x + c_{\rm e}(\lfloor 32x \rfloor)$ , where  $c_{\rm I}(\lfloor 32x \rfloor)$  and  $c_{\rm e}(\lfloor 32x \rfloor)$  are two hard-coded look-up tables each containing 32 entries.

Table II reports the area and power result from synthesizing an unsigned  $15bit \times 15bit$  multiplier using various approximation functions targeting TSMC 28nm HPL process and 300MHz clock. We can see that the area and power are reduced by 42% and 22% respectively when the linear correction functions is used compared to conventional implementation.

#### VIII. RESULTS

In this section, we report the simulation results obtained using a fixed-point Matlab model for the proposed calibration algorithm targeting the system specifications detailed in Section II, unless stated otherwise. For the estimation procedure,

|                                                                                                                                                       | Area          | Power       | Relative error       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|----------------------|

| Conventional multiplier                                                                                                                               | $625\mu m^2$  | $143 \mu W$ | 0%                   |

| Logarithmic mult. with<br>$\zeta_{l}(x) \triangleq x + c_{l}(\lfloor 32 \ x \rfloor),$<br>$\zeta_{e}(x) \triangleq x + c_{e}(\lfloor 32 \ x \rfloor)$ | $564 \mu m^2$ | $135 \mu W$ | $-1.3\% \sim 0.8\%$  |

| Logarithmic mult. with $\zeta_1(x) = \zeta_e(x) \triangleq x$                                                                                         | $363\mu m^2$  | $112 \mu W$ | 0%~11.1%             |

| Logarithmic mult. with $\zeta_{l}(x) = \zeta_{e}(x) \triangleq 0$                                                                                     | $174 \mu m^2$ | $99\mu W$   | $-100\%{\sim}49.2\%$ |

TABLE II: AREA UTILIZATION AND POWER FOR DIFFERENT MULTIPLIER IMPLEMENTATIONS.

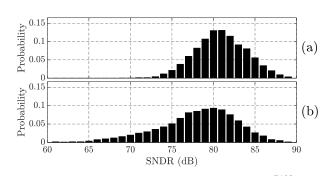

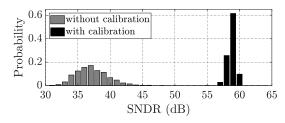

Fig. 7: Histogram for measured SNDR using input frequency  $\frac{7193}{2^{13}}\pi$ . The timing reference is selected as (a)  $r = \overline{\tau}$ , and (b)  $r = \tau_0$ .

we use  $L = 2^{13}$ , i.e.,  $ML = 2^{16}$  samples are processed for each calibration cycle.

In the following subsections, three scenarios are considered in turn

- an ADC system with infinite precision (N → ∞) and perfect time skew estimation. This creates a baseline set of results where the effects of both ADC quantization and time skew estimation errors are ignored.

- 2) an ADC system with  $N \to \infty$  where both the estimation and correction mechanisms are connected to form a closed-loop.

- 3) a 12-bit ADC with closed-loop calibration.

## A. Scenario 1

In this scenario, the ADC has an infinite precision, and we assume that the time skew values are known (known as a "Genie-based" approach). Monte Carlo simulations were run for 10,000 ADC instances with randomly generated time skews and a full-scale sinusoidal input with frequency  $\frac{7193}{2^{13}}\pi$ .

Figures 7a and 7b show the resulting histogram for the measured SNDR with a timing reference  $r = \bar{\tau}$  and  $r = \tau_0$  respectively. For a 12-bit ADC, we target 74dB SNDR performance<sup>4</sup>. We see that when  $r = \bar{\tau}$ , the target performance is achieved in 98.7% of the ADC instances; this is in line with the target specification of  $\eta = 98\%$ . For  $r = \tau_0$ , the target performance is satisfied in only 81.4% of the instances.

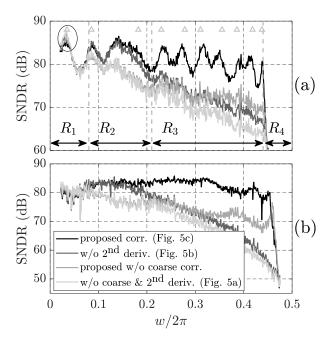

To assess any frequency dependency, we repeated the same SNDR measurements for sinusoidal inputs at different frequencies. Additionally, to quantify the significance of each part of the proposed correction mechanism depicted in Figure 5c, we simulate the system for the three correction mechanisms in Figure 5 and using the proposed calibration method without the coarse correction stage; the results are presented together in Figure 8a. The frequency range is divided into four regions:  $R_1$  through  $R_4$ , as indicated.

The SNDR satisfies the required level of 74dB within the frequency band of interest (regions  $R_1 - R_3$ ) when the full proposed correction mechanism depicted in Figure 5c is used. There is a correlation between the achieved SNDR and the error of the magnitude response for  $h_{d,1}$  shown in Figure 6a. The local SNDR maximas occur when the error hits the zero level; the corresponding frequencies are marked by light gray triangles in both figures. This is an indication that the error in  $h_{d,1}$  dominates the performance, and both the second order and the non-uniform sampled input distortions are successfully suppressed by  $h_{d,2}$  and  $h_{d,c}$  respectively. A minor performance degradation compared to other correction configurations can be observed in the low frequency region marked with a circle in Figure 8a. This degradation occurs because  $|\nu_{d,c}(w)| > w$  in this frequency range, a possibility that was noted in Subsection V-A.

Looking at the other traces in Figure 8a, we see that in the absence of  $h_{d,c}$  and/or  $h_{d,2}$ , a significant performance degradation occurs, and this becomes more pronounced with increasing the frequency. In the range  $R_1$ , the error in  $h_{d,1}$ dominates the performance in all traces. In frequency range  $R_2$ , the correction mechanisms without coarse stage suffer more SNDR degradation, suggesting that the impact of the non-uniform sampled input distortion is larger than all other distortion sources. For the range  $R_3$ , we can notice that the second order distortion correction stage dominates the performance for the correction mechanisms that do not have the filter  $h_{d,2}$ . We may conclude that the proposed architecture depicted in Figure 5c is suitable for ADC designs intended to utilize most of the available Nyquist range.

#### B. Scenario 2

We compared the results obtained in the previous test depicted in Figure 8a with the results shown in Figure 8b, which are obtained when the estimation-and-correction loop is closed. With the proposed correction mechanism, the SNDR experiences a minor degradation in some of the cases; however, it still meets the target performance. In some other cases, a better SNDR is obtained due to adjusting the estimated time skew to compensate the error in the magnitude response of  $h_{d,1}$  corresponding to the input frequency; however, we consider this to be a false (i.e., non-representative) improvement, because it occurs only for simple input signals with narrow bandwidth. Because of this phenomenon, we present results for a more complex input signal in the next subsection.

We note that there is a large drop in performance when the second order correction stage is removed in this scenario compared to the results obtained with perfect estimation in Figure 8a. From this we conclude that the correction of the

$<sup>^{4}</sup>$ In this simulation, the performance is limited only by the time skew mismatch.

Fig. 8: Measured average SNDR  $(N \rightarrow \infty)$  with sinusoidal input, plotted against the input frequency, for different correction mechanisms (a) with perfect estimation, and (b) with closed-loop calibration.

second order terms has a significant impact on the accuracy of the time skew estimates.

#### C. Scenario 3

In this subsection, we verify the proposed estimation and correction closed-loop with a 12-bit ADC where the early terminated samples have 10-bit resolution. To model other types of ADC impairments, Gaussian distributed noise is added to the ADC's input; the additive noise level is selected to limit the ENOB to 11 bits, i.e., the maximum possible SNDR for a sinusoidal input is 68dB. All outputs after calibration are rounded to 12 bits, causing a minor SNDR degradation.

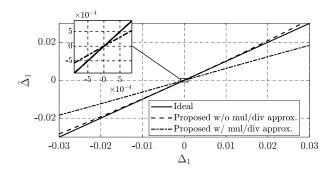

To verify the accuracy of the proposed estimation algorithm, Figure 9 depicts the estimated time skew residue  $\tilde{\Delta}_1$  obtained from (16) using a sinusoidal input against the actual value  $\Delta_1$ predicted in (3). The estimated values are plotted with and without the proposed HW simplifications in Section VII and the  $\lceil . \rceil_2$  approximation in (15). Without these simplifications,  $\tilde{\Delta}_1$  is estimated correctly for small values of  $\Delta_1$ ; however, it suffers from visible non-linearity at large  $\Delta_1$ , this effect is neutralized on convergence as  $\Delta_1 \rightarrow 0$ . Using the proposed simplifications,  $\tilde{\Delta}_1$  is under-estimated mainly due to the use of  $\lceil . \rceil_2$ ; however, all estimates are scaled down by the same factor, an effect that can be absorbed in the adaptation step size  $\mu$  in (4).

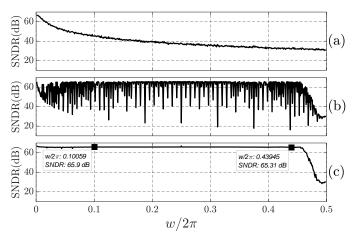

Figure 10 shows the measured average SNDR using a simple sinusoidal input at different frequencies. Figure 10a shows the results before calibration where over 30dB SNDR degradation is noticed at high input frequency. Figure 10b shows the results when the sampling sequence intervention is absent; a dramatic degradation can be noticed at certain frequencies due to the limitations of blind estimation algorithms

Fig. 9: Estimated time skew residue against the actual.

Fig. 10: Measured SNDR using a 12-bit ADC model and a sinusoidal input (a) without calibration, (b) with calibration and normal sampling sequence, (c) with calibration and sampling sequence intervention.

discussed in Section IV. On the other hand, these limitations are relaxed with the proposed sampling sequence intervention whose results are shown in Figure 10c. The average measured SNDR is approximately 65.5dB over the target bandwidth. The average measured SNDR and SFDR for input frequency around  $w = \beta \pi$  are 65.3dB and 82.6 respectively.

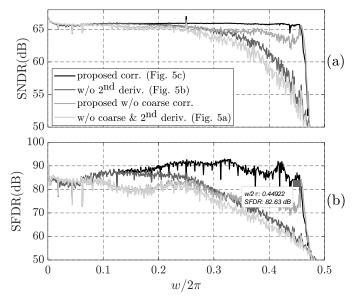

Figure 11a and 11b depict the average measured SNDR and SFDR, respectively, against the input frequency using different correction mechanisms under the same conditions of the previous test, these measurements being taken after 100 calibration cycles. From these results, we can see that the proposed correction mechanism does not suffer from significant performance degradation on increasing the input frequency, in contrast to conventional digital correction mechanisms based on the Taylor series depicted in Figure 5a.

A more complex input consisting of 64 sinusoids was also used for testing. Figure 12 shows the measured PSD for the TIADC output before and after 50 calibration cycles, where we note that the mismatch spurs are successfully reduced by 32.1dB.

A Monte Carlo simulation with a band-limited random input signal is used; the input consists of independent and identically distributed (i.i.d.) samples, and a low-pass filter is used to limit the signal bandwidth to  $0.88\pi$ . The test is repeated 1,000 times with different input and time skew parameters; a histogram of the measured SNDR before and after 640 calibration cycles is

Fig. 11: Measured SNDR and SFDR using a 12-bit ADC model and a sinusoidal input with different digital correction configurations.

Fig. 12: Measured PSD for multi-tone input (a) before, (b) after calibration.

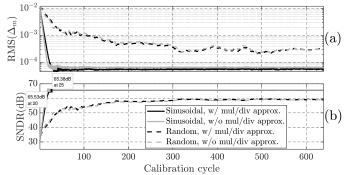

shown in Figure 13. On average, the SNDR is improved from 37.2dB to 58.8dB.

To investigate the convergence behavior, we use a sinusoidal input having frequency  $w = \frac{7193}{2^{13}}\pi$ . Figure 14 depicts the evolution of the RMS of the time skew residues and the SNDR during the calibration process where the algorithm converges after 30 calibration cycles. The figure also depicts the performance evolution for a band-limited random input where the calibration algorithm converges after approximately 300 calibration cycles, which is ten times slower compared to the results obtained for a simple sinusoidal input. The slow convergence is due to the fact that it takes many more samples to produce accurate correlation estimates,  $c_m$ , in the case of a random signal compared to a sinusoidal input. Also, the figure compares the convergence behaviour when all multipliers and dividers are implemented with and without the proposed HW simplifications. For a sinusoidal input, the measured SNDR hits 65.2dB after 25 and 20 calibration cycles with and without those simplifications respectively; this difference is mainly due to using the approximation  $[.]_2$  in (15).

Fig. 13: Measured SNDR histogram using a band-limited input signal.

Fig. 14: The convergence, using different input signal types, of (a) the root mean square of the time skew residues, (b) the SNDR.

| TABLE III: AREA UTILIZATION AND POWER BREAKDOWN FOR THI | 3 |

|---------------------------------------------------------|---|

| CALIBRATION ALGORITHM.                                  |   |

|            | Area             | Area% | Power  | Power% |

|------------|------------------|-------|--------|--------|

| Estimation | $7,439\mu m^2$   | 24%   | 2.4mW  | 22%    |

| Correction | 22,946 $\mu m^2$ | 76%   | 8.6mW  | 78%    |

| Total      | $30,386\mu m^2$  | 100%  | 11.0mW | 100%   |

#### D. Hardware implementation and comparison

A VHDL implementation for the proposed calibration algorithm was carried out, which was verified to be a bitaccurate representation for the Matlab model via simulation. The implementation supports the estimation and the correction for time skew values within  $\pm 6\sigma_{\tau}$ .

The design was synthesized using the Synopsys Design Compiler tool in TSMC 28nm HPL process targeting a 300MHz clock to provide 2.4GS/s aggregated sampling rate. Successful gate level simulation was carried out, allowing to measure the switching activity for each internal signal in the design across two complete calibration cycles. Table III shows the area utilization and power breakdown. The design occupies an area of  $0.03 \text{mm}^2$  and consumed 11mW. Without the use of the HW simplifications proposed in Section VII, the estimation circuit occupies  $9,852\mu m^2$  and consumes 3.2mW, i.e., the proposed simplifications enable 25% area and power reduction.

## IX. CONCLUSION

In this paper, a digital time skew calibration technique was presented which can be used for a TIADC system with an arbitrary number of sub-ADCs. A novel hardware modification suitable for SAR ADCs is suggested to relax the limitations that face blind estimation techniques. The resulting increased robustness of the estimator comes at the cost of a very minor reduction in the ADC output precision. A two-stage correction mechanism was proposed to satisfy the target high precision correction. A quantitative study was conducted on the requirements imposed on the digital correction to achieve the target performance and yield, and a filter design method was proposed to enforce these requirements. We proposed tailored hardware implementations for the main multipliers in both the correction and estimation sides, which leads to a 25% area and power reduction in the estimation circuit. The proposed calibration method was verified via Matlab using different input signal types. The calibration algorithm maintains the SNDR above 65dB for a sinusoidal input within the target bandwidth, which cannot be achieved via conventional digital correction mechanisms based on the Taylor series. A VHDL model was implemented and synthesized using 28nm HPL TSMC process, targeting a 2.4GHz sampling frequency for an 8 sub-ADC system. The calibration block occupies 0.03mm<sup>2</sup> and consumes 11mW.

#### ACKNOWLEDGMENT

The authors would like to thank Benjamin Tardivel, Gavin Lacy and João Marques for the fruitful discussion during the algorithm design and implementation.

## APPENDIX A INVERSION OF U

Using the unitary *M*-point discrete Fourier transform (DFT) matrix **F** having (x, y) entry  $F_{x,y} = e^{-j\frac{2\pi xy}{M}}/\sqrt{M}$ , the circulant matrix **U** described in (13) can be diagonalized as

$$\mathbf{U} = \mathbf{F}^{\mathcal{H}} \mathbf{\Lambda} \mathbf{F},\tag{37}$$

where  $(.)^{\mathcal{H}}$  is the Hermitian transpose, and  $\Lambda \triangleq \operatorname{diag}(\lambda_0, \lambda_1, \ldots, \lambda_{M-1})$  is a diagonal matrix of eigenvalues of **U**, which, recalling (13), can be computed to be (c.f. [25])

$$\lambda_k = 2 - 2\cos\left(\frac{2\pi}{M}k\right). \tag{38}$$

We note that U is a rank-deficient matrix since  $\lambda_0 = 0$ , and thus U is non-invertible. This non-invertibility was also noted in [1], [7], [8], [16]; the solution proposed in [7], [8] involved the removal of a row of U (and of the corresponding value in e) and then applying the Moore-Penrose pseudo inverse formula. In [1] and [16], it was suggested to force  $\Delta_0 =$ 0 in order to be able to find a solution. In this work, we apply a more general pseudo inverse methodology that does not involve the removal of any measurement data, nor the application of an unnecessary constraint on any particular  $\tau_m$ . Specifically, we compute U<sup>†</sup>, the generalized pseudo inverse using the singular-value decomposition (SVD) technique [26], as

$$\mathbf{U}^{\dagger} = \mathbf{F}^{\mathcal{H}} \begin{bmatrix} 0 & 0 & 0 & \dots & 0 \\ 0 & \lambda_1^{-1} & 0 & \dots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \dots & \lambda_{M-1}^{-1} \end{bmatrix} \mathbf{F}.$$

(39)

The (x, y)-entry of  $\mathbf{U}^{\dagger}$  is given by

$$U_{x,y}^{\dagger} = \frac{1}{M} \sum_{k=1}^{M-1} \frac{1}{\lambda_k} e^{-j\frac{2\pi k(y-x)}{M}}.$$

(40)

Since  $\lambda_k = \lambda_{M-k}$  for every k, all elements in  $\mathbf{U}^{\dagger}$  are real, and from (40) we can note that  $\mathbf{U}^{\dagger}$  is a symmetric circulant matrix; this also implies that  $\mathbf{U}^{\dagger}$  can be described using at most  $\lceil \frac{M+1}{2} \rceil$  distinct values. These features can be exploited to simplify the hardware implementation of the calculations needed in (16). Note that these features are not present in other algorithms that employ matrix manipulation for time skew estimation, e.g., [1], [7], [8], [16].

We note that  $\mathbf{F}^{\mathcal{H}}$  acts as an inverse DFT operator, and the inclusion of a zero in the upper-leftmost position of the diagonal matrix in (39) constrains the solution to (16) to have zero mean as concluded in (17).

Using (40), it can be shown that the elements of  $\mathbf{U}^{\dagger}$  can be represented as constant rational numbers whose common denominator is at most 12*M*. As an example, for M = 6 we have

$$\mathbf{U}^{\dagger} = \frac{1}{72} \begin{bmatrix} 35 & 5 & -13 & -19 & -13 & 5\\ 5 & 35 & 5 & -13 & -19 & -13\\ -13 & 5 & 35 & 5 & -13 & -19\\ -19 & -13 & 5 & 35 & 5 & -13\\ -13 & -19 & -13 & 5 & 35 & 5\\ 5 & -13 & -19 & -13 & 5 & 35 \end{bmatrix}.$$

(41)

For the proposed feed-backward calibration algorithm, the denominator in (41) can be approximated to a power of two to simplify the calculations in (16).

#### Appendix B

## NON-UNIFORM SAMPLING ANALYSIS

The frequency-dependent nature of the contribution of the non-uniform sampling to the approximation in (23) can be seen by computing the error, compared to the uniform sampling, induced at the output of an ideal first order differentiator filter in response to a sinusoidal input with frequency w and amplitude  $\mathcal{A}$ ,

$$x(t) = \mathcal{A}\sin\left(w\frac{t}{T_{\rm s}}\right).\tag{42}$$

For simplicity and without loss of generality, we let r=0, in which case the  $n^{\text{th}}$  input to the filter can be written as

$$y[n] = x((n+\dot{\tau}[n])T_{s}) = \mathcal{A}\sin((n+\dot{\tau}[n])w)$$

$$\approx x[n] + \underbrace{\mathcal{A}w\dot{\tau}[n]\cos(nw)}_{\text{first order error term}} = x[n] + e[n]$$

(43)

where  $x[n] \triangleq x(nT_s)$ , and the approximation in (43) is valid for sufficiently small  $\dot{\tau}_m$ . The first order error term e[n] can be written as

$$e[n] = \mathcal{A}w\dot{\tau}[n]\cos(n\,w) = \mathcal{A}w\cos(n\,w)\sum_{m=0}^{M-1}\dot{\tau}_m\delta_m(n), \quad (44)$$

where  $\delta_m(n)$  is a train of Kronecker delta functions having period M and phase such that  $\delta_m(m) = 1$ , i.e.,  $\delta_m(n) \triangleq$

$\sum_{i=-\infty}^{\infty} \delta(n-m-iM)$  where  $\delta(n)$  is the discrete-time unit impulse function. The effect of the product of the cosine with  $\delta_m(n)$  is a convolution in the frequency domain which results in M aliased components, i.e.,

$$e[n] = \mathcal{A} w \sum_{a=0}^{M-1} \sum_{m=0}^{M-1} \frac{\dot{\tau}_m}{M} \cos(nw_a + m\,\beta_a), \qquad (45)$$

where the  $\{w_a\}$  and  $\{\beta_a\}$  are the frequencies and phases of the *M* spurs resulting from the time skew.

1) Using the conventional one-stage correction mechanism in Figure 5a: the filter  $h_{d,1}$  output at Node A can be expressed as  $y'[n] = (h_{d,1} * y)[n]$ . Using an ideal  $h_{d,1}$  and the approximated input in (43), the signal at Node B can be written as

$$y'[n]\dot{\tau}[n] = e[n] - w\dot{\tau}[n]\vartheta[n], \qquad (46)$$

where

$$\vartheta[n] = \mathcal{A} \sum_{a=0}^{M-1} \sum_{m=0}^{M-1} \frac{\dot{\tau}_m}{M} w_a \sin(nw_a + m\beta_a).$$

(47)

Accordingly, the output of the correction mechanism can be written as

$$\tilde{x}[n] = x[n] + w \dot{\tau}[n] \vartheta[n], \qquad (48)$$

where we observe that the first order error term, e[n], in (43) has been fully removed; however, another error term appears.

2) Using the two-stage correction mechanism in Figure 5b: the output of  $h_{d,c}$  filter for the input described in (42) can be approximated to  $\mathcal{A}(H_{d,c}(w)/j)\cos(nw)$  where  $H_{d,c}(w)$  is the filter  $h_{d,c}$  purely imaginary frequency response. Thus the input to  $h_{d,1}$  after the coarse correction is approximated by

$$\tilde{y}[n] \approx x(nT_{\rm s}) + \mathcal{A}\nu_{\rm d, c}(w)\dot{\tau}[n]\cos(nw),$$

(49)

where  $\nu_{d,c}(w) \triangleq (jw - H_{d,c}(w))/j$  is the error in the magnitude response of the filter  $h_{d,c}$  at w. Using  $\tilde{y}[n]$  as an input to the fine correction stage and doing a similar analysis, we can write the corrected output as

$$\tilde{x}[n] = x[n] + \nu_{d,c}(w) \dot{\tau}[n] \vartheta[n].$$

(50)

Comparing (48) with (50), we can conclude that the error magnitude is scaled by a factor of  $|\nu_{d,c}(w)|/w$ .

## APPENDIX C FILTER DESIGN

We target the design of a linear phase  $q^{\text{th}}$  order differentiator filter  $h_{d,q}$  with an integer number of samples group delay and zero DC response, necessitating an odd length  $L_q$ . The result of applying a DFT with size F on the filter  $h_{d,q}$  can be written as

$$H_{d,q}[k] = 2^{-b} \sum_{n=0}^{L_q-1} \hat{h}_{d,q}[n] e^{-j\pi \frac{2n}{F}k},$$

(51)

where b is the fractional part width assigned for the required coefficients, and  $\hat{h}_{d,q}[n]$  is an integer scaled version of  $h_{d,q}[n]$ , i.e.,  $\hat{h}_{d,q}[n] = 2^b h_{d,q}[n]$ .

The DFT of the ideal  $q^{\text{th}}$  order differentiator filter with a group delay of length  $(L_q - 1)/2$  can be expressed as

$$\bar{H}_{\mathrm{d},q}[k] = \left(j\frac{2\pi k}{F}\right)^q e^{-j\pi \frac{(L_q-1)}{F}k}, \quad \forall 0 \le k < \frac{F}{2}.$$

(52)

According to the design specifications,  $h_{d,q}$  needs to be designed such that  $|\bar{H}_{d,q}[k] - H_{d,q}[k]| \leq \xi_{d,q}[k], \quad \forall 0 \leq k \leq \lceil \beta F/2 \rceil$ , where  $\beta$  is the ADC target relative bandwidth, and  $\xi_{d,q}[k] \triangleq \xi_{d,q}(2\pi k/F)$  is the upper bound frequencydependent constraint set on  $|\bar{H}_{d,q}[k] - H_{d,q}[k]|$  as per Section VI.

For odd q, if  $h_{d,q}$  is chosen to have an odd symmetry about the center tap, we can guarantee that the phase response satisfies  $\angle \overline{H}_{d,q}[k] = \angle H_{d,q}[k] \pmod{\pi}$ . This allows to form the following Mixed-Integer Linear Programming (MILP) optimization problem

$$\begin{array}{l} \underset{\hat{h}_{d,q}}{\text{minimize}} \sum_{k=0}^{\lceil \beta F/2 \rceil} |\bar{H}_{d,q}[k] - H_{d,q}[k]| \\ \text{subject to} |\bar{H}_{d,q}[k] - H_{d,q}[k]| \leq \xi_{d,q}[k], \forall k \in \{0, ..., \lceil \beta F/2 \rceil\}, \\ \hat{h}_{d,q}[i] = -\hat{h}_{d,q}[L_q - 1 - i], \ i \in \{0, ..., L_q - 1\}, \\ \hat{h}_{d,q}\Big[\frac{L_q - 1}{2}\Big] = 0. \end{array}$$

$$(53)$$

On the surface, this does not appear to be a linear program because of the term  $|\bar{H}_{d,q}[k]-H_{d,q}[k]|$ , which is the magnitude of a complex quantity. However, due to the phase response property guaranteed by the odd symmetry, this term may be expressed as

$$\begin{cases} \frac{|\Re\{\bar{H}_{d,q}[k]\} - \Re\{H_{d,q}[k]\}|}{|\cos \angle \bar{H}_{d,q}[k]|}, & |\Re\{\bar{H}_{d,q}[k]\}| > |\Im\{\bar{H}_{d,q}[k]\}| \\ \frac{|\Im\{\bar{H}_{d,q}[k]\} - \Im\{H_{d,q}[k]\}|}{|\sin \angle \bar{H}_{d,q}[k]|}, & \text{otherwise}, \end{cases}$$

(54)

where  $\Re\{X\}$  and  $\Im\{X\}$  denote the real and imaginary parts respectively of a complex number X. Both branches in (54) are, in principle, the same, but for numerical accuracy reasons, we favor one over the other in the regions indicated. The *linear* relationships between  $\hat{h}_{d,q}$  coefficients and both  $\Re\{H_{d,q}[k]\}$ and  $\Im\{H_{d,q}[k]\}$  are governed by (51), allowing reformulation of the problem into the form of a canonical linear program.

For an even q, a similar approach can be used to design  $\hat{h}_{d,q}$ , except that it is necessary to have an *even* symmetry around the center tap to enforce the required phase response properties, i.e., we can write the MILP optimization problem as

$$\begin{array}{l} \underset{\hat{h}_{d,q}}{\text{minimize}} \sum_{k=0}^{\lceil \beta F/2 \rceil} |\bar{H}_{d,q}[k] - H_{d,q}[k]| \\ \text{subject to} |\bar{H}_{d,q}[k] - H_{d,q}[k]| \leq \xi_{d,q}[k], \forall k \in \{0, ..., \lceil \beta F/2 \rceil\}, \\ \hat{h}_{d,q}[i] = \hat{h}_{d,q}[L_q - 1 - i], \ i \in \{0, ..., L_q - 1\}, \\ \sum_{i=0}^{L_q - 1} \hat{h}_{d,q}[i] = 0. \end{array} \tag{55}$$

This approach allows us to obtain directly a quantized version of the coefficients using a MILP solver, e.g., the intlinprog tool in Matlab, thus obviating the need to perform a distinct quantization operation on the coefficients.

#### REFERENCES

- A. Salib, B. Cardiff, and M. F. Flanagan, "A low-complexity correlationbased time skew estimation technique for time-interleaved SAR ADCs," in *Proc. IEEE Int. Symp. on Circuits and Syst. (ISCAS)*, May 2017, pp. 1–4.

- [2] S. Jamal, D. Fu, N.-J. Chang, P. Hurst, and S. Lewis, "A 10-b 120-msample/s time-interleaved analog-to-digital converter with digital background calibration," *IEEE J. Solid-State Circuits*, vol. 37, no. 12, pp. 1618–1627, Dec. 2002.

- [3] C.-Y. Lin, Y.-H. Wei, and T.-C. Lee, "A 10b 2.6GS/s time-interleaved SAR ADC with background timing-skew calibration," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Jun. 2016, pp. 468–469.

- [4] H. Wei, P. Zhang, B. D. Sahoo, and B. Razavi, "An 8 bit 4 GS/s 120 mW CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1751–1761, Aug. 2014.

- [5] N. L. Dortz, J.-P. Blanc, T. Simon, S. Verhaeren, E. Rouat, P. Urard, S. L. Tual, D. Goguet, C. Lelandais-Perrault, and P. Benabes, "A 1.62GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70dBFS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2014, pp. 386–388.

- [6] A. Uran, M. Kilic, and Y. Leblebici, "Generalization of referenceless timing mismatch calibration methods for time-interleaved ADCs," in *Conference on Ph.D. Research in Microelectronics and Electronics* (*PRIME*), Jul. 2018, pp. 21–24.

- [7] N. L. Dortz, "Compensation numérique pour convertisseur large bande hautement parallélisé," Ph.D. dissertation, Supélec, 2016.

- [8] H. L. Duc, D. M. Nguyen, C. Jabbour, P. Desgreys, O. Jamin, and V. T. Nguyen, "Fully digital feedforward background calibration of clock skews for sub-sampling TIADCs using the polyphase decomposition," *IEEE Trans. on Circuits and Syst. I, Regular Papers*, vol. 64, no. 6, pp. 1515–1528, Jun. 2017.

- [9] Y. X. Zou, S. L. Zhang, Y. C. Lim, and X. Chen, "Timing mismatch compensation in time-interleaved ADCs based on multichannel lagrange polynomial interpolation," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 4, pp. 1123–1131, Apr. 2011.

- [10] A. Mrassy and M. Dessouky, "Channel mismatch background calibration for pipelined time interleaved ADCs," in *Proc. IEEE Int. Conf. on Electron., Circuits and Syst. (ICECS)*, Dec. 2012, pp. 609–612.

- [11] V. Divi and G. W. Wornell, "Blind calibration of timing skew in timeinterleaved analog-to-digital converters," *IEEE J. Sel. Topics Signal Process.*, vol. 3, no. 3, pp. 509–522, Jun. 2009.

- [12] S. Saleem and C. Vogel, "Adaptive blind background calibration of polynomial-represented frequency response mismatches in a twochannel time-interleaved ADC," *IEEE Trans. on Circuits and Syst. I, Regular Papers*, vol. 58, no. 6, pp. 1300–1310, Jun. 2011.

- [13] J. Song, K. Ragab, X. Tang, and N. Sun, "A 10-b 800-MS/s timeinterleaved SAR ADC with fast variance-based timing-skew calibration," *IEEE J. Solid-State Circuits*, vol. 52, no. 10, pp. 2563–2575, Oct. 2017.

- [14] Q. Lei, Y. Zheng, D. Zhu, and L. Siek, "A statistic based time skew calibration method for time-interleaved ADCs," in *Proc. IEEE Int. Symp.* on *Circuits and Syst. (ISCAS)*, Jun. 2014, pp. 2373–2376.

- [15] L. Wang, Q. Wang, and A. C. Carusone, "Time interleaved C-2C SAR ADC with background timing skew calibration in 65nm CMOS," in *Proc. Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 207– 210.

- [16] A. Leuciuc, "Sampling time calibration method for multi-channel interleaved ADCs," in *Proc. IEEE Int. Symp. on Circuits and Syst. (ISCAS)*, May 2017, pp. 1–4.

- [17] S. Chen, L. Wang, H. Zhang, R. Murugesu, D. Dunwell, and A. C. Carusone, "All-digital calibration of timing mismatch error in timeinterleaved analog-to-digital converters," *IEEE Trans. on Very Large Scale Integration Syst.*, vol. 25, no. 9, pp. 2552–2560, Sep. 2017.