# A Hybrid BIST Architecture and its Optimization for SoC Testing

Gert Jervan, Zebo Peng Embedded Systems Laboratory Linköping University, Sweden Raimund Ubar, Helena Kruus Dept. of Computer Engineering Tallinn Technical University, Estonia

#### Overview

- A Hybrid BIST architecture that supports the combination of pseudorandom and deterministic test patterns in cost effective way.

- The architecture can be implemented only in software and is therefore flexible and well suitable for SoC designs.

- An approach to find the optimal balance between pseudorandom and deterministic test sets with minimum cost of time and memory, without losing test quality.

- Our approach can lead to significant decreases in overall test cost.

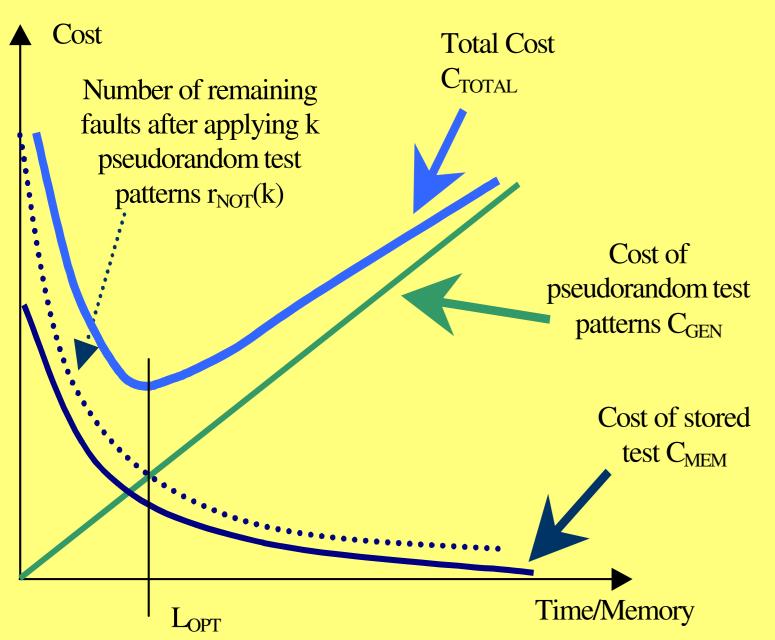

#### **Total Cost Calculation**

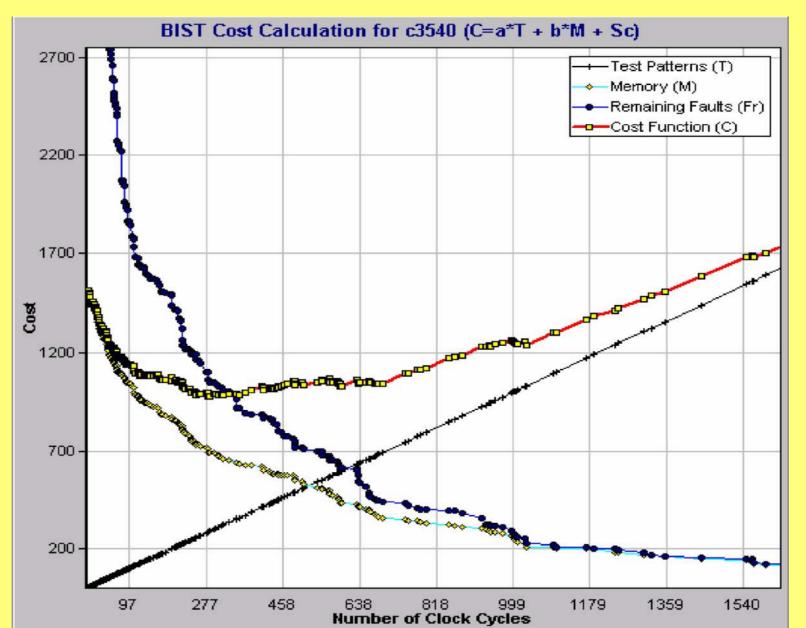

### **Cost Calculation Algorithms**

- Cost and efficiency of pseudorandom test can be calculated based on simulation results.

- Deterministic test set can be calculated by:

- Using ATPG in the loop

- Iteratively transforming fault tables.

- Optimal combination between pseudorandom and deterministic test vectors is found by using a Tabu search heuristic, which reduces the number of calculations significantly (in average 10 times) without losing in cost calculation accuracy (not less than 97,2%).

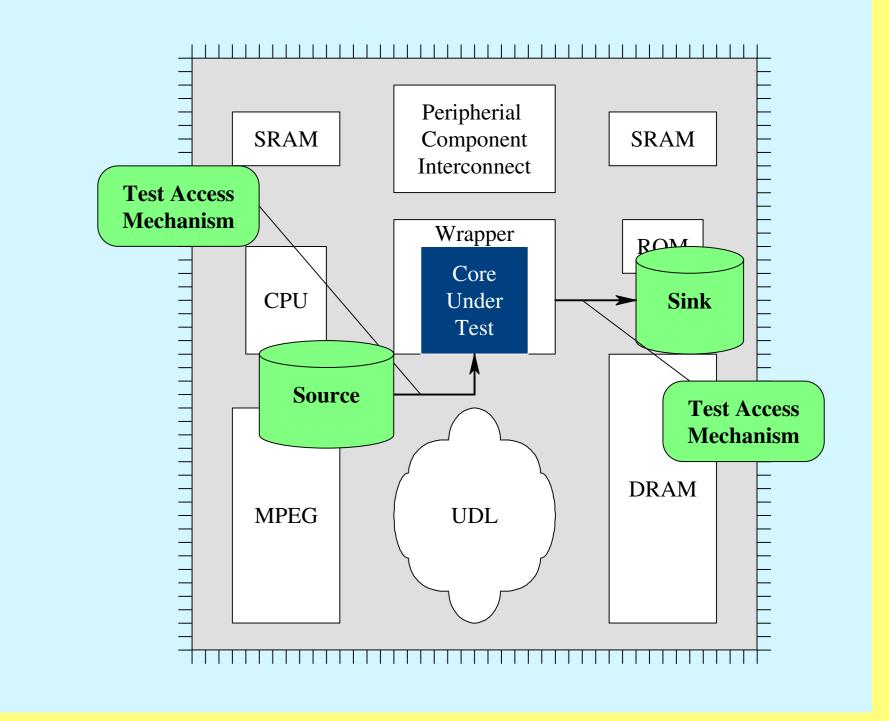

# SoC Testing

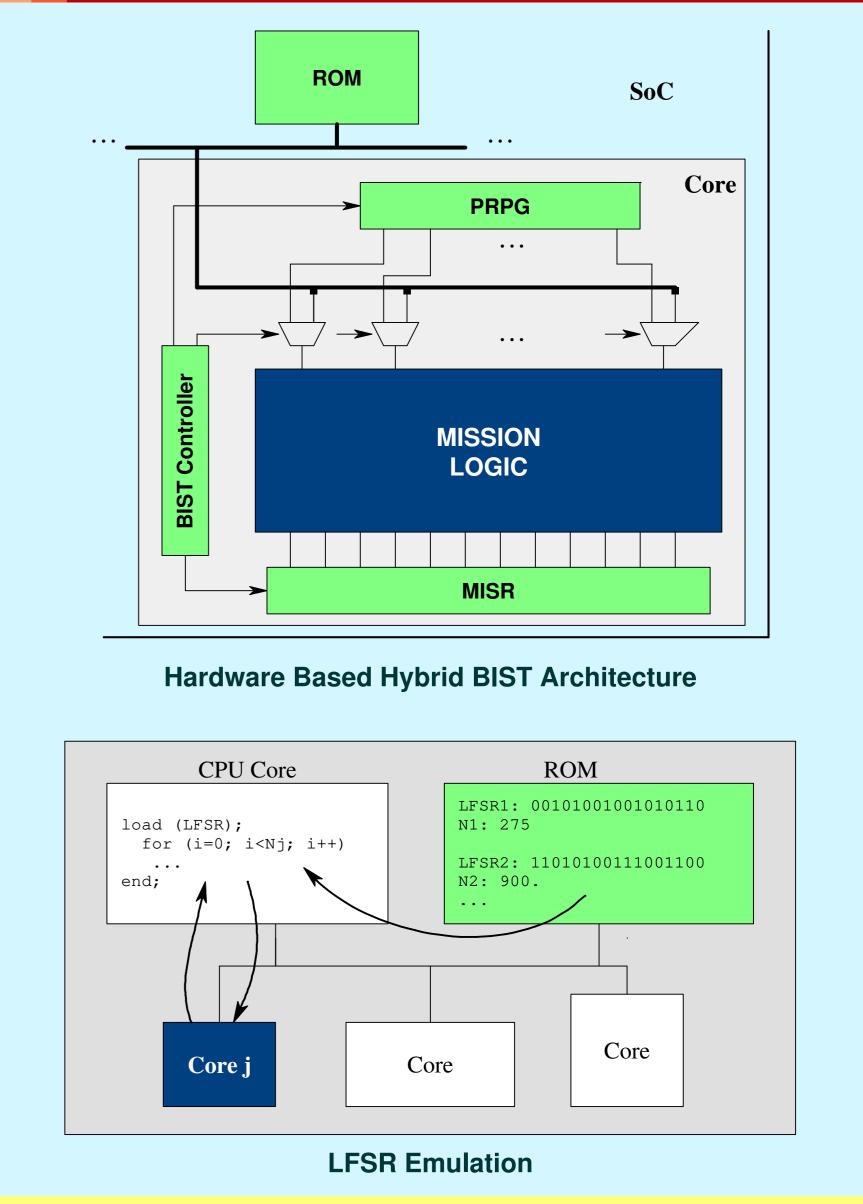

## Hybrid BIST Architecture

## **Experimental Results**

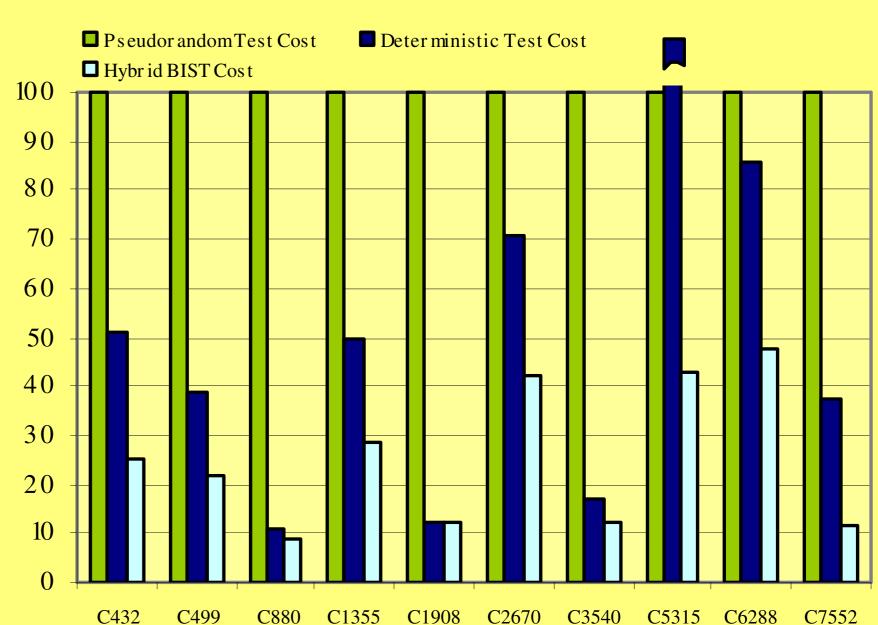

- Hybrid BIST approach gives considerable reduction of cost compare to the pure pseudorandom or deterministic test.

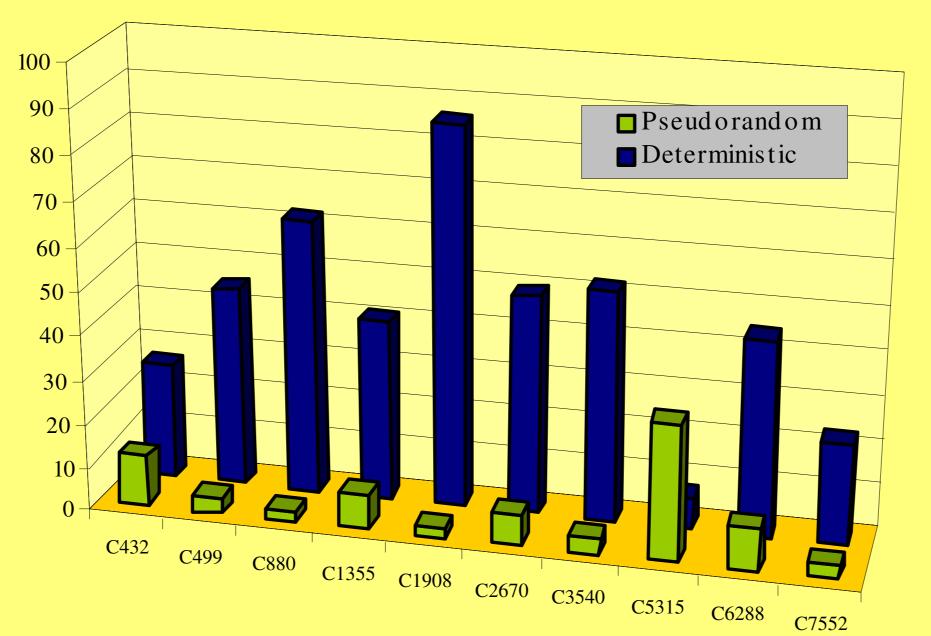

- Typically less than half of the deterministic vectors and only a small fraction of pseudo-random vectors are needed.

- Fault coverage is not sacrified.

Percentage of test patterns in the optimized test sets compared to the original test sets

Cost comparison of different methods.

Cost of pseudorandom test is taken as 100%