## A HYBRID THERMOELECTRIC COOLER THERMAL MANAGEMENT

#### SYSTEM FOR ELECTRONIC PACKAGING

ł

#### A HYBRID THERMOELECTRIC COOLER THERMAL MANAGEMENT SYSTEM FOR ELECTRONIC PACKAGING

By

MD. KAMRUL RUSSEL, B.Sc.

A Thesis

Submitted to the School of Graduate Studies

in Partial Fulfillment of the Requirements

for the Degree

Master of Applied Science

McMaster University

Hamilton, Ontario, Canada

© Copyright by Md. Kamrul Russel, February 2011

MASTER OF APPLIED SCIENCE (2011) (Mechanical Engineering) McMaster University Hamilton, Ontario, Canada

| TITLE      | A Hybrid Thermoelectric Cooler Thermal Management System for Electronic Packaging |

|------------|-----------------------------------------------------------------------------------|

| AUTHOR     | Md. Kamrul I. Russel, B.Sc.                                                       |

| SUPERVISOR | Dr. Chan Y. Ching, Professor<br>Department of Mechanical Engineering              |

NUMBER OF PAGES xvi, 131

#### ABSTRACT

Conventional cooling techniques, such as the use of heat pipes and forced convective cooling can be inadequate for many high performance electronic chips or when the operating ambient temperature is high. In such cases, there is a need for active cooling of the chip to keep its operating temperature below the design point. Thermo-Electric coolers (TEC) provide an attractive option in such instances and have been developed and used for thermal management in electronic packaging systems. Such systems, however, can have a low overall coefficient of performance since the TEC needs to be kept on even at low heat load conditions. In this thesis a hybrid thermal management system is considered that incorporates a TEC based active path in parallel with a conventional heat pipe based passive path. A thermal resistance network model is developed for the hybrid system that takes into account the governing thermo-physical equations for the TEC. The advantage of this hybrid system is that the passive path can transport the heat from the chip at moderate thermal conditions keeping the TEC electrically off while the TEC modules can be turned on when the conditions become adverse. A higher overall system coefficient of performance can be achieved compared to a system consisting of only TEC module(s). One important design parameter is the fraction of the total heat sink area dedicated to each path, which will depend on the rated heat dissipation from the chip, thermal resistance of the entire heat sink and the operational ambient temperature. Controlled experiments were performed to validate the hybrid thermal management model for an example case of electronic package. The experimental facility consisted of a flexible heater to simulate the chip. The heat sink in the experiments was a cooling loop and the ambient temperature was

controlled by changing the temperature of the water flowing through the cooling loop. The thermal resistance of the heat sink was simulated by acrylic glass. Experiments were performed for different fraction of the heat sink area dedicated to the heat transfer paths for a range of ambient temperatures. An operating envelope was presented to compare different hybrid thermal management configurations with a heat pipe based passive system and an only TEC system. The model predictions were in good agreement with the experimental results. Parametric studies were performed to analyze the effect of different variables on the system performance. The hybrid model can be used for other thermal management systems involving TEC modules.

#### ACKNOWLEDGEMENTS

The author would like to acknowledge his gratitude to his supervisor Dr. Chan Y. Ching for his supervision, guidance, motivation and support throughout the course of his studies. The author is grateful to Dr. Jim Cotton for his critical comments and suggestions in the last couple of years on of this thesis. The author would like to give special thanks to Dr. Daniel Ewing for his support and advice on several analytical and technical issues. The author would also like to thank his friend Mohammad Badrul Alam for his time and help on developing the flowcharts presented in Chapter 3.

The technicians in the Mechanical Engineering department shop Joe Verhaeghe, J. P. Talon, Ron Lodewyks, Jim McLaren and Mark Mackenzie provided valuable help at many points during this project.

The author would like to express his gratitude to all his friends and colleagues in the Thermal Management Research Laboratory for their continuous support throughout the course of his graduate program. The author also would like to express his sincere gratitude to his parents, who always encouraged and supported him in all his difficulties. The support from his wife, Zakia Sultana is priceless to the author and without her support it would be impossible to accomplish many achievements.

v

## **TABLE OF CONTENTS**

| ABSTRACT                                                                                      |

|-----------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSv                                                                             |

| TABLE OF CONTENTS                                                                             |

| LIST OF TABLES                                                                                |

| LIST OF FIGURES ix                                                                            |

| NOMENCLATURE                                                                                  |

| Chapter 1 INTRODUCTION                                                                        |

| Chapter 2 LITERATURE REVIEW                                                                   |

| 2.1. Thermoelectric Cooler (TEC)                                                              |

| 2.2. Air Cooled Heat Sinks                                                                    |

| Chapter 3 SYSTEM MODELING                                                                     |

| 3.1. Modeling the Hybrid System                                                               |

| 3.2. Limiting Cases of the Hybrid Model                                                       |

| 3.3. Convergence of the Model                                                                 |

| Chapter 4 EXPERIMENTAL FACILITY                                                               |

| 4.1. Test Facility                                                                            |

| 4.2. Experimental Methodology                                                                 |

| 4.3. Data Analysis                                                                            |

| 4.4. Determination of Component Properties                                                    |

| 4.4.1. Thermal Conductivity of Ceramic Substrate (Alumina, Al <sub>2</sub> O <sub>3</sub> )64 |

| 4.4.2. Thermal Resistance of the Heat Pipe Units                                              |

| 4.4.3. Thermal Resistance of Acrylic71                                                        |

| 4.5. Uncertainty Analysis73                                                                   |

| Chapter 5 RESULTS & DISCUSSION                                                                |

| 5.1. Conventional Passive Thermal Management System $(r_c = 1)$                               |

| 5.2. Only TEC System ( $r_c = 0$ )                                               |

|----------------------------------------------------------------------------------|

| 5.3. Hybrid System                                                               |

| 5.3.1. Hybrid System with $r_C = 0.5$                                            |

| 5.3.2. Hybrid System with $r_C = 0.33$                                           |

| 5.4. Effect of r <sub>C</sub> on Chip Temperature                                |

| 5.5. Effect of Ambient Temperature on Maximum Heat Dissipation Capacity          |

| 5.6. Operating Current and COP <sub>sys</sub> Contours                           |

| 5.7. Effect of $r_C$ on Maximum Heat Dissipation Capacity and $\text{COP}_{sys}$ |

| 5.8. Effect of Number of Thermoelectrics                                         |

| 5.9. Effect of Heat Sink Thermal Resistance                                      |

| Chapter 6 CONCLUSION & RECOMMENDATIONS 117                                       |

| 6.1. Recommendations for Future Work                                             |

| APPENDIX A –TEMPERATURE DEPENDENT PROPERTIES OF THERMO-                          |

| ELEMENTS                                                                         |

| Thomson Effect 122                                                               |

| APPENDIX B –PARAMETRIC STUDIES 124                                               |

| REFERENCES                                                                       |

# LIST OF TABLES

| Table 4.1: Specification data for thermoelectric module (CP 1.4-127-06L)                             |

|------------------------------------------------------------------------------------------------------|

| Table 4.2: Thermal conductivity of acrylic from previous studies (Miller and Kotler, 1993)           |

| Table 4.3: Uncertainty of the measured quantities    74                                              |

| Table 4.4: Uncertainty of the calculated quantities    75                                            |

| Table A.1: Thermo-element (n or p-type) material properties of TEC module CP 1.4-127-06L (Melcor)121 |

### **LIST OF FIGURES**

| Figure 1.1: Schematic of a sealed computer                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Schematic of the hybrid thermal management system                                                                                                 |

| Figure 2.1: Schematic of a typical thermoelectric module9                                                                                                     |

| Figure 2.2: Schematic of thermoelectric module operation                                                                                                      |

| Figure 2.3: Schematic of basic thermocouple demonstrating Seebect effect (Gray, 1961).11                                                                      |

| Figure 2.4: Seebeck coefficient of Bi <sub>2</sub> Te <sub>3</sub> at room temperature (Goldsmid, 1961) 11                                                    |

| Figure 2.5: Schematic of a thermocouple demonstrating Peltier effect (Gray, 1961)13                                                                           |

| Figure 2.6: Schematic illustrating Thomson effect (Gray, 1961)13                                                                                              |

| Figure 2.7: Effect of charge carrier concentration on the components of figure of merit (Ioffe, 1957)                                                         |

| Figure 2.8: Schematic of a typical thermal management system incorporating TEC module.                                                                        |

| Figure 2.9: Typical air cooled heat sink                                                                                                                      |

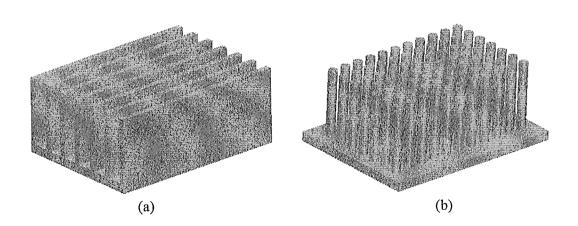

| Figure 2.10: Typical (a) rectangular straight/flat and (b) pin fin heat sink                                                                                  |

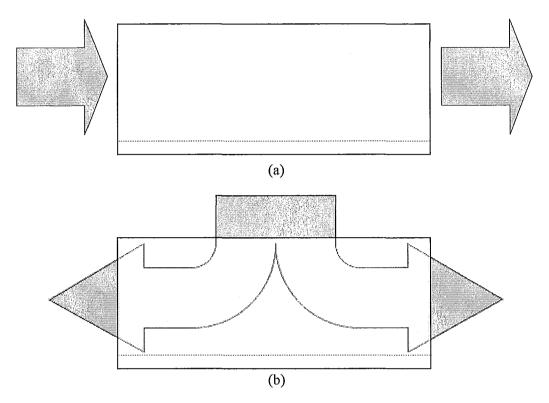

| Figure 2.11: Air flow through the heat sink (a) duct flow and (b) impingement flow 23                                                                         |

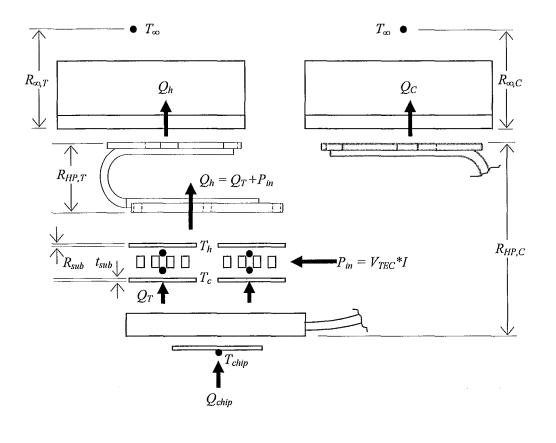

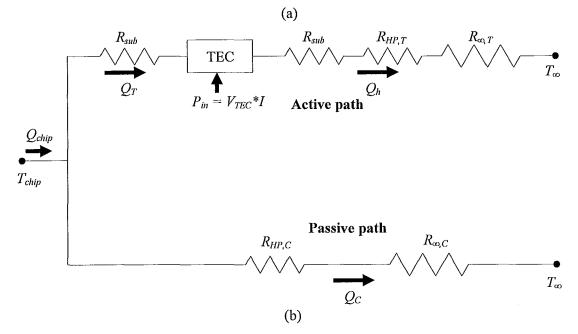

| Figure 3.1: Hybrid thermal management system (a) exploded view (b) thermal resistance network                                                                 |

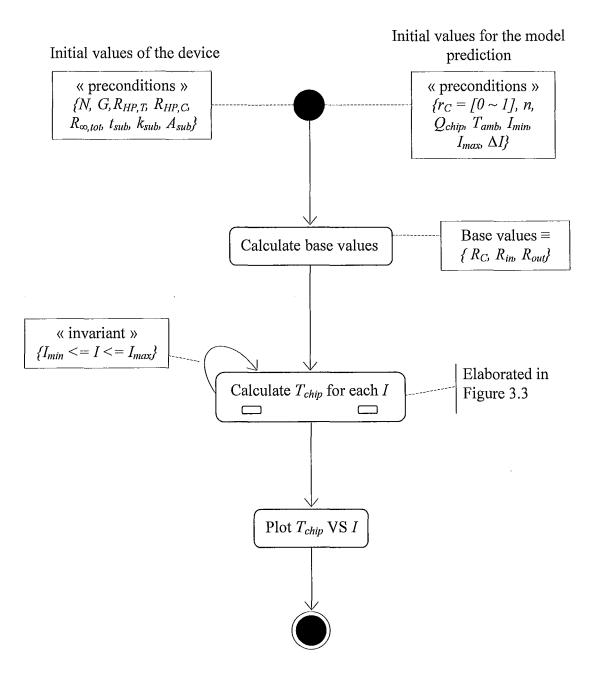

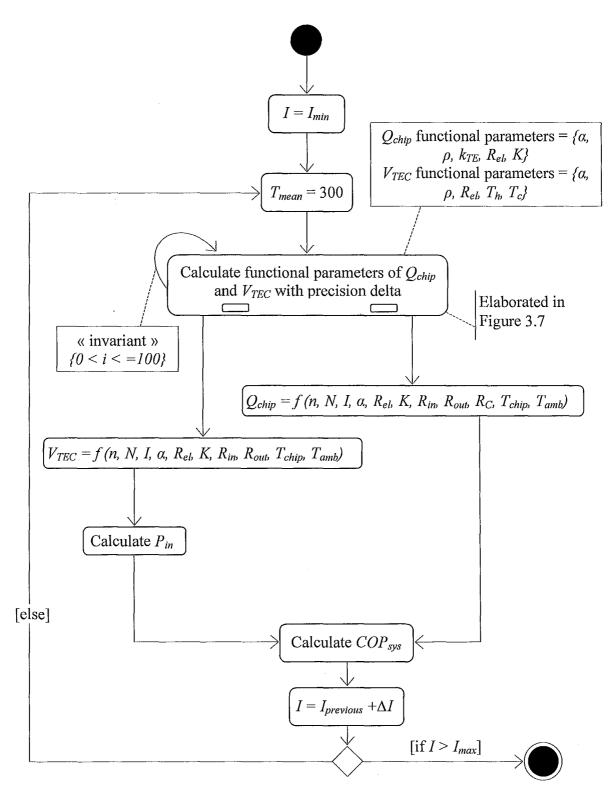

| Figure 3.2: Flowchart ( <i>T<sub>chip</sub></i> VS <i>I</i> ): Top level state diagram for chip temperature at different applied current                      |

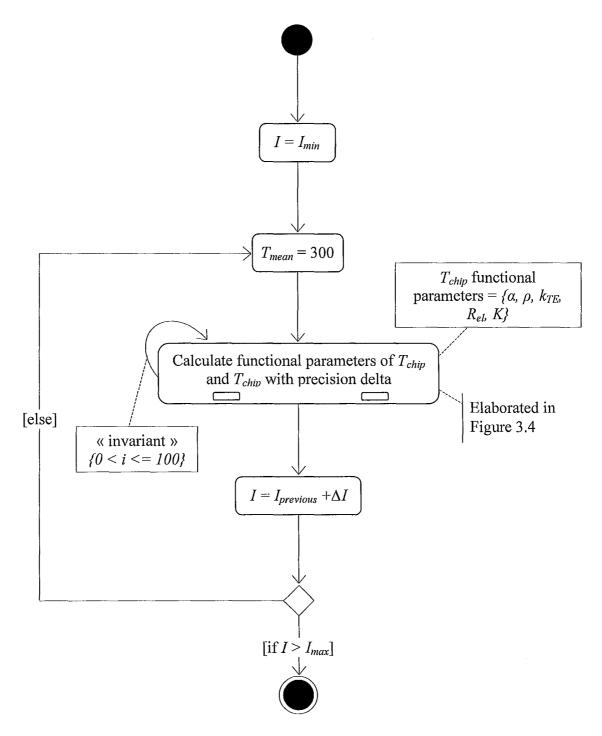

| Figure 3.3: Flowchart ( $T_{chip}$ VS <i>I</i> contd.): Elaboration of calculating chip temperature for each applied current                                  |

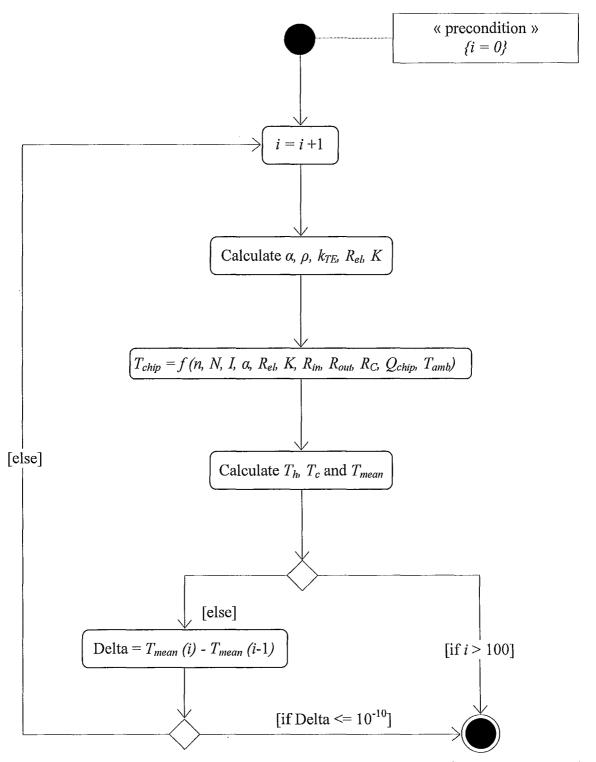

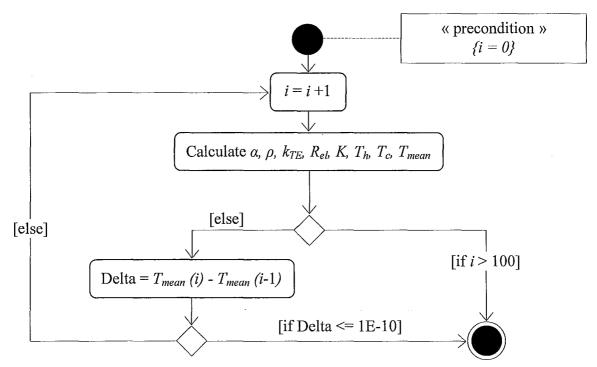

| Figure 3.4: Flowchart ( $T_{chip}$ VS I contd.): Elaboration of calculating chip temperature with precision delta                                             |

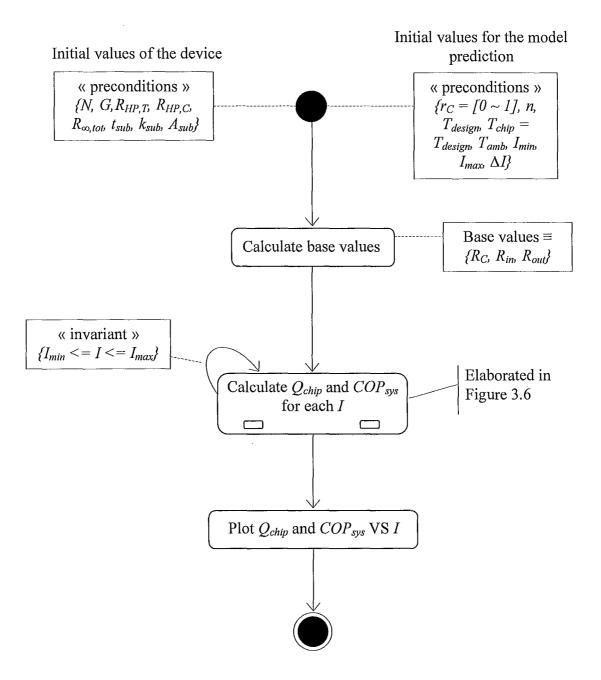

| Figure 3.5: Flowchart ( $Q_{chip}$ VS I at $T_{chip} = T_{design}$ ): Top level state diagram for heat dissipation from the chip at different applied current |

| Figure 3.6: Flowchart ( $Q_{chip}$ VS <i>I</i> at $T_{chip} = T_{design}$ contd.): Elaboration of calculating heat dissipation from the chip and system <i>COP</i> for each applied current                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.7: Flowchart ( $Q_{chip}$ VS <i>I</i> at $T_{chip} = T_{design}$ contd.): Elaboration of calculating the functional parameters of heat dissipation from the chip and voltage with precision delta. 45                                                                                                     |

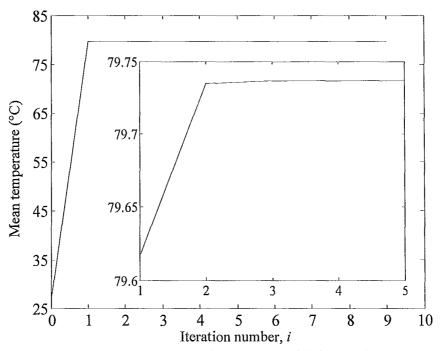

| Figure 3.8: Predicted mean temperature of the hot and cold side of the thermoelectric modules at different iterations ( $n = 2$ , $r_c = 0$ , $I=0.625$ A)                                                                                                                                                         |

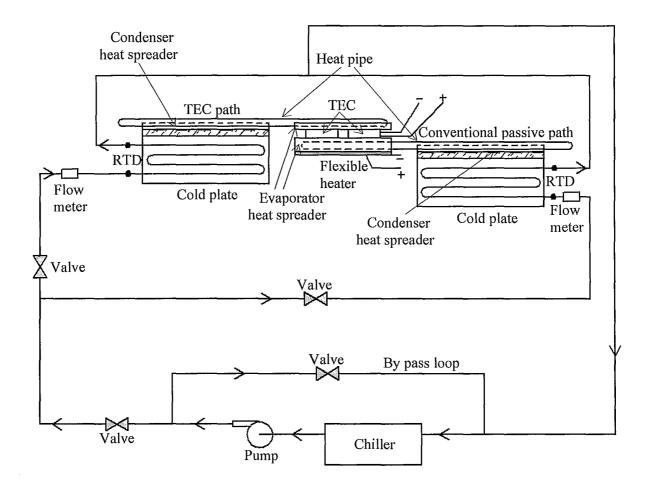

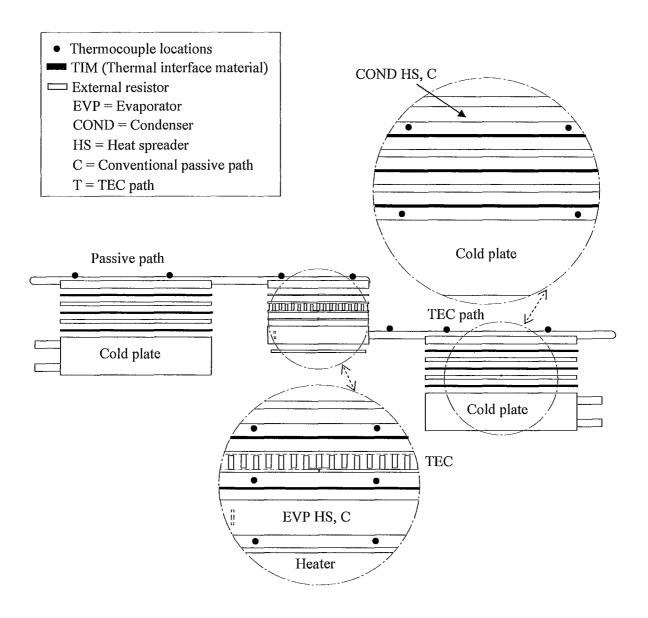

| Figure 4.1: Schematic of the experimental test facility                                                                                                                                                                                                                                                            |

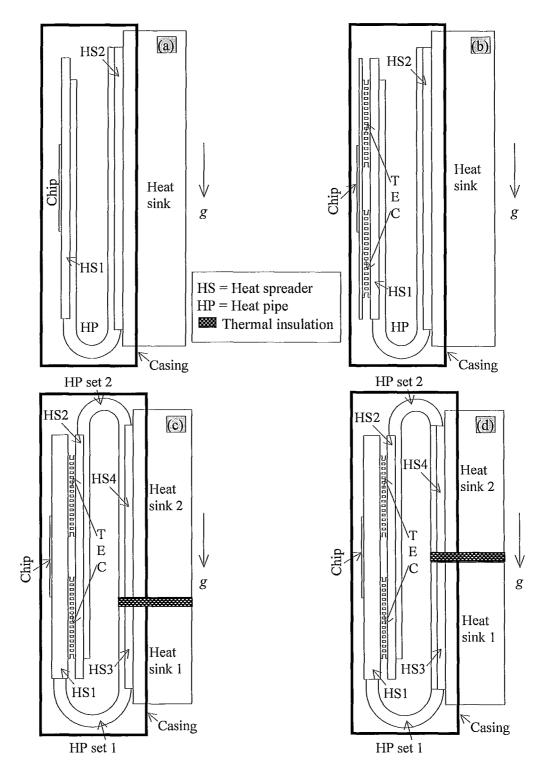

| Figure 4.2: Schematic of different hybrid configurations (a) only passive system ( $r_c = 1$ ), (b) only thermoelectric cooler system ( $r_c = 0$ ) and hybrid system with (c) $r_c = 0.33$ , (d) $r_c = 0.5$                                                                                                      |

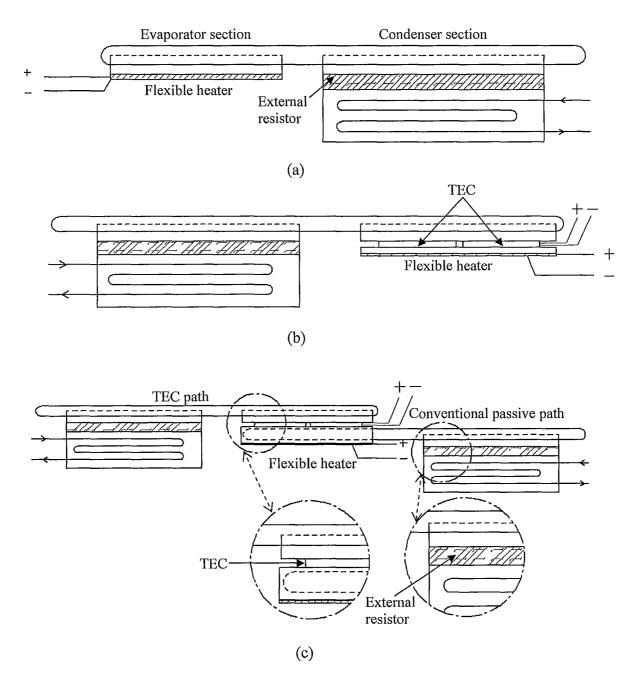

| Figure 4.3: Schematic of different configurations experimented (a) only passive system ( $r_c = 1$ ) (b) only thermoelectric cooler system ( $r_c = 0$ ) and (c) hybrid system ( $0 < r_c < 1$ ) 52                                                                                                                |

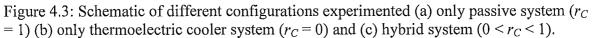

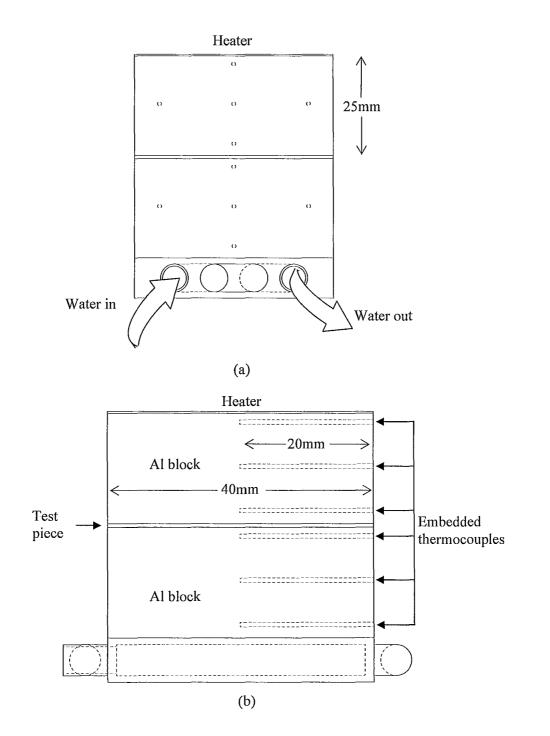

| Figure 4.4: Schematic of the cold plate (a) isometric view, (b) front view and (c) top view. (all units are in mm)                                                                                                                                                                                                 |

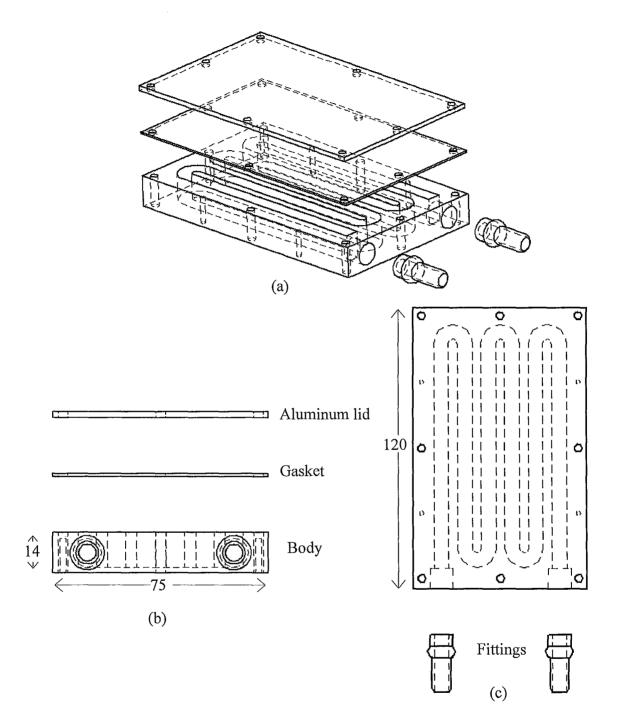

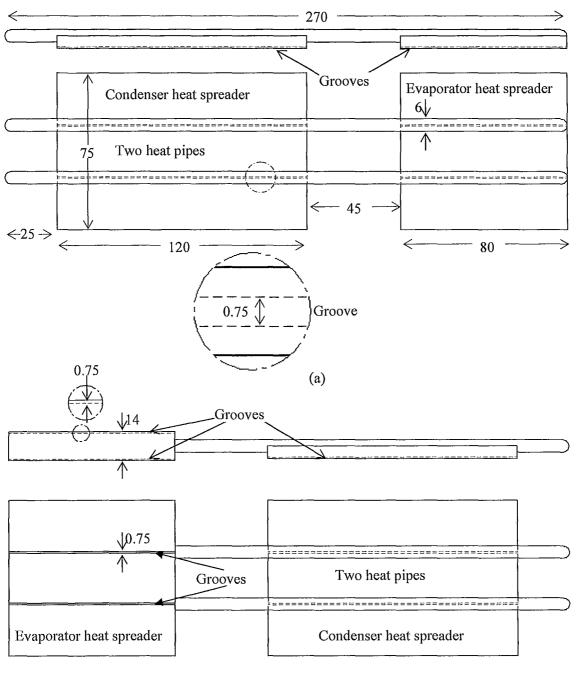

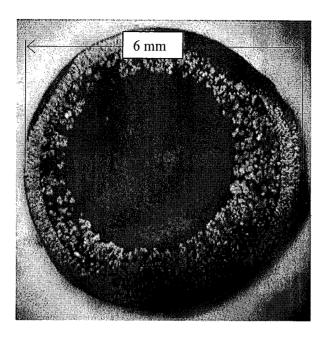

| Figure 4.5: Schematic of heat pipe units (a) for only passive system ( $r_c = 1$ ) or only thermoelectric cooler system ( $r_c = 0$ ) or the TEC based active path in the hybrid system ( $0 < r_c < 1$ ) and (b) for the conventional passive path in the hybrid system ( $0 < r_c < 1$ ). (all units are in mm). |

| Figure 4.6: Cross sectional view of the heat pipes                                                                                                                                                                                                                                                                 |

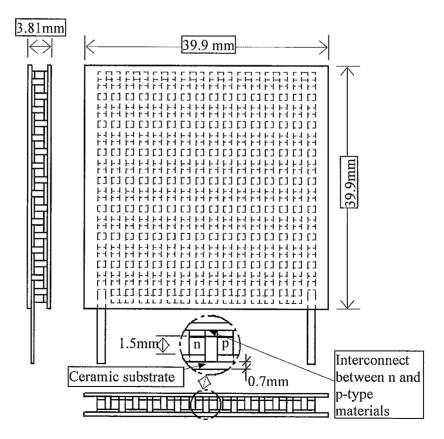

| Figure 4.7: Schematic of thermoelectric module (CP 1.4-127-06L)                                                                                                                                                                                                                                                    |

| Figure 4.8: Location of the T-type thermocouples in the hybrid system                                                                                                                                                                                                                                              |

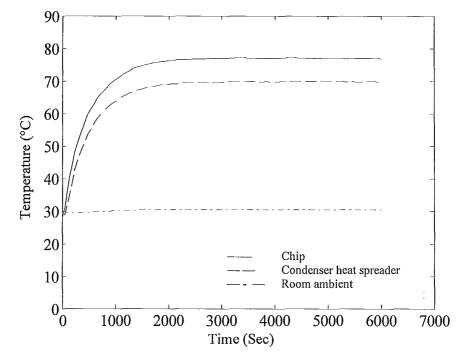

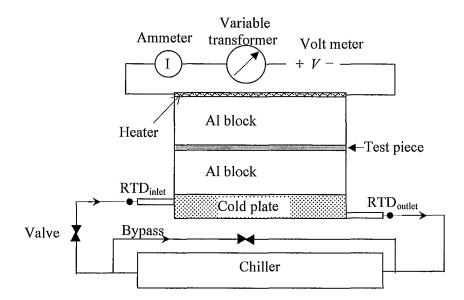

| Figure 4.9: Transient analysis of the system                                                                                                                                                                                                                                                                       |

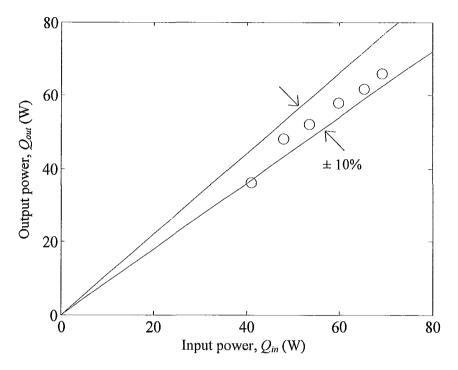

| Figure 4.10: Corrected energy balance                                                                                                                                                                                                                                                                              |

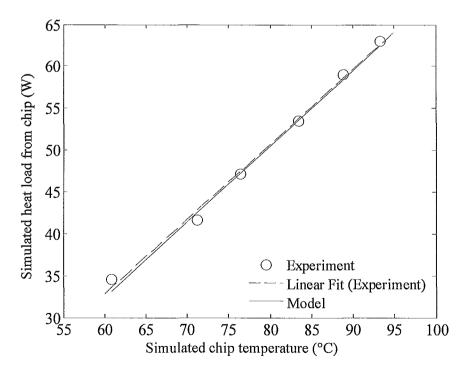

| Figure 4.11: Variation of chip temperature with applied heat load to the chip                                                                                                                                                                                                                                      |

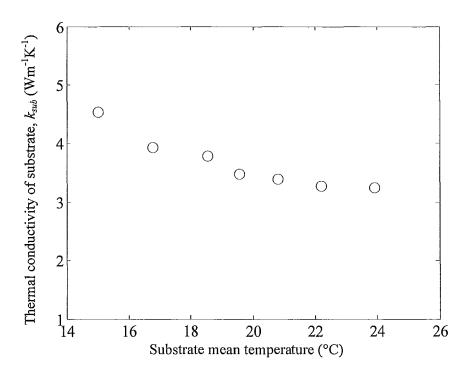

| Figure 4.12: Schematic of the experimental setup to measure thermal conductivity of ceramic substrate                                                                                                                                                                                                              |

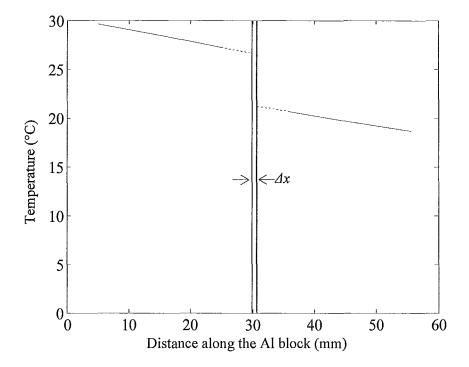

| Figure 4.13: Schematic of the experimental facility showing the locations of the embedded thermocouples in the aluminum blocks (a) front view and (b) side view                                                                                                                                                    |

| Figure 4.14: Temperature distribution along the aluminum blocks to obtain the surface temperatures of the ceramic substrate                                                                                                                                                                                        |

| Figure 4.15: Thermal conductivity of the ceramic substrate at different mean temperatures.                                                                                                                                                                                                                                                                                   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

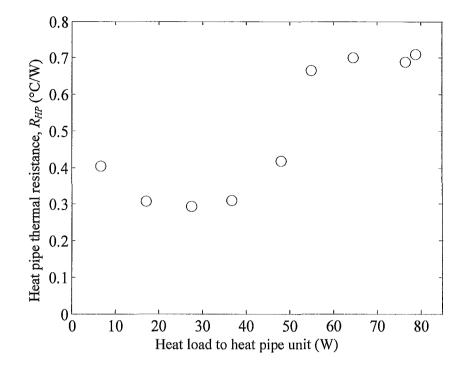

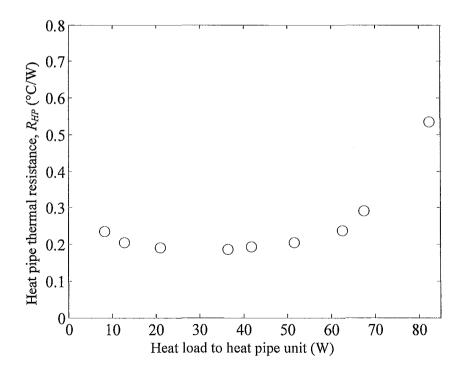

| Figure 4.16: Thermal resistance of heat pipe unit shown in Figure 4.5 (b)                                                                                                                                                                                                                                                                                                    |  |  |

| Figure 4.17: Thermal resistance of heat pipe unit shown in Figure 4.5 (a)70                                                                                                                                                                                                                                                                                                  |  |  |

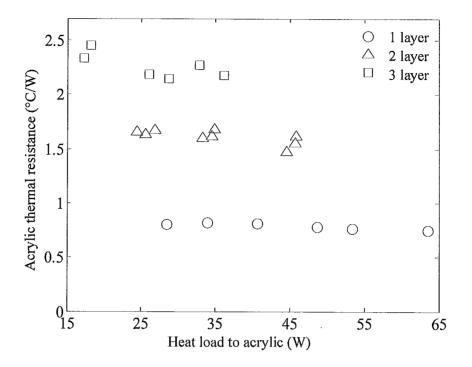

| Figure 4.18: Thermal resistance of different layers of acrylic glass                                                                                                                                                                                                                                                                                                         |  |  |

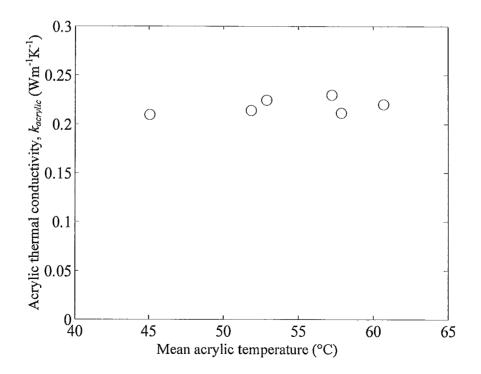

| Figure 4.19: Thermal conductivity of acrylic glass at different mean temperatures                                                                                                                                                                                                                                                                                            |  |  |

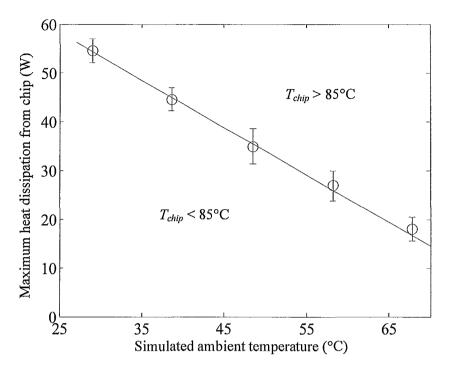

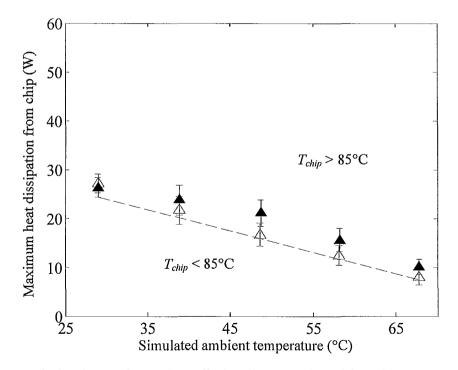

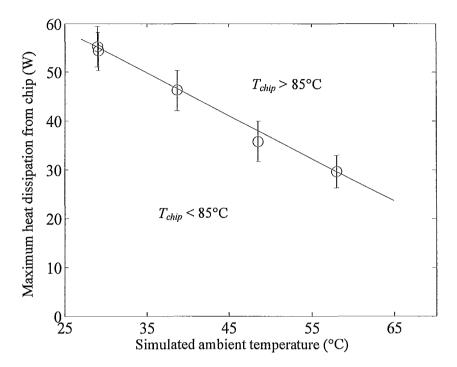

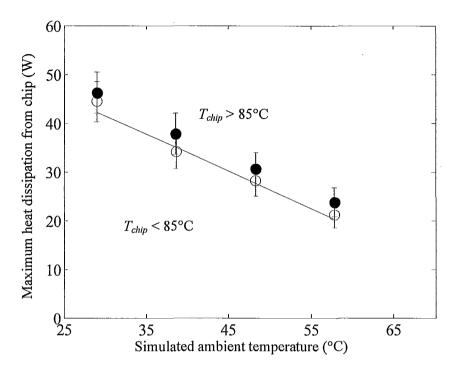

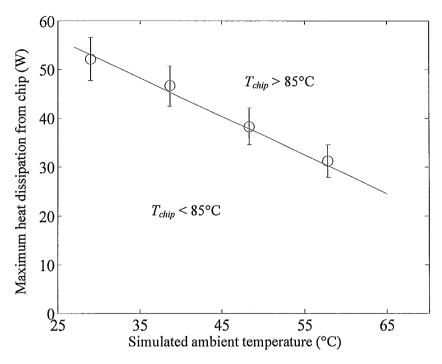

| Figure 5.1: Variation in maximum heat dissipation capacity ( $\circ$ Experiment, — Model) with ambient temperature for the conventional passive system ( $r_c = 1$ ) at $T_{chip} = \text{ of } 85 \text{ °C}$ .                                                                                                                                                             |  |  |

| Figure 5.2: Variation in maximum heat dissipation capacity with ambient temperature for only TEC system ( $r_c = 0$ ) off condition at $T_{chip} = \text{of 85 °C}$ for $\Delta$ open circuit, $\blacktriangle$ short circuit and — — open circuit model prediction                                                                                                          |  |  |

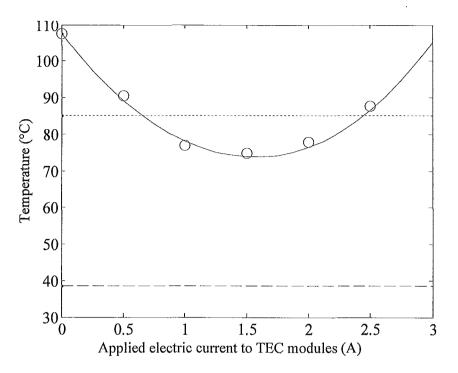

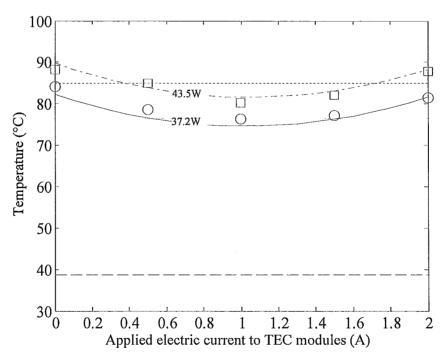

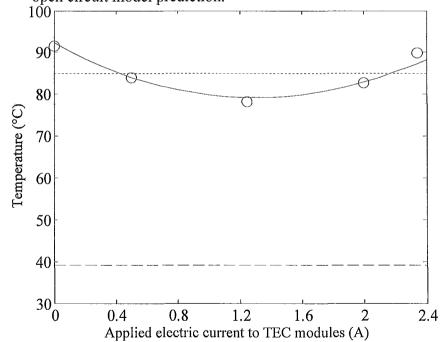

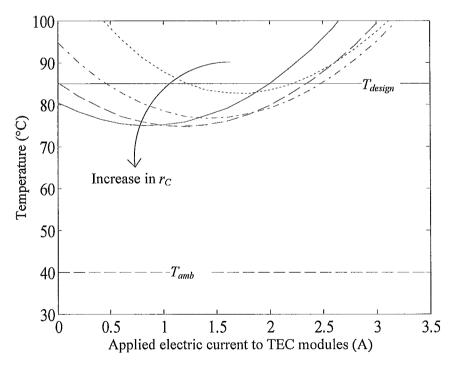

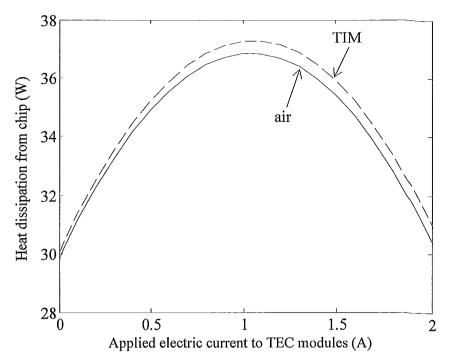

| Figure 5.3: Effect of applied current on chip temperature ( $\circ$ Experiment, — Model) for only TEC system ( $r_c = 0$ ) at $Q_{chip} = 30$ W and $- T_{amb} = 38.5$ °C. ( $T_{design} = 85$ °C) 81                                                                                                                                                                        |  |  |

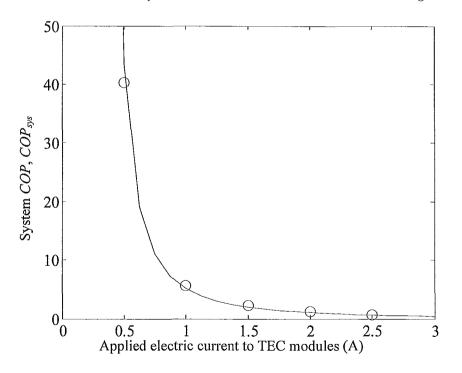

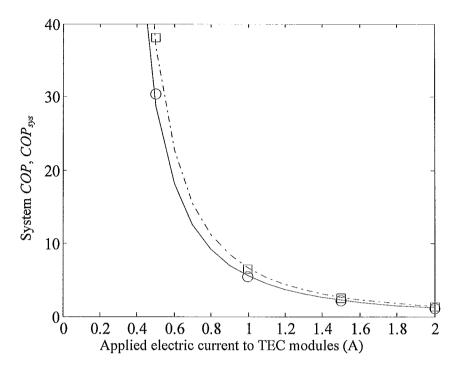

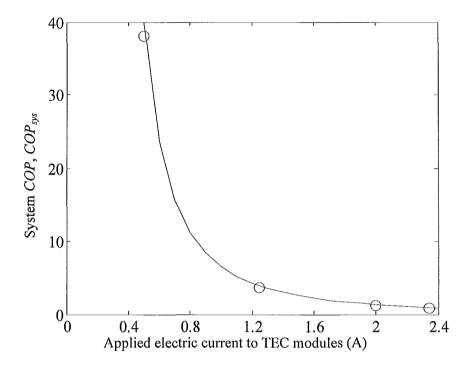

| Figure 5.4: Effect of applied current on the system <i>COP</i> ( $\circ$ Experiment, — Model) for only TEC system ( $r_C = 0$ ) at $Q_{chip} = 30$ W and $T_{amb} = 38.5$ °C                                                                                                                                                                                                 |  |  |

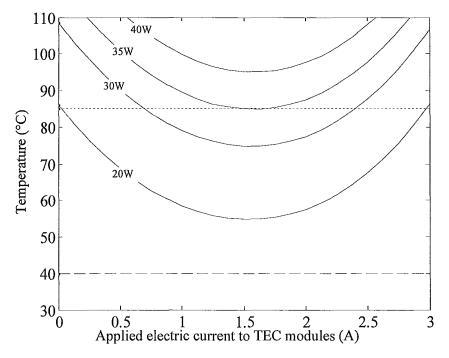

| Figure 5.5: Model prediction of chip temperature at different heat loads from chip and different applied currents for only TEC system ( $r_c = 0$ ). — $T_{chip}$ , $T_{design}$ (85 °C) and — $T_{amb}$ (40 °C)                                                                                                                                                             |  |  |

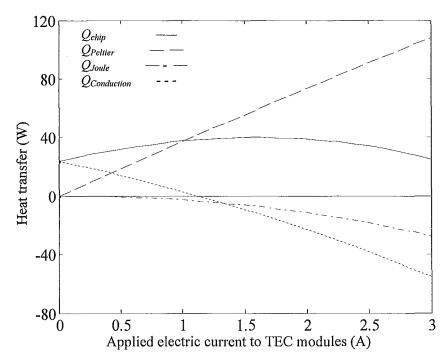

| Figure 5.6: Peltier effect, Joule heating and conduction in a TEC module at $T_{amb} = 30$ °C and $T_{chip} = 85$ °C                                                                                                                                                                                                                                                         |  |  |

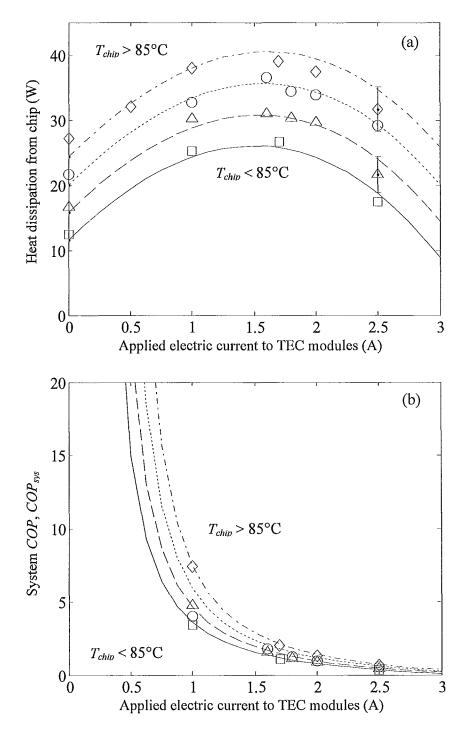

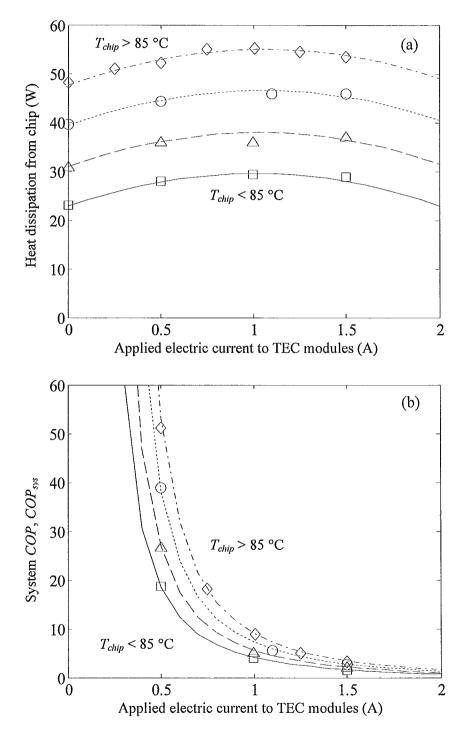

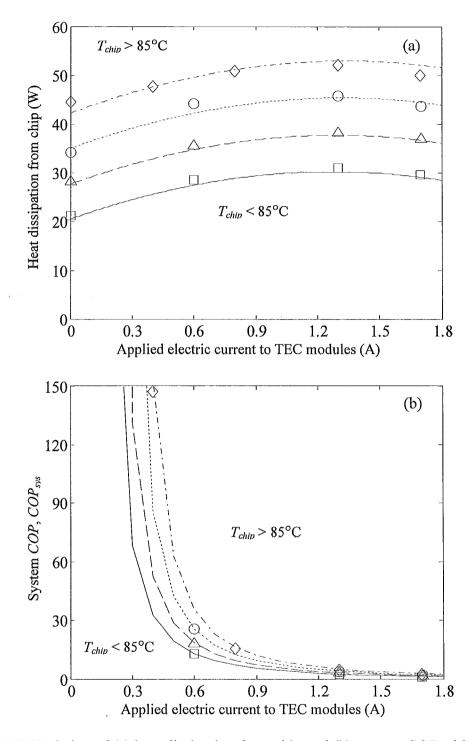

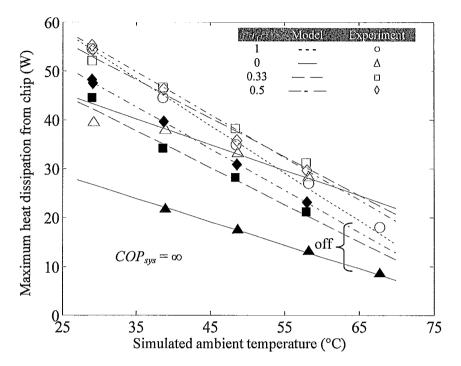

| Figure 5.7: Variation of (a) heat dissipation from chip and (b) system <i>COP</i> with applied current at $T_{amb} = 29 \text{ °C}$ ( $\diamond$ Experiment, — – Model), 38.9 °C ( $\diamond$ Experiment, – – Model), 48.6 °C ( $\triangle$ Experiment, — – Model) and 58.2 °C ( $\Box$ Experiment, — Model) for only TEC system ( $r_C = 0$ ) at $T_{chip} = 85 \text{ °C}$ |  |  |

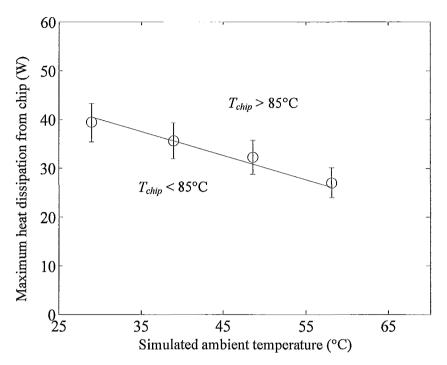

| Figure 5.8: Variation in maximum heat dissipation capacity ( $\circ$ Experiment, —— Model) with ambient temperature for only TEC system ( $r_c = 0$ ) on condition at $T_{chip} = 85$ °C 86                                                                                                                                                                                  |  |  |

| Figure 5.9: Variation in maximum heat dissipation capacity with ambient temperature for hybrid system with $r_C = 0.5$ off condition at $T_{chip} = 85$ °C for $\Box$ open circuit, $\blacksquare$ short circuit and — - — open circuit model prediction                                                                                                                     |  |  |

| Figure 5.10: Effect of applied current on chip temperature for hybrid system with $r_C = 0.5$<br>at $Q_{chip} = 37.2$ W ( $\circ$ Experiment, — Model) and 43.5 W ( $\Box$ Experiment, — - Model) at<br>— $T_{amb} = 38.6$ °C. ( $T_{design} = 85$ °C)                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Figure 5.11: Effect of applied current on system <i>COP</i> for hybrid system with $r_c = 0.5$ at $Q_{chip} = 37.2$ W ( $\circ$ Experiment, — Model) and 43.5 W ( $\Box$ Experiment, — - Model) at $T_{amb} = 38.6$ °C                                                                                                                                                        |  |  |

| Figure 5.12: Variation of (a) heat dissipation from chip and (b) system <i>COP</i> with applied current at $T_{amb} = 29 \text{ °C}$ ( $\diamond$ Experiment, — – Model), 38.6 °C ( $\diamond$ Experiment, – – Model), 48.5 °C ( $\diamond$ Experiment, — Model) and 58 °C ( $\Box$ Experiment, — Model) for hybrid system with $r_C = 0.5$ and at $T_{chip} = 85 \text{ °C}$ |  |  |

| Figure 5.13: Variation in maximum heat dissipation capacity ( $\circ$ Experiment, —— Model) with ambient temperature for hybrid system with $r_C = 0.5$ on condition at $T_{chip} = 85$ °C 93                                                                                                                                                                                 |  |  |

| Figure 5.14: Variation in maximum heat dissipation capacity with ambient temperature for hybrid system with $r_C = 0.33$ off condition at $T_{chip} = 85$ °C for $\circ$ open circuit, $\bullet$ short circuit and — open circuit model prediction                                                                                                                            |  |  |

| Figure 5.15: Effect of applied current on chip temperature ( $\circ$ Experiment, — Model) for hybrid system with $r_C = 0.33$ at $Q_{chip} = 40$ W at — $T_{amb} = 39.1$ °C. ( $T_{design} = 85$ °C).                                                                                                                                                                         |  |  |

| Figure 5.16: Effect of applied current on system <i>COP</i> ( $\circ$ Experiment, — Model) for hybrid system with $r_C = 0.33$ at $Q_{chip} = 40$ W at $T_{amb} = 39.1$ °C                                                                                                                                                                                                    |  |  |

| Figure 5.17: Variation of (a) heat dissipation from chip and (b) system <i>COP</i> with applied current at $T_{amb} = 29 \text{ °C}$ ( $\diamond$ Experiment, — - Model), 38.6 °C ( $\diamond$ Experiment, Model), 48.3 °C ( $\triangle$ Experiment, — Model) and 57.9 °C ( $\Box$ Experiment, — Model) for hybrid system with $r_C = 0.33$ and at $T_{chip} = 85 \text{ °C}$ |  |  |

| Figure 5.18: Variation in maximum heat dissipation capacity ( $\circ$ Experiment, — Model) with ambient temperature for hybrid system with $r_C = 0.33$ on condition at $T_{chip} = 85$ °C. 99                                                                                                                                                                                |  |  |

| Figure 5.19: Effect of applied current on chip temperature for different system configurations of $ r_C = 0, r_C = 0.2, r_C = 0.4$ and $ r_C = 0.6$ at $Q_{chip} = 36$ W and $ T_{amb} = 40$ °C. ( $T_{design} = 85$ °C)                                                                                                                                                      |  |  |

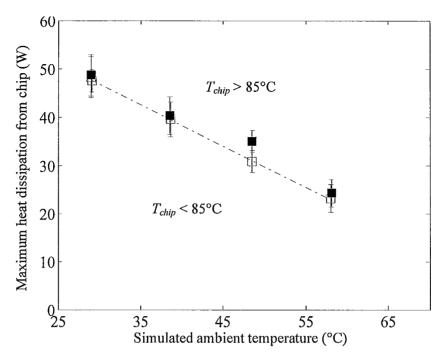

| Figure 5.20: Variation in maximum heat dissipation capacity with ambient temperature at $T_{chip} = 85$ °C with TEC on (open symbols for Experiment and black lines for Model prediction) and off (filled symbols for Experiment and gray lines for Model prediction).                                                                                                        |  |  |

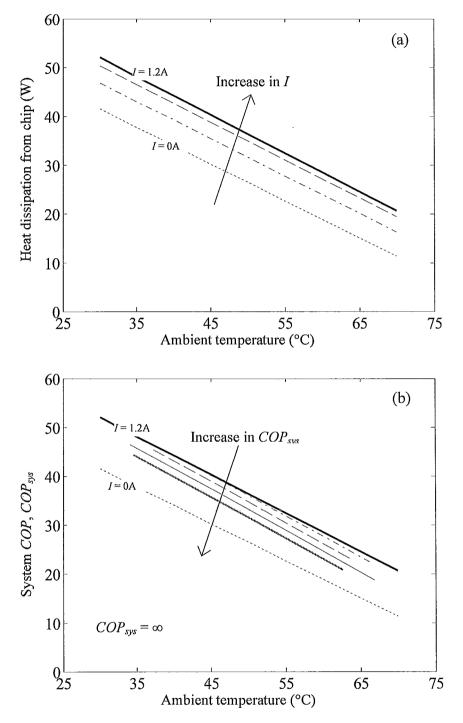

| Figure 5.21:(a) Applied current contours of $I =0$ A, $0.4$ A, $0.8$ A, $1.2$ A and $1.6$ A and (b) corresponding system <i>COP</i> contours of $COP_{sys} =5$ , $10$ , $20$ and $50$ at different heat loads and ambient temperatures for only TEC system ( $r_C = 0$ ) at $T_{chip} = 85$ °C                                                                 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

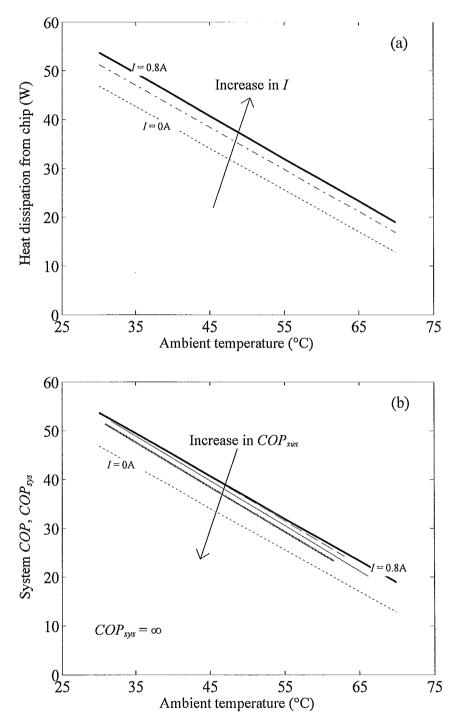

| Figure 5.22: (a) Applied current contours of $I =0$ A, $0.4$ A, $0.8$ A and $1.2$ A and (b) corresponding system <i>COP</i> contours of $COP_{sys} =5$ , $10$ , $20$ and $50$ at different heat loads and ambient temperatures for hybrid system with $r_C = 0.33$ at $T_{chip} = 85$ °C                                                                       |  |  |

| Figure 5.23: (a) Applied current contours of $I =0$ A, $0.4$ A and $0.8$ A and (b) corresponding system <i>COP</i> contours of $COP_{sys} =10$ , $20$ and $50$ at different heat loads and ambient temperatures for hybrid system with $r_C = 0.5$ at $T_{chip} = 85$ °C                                                                                       |  |  |

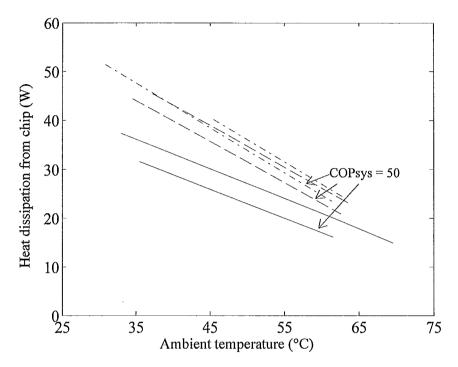

| Figure 5.24: System <i>COP</i> contours at different heat loads and ambient temperatures for — $r_C = 0, r_C = 0.33$ and $ r_C = 0.5$ at $T_{chip} = 85$ °C (black lines for $COP_{sys} = 50$ and gray lines for $COP_{sys} = 10$ )                                                                                                                            |  |  |

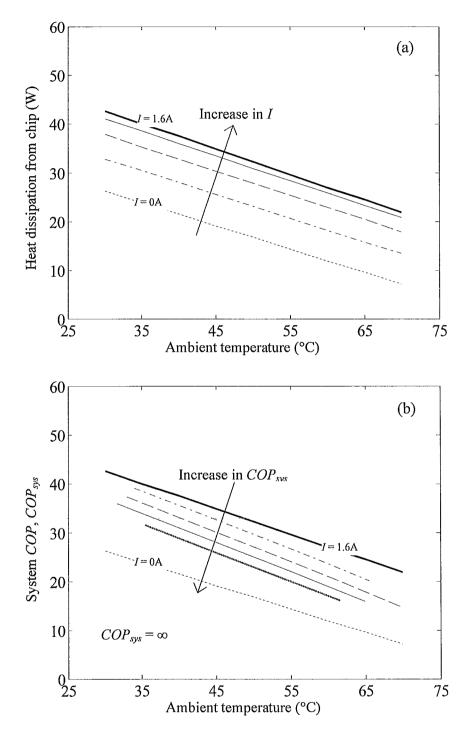

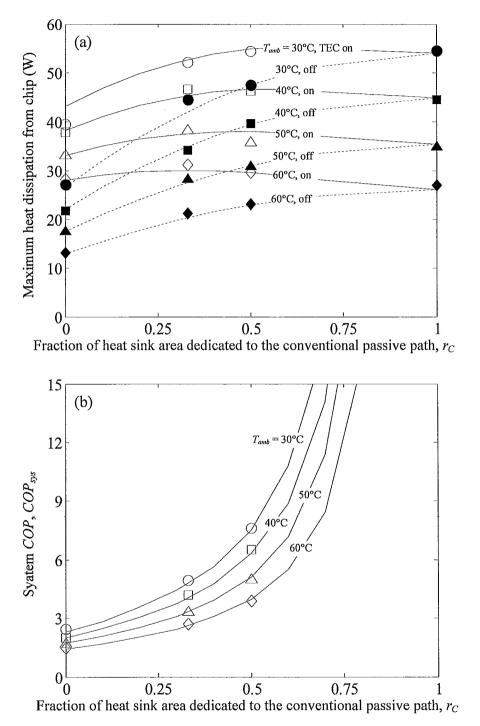

| Figure 5.25: Variation of (a) maximum heat dissipation capacity and (b) corresponding system <i>COP</i> with $r_C$ at $T_{amb} = 0.30$ , $\Box 40$ , $\Delta 50$ and $\diamond 60$ °C. Symbols (open for TEC on and filled for TEC off) represent experimental results and lines (solid for TEC on and dashed for TEC off) represent model predictions. 110    |  |  |

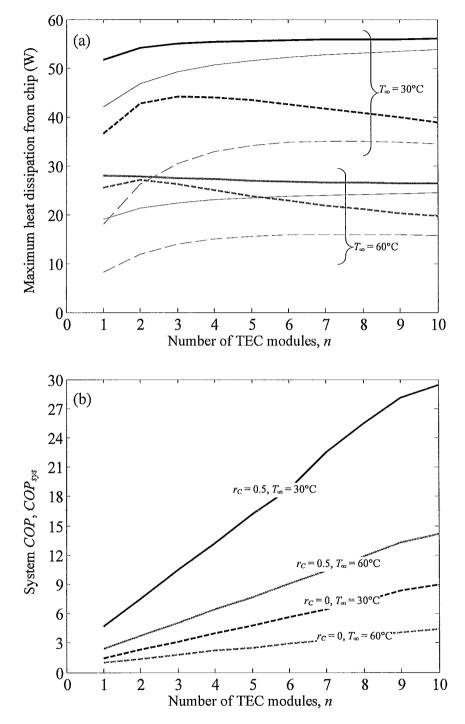

| Figure 5.26: Effect of number of TEC modules on (a) maximum heat dissipation capacity<br>and (b) corresponding system <i>COP</i> for $r_C = 0$ (dashed lines) and 0.5 (solid lines) at $T_{amb} =$<br>30 °C (black lines) and 60 °C (gray lines) from the model prediction at $T_{chip} = 85$ °C for<br>TEC on (bold Lines) and off (regular lines) conditions |  |  |

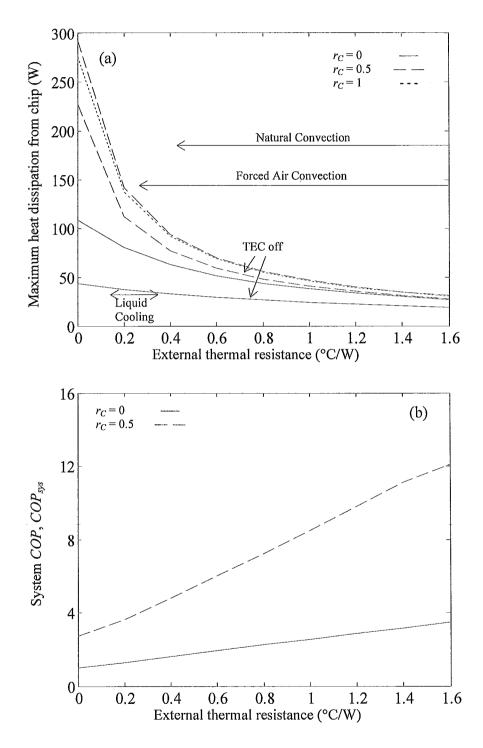

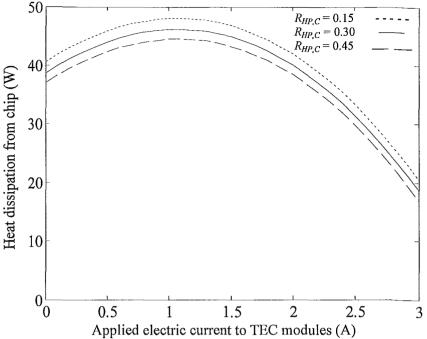

| Figure 5.27: Effect of external thermal resistance on (a) maximum heat dissipation capacity and (b) corresponding system <i>COP</i> from the model for TEC on (black lines) and off (gray lines) conditions at $T_{amb} = 30$ °C and $T_{chip} = 85$ °C                                                                                                        |  |  |

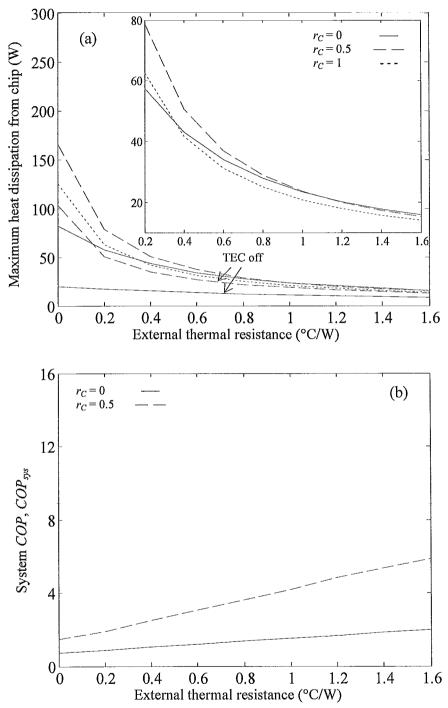

| Figure 5.28: Effect of external thermal resistance on (a) maximum heat dissipation capacity and (b) corresponding system <i>COP</i> from the model for TEC on (black lines) and off (gray lines) conditions at $T_{amb} = 60$ °C and $T_{chip} = 85$ °C                                                                                                        |  |  |

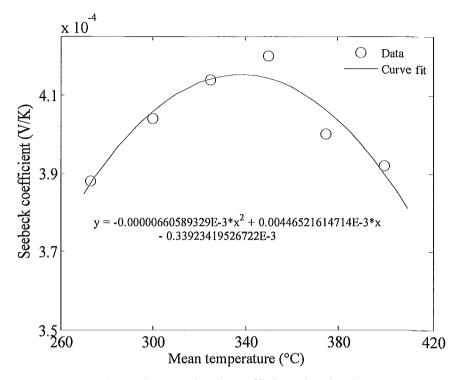

| Figure A.1: Temperature dependent Seebeck coefficient (Melcor)                                                                                                                                                                                                                                                                                                 |  |  |

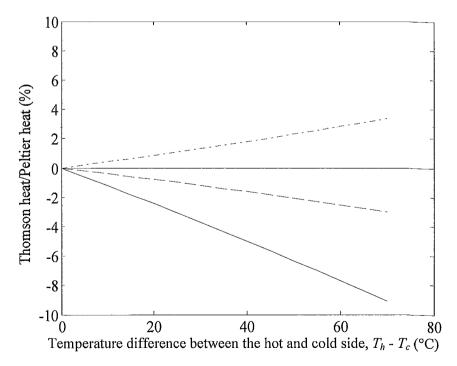

| Figure A.2: Thomson to Peltier heat transfer ratio for a range of temperature difference between the hot and cold side of the TEC modules at mean temperature of — – 325 K (52 °C), — — 350 K (77 °C) and — 375 K (102 °C)                                                                                                                                     |  |  |

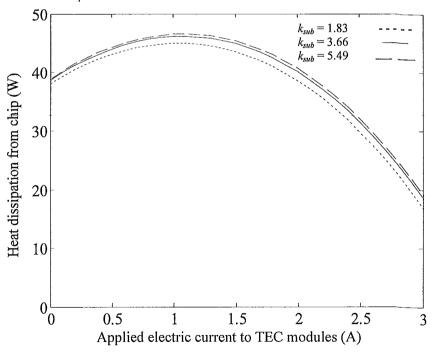

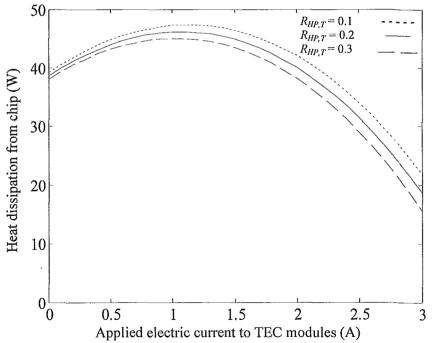

Figure B.4: Effect of the thermal resistance of the heat pipe unit in the TEC based active path on heat dissipation from chip at different applied current at  $T_{amb} = 40$  °C for hybrid system with  $r_C = 0.5$  and at  $T_{chip} = 85$  °C.

## NOMENCLATURE

| Symbols         |                                                                   |

|-----------------|-------------------------------------------------------------------|

| Ă               | Cross-sectional area, surface area (m <sup>2</sup> )              |

| $C_p$           | Specific heat of water $(JKg^{-1}K^{-1})$                         |

| ĊOP             | Coefficient of performance                                        |

| g               | Direction of gravity force                                        |

| G               | Geometric factor (m)                                              |

| h               | Heat transfer coefficient (Wm <sup>-2</sup> K <sup>-1</sup> )     |

| Ι               | Applied electric current (A)                                      |

| k               | Thermal conductivity $(Wm^{-1}K^{-1})$                            |

| K               | Thermal conductance (WK <sup>-1</sup> )                           |

| L               | Length (m)                                                        |

| •               | Magg flow up to of water (V a/a)                                  |

| т               | Mass flow rate of water (Kg/s)                                    |

| n               | Number of TEC modules                                             |

| Ν               | Number of thermo-couples in a TEC module                          |

| P <sub>in</sub> | Input power to TEC (W)                                            |

| Q               | Heat load, transfer, flow (W)                                     |

| $r_C$           | Fraction of heat sink area dedicated to conventional passive path |

| R               | Thermal resistance (°C/W)                                         |

| R <sub>el</sub> | Electric resistance of one thermo-couple ( $\Omega$ )             |

| t               | Thickness, length (m)                                             |

| T               | Temperature (°C, K)                                               |

| u'''            | Energy generation per unit volume (W/m <sup>3</sup> )             |

| V               | Voltage (V)                                                       |

| x               | Spatial co-ordinate                                               |

| Δ               | Différence                                                        |

|                 |                                                                   |

| <b>Greek Symbols</b> |                                                                                                                                                    |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| α                    | Seebeck coefficient of one thermo-couple (V/K)                                                                                                     |

| η                    | Charge carrier concentration (cm <sup>-3</sup> )                                                                                                   |

| π                    | Peltier constant of one thermo-couple (V)                                                                                                          |

| ρ                    | Electrical resistivity of n or p-type thermo-element ( $\Omega$ .m)                                                                                |

| σ                    | Electrical resistivity of n or p-type thermo-element ( $\Omega$ .m)<br>Electrical conductivity (Sm <sup>-1</sup> = $\Omega^{-1}$ m <sup>-1</sup> ) |

| τ                    | Thomson constant (V/K)                                                                                                                             |

#### Subscripts

| amb | Ambient   |

|-----|-----------|

| С   | Cold side |

| chip     | Chip                                  |

|----------|---------------------------------------|

| C        | Conventional passive path             |

| design   | Design value of chip                  |

| fin      | Finned heat sink                      |

| ĥ        | Hot side                              |

| HP       | Heat pipe                             |

| i        | Inlet, iteration number               |

| in       | Inside, input                         |

| max      | Maximum                               |

| mean     | Mean, average                         |

| min      | Minimum                               |

| n        | n-type semiconductor                  |

| 0        | Outlet                                |

| opt      | Optimum                               |

| out      | Outside, output                       |

| p        | p-type semiconductor                  |

| Р        | Peltier effect                        |

| sub      | Substrate                             |

| sys      | System                                |

| tot      | Total                                 |

| T        | TEC based active path, Thomson effect |

| TE       | Thermo-element                        |

| TEC      | Thermo-electric cooler                |

| $\infty$ | Ambient, infinity                     |

|          |                                       |

#### **Chapter 1 INTRODUCTION**

Since the advent of the Integrated Circuit (IC) by Kilby at Texas Instruments and Noyce at Fairchild Semiconductors in 1959 (Hanson, 1982), the packaging density of electronics has continued to increase. Over the last decade electronic circuitry has significantly been improved in terms of miniaturization. This is particularly evident in microprocessors where the number of micro transistors on a single die has increased from  $10^6$  to  $10^9$ . As a result, more electrical energy is required to make them functional with a resultant increase in heat dissipation. Multi-core microprocessors are projected to dissipate a heat flux ranging from 10 to 50 W/cm<sup>2</sup> while power electronics or laser semiconductors are projected to dissipate over 100 W/cm<sup>2</sup> of heat flux (DTI report, 2006). For example, heat dissipation from a high performance single chip is predicted to be 183 W by 2014 (Phelan et al., 2002). Processors must operate below its safe design temperature which is typically 100 °C (DTI report, 2006), beyond which permanent failure may occur. The safe design temperature of the chip is not expected to increase in the electronics industry to keep pace with the increasing trend of the chip rated power (Krueger and Bar-Cohen, 2004). Over-heating of the chip can drastically deteriorate the chip performance and shorten its lifetime (Kock and Visser, 2004). The reliability of the chip was found to decrease by 10% for every 2 °C increase above its safe design temperature (Bar-Cohen et al., 1983).

Thermal management of the electronic packages at elevated ambient temperature is becoming a challenge for thermal designers. Several cooling techniques have been developed to dissipate more heat from a chip and to maintain the functionality of the electronic packages. These cooling methods are usually limited by several factors such as size, shape and form factor of the packaging. One commonly used cooling method for electronic packaging is forced convection air cooling with extended surface heat sinks. In typical computers, fans are used to force air past a finned heat sink to remove heat from the chip and other fans to move cool air into and hot air out of the case (Saini and Webb, 2003). Such solutions, however, can be inadequate when the electronic packaging is operated in a high temperature ambient environment or if high performance chips are used in the packaging. Liquid cooling has been proposed for high heat dissipation rates from the chip. Zhang et al. (2003) reported a heat dissipation of 140 to 170 W using liquid cooling through a miniaturized aluminum heat sink with micro channels.

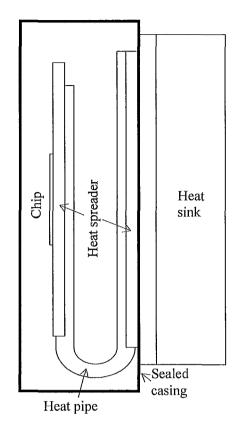

There are other applications such as sealed computers (Figure 1.1) where fans cannot be used to move fresh air in or hot air out of the case because of the nature of the casing. The cooling system in this computer typically consists of a heat pipe unit that transports the heat from the heat generating components to the finned case wall. The fins on the outside of the case allow the heat to be dissipated to the surroundings via natural convection. Sealed computers are used for specific purposes such as in industrial

Figure 1.1: Schematic of a sealed computer.

environments where contaminant particles can accumulate on sensitive electronic components, in special vehicles such as police cars, military vehicles and coast guard ships. In such applications, refrigeration cooling using thermoelectric coolers (TEC) have been adopted to keep the chip temperature below its design point. Thermoelectric coolers (TEC) are an attractive option in such instances, and have been developed and used for thermal management in electronic packaging systems for years. B eing a solid state device, it overcomes the orientation effect of heat pipes (Loh et al., 2005, Russel et al., 2011) and provides high reliability (Riffat and Ma, 2003) and control in cooling the chip. Its smaller size and weight, noise free operation, absence of any moving parts make it advantageous over other cooling methods.

#### M.A.Sc. Thesis – M. K. Russel McMaster University – Department of Mechanical Engineering

Typically, the cold side of the thermoelectric cooler (TEC) is in contact with the chip to maintain the chip temperature below its design temperature with natural or forced convection at the hot side of the TEC to transport the heat from the chip and the applied power to the TEC module to the ambient. The heat load from the processor will typically fluctuate over time and will depend on its operation. At moderate processor heat load and moderate ambient temperatures, a passive thermal management system such as use of heat pipes would be sufficient to transport the heat from the chip to the ambient. However, at high ambient temperatures or high heat load, such a system may fail to maintain the chip below its safe operating temperature. If only a TEC based system is used in this circumstance, the TEC module will have to be kept electrically on even at moderate operating conditions because of its high thermal resistance at the electrically off mode which would result in a low system coefficient of performance ( $COP_{sys}$ ).

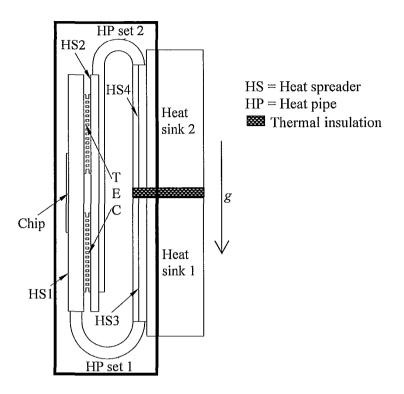

The objective of this research is to develop a hybrid thermal management system that incorporates a TEC based active path in parallel with a conventional heat pipe based passive path (Figure 1.2). The passive path consists of a heat pipe unit and a finned heat sink where the TEC based active path consists of TEC module(s), a heat pipe unit and a second finned heat sink. The two heat sinks associated with the two parallel paths are thermally isolated from each other. The proposed hybrid system utilizes the passive path at moderate heat loads at moderate ambient conditions while at higher ambient temperatures or high processor heat loads, the thermoelectric cooler will be electrically turned on with the necessary amount of current to keep the chip temperature below its safe operating temperature. Use of this hybrid system will improve the performance of the system in two

Figure 1.2: Schematic of the hybrid thermal management system.

ways: (a) the operating envelope will be extended at higher ambient temperature and (b) the  $COP_{sys}$  will be improved compared to an only TEC based thermal management system. A thermal resistance network model is developed for the hybrid system that takes into account the governing equations of the TEC modules. An experimental facility was developed to simulate different practical conditions for the hybrid system and to validate the predictions of the thermo-physical model.

This thesis is divided into six chapters. Chapter 2 provides background on thermoelectric cooler (TEC) modules, their operating principles, different studies performed previously on TEC systems and finally natural and forced convection at the heat sink. The modeling of the proposed hybrid system is presented in Chapter 3. Chapter 4 outlines the experimental set up and methodology used for the experiments. The results of the experimental findings are presented and discussed in Chapter 5. The model predictions are compared with the experimental results. Chapter 6 summarizes the work and provides recommendations for continuation of this project. The appendix of the thesis contains information on the thermo-physical properties of the TEC material and different parametric studies.

# **Chapter 2 LITERATURE REVIEW**

There are several methods of cooling electronic packaging depending on the application. The cooling techniques can be classified broadly into two classes: (i) Passive and (ii) Active techniques. Passive techniques can be defined as those where no external power is required for cooling the electronic packages where active techniques require external power to cool the electronics (Baily, 2008). There are three scales of cooling for computer products: (i) Module level cooling, (ii) System Cooling and (iii) Data centre cooling (Chu et al., 2004). Module level cooling refers to cooling the chip, system level cooling refers to the entire electronic package and data centre cooling refers to cooling the rooms where computers and telecommunications equipment are stored. The research in this project will focus on the system level cooling using a hybrid thermal management system which involves thermoelectric cooler (TEC) modules, heat pipes and an air cooled heat sink. The components of the hybrid system along with other cooling techniques, both active and passive, adopted in electronics cooling are reviewed in the following sections.

#### 2.1. THERMOELECTRIC COOLER (TEC)

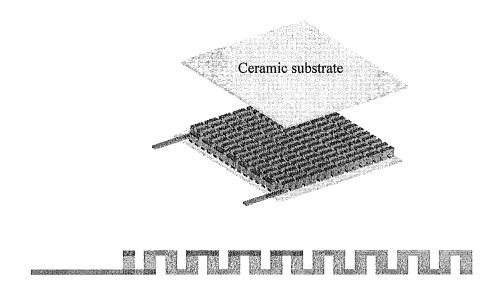

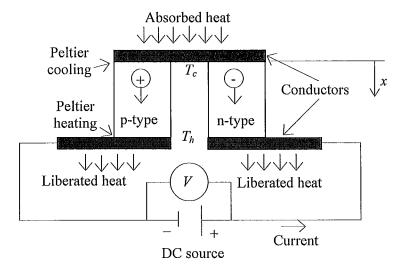

A typical thermoelectric module consists of a number of thermocouples sandwiched between two layers of ceramic substrates. The ceramic substrates should ideally have a very high thermal conductivity so that there is minimal temperature drop across the layer of the substrate but very low electrical conductivity to avoid any leakage current flow through the substrate. A schematic of the construction of a typical TEC module is shown in Figure 2.1. Detailed descriptions of thermoelectric module operation and applications can be found in Ioffe (1957), Gray (1961), Goldsmid (1961). Thermoelectric cooling is achieved with the penalty of DC current supply through one or a series of thermocouples electrically connected in series but thermally in parallel. The schematic of a single thermocouple which consists of one n and one p-type semiconductor material, also known as a thermo-element with its operating principle is shown in Figure 2.2. In the n and p type semiconductors there exist excess electrons and holes respectively. With the electric polarity shown in Figure 2.2, electrons in p and n-type material flow from bottom to top and from top to bottom respectively, thus resulting in a clockwise electron flow or counter clockwise current flow through this circuit. Heat is absorbed at the top and released at the bottom of the schematic shown in Figure 2.2. If the polarity is changed, the hot and cold junction as well as the heat absorption and rejection will interchange. There are three important thermoelectric effects that have been known since the nineteenth century: (i) Seebeck effect, (ii) Peltier effect and (iii) Thomson effect.

Seebeck in 1821 discovered that, when a temperature difference is maintained at the two junctions of a thermocouple composed of two dissimilar conductors, a voltage is

Figure 2.1: Schematic of a typical thermoelectric module.

Figure 2.2: Schematic of thermoelectric module operation.

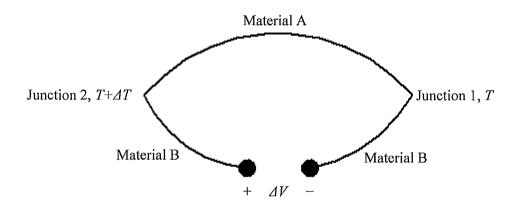

generated at the two terminals of the thermocouple as shown in Figure 2.3. The generated voltage is proportional to the temperature difference between the junctions and leads to the definition of the Seebeck coefficient,  $\alpha_{AB}$  as

$$\alpha_{AB}(T) = \frac{\Delta V}{\Delta T}$$

2.1

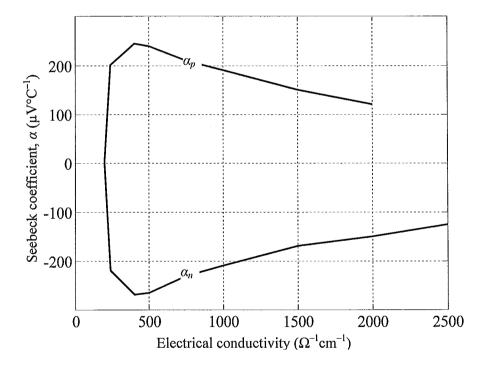

The Seebeck coefficient depends on the materials A and B. A couple in a thermoelectric module is made of one n and one p-type semiconductor where the Seebeck coefficient  $a_{pn}$  is expressed as  $a_{pn} = \alpha = \alpha_p - \alpha_n$ . Here  $\alpha_p$  and  $\alpha_n$  are the absolute Seebeck coefficient of p and n-type semiconductor respectively with respect to a superconductor (having zero Seebeck coefficient). Goldsmid (1961) presented Seebeck coefficients of n and p type bismuth telluride (Bi<sub>2</sub>Te<sub>3</sub>) at room temperature as a function of electrical conductivity which is reproduced in Figure 2.4.

The concentration of the charge carriers (electrons in n and holes or protons in p type semiconductors) depends upon the temperature. When there is a temperature gradient, negative charge carriers or electrons in n and positive charge carriers or holes in p-type semiconductors flow from the hot junction to the cold junction and thus produces an electron flow through the circuit when shorted and a voltage at open circuit condition.

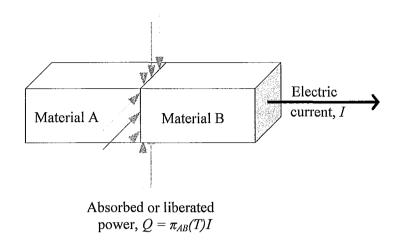

Peltier in 1834 observed that, when an electric current flows through a junction composed of two dissimilar materials heat is either absorbed from the surrounding or dissipated to the surrounding at the junction as shown in Figure 2.5. The amount of heat absorbed or liberated at the junction is directly proportional to the electric current, *I* and related as

10

Figure 2.3: Schematic of basic thermocouple demonstrating Seebect effect (Gray, 1961).

Figure 2.4: Seebeck coefficient of Bi<sub>2</sub>Te<sub>3</sub> at room temperature (Goldsmid, 1961).

$$Q = \pi_{AB}(T)I \tag{2.2}$$

where  $\pi_{AB}(T)$  is the temperature dependent proportionality constant and known as Peltier constant. The Peltier constant is related to the Seebeck coefficient as

$$\alpha_{AB} = \frac{\pi_{AB}}{T}$$

2.3

where T is the absolute temperature of the junction.

The potential energy of the charge carriers in different materials is different. The Peltier effect occurs at the junctions due to the difference in the energy levels in two dissimilar materials. For the polarity shown in Figure 2.2, at the cold junction heat is absorbed by the electrons as they move from a low energy level in the p-type to a high energy level in the n-type semiconductor. This consequently causes the holes in the p-type semiconductor to move in the opposite direction of the electron flow, i.e. toward the hot end. The electrons in the n-type semiconductor also move toward the hot end. Both the electrons and the holes carry thermal energy. So, the result is a net flow of heat from the cold end to the hot end where the heat is rejected due to the difference in energy levels.

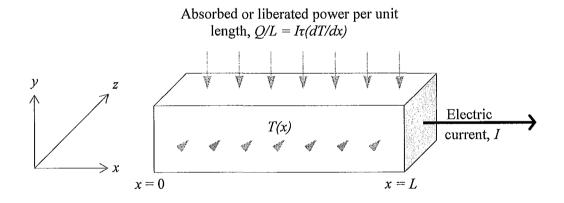

Thomson in 1857 observed that when an electric current flows through a single homogeneous conductor in the presence of a temperature gradient in that conductor, the conductor exchanges energy with the surrounding. This phenomenon is illustrated in Figure 2.6. The direction of energy interchange between the conductor and the surrounding will depend on the direction of the temperature gradient and the direction of charge carrier in the conductor. The amount of heat absorbed or dissipated per unit length of the conductor is proportional to the current and the temperature gradient and is expressed as

Figure 2.6: Schematic illustrating Thomson effect (Gray, 1961).

$$\frac{Q}{L} = I\tau \frac{dT}{dx}$$

2.4

where  $\tau$  is the Thomson coefficient which is related to the Seebeck coefficient as

$$\frac{d\alpha}{dT} = \frac{\tau}{T}$$

2.5

The Thompson effect is reported as a second order effect in thermoelectric cooling as the heat flow due to this effect depends upon the product of the current and the temperature gradient (Gray, 1961). The Thomson effect has also been reported to be small (Ioffe, 1957, Goldsmid, 1961, Soo, 1968) and thus usually neglected in thermoelectric cooling or heating. The manufacture's specification (Melcor) of the thermo-element was used to determine the importance of the Thomson effect and is described in APPENDIX A. It was found that the heat transfer due to the Thomson effect is an order of magnitude smaller than the Peltier cooling effect and thus neglected in this study.

There are three major phenomena in a thermocouple shown in Figure 2.2 when the Thompson effect is neglected. They are:

- (i) Reversible Peltier cooling and heating at the cold and hot junction respectively.

- (ii) Irreversible thermal conduction along the temperature gradient.

- (iii) Irreversible Joule heating.

The thermal conduction and the Joule heating oppose the cooling due to the Peltier effect in a thermo-couple. To achieve a higher cooling performance at the cold junction, a higher Seebeck coefficient ( $\alpha$ ), lower thermal conductance (K) or conductivity (k) and lower electrical resistance ( $\rho$ ) or higher electrical conductivity ( $\sigma = 1/\rho$ ) of the thermo-element is favorable. Combining these parameters, a figure of merit which describes the quality of the thermocouple is expressed as (Ioffe, 1957)

$$z = \frac{\alpha^2 \sigma}{k}$$

2.6

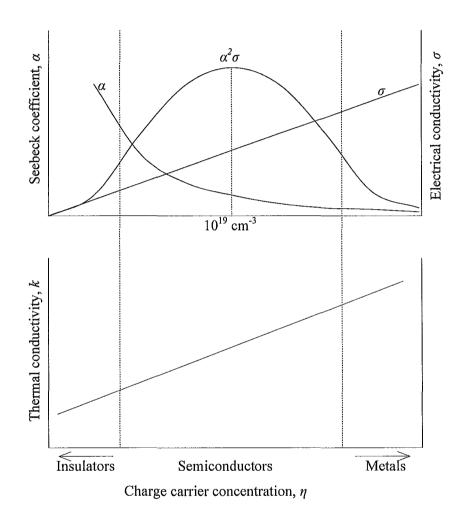

The three parameters, Seebeck coefficient  $\alpha$ , thermal conductivity k and electrical conductivity  $\sigma$  are all functions of charge carrier concentration (free electrons or holes),  $\eta$ . The relationship between the charge carrier concentration and these three properties of thermo-element is shown qualitatively by Ioffe (1957) and reproduced in Figure 2.7. The thermal and electrical conductivity is proportional to the carrier concentration,  $\eta$  while the Seebeck coefficient decreases nonlinearly with an increase in carrier concentration. The value of  $\alpha^2 \sigma$  approaches a maximum for a carrier concentration of the order of  $10^{19}$  cm<sup>-3</sup>, which is approximately 1000 times smaller than the free electron concentration in metals (Ioffe, 1957). The value of z is small for insulators due to their very low electric conductivity ( $\sigma$ ) and for metals due to a very low Seebeck coefficient ( $\alpha$ ). This explains why thermoelectric modules were not feasible until the discovery of semiconductors.

The figure of merit of a thermocouple limits the maximum achievable temperature difference ( $\Delta T_{max}$ ) between the hot and the cold junctions whereas the cross sectional area to the length ratio of the n or p-type thermo-element, which is generally known as geometric factor,  $G = A_{TE} / t_{TE}$  defines the heat pumping capacity. The most widely used thermoelectric material for refrigeration is a binary alloy, (Bi,Sb)<sub>2</sub>(Te,Se)<sub>3</sub>, commonly known as bismuth telluride (Guyer, 1988).

15

Figure 2.7: Effect of charge carrier concentration on the components of figure of merit (Ioffe, 1957).

Conventional thermoelectric modules can have various specifications in terms of their geometry, number of thermocouples and power rating for various applications. These devices can be cascaded to achieve a higher temperature differential across the entire thickness. Different applications of thermo-electric modules for (i) cooling, ranging from consumer products to military or aerospace applications, (ii) power generation, e.g. waste heat recovery (iii) sensors such as cryogenic heat flux sensor, ultrasonic intensity sensor, fluid flow sensor, infrared sensor are reviewed by Riffat and Ma (2003).

A number of investigations have been performed for geometric optimization of thermo-elements in a TEC to achieve better cooling capacity and coefficient of performance (Cheng and Lin, 2005, Fukutani and Shakouri, 2006, Hodes, 2007). The maximum cooling capacity improved for an increment in the cross sectional area of the thermo-element or a decrement in the length. The maximum achievable *COP*, irrelevant of the maximum cooling capacity, remained constant for any change in the area or the length of the thermo-element. To develop better thermo-element materials to achieve a higher figure of merit, several studies were performed by Venkatasubramanian et al. (2001) and Polvani et al. (2001). Venkatasubramanian et al. (2001) demonstrated a doubling in the thermoelectric figure of merit for super-lattice materials.

The physical modeling of thermoelectric devices has been considered in a number of studies e.g., one dimensional differential control volume approach by Hodes (2005) and finite element modeling by Seifert (2001) for the module alone and equivalent electric circuit model by Fukutani and Shakouri (2006), thermal resistance network model by Taylor and Solbrekken (2008), energy balance approach by Zhang et al. (2009) and

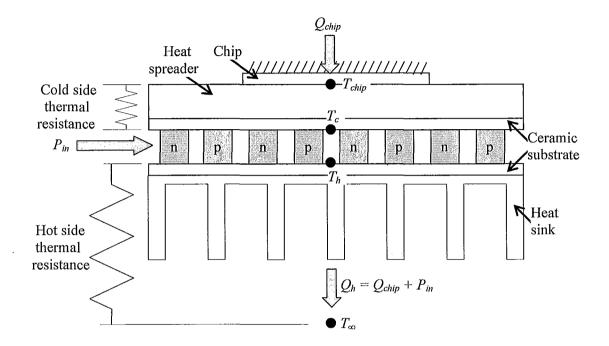

Yamanashi (1996) for a system consisting TEC module(s). Yamanashi (1996) adopted an entropy balance approach to analyze the system and presented both dimensional and non dimensional energy and entropy flow equations. The typical system considered is an only TEC system which consists of a heat source or chip, a cold side thermal resistor (from the chip to the cold side of the module), TEC module(s) and a hot side thermal resistor (from the hot side of the thermoelectric module to the ambient) as shown in Figure 2.8. The performance of TEC based thermal management systems in practical cooling applications has been considered for both forced air (Phelan et al., 2002, Zhang et al., 2009) and liquid (Zhang et al., 2009) cooling applications at the hot side of the system for fixed ambient temperature. The results showed that the chip temperature can be reduced or the heat dissipation from the chip can be improved by using TEC module(s). The hot side thermal resistance had a more significant effect on the performance of a TEC based thermal management system than the cold side thermal resistance at fixed ambient temperature (Phelan et al., 2002, Fukutani and Shakouri, 2006, Yamanashi, 1996). In particular, an increase in the hot side thermal resistance appeared to have an exponential effect on the chip temperature due to the non-linearity caused by the TEC module, while the cold side thermal resistance had a linear effect on the chip temperature. The optimized current and geometry factor used in the model proposed by Fukutani and Shakouri (2006) showed a minimum of 10 °C reduction in chip temperature compared to the model proposed by Phelan et al. (2002) for a range of heat load from the chip. An increase in hot side thermal resistance reduced the range of operating current where the TEC was effective

Figure 2.8: Schematic of a typical thermal management system incorporating TEC module.

(Yamanashi, 1996). This indicates the importance of considering all thermal resistances at the hot side including the hot side ceramic substrate which was ignored by Zhang et al. (2009). An empirical expression was proposed by Huang et al. (2000) for optimizing the performance of a TEC using its bulk properties and to obtain the required hot side thermal resistance. The empirical relation, however, was specific to the TEC module considered and was obtained from the curve fit to the experimental data. The prediction of performance of a TEC based system by Taylor and Solbrekken (2008) and Zhang et al. (2009) was found to be in reasonable agreement with experiments. Taylor and Solbrekken (2008) used temperature dependent thermo-element material properties in their model to predict chip temperature at a fixed heat load with a fixed hot side thermal resistance while Zhang et al. (2009) considered temperature independent properties to minimize chip temperature at fixed heat load and to maximize heat dissipation from chip at fixed chip temperature both at a fixed ambient temperature. Use of temperature dependent properties resulted in better agreement compared to the temperature independent properties (Taylor and Solbrekken, 2008). Thomson effect was neglected in these studies considering its small effect.

The aforementioned TEC based systems were studied to meet the most extreme condition that a thermal management system might experience. In many practical applications, the chip would experience a range of heat loads and/or a wide range of ambient temperatures. One disadvantage of an only TEC based system is that the TEC has a relatively high thermal resistance when it is off. Thus, it would have to be operational even for operating conditions where a conventional thermal management system would be sufficient, which results in a lower overall *COP* (Phelan et al., 2002).

The heat dissipated at the hot side of the TEC module(s) in a TEC based thermal management system are typically cooled by natural or forced air convection. The sealed computer shown in Figure 1.1 has air cooling at the hot side. Air cooled heat sinks are thus further reviewed in the following section.

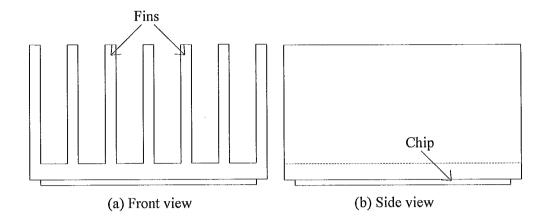

#### **2.2. AIR COOLED HEAT SINKS**

Heat sinks with natural or forced convection air cooling has been used for many years to transport heat from the chip or a TEC module to the ambient. A schematic of typical air cooled heat sink is shown in Figure 2.9. The base plate of the heat sink is in thermal contact with the chip or the hot side of the TEC module and the fins act as extended surface to transport heat to the ambient. Rectangular flat or pin fins (Figure 2.10) are commonly used in cooling electronics. Air flow can either be lateral (duct flow) or can impinge from the top through the passages between the fins (Figure 2.11). The thermal performance of the heat sink depends on many parameters: geometric parameters such as base plate thickness, height, thickness and spacing between the fins; material properties and the number of fins. The orientation of the flat fin heat sink at natural convection also has an effect on thermal performance. Several studies have been performed to optimize a heat sink. Yüncü and Anbar (1998) studied the performance of rectangular fins on a horizontal base plate for natural convection and found that natural convection heat transfer rate improves with increasing fin height for fixed fin spacing and fixed number of fins. A

Figure 2.9: Typical air cooled heat sink.

Figure 2.10: Typical (a) rectangular straight/flat and (b) pin fin heat sink.

Figure 2.11: Air flow through the heat sink (a) duct flow and (b) impingement flow.

dimensionless empirical expression to correlate the natural convection heat transfer as a function of number of fins, fin height and fin spacing was developed. Güvenç and Yüncü (2001) investigated the performance of fins on a vertical base plate for natural convection. The natural convection heat transfer was improved by increasing the fin height and the fin base to ambient temperature difference. Fin spacing was found to have an optimum value at different fin base to ambient temperature differences. A better heat transfer enhancement was obtained with vertically oriented fin arrays than with horizontally oriented ones for the same fin geometry. Yazicioğlu and Yüncü (2007) studied the optimization of rectangular fins on a vertical base plate for natural convection and developed empirical expressions for optimum fin spacing as a function of fin length and Rayleigh number and for the ratio of maximum convection heat transfer rate at vertical orientation with rectangular fin to that of a flat plate with equal base area as a function of Rayleigh number, base to ambient temperature difference, base plate width and fin length. Teertstra et al. (1999) developed a model to predict the heat transfer from fin arrays with forced convection for a plate fin heat sink at duct flow with and without considering the fin efficiency. They experimentally showed that the effect of fin efficiency is an important parameter to be considered in case of high aspect ratio heat sinks (i.e. fin spacing  $\ll$  fin height) which are used for electronic package cooling. Experimental results were in good agreement with the predictions from model. Saini and Webb (2002) developed models for air cooled plane fin heat sinks both for duct and impinging flow to predict convection resistance of the heat sink. Kock and Visser (2004) considered trading-off between heat sink mass and thermal resistance to optimize the heat sink geometry for base plate thickness, fin thickness, height and number of fins at a fixed heat load from the chip for both natural and forced convections for straight fin heat sink. The heat sink thermal resistance decreased with an increase in fin thickness, base plate thickness, number of fins and thus mass of the fin. Maveety and Hendricks (1999) studied the effect of heat sink geometry, material, nozzle to heat sink vertical distance and Reynolds number based on nozzle diameter for air impingement cooling. Ledezma et al. (1996) optimized the pin fin spacing for impingement flow and found that the optimized fin height to base plate length ratio was 0.53 and the optimum fin width to base plate length ratio was 0.1 for a square pin fin. Maveety and Jung (2000) performed a numerical and experimental study to optimize square pin fins with turbulent air impingement.

## **Chapter 3 SYSTEM MODELING**

The hybrid thermal management system considered here consists of two thermally parallel paths: (i) a conventional heat pipe based passive path and (ii) a TEC based active path. The passive path consists of heat pipes and heat spreaders with a finned heat sink and the TEC path consists of two TEC modules with a second set of heat pipes and heat sink as shown in Figure 1.2. An exploded view with the heat transfer through the different elements is shown in Figure 3.1 (a). The TEC modules in the active TEC path are electrically in series but thermally in parallel when more than one module is used. The case considered here is a natural convection cooling system to the ambient through a finned plate. The total finned area is fixed thus the thermal resistance of the total heat sink has a nominal fixed value over a range of operating ambient temperatures. The performance of the thermal management system will thus depend on the portion of the total heat sink area dedicated to each path. This is characterized by  $r_c$ , the fraction of heat sink area dedicated to the conventional passive path. When  $r_c = 0$ , the system is completely active, while when  $r_{C} = 1$ , the system is completely passive which means, in practice the TEC based active path is absent. When  $0 < r_C < 1$ , the system is a hybrid with a portion of the heat transferred M.A.Sc. Thesis – M. K. Russel McMaster University – Department of Mechanical Engineering

Figure 3.1: Hybrid thermal management system (a) exploded view (b) thermal resistance network.

through each path depending on the thermal resistance of the heat sink, operating condition of the chip and ambient,  $r_c$  and the number and operating conditions of the TEC modules.

#### **3.1. MODELING THE HYBRID SYSTEM**

The performance of the hybrid thermal management system is modeled using a thermal resistance network as shown in Figure 3.1 (b). When the TEC is off (i.e. no current supplied to the TEC modules), the mode of heat transfer from the chip to the finned heat sink is through the heat pipes and from the fin plate to the ambient by natural convection.

The governing equations at the TEC off mode are

$$Q_{chip} = Q_C + Q_T \tag{3.1}$$

where

$$Q_C = \frac{T_{chip} - T_{\infty}}{R_C}$$

3.2

and

$$Q_T = Q_h = \frac{T_{chip} - T_{\infty}}{R_T}$$

3.3

Here,  $Q_{chip}$  is the total heat load from the chip to the thermal management system,  $Q_C$  is the heat transported through the conventional path and  $Q_T$  is the heat flow through the TEC based active path. In this case the heat exiting from the TEC ( $Q_h$ ) is the same as  $Q_T$  since the TEC is off.

The thermal resistance of the passive path can be expressed as

$$R_C = R_{HP,C} + R_{\infty,C} \tag{3.4}$$

where

$$R_{\infty,C} = \frac{R_{\infty,tot}}{r_C}$$

3.5

$R_{HP,C}$  is the thermal resistance of the heat pipe unit in the conventional passive path,  $R_{\infty,C}$  is the thermal resistance of the associated heat sink,  $R_{\infty,tot}$  is the thermal resistance of the entire heat sink and  $r_C$  is the fraction of the heat sink area dedicated to the conventional path. The thermal resistance of the interface material between the evaporator heat spreader and chip and between the condenser heat spreader and the associated heat sink is incorporated into the thermal resistance of the heat pipe unit. The thermal resistance of the entire heat sink is given by

$$R_{\infty,tot} = \frac{1}{hA_{fin,tot}}$$

3.6

where h is the heat transfer coefficient and  $A_{fin,tot}$  is the surface area of the finned heat sink.

The thermal resistance of the TEC path when no current is applied to the TEC is given by

$$R_T = R_{in} + R_{TEC} + R_{out} \tag{3.7}$$

where  $R_{in}$  is the thermal resistance between chip and cold side and is given by

$$R_{in} = \frac{R_{sub}}{n} = \frac{1}{n} \frac{t_{sub}}{k_{sub} A_{sub}}$$

3.8

where  $t_{sub}$  is the thickness of the substrate (Figure 3.1 (a)),  $k_{sub}$  is the thermal conductivity of the substrate material and  $A_{sub}$  is the cross sectional area of the substrate in one module. The thermal resistance of the interface material associated with the cold side ceramic substrate layer is incorporated into  $R_{in}$ . Here and throughout, the relations are developed for n modules electrically in series but thermally in parallel. When the interconnect material between n and p-type thermo-element is assumed to be ideal the thermal resistance of n modules when they are electrically turned off, each having N thermocouples is approximated as

$$R_{TEC} = \frac{t_{TE}}{k_{TE} (2nNA_{TE})}$$

3.9

Here,  $t_{TE}$  and  $A_{TE}$  are the length and the cross sectional area of n or p-type elements respectively that are assumed to be equal; and  $k_{TE}$  is the thermal conductivity of n or p-type elements (that are assumed to be equal here (Simons and Chu, 2000)). Nolas et al. (2001) noted that the electric resistivity  $\rho$  and thermal conductivity  $k_{TE}$  for both n and p-type conventional thermo-elements are almost the same. The thermal resistance from the hot side of TEC to the ambient is given by

$$R_{out} = \frac{R_{sub}}{n} + R_{HP,T} + R_{\infty,T} = \frac{1}{n} \frac{t_{sub}}{k_{sub} A_{sub}} + R_{HP,T} + R_{\infty,T}$$

3.10

where

$$R_{\infty,T} = \frac{R_{\infty,tot}}{1 - r_C}$$

3.11

and  $R_{HP,T}$  is the thermal resistance of the heat pipe unit in the TEC path and  $R_{\infty,T}$  is the thermal resistance of the associated heat sink. The thermal resistance of the interface material between the evaporator heat spreader and hot side ceramic substrate layer and between the condenser heat spreader and the associated heat sink is incorporated into the thermal resistance of the heat pipe unit,  $R_{HP,T}$ .

These equations can be solved to determine the heat load from the chip and the ratio of heat transfer through each path when the TEC is off. Thus,

$$Q_{chip} = \left(T_{chip} - T_{\infty}\right) \frac{R_C + R_{in} + R_{TEC} + R_{out}}{R_C \left(R_{in} + R_{TEC} + R_{out}\right)}$$

3.12

and

$$\frac{Q_T}{Q_C} = \frac{R_C}{R_T}$$

3.13

The thermal resistance model is more complex when the TEC is on as performance of the system depends on the applied DC current. The total heat load from the chip is still given by Eqn. 3.1, but the heat exiting at the hot side of the TEC modules  $Q_h$  when they are on is given by

$$Q_h = Q_T + P_{in} \tag{3.14}$$

where

$$P_{in} = V_{TEC} I \tag{3.15}$$

$P_{in}$  is the electric power required by the TEC modules to transport  $Q_T$ , the amount of heat at the cold side of the TEC. The analysis of the conventional path is the same as when the TEC is off and is thus given by Eqn. 3.2 and Eqn. 3.4. The relationship between the portion of the heat dissipation from chip that is transported through the TEC path,  $Q_T$ , and the temperature difference between the chip and cold side of the TEC,  $T_c$  is given by

$$Q_T = \frac{T_{chip} - T_c}{R_{in}}$$

3.16

where  $R_{in}$  is the thermal resistance between the chip and the cold side of the TEC and is given by Eqn. 3.8. The relationship between the heat exiting the hot side of the TEC,  $Q_h$

and the temperature difference between the hot side of the TEC,  $T_h$  and the ambient is given by

$$Q_h = \frac{T_h - T_\infty}{R_{out}}$$

3.17

where  $R_{out}$  is given by Eqn. 3.10.

The governing differential equation at steady state for one thermo-couple shown in Figure 2.2 when the thermo-elements are isotropic is expressed as (Arpaci, 1966)

$$k_{TE} \frac{d^2 T}{dx^2} + u''' = 0 3.18$$

where u''' is the energy generation per unit volume in one thermo-couple, which in this case is Joule heating, as the Thomson effect is neglected (APPENDIX A) and is expressed as

$$u''' = \frac{I^2 R_{el}}{2A_{TE} t_{TE}}$$

3.19

Here *I* is the applied current and  $R_{el}$  is the electric resistance of one couple and is expressed as

$$R_{el} = \frac{2t_{TE}\rho}{A_{TE}}$$

3.20

Here,  $\rho$  is the electric resistivity of n or p-type elements (that are assumed to be equal for this analysis (Simons and Chu, 2000)).Combining Eqn. 3.18, 3.19, 3.20 the governing equation is expressed as (Hodes, 2005)

$$\frac{d^2T}{dx^2} + \frac{I^2\rho}{k_{TE}A_{TE}^2} = 0$$

3.21

The boundary conditions are

$$T(0) = T_c$$

3.22

$$T(t_{TE}) = T_h \tag{3.23}$$

Solving Eqn 3.21 for these boundary conditions, the temperature distribution is expressed as (Hodes, 2005)

$$T(x) = \frac{-I^2 \rho}{2k_{TE} A_{TE}^2} x^2 + \left(\frac{I^2 \rho t_{TE}}{2k_{TE} A_{TE}^2} + \frac{T_h - T_c}{t_{TE}}\right) x + T_c$$

3.24

The heat transfer at the cold and hot junction is obtained from the surface energy balance at these junctions. The heat transferred at any junction is the energy absorbed or released due to the Peltier effect plus the conduction heat transfer. Hence

$$Q(x) = I\alpha T(x) - 2k_{TE} \frac{dT}{dx}\Big|_{x}$$

3.25

The heat transfer at the cold and hot junction can be obtained using Eqn. 3.25 for the boundary conditions expressed in Eqn. 3.22 and Eqn. 3.23 respectively and are expressed for one couple as

$$Q_{c1} = I\alpha T_c - K(T_h - T_c) - 0.5I^2 R_{el}$$

3.26

$$Q_{h1} = I\alpha T_h - K(T_h - T_c) + 0.5I^2 R_{el}$$

3.27

where K, the thermal conductance of one couple is given by

$$K = \frac{2k_{TE}A_{TE}}{t_{TE}}$$

3.28

The relationship between the heat into and out of the TEC module(s) is typically approximated assuming that, the interconnect material between the n and p-type thermoelements are ideal and the material properties of the n and p-type thermo-elements are identical (Simons and Chu, 2000) with opposite polarity for the Seebeck coefficient,  $\alpha$ . The interconnect material between the n and p-type semiconductor is assumed to have no effect on the performance of the thermocouple, which is true if the interconnect material has a zero Seebeck coefficient. Typically a good conductor is used as the interconnect material as it possesses a low Seebeck coefficient and so that there is no temperature gradient. The interconnect thermal and electrical contact resistances for a typical TEC module are  $10^{-8}$  to  $10^{-7}$  KW<sup>-1</sup>m<sup>-2</sup> and  $10^{-9}$  to  $10^{-8}$   $\Omega$ m<sup>2</sup> respectively (Silva and Kaviany, 2004) which leads to a contact thermal and electrical resistances of 1.74 X  $10^{-13}$  °C/W and 1.74 X $10^{-14}$   $\Omega$  respectively for a CP 1.4-127-06L thermoelectric cooler module from Melcor.

The expressions for  $Q_T$  and  $Q_h$  for *n* modules each containing *N* thermocouples (Figure 3.1 (b)) are thus expressed as

$$Q_T = nN \left[ I \alpha T_c - K (T_h - T_c) - 0.5 I^2 R_{el} \right]$$

3.29

and

$$Q_{h} = nN \Big[ I\alpha T_{h} - K(T_{h} - T_{c}) + 0.5I^{2}R_{el} \Big]$$

3.30

The Peltier cooling is linearly proportional to the applied current while the Joule heating is proportional to the current squared making it a more dominant factor. Thus, if the applied current exceeds a certain value the net cooling will start decreasing with a further increase in applied current.

The above set of equations can be solved to determine an expression for the heat load from the chip for the Hybrid system when the TEC is on as

$$Q_{chip} = \frac{\left[ \begin{cases} 1 + nNI\alpha(R_{in} - R_{out}) + nNK(R_{in} + R_{out}) \\ -(nNI\alpha)^2 R_{in}R_{out} + nNR_c * \\ (I\alpha + K - nNI^2\alpha^2 R_{out}) \end{cases}}{(I\alpha + K - nNI^2\alpha^2 R_{out}) + nNK * \\ (I\alpha + K - nNI^2\alpha^2 R_{out}) + nNK * \\ R_C + R_{in} + R_{out}) - (nNI\alpha)^2 R_{in}R_{out} \end{cases}} T_{\infty}$$

$$-0.5nNI^2 R_{el}R_C (1 - nNI\alpha R_{out} + 2nNKR_{out})$$

$$R_C \begin{bmatrix} 1 + nNI\alpha(R_{in} - R_{out}) + nNK(R_{in} + R_{out}) \\ -(nNI\alpha)^2 R_{in}R_{out} \end{bmatrix}$$

$$3.31$$