Received February 6, 2021, accepted February 20, 2021, date of publication March 23, 2021, date of current version April 14, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3068335

# A Hysteresis Space Vector PWM for PV Tied **Z-Source NPC-MLI With DC-Link Neutral Point Balancing**

SURESH KUMAR ANNAM<sup>®</sup><sup>1</sup>, R. K. PONGIANNAN<sup>2</sup>, AND N. YADAIAH<sup>3</sup>, (Senior Member, IEEE) <sup>1</sup>Department of Electrical and Electronics Engineering, Samskruti College of Engineering and Technology, Hyderabad 501301, India <sup>2</sup>Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Kattankulathur 603203, India <sup>3</sup>Department of Electrical and Electronics Engineering, JNTUHCEH, Hyderabad 500085, India

Corresponding author: Suresh Kumar Annam (sureshpck4u@gmail.com)

This work was supported in part by the Department of Science and Technology, India, under Project SR/SCRI/132/2013, and in part by the Jawaharlal Nehru Technological University, Hyderabad.

**ABSTRACT** The Photo-voltaic (PV) tied Z-source Neutral-point clamped multilevel inverter (Z-NPC-MLI) is used in solar grid connected applications due to its single stage conversion and better performance. Though the Z source inverters adaptation is accepted in grid connected technology, the need for suitable controller and PWM scheme are necessary to meet out the performance such as shoot through switching, neutral point balancing, and harmonic reduction. The space vector pulse width modulation (SVPWM) strategy is a prominent modulation technique for Z-source NPC-MLIs due to the flexibility to select the appropriate voltage vector. Previous publications have shown the control of a Z-source MLI using the SVPWM with and without modification of shoot through switching. However, the current controller (CC) based SVPWM is not matured, which is the most essential consideration for the grid connected inverter to provide neutral point balancing, shoot through control for low harmonic distortion and a high quality current. With all these aims, this paper presents a PV tied Z-NPC-MLI grid connected system with a unique hysteresis current control SVPWM (HSVM) strategy with neutral point (NP) balancing control and direct current control in the inverter input side. Also, the proposed HSVM is assuring the grid connection with high quality voltage and current waveforms. This CC based SVPWM for Z-NPC MLI has been validated through simulation and FPGA based experimental investigations. The results are confirmed the feasibility and reliability of the proposed HSVM for the PV tie grid connected Z- Source NPC-MLI.

**INDEX TERMS** Z source MLI, neutral-point clamped inverter, space vector PWM (SVPWM), hysteresis current controller (HCC), neutral point balancing.

#### I. INTRODUCTION

Renewable resource (RER) is inevitable in the present power generation system (PGS) era which recently witnessed an exponential growth worldwide, and is expected to continue in the same direction. After hitting about 401GW of solar photo-voltaic (PV) power capacity by the end of 2017, global solar PV capacity is expected to hit 800GW soon [1]. The photo-voltaic (PV) power generation needs a two-stage power conversion (DC to DC by buck-boost converters and DC to AC by inverters). Nevertheless, due to this two-stage power conversion and converters usages, the overall system cost and efficiency is not desirable, since it involves more active and

The associate editor coordinating the review of this manuscript and approving it for publication was Alon Kuperman<sup>10</sup>.

passive components [2]. After the arrival of Z source inverters [3], the two-stage power conversion (DC to DC and DC to AC) is made possible through single stage(DC to boosted AC), which reduced circuit size, losses and cost [4]. Hence Z-source inverter is considered an interesting topology for drives and PV applications [5]-[7] The combining Z source concept with multilevel inverters (MLIs) is most successful in terms of reduced conversion stage, enhanced system performance [8], [9]. Particularly, Neutral-point clamped (NPC) MLI is the good choice among other MLI topologies due to their circuit structure and operation is quite similar to conventional six switch voltage source inverter (VSI) [10].

In Z source inverter, the boost operation is decided by the shoot through (ST) switching state, in which the inverter input DC-link voltage is short circuited via Z source inductors and capacitors [11]. When the pulse width modulation (PWM) is used in the Z source inverter, it is fully capable to handle ST events for handling the inverter internal issues such as DC-link control and to improve quality of the output. The PWM approaches are investigated by adjusting the carrier positions and altering the shoot through (ST) for minimum, constant and maximum boosting methods. The SVPWM strategy provides opportunity to deal the switching sequence directly [12], [30], which facility is not possible in carrier based PWM. The P. C. Loh et.al has proposed SVPWM for controlling three-phase three-level Z-MLI with 24 ST options [13]. Followed by [14] F. B. Effah et.al developed a new set of ST options, where the authors used 12 ST states. These attempts have well concluded about controlling the inverter voltage. However, the current control is not attempted which the main factor of dc-link capacitor balancing.

In grid connected power systems, to overcome the transformer usage issue, researchers have proposed different PV powered transformerless (TL) inverters for both single and three-phase systems [15, 16]. There are many innovations in single phase TL inverter topologies, in which the idea is to only mitigate the leakage current by adding the extra power switches in the main inverter circuitry. In three-phase networks, the researchers are totally involved with PWM and current control design algorithms [17], [18]. The Z source MLIs are the better choice for PV applications compared to two-level VSIs, with respect to reduction of harmonic content output waveforms and common mode voltage (CMV) suppression filters and EMI filters. According to TL grid tied inverter, the control of the inductor current along with the grid voltage synchronization is essential. Therefore, the combined current controller (CC) and voltage control PWM is interesting for such TL grid connected system. There are a variety of CCs are available for controlling the electrical power [19]. Among them, the hysteresis current controller (HCC) is a potential one, as it has simple control competence associated with PWM methods [20], [21]. Very few attempts have been made on SVPWM based HCC [22], [23]. However, these methods are involving difficult mathematical operation to locate the active switching vector and also the capacitor balancing is very hard to attain. In practice, maintaining these capacitors is much challenging. This deceptive curtail reduces the NP capacitor's lifespan due to the NP fluctuation between the capacitors crops the high voltage and current harmonics, which leads to the inferior grid power quality. There are few attempts made for capacitors balancing through the separate balancing circuits as well as PWM algorithms [24]-[27], [31]-[33]. Here, rather a circuit based balancing; PWM algorithms gave an attractive result. Among the reported PWM methods and their ideologies, the SVPWM based consideration was superficies [29]. Based on the above organized discussion, the TL PV tied grid system requires a stable power converter, current controller and PWM technique for the straight forward operation, less cost, and high performance. In context with capacitor balancing in Z source NPC MLI, few examples found in [28], [31] using

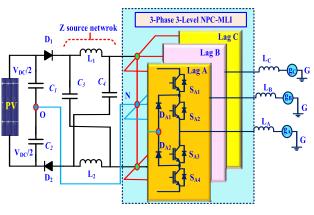

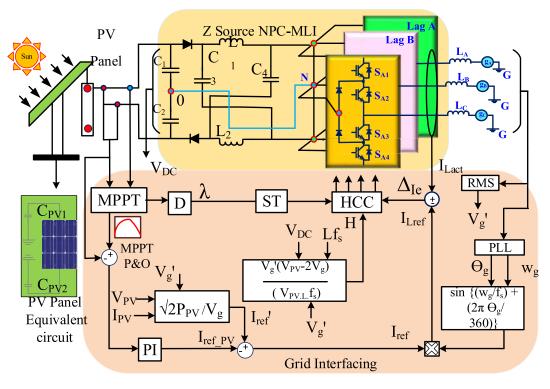

FIGURE 1. PV tied grid connected three-phase three-level Z source NPC-MLI.

SVPWM and carrier level-shifted based control, which are not discussed about the current control.

With this motivation, this paper suggests the three-phase three-level PV connected Z source-MLI for the utility grid. The Hysteresis current control based SVPWM (HSVM) control system is designed for the grid synchronization. The proposed HSVM eliminates the low frequency oscillations using suitable ST (Upper and Lower ST), with regular switching events, which ensures the DC-link capacitors balancing along with current control. The proposed system is simulated and verified through MATLAB/Simulink software. The experimental prototype 2-kW solar panels attached grid connected three-phase three-level Z-NPC-MLI is established and the validation is done through Xilinx family SPARTAN-6 controller. The results obtained from the simulation and experiment is confirming the technical feasibility and advantages such as reduced harmonics and neutral point balancing of the proposed HSVM.

In addition the results have shown the uniqueness of the proposed current controller involvement with SVPWM for improving the inverter performance. The section II elaborates about the Z source NPC-MLI topology, concepts of shoot through, and design concepts of Z network. The HCC based SVPWM for Z-NPC-MLI is presented in section III. Section IV brings out the simulation and experimental verifications. Finally, conclusions are summarized in section V.

#### II. Z-SOURCE NPC-MLI TOPOLOGY

The Z-source concept applied to MLI gives more advantages like suppression the voltage ripples, flexible shoot through state and neutral point balancing. Therefore, this session describes the Z-NPC-MLI power circuit, its operation and the design of Z Network components along with analysis of topology.

#### A. Z-NPC-MLI

The Fig.1 shows the power circuit topology of Z-NPC-MLI in three-phase three-level structure, which consists of three legs, and each leg has four power switches  $(S_{1A} - S_{4A})$  with

| TABLE 1. ST and | d non ST op | eration of | Z-NPC-MLI. |

|-----------------|-------------|------------|------------|

|-----------------|-------------|------------|------------|

| Mod<br>e | Switchi<br>ng State | Tuned on switches                                      | Action         | V <sub>out</sub>            |

|----------|---------------------|--------------------------------------------------------|----------------|-----------------------------|

|          | +1                  | $S_{X1}$ $S_{X2}$                                      | -              | $(V_{DC}/2)+L_1*(d_i/d_t)$  |

| NST      | 0                   | $S_{X2}$ $S_{X3}$                                      | -              | 0                           |

|          | -1                  | $S_{X3}$ $S_{X4}$                                      | -              | $-(V_{DC}/2)-L_2*(d_i/d_t)$ |

| ST       | Full ST             | $S_{X1} \hspace{0.1 cm} S_{X2} \hspace{0.1 cm} S_{X3}$ | Charging       | 0                           |

|          |                     | S <sub>X4</sub>                                        | $L_1 \& L_2$   |                             |

| STT      | Top ST              | $S_{X1} S_{X2} S_{X3}$                                 | $L_1$          | 0                           |

|          |                     |                                                        | Charging       |                             |

| STB      | Bottom              | $S_{X2}S_{X3}S_{X4}$                                   | L <sub>2</sub> | 0                           |

|          | ST                  |                                                        | Charging       |                             |

2 clamping diodes ( $D_{A1}$  and  $D_{A2}$ ). The Z source impedance elements ( $L_1 = L_2 = L, C_3 = C_4 = C$ ) are connected in the input side and obtaining power from DC-link. Two DClink capacitors ( $C_1, C_2$ ) are serially coupled with DC input source, which split the DC-link voltage as  $V_{DC}/2$  for making the multilevel output as 0,  $V_{DC}/2$ , and  $V_{DC}$ . In the load side, each inverter leg is connected to grid by using inductor ( $L_A = L_B = L_C = L_B$ ). The Z-NPC-MLI is operating with shoot through (ST) and non-shoot through (NST) modes. In ST mode, the input DC supply is short circuited through inverter switch and Z –network inductors, to store the energy in the inductors, L1 and L2. During NST mode, the DC power is converted to AC power (through normal inverter switching).

The Z source impedance elements ( $L_1 = L_2 = L, C_3 = C_4 = C$ ) are connected in the input side and obtaining power from DC-link. Two DC-link capacitors ( $C_1, C_2$ ) are serially coupled with DC input source, which split the DClink voltage as  $V_{DC}/2$  for making the multilevel output as 0,  $V_{DC}/2$ , and  $V_{DC}$ . In the load side, each inverter leg is connected to grid by using inductor ( $L_A = L_B = L_C = L_g$ ). The Z-NPC-MLI is operating with shoot through (ST) and non-shoot through (NST) modes. In ST mode, the input DC supply is short circuited through inverter switch and Z – network inductors, to store the energy in the inductors,  $L_1$ and  $L_2$ . During NST mode, the DC power is converted to AC power (through normal inverter switching).

By considering one leg in NPC-MLI, the operation is described by three switch options; 1(both upper switch ON), 0(middle switch ON),-1(both lower switch ON). Including Z source operation with NPC-MLI regular switching operations, the ST mode is created in order to short the input DC supply through inductors by switching ON all the four switches in the leg, which is called as full shoot through (FST). Alternatively, for reducing the switching losses, the top ST (top 3 switches is ON in a leg) and bottom ST (bottom 3 switches is ON in a leg). The table-I describes all the possible combinations of the switching options for Z-NPC-MLI.

### B. ST AND NST OPERATION OF Z-NPC-MLI

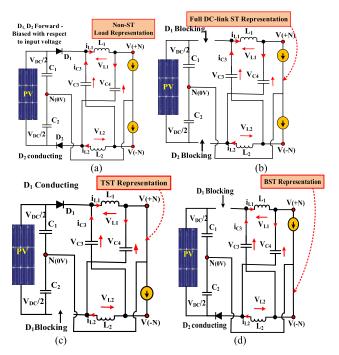

The ST and NST mode of operation of the circuitry is shown in the Fig.2. During the ST mode, the inverter can be involved

FIGURE 2. ST and NST mode operation of Z source NPC-MLI; (a) Non-ST (NST),(b) full-ST,(c)TST,(d)BST.

either full ST or partial ST [28]. Though, the both methods are shorting the input DC source via inductors  $L_1$  and  $L_2$ , the full ST(FST) is not a best choice of balancing the inductor's charging profile (nonlinearity charging) and it roots the high magnitude of lower order harmonics in the output waveforms. Since the top-ST(TST) and bottom-ST(BST) has an individual control on the  $L_1$  and  $L_2$  charging characteristics, the combination of TST and BST maintains the inductors charging in parallel, which ensures the better quality output waveform [8], [13].

### C. DESIGN OF Z SOURCE NETWORK

The In the Z network, calculation of the Z network elements (Inductor(L) and Capacitor(C)) and its charging, discharging and boosting functions are important. During ST period, while considering the symmetry charging and discharging nature on L ( $L_1 = L_2 = L$ ) and C ( $C_3 = C_4 = C$ ), the role of the inductor is to limit the current ripple during shootthrough state. The capacitor absorbs the current ripple and achieves a quite stable voltage. The inductor is charged by the capacitor during shoot-through time( $T_{sh}$ ).  $\Delta I$  is current ripple of the inductor.Inductor and capacitor values are calculated as  $L = \frac{VT_{sh}}{\Delta I}$  and  $C = \frac{\bar{I}_L T_{sh}}{\Delta V_C}$  respectively. The average current of the inductor can be found from  $\bar{I}_L = \frac{P}{V_{PV}}$ . The  $\Delta V_C$  is the assumed voltage ripple of the capacitor.  $V_{PV}$  is PV output voltage, P is the total power. The voltage across the inductors and capacitors are approaches to V<sub>L</sub> and V<sub>C</sub> respectively, where  $V_{L1} = V_{L2} = V_L = L_1(di/dt) = L_2(di/dt)$  and  $V_C \ = \ V_{C3} \ = \ V_{C4} \ = \ V_{DC}/2.$  During the NST mode,  $V_L = V_C = V_{DC}/2$ . This condition is satisfied, since the

capacitors  $C_1$  and  $C_2$  are connected in parallel and voltage across the Z source network will be  $2V_C$ . In ideal conditions,  $V_L = V_C$  and  $2V_C = 2V_{dc}$ . During this condition, the inverter output voltage,  $V_o = 0$ .

From the Fig 2, considering NST mode of operation (see Fig. 2.a); when diode  $D_1$  and  $D_2$  are in forward bias conduction,

The inductor voltage,

$$V_{L1} = V_{DC} - V_C \tag{1}$$

$$V(+) \Longrightarrow \frac{V_i}{V_i}; \quad V(-) \Longrightarrow -\frac{V_i}{V_i} \tag{2}$$

$$V_i = 2V_C - V_{DC}$$

(3)

During TST mode operation as shown in Fig.2.c, the diode  $D_1$  is in conduction and  $D_2$  is in blocking state. Hence, the inductor voltages are obtained as,

$$V_{L1} = \frac{V_{DC}}{2}; \quad V_{L2} = 0$$

(4)

and,

$$V(+) = 0V; V(-) = \frac{V_{DC}}{2} - V_{C3}$$

(5)

During BST mode operation as shown in Fig.2.d, the diode  $D_2$  is in conduction and  $D_1$  is in blocking state. Hence the inductor voltages are obtained as,

$$V_{L1} = 0; V_{L2} = \frac{V_{DC}}{2}$$

(6)

and,

$$V(-) = 0V; V(+) = -\frac{V_{DC}}{2} + V_{C4}$$

(7)

At steady state condition, the Z- network inductors  $L_1$  and  $L_2$  average voltage in one T cycle is zero.

$$V_{L1} = \frac{(V_{DC} - V_C) * T_{NST} + \left(\frac{V_{DC}}{2}\right) * T_{TST} + \left(\frac{V_{DC}}{2}\right) * T_{BST}}{T}$$

(8)

$$T_{NST} + T_{TST} + T_{BST} = T (9)$$

$$V_C = \frac{V_{DC} * \left(1 - \frac{T_{TST} + T_{BST}}{2T}\right)}{\left(1 - \frac{T_{TST} + T_{BST}}{T}\right)} \tag{10}$$

Using  $V_C$  in NST, TST and BST mode operations, the DClink voltage of the inverter for NST, TST and BST is derived as,

$$V_{i\_NST} = \frac{V_{DC}}{\left(1 - \frac{T_{TST} + T_{BST}}{T}\right)} \tag{11}$$

$$V_{i\_TST} = V_{i\_BST} \frac{V_{DC}/2}{\left(1 - \frac{T_{TST} + T_{BST}}{T}\right)}$$

(12)

Form the Eqs. (11) and (12) during TST and BST, the voltage present in the DC-link is half that of NST. Hence, it is proven that by equally sharing TST and BST mode using input DC-link capacitors ( $C_1$  and  $C_2$ ), the inverter is boosting voltage with proper DC-link balancing, which helps to improve the THD performance on the output voltage and current waveform.

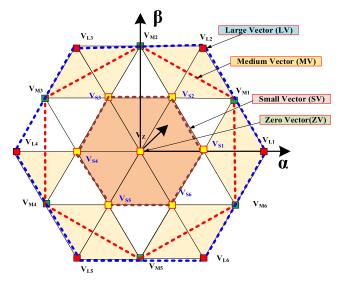

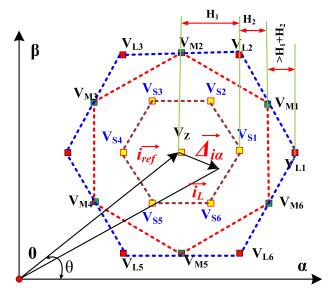

FIGURE 3. SVD of three-phase three-level Z-NPC-MLI.

The inverter peak ac voltage output,  $Vx_0(x=\{A,B,C\})$  is resulting as,

$$V_{x0} = \frac{M}{\sqrt{3}} V_{i\_NST} \tag{13}$$

$$V_{xo} = \{\frac{M}{\sqrt{3}} V_{DC} \frac{1}{\left(1 - \frac{T_{TST} + T_{BST}}{T}\right)} = \{\frac{M}{\sqrt{3}} V_{DC} B_F \quad (14)$$

where  $B_F$  is boosting factor ( $B_F \ge 1$ ).

#### III. HCC BASED SVPWM FOR Z-NPC-MLI

SVPWM technique offers the flexibility in selection of switching states [14]. The hysteresis current control (HCC) method gives an opportunity of harmonics reduction. To widen the scope of SVPWM, the hysteresis current control strategy has been incorporated to achieve the better harmonic reduction and neutral point balancing in Z source NPC-MLI. The theory of SVPWM presented in view of conventional and proposed techniques. A closed loop PV-tied grid connected control strategy developed is described in this section.

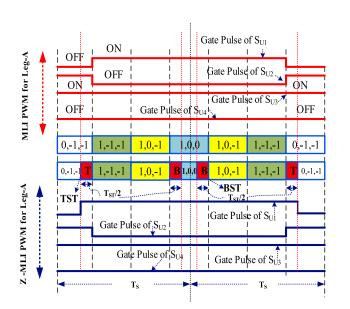

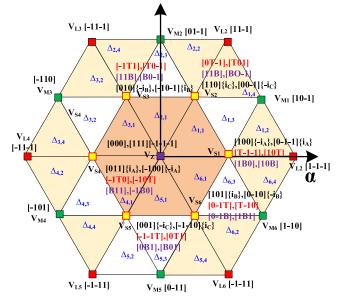

**A. OPERATION OF CONVENTIONAL SVPWM FOR NPC-MLI** The Fig. 3 shows the three-level space vector diagram (SVD) with the different switching state vectors. For normal inverter operation (during the NST mode), the inverter has four different switching vectors (zero vector {ZV}, small vector {SV}, medium vector {MV}, and large vector {LV}) to bring the multilevel output voltage [26]. These four switching vectors are forming a hexagon (called space vector diagram) using their 27 switching states, among which 3 for ZV, 12 for SV, 6 for MV and 6 for LV.

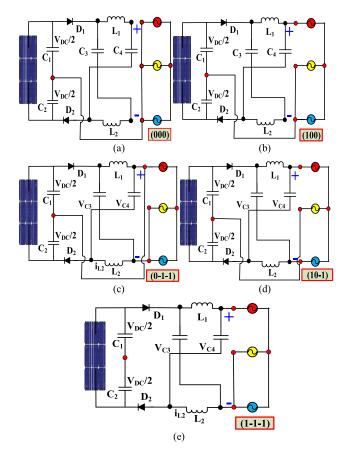

According to the SVD presented in Fig. 7, every switching action has an individual phase current, which affects the DC-link capacitors/NP balancing. For example, at SV switching state [1 0 0], the B and C phases are linked with neutral point 'O' and phase-A is associated to input DC link. Hence,

#### TABLE 2. ST and non ST operation of Z-NPC-MLI.

| (+)ve   | i <sub>N</sub> | (-) ve  | i <sub>NP</sub> | MVs     | i <sub>N</sub> | LVs     | i <sub>N</sub> | ZVs      | i <sub>N</sub> |

|---------|----------------|---------|-----------------|---------|----------------|---------|----------------|----------|----------------|

| SVs     | Р              | SVs     |                 |         | Р              |         | Р              |          | Р              |

| [0-1-1] | i <sub>A</sub> | [1 0 0] | -i <sub>A</sub> | [1 0-1] | i <sub>A</sub> | [1-1-1] | 0              | [111]    | 0              |

| [-10-1] | i <sub>B</sub> | [0 1 0] | -i <sub>B</sub> | [0 1-1] | i <sub>B</sub> | [11-1]  | 0              | [000]    | 0              |

| [0 0-1] | i <sub>C</sub> | [1 1 0] | -i <sub>C</sub> | [-1 10] | i <sub>c</sub> | [-11-1] | 0              | [-1-1-1] | 0              |

| [0 1 1] | i <sub>A</sub> | [-10 0] | -i <sub>A</sub> | [-1 01] | i <sub>A</sub> | [-111]  | 0              | -        | -              |

| [1 0 1] | i <sub>B</sub> | [0-1 0] | -i <sub>B</sub> | [0-1 1] | i <sub>B</sub> | [-1-11] | 0              | -        | -              |

| [-1-10] | i <sub>C</sub> | [0 0 1] | -i <sub>C</sub> | [1-1 0] | i <sub>C</sub> | [1-11]  | 0              | -        | -              |

**FIGURE 4.** Switching state of Z source NPC-MLI; (a) ZV[000], (b) Negative current SV[100 ], (c) positive current SV[0 -1 -1 ],) (d) MV[10 -1], (e) LV[1 -1 -1].

neutral current ( $I_N = i_A + i_B + i_C$ ) approaches to  $-i_A$ ( $i_B + i_C = -i_A$ ). For balanced DC-link condition, the  $I_N$ should be zero. Table-II shows the different switching of the three phase currents for the three-level NPC-MLI. Here, the ZV and SV have a redundant switching privilege, which helps balancing the DC-link. However, the MV and LV has only unique switching option for a sector. Hence, these vectors not helping for NP self-balancing. The Fig.4 shows the SVD with their different switching states of ZV, SV, MV and LV including phase currents.

Now, for creating TST and BST, the proposed SVPWM is considering SVs, since they have a redundant switch-

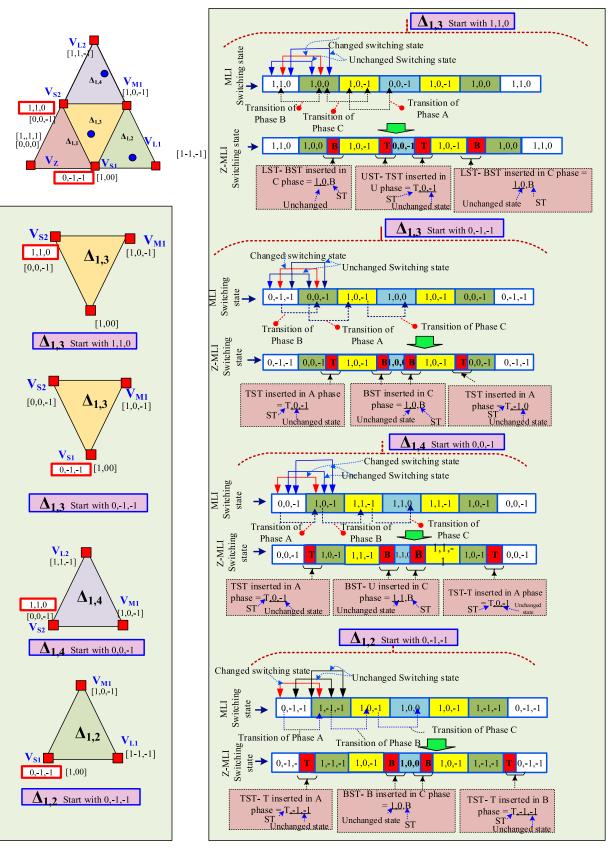

FIGURE 5.  $\Delta_{1,2}$  ST switching state creation for Z-NPC-MLI.

ing privilege which helps the inverter DC-link balancing. In the following section explains the operation of ZNPC-MLI SVPWM in detail.

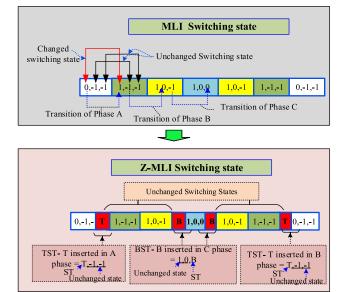

The Fig. 5 shows the creating of ST switching for Z-NPC-MLI. The TST and BST chosen based on switching state transition. Considering sector-1, the sub-triangle  $\Delta_{1,2}$  as shown in Fig.5, the regular MLI switching pattern is {[0 -1 -1], [1 -1 -1], [1 0 -1], [1 0 0], [1 0 -1], [1 -1 -1], [0 -1 -1]}. Here, considering proposed Z-MLI, ST is fixed through changes in the adjacent switching state. For example, the 1<sup>st</sup> switching state [0 -1 -1] and their next [1 -1 -1] the transition is only on A-phase switching (0  $\rightarrow$  1). Therefore, the ST is fixed through TST in A-phase and fixed between [0 -1 -1] and [1 -1 -1].

Similarly, in the same  $\Delta_1$ , 2 switching states series [1 0 -1] and [1 0 0] differs from their C-phase. Hence the next ST is fixed through BST in C-phase and fixing in between [1 0 -1] and [1 0 0]. The TST and BST selections are chosen based on the current flow directions on the inverter from DC-link to load. When, bit change in  $0 \rightarrow 1$ , the TST is chosen and when the bit change in  $-1 \rightarrow 0$ , the BST has chosen. The ST interval for both TST and BST is depend on the boosting factor using Eq(12). In order to maintain the NP self-balancing and volt-sec balancing, the inverter switching selections are starting from A- phase to C- phase in a forward switching and following the reverse same sequence order. The TST and BST switching states timing is sharing from the regular switching, which ensure the symmetry output voltage.

For example in Fig.6, when the target vector lies in  $\Delta_{1,2}$  the TST is time calculated from the boosting factor and it is fixed between [0 - 1 - 1] and [1 - 1 - 1] without changing switching frequency. Using this method, the number of power switching commutations in a switching cycle is same as traditional NPC-MLI, which ensures the switching losses in the

FIGURE 6.  $\Delta_{1,2}$  ST and NST switching state and PWM pulse for Z-NPC-MLI.

Z-NPC-MLI. In this method, when the inverter is operating in lower modulation index  $(M_a)$ / buck mode, there is no STs are inserted.

Therefore, this is ensuring the avoidance of collapse in inverter line to line voltage and NP balancing. In the next stage, the proposed HCC and the concepts used for neutral point balancing are discussed

#### B. HYSTERESIS CURRENT CONTROL BASED SVPWM

In proposed SVPWM current control method, the hysteresis bands are directly used to employ the four groups of (ZV, SV, MV and LV) vectors in SVD. Here the current control is made based on current error (error vector,  $\vec{\Delta}_i$ ) and available switching options on SVD. The proposed structure is principally employed to retain the  $\vec{i}_{Lact}$  close to the  $\vec{i}_{Lref}$  inside the hysteresis band values. To compensate for the complication of achieving the CC along with capacitors balancing, the SVPWM is modified based on the hysteresis band 'H'.

Fixed frequency HCC can be obtained by calculating the hysteresis band H using the transient value of the  $V_g$  and output voltage of PV array.

Based on that, the hysteresis band 'H' is calculated as,

$$H = \frac{V_g(V_{PV} - 2.V_g)}{V_{PV}.L.f_s}$$

(15)

where, the variant parameters are  $V_{PV}$ ,  $V_g$ ,  $f_S$  and fixed one is filter inductor (L). When the reference current ( $i_{Lref}$ ) and actual current ( $i_{Lact}$ ) lie in SVD error vector,  $\vec{\varepsilon_i}$  is calculated as,

$$\overrightarrow{\varepsilon_l} = \overrightarrow{l_{Lref}} - j\overrightarrow{l_{Lact}}$$

(16)

where,  $i_{Lref} = i_{Lref\alpha} + ji_{Lref\beta}$ ;  $i_{Lact} = i_{Lact\alpha} + ji_{Lact\beta}$ When the  $\overrightarrow{\varepsilon_i}$  expressed in the SVD plane with  $\alpha\beta$ -vector

**FIGURE 7.** SVD for three phase three Level Z source NPC-MLI including TST, BST and individual phase currents for NST switching states.

FIGURE 8. SVHCC for three-phase three-level Z source NPC-MLI.

components frame, the  $\overrightarrow{\varepsilon_i}$  can be represented as,

$$\overrightarrow{\varepsilon_l} = \overrightarrow{\Delta_{l\alpha}} + j \overrightarrow{\Delta_{l\beta}} \tag{17}$$

From Eq (17), the position of the  $\vec{\epsilon_i}$  in SVD is calculated and then the switching vectors are selected to keep the  $\vec{i}_{Lact}$ close to the  $\vec{i}_{Lref}$ . The Fig.8 shows the HSVM with  $\vec{\epsilon_i}$ and H. Here, the sector and sub-triangle, and its switching state selection is done based on the  $\vec{\epsilon_i}$  and H. The boundary area is determined by the hysteresis bands (H<sub>1</sub> and H<sub>2</sub>).

The values of  $H_1$  and  $H_2$  depends on  $i_{Lref}$  and its control dynamics. The values of H will vary between zero and H (Eq.15). Here the maximum value of the H is related with maximum operation modulation (Modulation Index,  $M_a$ ). To

FIGURE 9. The Proposed Grid-connected PV connected Z-NPC-MLI control blocks representation.

find the value of  $\vec{\epsilon_i}$  and H, the proposed SVD operating in three environments which are H<sub>1</sub>, H<sub>2</sub>, and > H<sub>1</sub> + H<sub>2</sub>.

During the  $H_1$  interval the switching selection is directed to use for ZV and SV. Similarly, for  $H_2$  the SV and MV, and when H is beyond  $H_1 + H_2$ , the SV, MV, LV switching states are selected.

#### C. NEUTRAL POINT/DC-LINK BALANCING

In the proposed HSVM is using nearest three vectors N3V switching selection vector selection [20], [22]. Based on the  $\vec{\epsilon_i}$  tip, the HSVM choose the sector and sub-triangle, and switch the vertices of the triangle in every switching period for the hysteresis region using all available vector to get zero phase current. For example, if  $\vec{\varepsilon}_i$  tip is situated in  $H_1$  region, the control lies in the triangle  $\Delta_1$ , 1, switching vectors,  $V_{Z0}$  [[000], [111], [-1 -1 -1]],  $V_{S2}$  [[110], [00-1]} and  $V_{S3}\{[010], [-10, -1]\}$  are selected with their ST options. Similarly, when vector lies in  $\Delta_{1,3}$ , in order or to balance the NP the vector switching are chosen in redundant manner as shown in Fig.10. Here, the SV switching sequences [0 -1 -1], [110] has chosen as a starting switching state to synthesis the reference vector. Hence, at target reference vector lies in  $\Delta_1$ , 3 the vector synthesization is happen in two time to balance the capacitor. Other sub-triangles  $\Delta_{1,2}$ and  $\Delta_1, 4$  are have only one, since they involve MV and LV. As shown in Table-1, and in the LV phase current is zero. However, the MV showing the particular phase current which is causes the small disturbance in DC link balancing. As per the NP fluctuation standard this is considerably small.

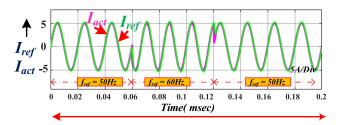

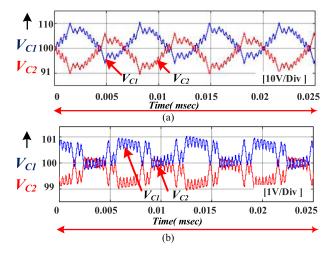

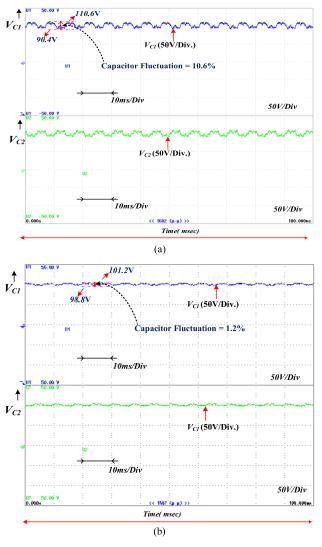

Actual load current and reference current tracking performance with fixed H band (5Amps). The tracking performance is executed with 50Hz and 60 Hz reference current. From the waveform, it could see that the actual current is clearly tracking the reference current with decent steady state and transient response. To validate the DC-link capacitors (V<sub>C1</sub> and V<sub>C2</sub>) balancing for HSVM, the simulation is performed for both conventional and proposed HSVM, which are shown in Fig. 14 (a) and Fig. 14. (b), respectively. The NP fluctuation (NPF) is calculated from V<sub>C1</sub> and V<sub>C2</sub>;

NPF =

$$\frac{(\frac{V_{DC}}{2}) - V_{C1}}{V_{C1}}$$

(18)

From the Eq.(18), the proposed HSVM NPF is very less (calculated as  $\approx 1\%$ ) the conventional Z-source SVPWM (calculated as  $\approx 10\%$ ), which ensure the output voltage and current waveform quality. Based on the results, the proposed HSVM claims that it is not only controlling current and it is also maintaining the NP current.

#### D. CLOSED-LOOP PV TIED GRID-CONNECTED CONTROL STRATEGY OF PROPOSED Z-NPC-MLI

The grid-connected PV connected Z-NPC-MLI control blocks representation is shown in Fig. 9. The system is classified into four modules, namely; PV module, boosting X-network, Z-NPC-MLI, and grid interfacing control system. In the solar module, the PV voltage and current are measured and given to P&O technique based MPPT. Here the  $\lambda$  is arrived from MPP gain and given as ST to HCC. The ouput of

FIGURE 10. Sector-1 ST and NST switching state.

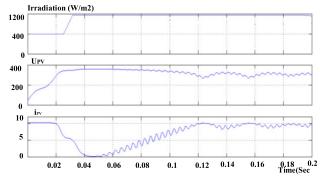

FIGURE 11. Simulation results of PV output.

the PV is connected directly to inverter DC-link and The  $C_1$  and  $C_2$  DC-link capacitors are splitting the DC-link voltage. This equaliency is maintained by the inverter proposed SVM switching.

In the outside, the PLL is implemented on the grid side to calculate grid angle  $\theta_g$  and utility grid nominal frequency  $(w_g = 2Vf_o), f_o$  is grid voltage frequency) for the grid synchronization. The simplest Zero-Crossing Detection (ZCD) algorithm has been used. The RMS value of grid voltage  $(V'_g)$ is measured and given to the  $I'_{ref}$  estimation block. The  $I'_{ref}$ sampling calculated from  $V_{PV}, I_{PV}$  and RMS values of grid voltage  $V'_g$  as below,

$$I_{ref}^* = \frac{\sqrt{2}V_{PV}I_{PV}}{V_g'} \tag{19}$$

This  $I_{ref}^*$  is compared with PV reference current  $(I_{PV-ref})$ and estimating the final grid reference current dc- component  $(I_{ref})$ , which is multiplied with sin  $((w_g + f_s) + (2\pi\theta_g/360))$  to calculate the final grid reference current  $(I_{ref})$ . It is also called a inductor reference current  $(I_{Lref})$ . The actual inductor  $I_{Lact}$ and  $I_{Lref}$  gives the error of inductor current  $\Delta_{ie}$  based on the  $\vec{\epsilon_i} = (i_{Lref} - i_{Lact})$ . Finally, the calculated real-time hysteresis band H using eq(15) and  $\Delta_{ie}$  gives gate pulses. The error  $\Delta_{ie}$ and  $\lambda$  obtain the inverter switching options and ST duty cycle for the boosting, current controller and capacitor balancing of the Z-NPC-MLI.

#### **IV. SIMULATION AND EXPERIMENTATION**

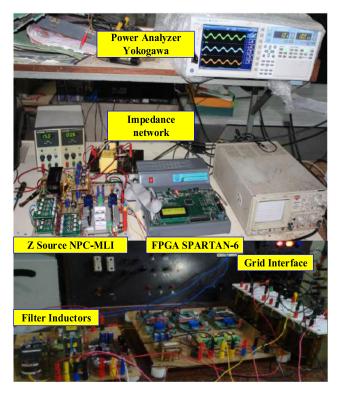

In order to validate the performance of proposed system. A closed loop PV grid tied Z\_NPC MLI system has been modeled in MATLAB-SIMULINK environment and a prototype model with 2kW PV tied grid connected Z NPC MLI system has been developed to carried out the experimentation. Experimental setup is shown in Fig.16. of 2-kWp roof-top PV panels (12 serial-parallel panels, each 250W) feeding a 2-kW three-phase 3-level Z-NPC-MLI grid connected system is developed. Xilinx family SPARTAN-6 FPGA controller is used to implement the hysteresis current control based SVPWM control scheme.

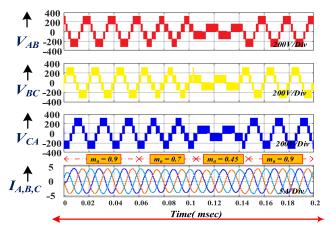

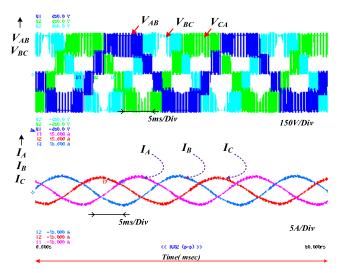

FIGURE 12. Simulation results of three phase voltage and current waveform of Z-NPC-MLI.

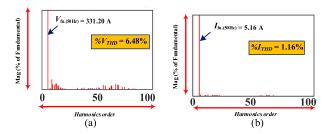

FIGURE 13. Simulation results of harmonics spectra for Z-NPC-MLI  $atm_a = 0.9$ ; (a) voltage harmonics spectra,(b)current harmonics spectra.

FIGURE 14. Simulation results of actual load current and reference current when H band is fixed at 5Amps.

#### A. SIMULATION STUDY

The 2kW PV array modules are configured (series model) to feed the power to inverter with each module rated at 152.5W. The NPC-MLI maintains the dc-link voltage close to 250V using two ( $C_1$  and  $C_2$ ) 470 $\mu$ F capacitors. The inverter is connected to 300V/50 Hz utility grid through 4 mH inductors. The simulation result of the PV is given in the Fig.11. The effects of variation of solar irradiation on PV observed here around 12hr 33min noon. The observed voltage and current in the range of 320V to 400V and 7A to 10.2 A respectively.

The inverter switching frequency  $(f_{sw})$  is maintained throughout the operation of the inverter as 5 kHz. Initially, the Z-NPC-MLI is simulated and investigated with grid connected system with fixed hysteresis bands. The inverter boosting factor set a 1.6, the inverter output voltage approach to 337V. The Fig.12 shows the inverter line voltages and

FIGURE 15. Simulation results of Z-NPC-MLI voltage across DC-link capacitors; (a) conventional SVM method, (b) HSVM.

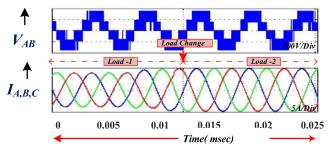

FIGURE 16. Simulation results -Transient response of inverter output currents.

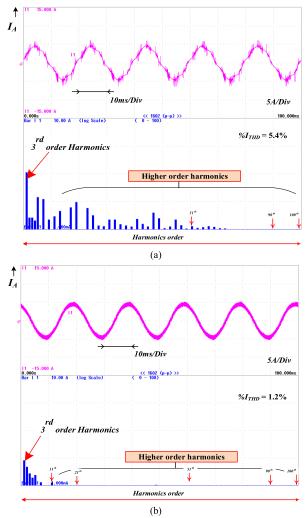

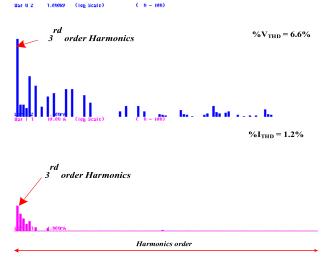

phase value of load current for different operating conditions (different modulation index). During every operation instant, the inverter delivers the voltage and current with reduced harmonics in voltage and current. The Fig. 13 illustrates the voltage and current harmonics spectra for the maximum inverter operating point with  $m_a = 0.9$ . From the THD spectrum results in Fig.13, it is observed that, the inverter output having the nominal voltage THD (6.48%) and current THD (1.16%), due to the control of DC-link voltage, which are in the acceptable range.

The Fig. 14 shows load current responses while varying hysteresis band and change in reference current frequency. From the result, it can see that the load current tracks the reference current. The Fig. 15(a) and 14(b) shows the voltage across DC link capacitors with conventional SVPWM method and HSVM method respectively. It indicates that Neutral point fluctuation (NPF) of conventional SVPWM method is 10.6% where as 1.2% of NPF of proposed HSVM method [22]. Fig.16 shows the transient response of the proposed HSVM. During the change in load at 0.012msec, the HSVM topology has ensured the enhanced boosting factor and meeting out the load voltage and current requirements together with NP balancing.

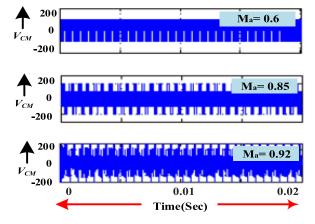

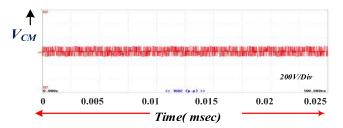

The Fig. 17 common-mode voltage presented with different modulation indices. From that results it is understood

**FIGURE 17.** Simulation results – Common-mode voltage for the different modulation indies ( $M_a = 0.6$ ,  $M_a = 0.85$ , and  $M_a = 0.9$ ).

FIGURE 18. Experimental setup of proposed PV fed grid connected three phase three Level Z source NPC-MLI.

the common-mode voltage is maintaining as  $V_{dc}/2$  for all modulation index operations.

#### **B. EXPERIMENTAL STUDY**

An experimental prototype model of 2-kWp roof-top PV panels (12 serial-parallel panels, each 250W) feeding a 2-kW three-phase 3-level Z-NPC-MLI grid connected system is developed. The complete experimental hardware set up is shown in Fig. 18. In the experiment, The Xilinx family SPARTAN-6 FPGA controller is used to implement the hysteresis current control based SVPWM control scheme. When

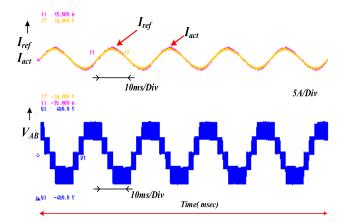

FIGURE 19. Experimental results for actual inverter current and reference current at  $f_0 = 50$  Hz and  $V_{dc} = 200$  V, inverter Voltage ( $V_{AB}$ ).

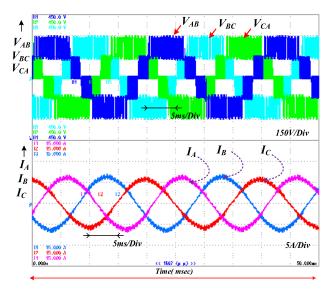

FIGURE 20. Experimental results for three phase inverter voltage and inverter current with  $m_a = 0.8$  at  $f_o = 50$ Hz,  $I_{load} = 5A$  and  $V_{dc} = 200V$ .

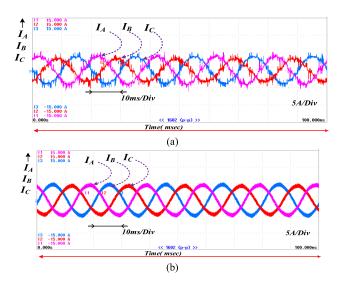

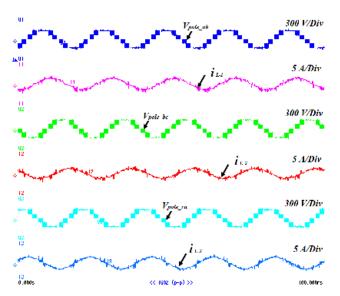

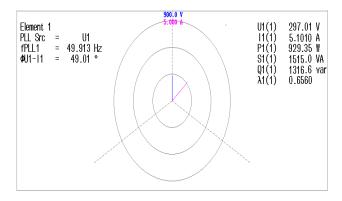

the inverter is operated under normal PV panel conditions (temperature: 27 °C and Irradiance: 1000 W/m2), the system deliver output of 300V, 50Hz. The MPPT controller maintains a DC-link voltage as 200V. The spectrum analyzer (YOKO-GAWA) is used for capturing the waveforms and harmonics. The performance of proposed HSVM control method such as voltage, current magnitude harmonics and DC link capacitor Neutral point balancing carried out via simulation; at same conditions the experimentation has been carried out and they are validated. When modulation index (ma) and boosting factor were set as 0.9 and 1.6(as similar specifications are taken in simulation), the inverter delivers output of  $\approx 300$  V. At aforementioned operating specifications, the inverter is connected to grid and results are verified. The Fig.19 shows inverter current and reference load current waveform along with inverter output voltage. During this operating condition, the HSVM tracks grid reference and controlling the current with better NP balancing with 1.2%. The Fig.20 shows the

FIGURE 21. Experimental results for three phase inverter voltage and inverter current with  $m_a=0.9$  at  $f_o=50 Hz, \ I_{load}=3A$  and  $V_{dc}=200V.$

FIGURE 22. Experimental results for actual inverter current and reference current at  $f_0 = 50$ Hz and  $V_{dc} = 200$ V; (a) Conventional SVM method (b) Proposed HSVM.

three-phase output line voltage and phase current waveforms of the inverter for  $m_a = 0.9$  at 5Amps Load. Similarly, Fig.20 and Fig.21 shows the inverter output voltage and current for  $m_a = 0.8$  and  $m_a = 0.9$ . From the results, it is observed that the output current waveform of the inverter is maintained with boosting the voltage. With the current control method, the DC-link capacitor balancing is maintained, which helps to utilize the maximum inverter DC-link voltage with better harmonics profile on inverter voltage and current waveforms.

In order to validate the features such as low current THD and low NPF, the experimentation is carried out for conventional and proposed HCC based SVM. Fig. 22(a) and Fig.22 (b) shows the experimental results of inverter current for conventional and proposed HSVM respectively. Here,

## IEEE Access

**FIGURE 23.** Experimental results for actual inverter current, reference current and THD spectra at  $f_0 = 50$ Hz and  $V_{dc} = 200$ V; (a) Conventional Z source SVPWM method, (b) HSVM.

FIGURE 24. Experimental results;  $V_{\text{line}}(V_{\text{AB}})$  THD spectra and  $I_{\text{Aphase}}$  THD spectra of HSVM method.

the HSVM maintains improved the current waveform in all the three-phases compared with the conventional SVPWM

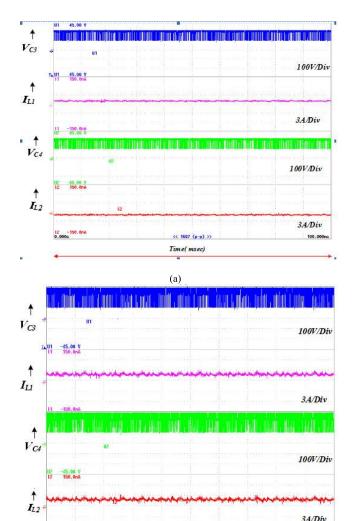

**FIGURE 25.** Experimental results; (a).  $V_{C3}$ ,  $V_{C4}$ ,  $I_{L1}$ ,  $I_{L2}$  during the lower STinterval and (b).  $V_{C3}$ ,  $V_{C4}$ ,  $I_{L1}$ ,  $I_{L2}$  during the higher ST interval.

(b)

<< 1602 (p-p) >

Time(msec)

topology. The Fig.23 (a) and Fig.23 (b) shows the experimental results of inverter current harmonics spectra for conventional and proposed HSVM. From the results, the proposed HSVM is having a minimal current THD spectrum as 1.2%, whereas a conventional method current THD spectrum is considerably high (5.4%) compare to HSVM. The Fig. 24 shows the experimental Voltage THD spectra and current THD spectra. By comparing the simulation results of current THD(1.16%), the experimental result of current THD(1.2%) is high due to the non- linear elements selection for Z network (L and C values) in real time.

The Fig. 25 (a) and (b) shows the impedance network capacitor voltages (C<sub>3</sub> and C<sub>4</sub>) and inductor currents (L<sub>1</sub> and L<sub>2</sub>) during lower and higher ST duty respectively. In the same operating condition, when  $m_a = 0.9$ , the inverter DC-link capacitor (C<sub>1</sub> and C<sub>2</sub>) voltages, V<sub>C1</sub> and V<sub>C2</sub> are measured and compared for conventional and

100 0

FIGURE 26. Experimental results of Z-NPC-MLI voltage across DC-link capacitors; (a) conventional Z source SVPWM method, (b) HSVM.

proposed HSVM and, they are shown in Fig. 26 (a) and Fig.26 (b) respectively. In conventional method, the capacitors voltages ( $V_{C1} = 110.6V$  and  $V_{C2} = 90.4V$ ) are fluctuating largely which causes the DC-link (neutral point) unbalancing (the NPF is calculated as 10.6%). This fluctuation causes the higher current THD. However, the proposed HSVM perform with capacitor balancing ( $V_{C1} = 101.2V$  and  $V_{C2} = 98.8V$ ) with the NP fluctuation is 1.2%, which helps to utilize the maximum inverter DC-link voltage with better harmonics profile on inverter voltage and current waveforms. Fig. 27 shows the inverter voltage and current with  $m_a = 0.9$  at  $f_o = 50Hz$ .

Based on the experimental results, during the steady state and transient conditions, the proposed HSVM control for Z-NPC MLI has a low value of NPF, and hence, the NP balancing is satisfied. The proposed HSVM can be used for other type of Z-source MLI. The proposed current controller and PWM functioned healthy with inverter and grid differ-

FIGURE 27. Experimental results for inverter voltage and current with 0.9 m<sub>a</sub> at  $f_0 = 50$ Hz.

FIGURE 28. Experimental results; Phasor diagram of inverter.

**FIGURE 29.** Experimental results - Common-mode voltage for  $m_a = 0.85$ .

ent operating condition. The observed inverter voltage and current to synchronize with grid is shown in Fig. 28. Here, the current and voltage is maintaining the grid frequency.

The Fig.29 common-mode voltage presented for  $m_a = 0.85$ . From that results it is understood the common-mode voltage is maintaining as  $V_{dc}/2$ . The CVM is maintained for all modulation indices as  $V_{dc}/2$ . The European efficiency of the inverter is calculated as 94.6%.

| TABLE 3. | Performance comparisons of conventional SVM and HSVM |

|----------|------------------------------------------------------|

| methods. |                                                      |

| Method             | Inverter Current<br>THD | Neutral point<br>Fluctuation |

|--------------------|-------------------------|------------------------------|

| Conventional SVPWM | 5.4%                    | 10.6%                        |

| Proposed HSVM      | 1.2%                    | 1.2%                         |

#### C. COMPARISON OF CONVENTIONAL Z SOURCE SVPWM AND PROPOSED HSVM

The proposed HSVM uses minimal ST compare to conventional Z source SVPWM [8], [11], [13], [14]. In view of the inverter performance, the proposed HSVM is maintaining the  $I_{THD}(1.2\%)$ , and NPF (1.2%) which is very minimal. Comparison of conventional SVPWM and proposed HSVM is presented in Table 3.

#### **V. CONCLUSION**

In this paper the three-level Z source NPC-MLI has investigated for PV tied grid connected system. Further also developed the PV tied grid connected system with hysteresis current control combined Z source SVPWM is known as HSVM is developed. The proposed HSVM uses minimal ST compares to conventional Z source SVPWM. In addition the proposed HSVM eliminates the low frequency oscillations using suitable ST (Upper and Lower ST), with regular switching events, which ensures the neutral point DC-link capacitors balancing along with current control. The HSVM maintains the volt-second and inverter voltage boosting competence irrespective of the angular location of the reference vector throughout the inverter operation. A 2 kWp solar panels attached three-phase three-level IGBT based Z-NPC-MLI grid connected system is established with Xilinx family FPGA SPARTAN-6 controller. From the results, it shows that the performance of proposed method is superior than compare to conventional Z source SVPWM in terms of Neutral point fluctuation, current control capability and better harmonic performance. This proposed HSVM method well suited for wind tied inverters, industrial and Electrical vehicles motor applications.

#### REFERENCES

- Z. Dobrotkova, K. Surana, and P. Audinet, "The price of solar energy: Comparing competitive auctions for utility-scale solar PV in developing countries," *Energy Policy*, vol. 118, pp. 133–148, Jul. 2018.

- [2] R. Teichmann and S. Bernet, "A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications," *IEEE Trans. Ind. Appl.*, vol. 41, no. 3, pp. 855–865, May/Jun. 2005.

- [3] F. Z. Peng, "Z-source inverter," *IEEE Trans. Ind. Appl.*, vol. 39, no. 2, pp. 504–510, Mar./Apr. 2003.

- [4] N. Yadaiah, A. S. Kumar, and Y. M. Reddy, "DSP based control of constant frequency and average current mode of boost converter for power factor correction (PFC)," in *Proc. Int. Conf. Adv. Power Convers. Energy Technol.* (APCET), Aug. 2012, pp. 1–6.

- [5] W. Liu, Y. Yang, T. Kerekes, and F. Blaabjerg, "Generalized space vector modulation for ripple current reduction in quasi-Z-source inverters," *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 1730–1741, Feb. 2021.

- [6] F. Gao, P. C. Loh, F. Blaabjerg, and D. M. Vilathgamuwa, "Dual Z-source inverter with three-level reduced common-mode switching," *IEEE Trans. Ind. Appl.*, vol. 43, no. 6, pp. 1597–1608, Dec. 2007.

- [7] Y. P. Siwakoti, F. Z. Peng, F. Blaabjerg, P. C. Loh, and G. E. Town, "Impedance-source networks for electric power conversion Part I: A topological review," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 699–716, Feb. 2015.

- [8] D. Yu, Q. Cheng, J. Gao, F. Tan, and Y. Zhang, "Three-level neutral-pointclamped quasi-Z-source inverter with reduced Z-source capacitor voltage," *Electron. Lett.*, vol. 53, no. 3, pp. 185–187, Feb. 2017.

- [9] S. Bayhan and H. Komurcugil, "A sliding-mode controlled singlephase grid-connected quasi-Z-source NPC inverter with double-line frequency ripple suppression," *IEEE Access*, vol. 7, pp. 160004–160016, 2019.

- [10] F. Gao, P. C. Loh, F. Blaabjerg, and D. M. Vilathgamuwa, "Performance evaluation of three-level Z-source inverters under semiconductorfailure conditions," *IEEE Trans. Ind. Appl.*, vol. 45, no. 3, pp. 971–981, May/Jun. 2009.

- [11] P. C. Loh, S. W. Lim, F. Gao, and F. Blaabjerg, "Three-level Z-source inverters using a single LC impedance network," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 706–711, Mar. 2007.

- [12] R. K. Pongiannan, S. Paramasivam, and N. Yadaiah, "Dynamically reconfigurable PWM controller for three-phase voltage-source inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1790–1799, Jun. 2011.

- [13] P. C. Loh, F. Gao, F. Blaabjerg, S. Y. C. Feng, and K. N. J. Soon, "Pulsewidth-modulated Z-source neutral-point-clamped inverter," *IEEE Trans. Ind. Appl.*, vol. 43, no. 5, pp. 1295–1308, Sep./Oct. 2007.

- [14] F. B. Effah, P. Wheeler, J. Clare, and A. Watson, "Space-vector-modulated three-level inverters with a single Z-source network," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2806–2815, Jun. 2013.

- [15] S. V. Araujo, P. Zacharias, and R. Mallwitz, "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 9, pp. 3118–3128, Sep. 2010.

- [16] W. Li, Y. Gu, H. Luo, W. Cui, X. He, and C. Xia, "Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression," *IEEE Trans. Ind. Electron.*, vol. 62, no. 7, pp. 4537–4551, Jul. 2015.

- [17] T. Kerekes, R. Teodorescu, M. Liserre, C. Klumpner, and M. Sumner, "Evaluation of three-phase transformerless photovoltaic inverter topologies," *IEEE Trans. Power Electron.*, vol. 24, no. 9, pp. 2202–2211, Sep. 2009.

- [18] P. Chaparala, E. Li, and S. Bhola, "Reliability qualification of photovoltaic smart panel electronics," in *Proc. 17th IEEE Int. Symp. Phys. Failure Anal. Integr. Circuits*, Jul. 2010, pp. 1–4.

- [19] M. P. Kazmierkowski and L. Malesani, "Current control techniques for three-phase voltage-source PWM converters: A survey," *IEEE Trans. Ind. Electron.*, vol. 45, no. 5, pp. 691–703, Oct. 1998.

- [20] M. A. Rahman, T. S. Radwan, A. M. Osheiba, and A. E. Lashine, "Analysis of current controllers for voltage-source inverter," *IEEE Trans. Ind. Electron.*, vol. 44, no. 4, pp. 477–485, Aug. 1997.

- [21] A. Shukla, A. Ghosh, and A. Joshi, "Hysteresis modulation of multilevel inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1396–1409, May 2011.

- [22] C. Bharatiraja, S. Jeevananthan, R. Latha, and V. Mohan, "Vector selection approach-based hexagonal hysteresis space vector current controller for a three phase diode clamped MLI with capacitor voltage balancing," *IET Power Electron.*, vol. 9, no. 7, pp. 1350–1361, Jun. 2016.

- [23] T. Ghennam, E. M. Berkouk, and B. Francois, "A novel space-vector current control based on circular hysteresis areas of a three-phase neutralpoint-clamped inverter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2669–2678, Aug. 2010.

- [24] C. Bharatiraja, S. Jeevananthan, and R. Latha, "FPGA based practical implementation of NPC-MLI with SVPWM for an autonomous operation PV system with capacitor balancing," *Int. J. Electr. Power Energy Syst.*, vol. 61, pp. 489–509, Oct. 2014.

- [25] C. Wang and Y. Li, "Analysis and calculation of zero-sequence voltage considering neutral-point potential balancing in three-level NPC converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2262–2271, Jul. 2010.

- [26] H. Zhang, S. J. Finney, A. Massoud, and B. W. Williams, "An SVM algorithm to balance the capacitor voltages of the three-level NPC active power filter," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2694–2702, Nov. 2008.

- [27] J.-S. Lee and K.-B. Lee, "New modulation techniques for a leakage current reduction and a neutral-point voltage balance in transformerless photovoltaic systems using a three-level inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1720–1732, Apr. 2014.

- [28] X. Xing, C. Zhang, A. Chen, J. He, W. Wang, and C. Du, "Space-vector-modulated method for boosting and neutral voltage balancing in Z-source three-level T-type inverter," *IEEE Trans. Ind. Appl.*, vol. 52, no. 2, pp. 1621–1631, Mar./Apr. 2016.

- [29] B. Chokkalingam, S. Padmanaban, P. Siano, Z. Leonowicz, and A. Iqbal, "A hexagonal hysteresis space vector current controller for single Z-source network multilevel inverter with capacitor balancing," in *Proc. IEEE Int. Conf. Environ. Electr. Eng., IEEE Ind. Commercial Power Syst. Eur.* (*EEEIC/L&CPS Europe*), Jun. 2017, pp. 1–6.

- [30] D. Shuai and Z. Qianfan, "Analysis and control of current ripples of Z-source inverters," *IEEE Access*, vol. 8, pp. 41220–41228, 2020.

- [31] H. Rostami, M. R. Azizian, S. A. Davari, and S. M. Rad, "Single-phase three-level neutral-point-clamped inverter based on modified Z-source network with reduced voltage stress on capacitors," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 1, pp. 980–993, Feb. 2021.

- [32] F. Wang, Z. Li, and X. Tong, "Modified predictive control method of three-level simplified neutral point clamped inverter for common-mode voltage reduction and neutral-point voltage balance," *IEEE Access*, vol. 7, pp. 119476–119485, 2019.

- [33] N. Kalaiarasi, S. D. Subhranshu, S. Paramasivam, and C. Bharatiraja, "Investigation on ANFIS aided MPPT technique for PV fed ZSI topologies in standalone applications," *J. Appl. Sci. Eng.*, vol. 24, no. 2, pp. 261–269, Apr. 2021.

**SURESH KUMAR ANNAM** received the B.Tech. degree in 2005 and the M.Tech. degree from the JNTU College of Engineering, Anantapur, India, in 2007. He is currently an Assistant Professor of electrical and electronics engineering with the Samskruti College of Engineering and Technology, Ghatkesar, Hyderabad. His research interests include power electronics, fuzzy logic, and ac drives.

**R. K. PONGIANNAN** received the B.E. degree from the Coimbatore Institute of Technology, Coimbatore, India, in 1995, the M.E. degree from the PSG College of Technology, Coimbatore, in 2004, and the Ph.D. degree from Jawaharlal Nehru Technological University, Hyderabad (JNTUH), India, in 2012. He is currently a Professor with the Department of Electrical and Electronics Engineering, Kattankulathur Campus, SRM Institute of Science and Technology (formerly

known as SRM University). He is the author or a coauthor of more than 30 papers in international journals and conferences. His research interests include power electronics, ac drives, and embedded systems. He is also a Reviewer of IEEE TRANSACTIONS and *Inderscience* Journals.

**N. YADAIAH** (Senior Member, IEEE) received the B.E. degree in electrical engineering from the College of Engineering, Osmania University, Hyderabad, in 1988, the M.Tech. degree from the Indian Institute of Technology Kharagpur, India, in 1991, and the Ph.D. degree from the Jawaharlal Nehru Technological University, Hyderabad (JNTUH), India, in 2000. He has visited the University of Alberta, Canada, as a Visiting Professor, from May 2007 to July 2007. He is currently a

Professor with the Electrical and Electronics Engineering, JNTUH College of Engineering Hyderabad. He has completed two research projects and holding one research project. He is the author or a coauthor of 135 publications. His research interests include neural networks, fuzzy logic systems, estimation techniques, AI techniques to power system and drives applications, fault detection techniques, system identification, and adaptive control. He received the Young Scientist Fellowship in 1999, the Engineer of Year Award-2014 from the Institution of Engineers of India, the Outstanding Reviewer Award of 2014 by Elsevier, the Telangana Meritorious State Teacher Award-2015, and the 43rd Systems Society of India Gold Medal 2019. He is also a Reviewer for IEEE, Elsevier, and *Inderscience* journals.