# K-DELTA-1-SIGMA MODULATORS FOR WIDEBAND ANALOG-TO-DIGITAL CONVERSION

by

Vishal Saxena

# A dissertation

submitted in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

Boise State University

©2010

Vishal Saxena

ALL RIGHTS RESERVED

## BOISE STATE UNIVERSITY GRADUATE COLLEGE

## DEFENSE COMMITTEE AND FINAL READING APPROVALS

## of the dissertation submitted by

#### Vishal Saxena

Dissertation Title: K-Delta-1-Sigma Modulators for Wideband Analog-to-Digital

Conversion

Date of Final Oral Examination: 09 April 2009

The following individuals read and discussed the dissertation submitted by student Stephanie Stacey Starr, and they also evaluated her presentation and response to questions during the final oral examination. They found that the student passed the final oral examination, and that the dissertation was satisfactory for a doctoral degree and ready for any final modifications that they explicitly required.

R. Jacob Baker, Ph.D. Chair, Supervisory Committee

Jim Browning, Ph.D. Member, Supervisory Committee

Kris Campbell, Ph.D. Member, Supervisory Committee

John Chiasson, Ph.D. Member, Supervisory Committee

Wan Kuang, Ph.D. Member, Supervisory Committee

TBD External Examiner

The final reading approval of the dissertation was granted by R. Jacob Baker, Ph.D., Chair of the Supervisory Committee. The dissertation was approved for the Graduate College by John R. Pelton, Ph.D., Dean of the Graduate College.

## **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my parents and siblings for their extreme patience and unconditional support during the course of my graduate studies. I also thank my adviser Dr. Jake Baker for the opportunity to research on delta-sigma data converters and for the motivation to further my academic interests. Further, I would like to thank Dr. Jim Browning, Dr. Kris Campbell, Dr. John Chiasson, Dr. Wan Kuang, and Dr. Peter Stubberud for being on my dissertation committee. I express my gratitude towards Dr. Thad Welch, Dr. Bill Knowlton, Dr. Nader Rafla and Dr. for their encouragement and support. I acknowledge the support of Geng Zheng and Kaijun Li for their help in chip layout and testing. I would thank Terry Gafron and David Moore for the help with packaging and wire bonding of the fabricated chips. Special thanks to Sakkarpani Balagopal and Mahyar Arimand Rad for their help in proof-reading the dissertation manuscript and presentation dry-runs. I would also like to single out Rajesh Krishnamachari, Venkatesh Acharya, Vijay Mahadevan and Divyakumar Kesarwani for the extended discussions. Thanks are due aplenty to Shantanu Gupta, Armand Bregaj, Rahul Mhatre, Samir Patel, Pulok Pattanaik, Sanghyun Park, Ahmed Oteafy, Hidayatullah Ahsan, Avinash Rajagiri, Harikrishna Rapole amongst several others for being a helpful company at Boise. I express my indebtedness to Soham Pathak, Vinky Pathak, Ba, Keith Montgomery, Vipul Patel, Russ Romano, Bipin Dama, Kal Shastri,

Mark Webbster, and Mark Kerestes for the memorable stay in Allentown, PA, during my summer internship at Lightwire. Lastly but not the least, thanks to Chandra Bhushan Prakash, Karthick Santhanam, Hariharan Rajendran, Mark McDermott, Dr. Jacob Abraham, Dr. Ranjit Gharpurey, Saurabh Singh, Anantha Nag, and many others at UT Austin for their help and support during my stay at Austin.

## **ABSTRACT**

As CMOS technology scales, the transistor speed increases enabling higher speed communications and more complex systems. These benefits come at the cost of decreasing inherent device gain, increased transistor leakage currents, and additional mismatches due to process variations. All of these drawbacks affect the design of high-resolution analog-to-digital converters (ADCs) in nano-CMOS processes. To move towards an ADC topology useful in these small processes a first-order K-Delta-1-Sigma (KD1S) modulator-based ADC was proposed. The KD1S topology employs inherent time-interleaving with a shared integrator and *K*-quantizing feedback paths and can potentially achieve significantly higher conversion bandwidths when compared to the traditional switched-capacitor delta-sigma ADCs. The shared integrator in the KD1S modulator settles over a half the clock period and the op-amp is designed to operate at the base clock frequency.

In this dissertation, the first-order KD1S modulator topology is analyzed for the effects of the non-idealities introduced by the *K*-path operation of the switched-capacitor integrator. Then, the concept of KD1S modulator is extended to higher-order modulators in order to achieve superior noise-shaping performance. A systematic synthesis method has been developed to design and simulate higher-order KD1S modulators at the system level. In order to demonstrate the developed theory, a prototype second-order KD1S modulator has been designed and fabricated in a 500-nm CMOS technology.

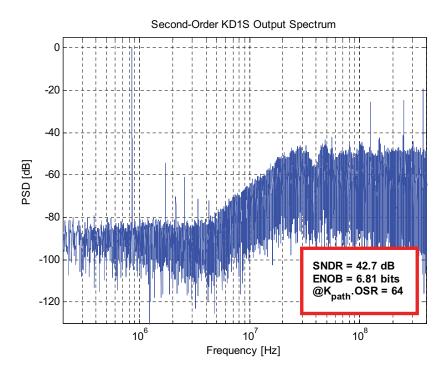

The second-order KD1S modulator exhibits wideband noise-shaping with an SNDR of 42.7 dB or 6.81 bits in resolution for  $K_{path} = 8$  paths, an effective sampling rate of  $f_{s,new} = 800$  MHz, effective oversampling ratio  $K_{path} \cdot OSR = 64$  and a signal bandwidth of 6.25 MHz. The second-order KD1S modulator consumes an average current of 3.0 mA from the 5 V supply and occupies an area of 0.55  $mm^2$ .

# CONTENTS

| A  | cknov    | vledgem       | nents                                    |   | vi    |

|----|----------|---------------|------------------------------------------|---|-------|

| Al | bstrac   | et            |                                          |   | viii  |

| Li | ist of   | <b>Fables</b> |                                          |   | XV    |

| Li | ist of l | Figures       |                                          | X | xviii |

| 1  | Intr     | oductio       | o <b>n</b>                               |   | 1     |

|    | 1.1      | Motiva        | ation                                    |   | 3     |

|    | 1.2      | Disser        | rtation Organization                     |   | 5     |

| 2  | Tim      | e-Interl      | leaved Analog-to-Digital Converters      |   | 7     |

|    | 2.1      | Time-         | Interleaved Analog-to-Digital Converters |   | 7     |

|    | 2.2      | Non-u         | niformly Sampled Sinusoidal              |   | 10    |

|    |          | 2.2.1         | Path Offset Errors                       |   | 13    |

|    |          | 2.2.2         | Gain Mismatch Errors                     |   | 13    |

|    |          | 2.2.3         | Phase Skew Errors                        |   | 16    |

|    |          | 2.2.4         | Errors Due to Bandwidth Mismatch         |   | 18    |

|    | 2.3      | Oversa        | ampling in Time-Interleaved ADCs         |   | 19    |

|    | 2.4      | Rando         | omization and Calibration                |   | 20    |

|   | 2.5 | Conclu  | asion                                                | 20 |

|---|-----|---------|------------------------------------------------------|----|

| 3 | Wid | eband A | Analog-to-Digital Converters                         | 21 |

|   | 3.1 | Digital | Calibration of ADCs                                  | 21 |

|   | 3.2 | Delta-S | Sigma Modulation                                     | 24 |

|   |     | 3.2.1   | First-order Delta-Sigma Modulator                    | 26 |

|   |     | 3.2.2   | Second-Order Delta-Sigma Modulator                   | 28 |

|   | 3.3 | Prior a | nd Current Art in Wideband Delta-Sigma Modulators    | 31 |

|   |     | 3.3.1   | Double-Sampling DSM                                  | 31 |

|   |     | 3.3.2   | Time-Interleaving of Delta-Sigma Modulators          | 37 |

|   |     | 3.3.3   | Parallel Delta-Sigma Modulators                      | 39 |

|   |     | 3.3.4   | Wideband Continuous-Time Delta-Sigma Modulators      | 44 |

|   | 3.4 | Conclu  | ision                                                | 47 |

| 4 | The | K-Delta | a-1-Sigma Modulator                                  | 49 |

|   | 4.1 | Switch  | ed-Capacitor Integrator (SCI) Dynamics               | 49 |

|   | 4.2 | The K-  | -Path Switched-Capacitor Integrator ( <i>K</i> -SCI) | 53 |

|   |     | 4.2.1   | Path Mismatch in the <i>K</i> -path SC Integrator    | 61 |

|   | 4.3 | The Fi  | rst-Order K-Delta-1-Sigma Modulator                  | 62 |

|   |     | 4.3.1   | Ideal Simulation Results                             | 65 |

|   |     | 4.3.2   | Noise Flow in the KD1S Modulator                     | 66 |

|   | 4.4 | Effects | s of Circuit Nonidealities in KD1S                   | 68 |

|   |     | 441     | Finite On-amp Unity-Gain Frequency (f)               | 68 |

|   |      | 4.4.2     | Finite Op-amp Gain                                | 72  |

|---|------|-----------|---------------------------------------------------|-----|

|   |      | 4.4.3     | Slewing in the Op-amp                             | 74  |

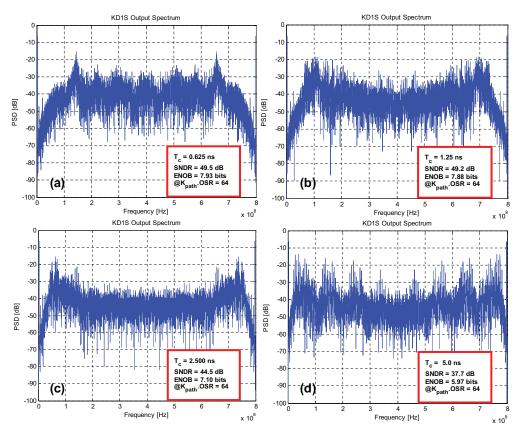

|   |      | 4.4.4     | Real Quantizer Effects                            | 78  |

|   |      | 4.4.5     | Capacitor Mismatch, Phase Skew and Noise Folding  | 87  |

|   |      | 4.4.6     | Clock Jitter                                      | 92  |

|   | 4.5  | Noise     | Effects in a KD1S Modulator                       | 95  |

|   | 4.6  | Conclu    | usion                                             | 106 |

| 5 | A Se | econd-O   | Order KD1S Modulator Topology                     | 108 |

|   | 5.1  | A Seco    | ond-Order KD1S Modulator                          | 108 |

|   |      | 5.1.1     | Integrator Saturation and Dynamic Range Scaling   | 113 |

|   |      | 5.1.2     | Ideal Simulation Results                          | 115 |

|   | 5.2  | Effects   | s of the circuit non-idealities                   | 117 |

|   |      | 5.2.1     | Finite Op-amp Unity-Gain Frequency $(f_{un})$     | 117 |

|   |      | 5.2.2     | Finite Op-amp Gain                                | 121 |

|   |      | 5.2.3     | Real Quantizer Effects                            | 122 |

|   |      | 5.2.4     | Capacitor Mismatch and Clock Skew                 | 130 |

|   |      | 5.2.5     | Clock Jitter                                      | 132 |

|   | 5.3  | Conclu    | asion                                             | 132 |

| 6 | Synt | thesis of | f Higher-Order KD1S Modulators                    | 133 |

|   | 6.1  | Higher    | r-order Delta-Sigma Modulators                    | 133 |

|   |      | 6.1.1     | Stability Considerations and Multi-Bit Modulators | 136 |

|   | 6.2  | NTFP     | ole and Zero Optimization                              | 141 |

|---|------|----------|--------------------------------------------------------|-----|

|   | 6.3  | Loop-f   | filter Architectures                                   | 142 |

|   | 6.4  | Synthe   | esis Procedure for KD1S Modulators                     | 146 |

|   |      | 6.4.1    | The ABCD Matrix                                        | 147 |

|   |      | 6.4.2    | <i>K</i> -path Integrator Modeling                     | 149 |

|   |      | 6.4.3    | The State-Space Embedding Method                       | 153 |

|   |      | 6.4.4    | Dynamic Range Scaling                                  | 156 |

|   |      | 6.4.5    | Mapping to a Loop-filter Architecture                  | 157 |

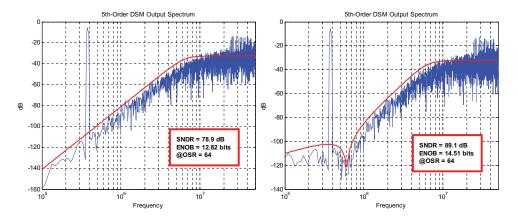

|   | 6.5  | Simula   | ation Results                                          | 159 |

|   |      | 6.5.1    | A Second-order CIFB KD1S Modulator with NTF Zero Opti- |     |

|   |      |          | mization                                               | 159 |

|   |      | 6.5.2    | A Third-order CIFF KD1S Modulator                      | 161 |

|   | 6.6  | Compa    | arison with conventional DSMs                          | 163 |

|   | 6.7  | Conclu   | usion                                                  | 165 |

| 7 | Chip | o Design | n and Testing                                          | 166 |

|   | 7.1  | Introdu  | uction                                                 | 166 |

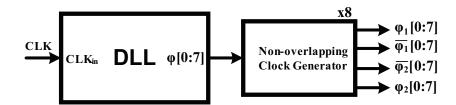

|   | 7.2  | Delay-   | Locked Loop for Multi-phase Clock Generation           | 166 |

|   |      | 7.2.1    | Phase Frequency Detector (PFD)                         | 170 |

|   |      | 7.2.2    | Charge Pump and Loop-Filter                            | 173 |

|   |      | 7.2.3    | Voltage-Controlled Delay-Line (VCDL)                   | 174 |

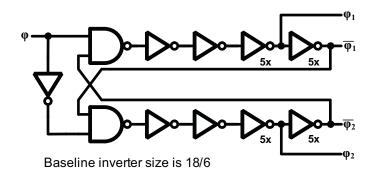

|   |      | 7.2.4    | Non-overlapping clock generator                        | 175 |

|   |      | 7.2.5    | DLL Simulation                                         | 177 |

|    | 7.3   | First-O  | Order KD1S Modulator                | 178 |

|----|-------|----------|-------------------------------------|-----|

|    |       | 7.3.1    | KD1S Output Synchronization         | 179 |

|    | 7.4   | Second   | d-Order KD1S Modulator              | 180 |

|    | 7.5   | KD1S     | Modulator Circuit Blocks            | 181 |

|    |       | 7.5.1    | Switched-Capacitors                 | 181 |

|    |       | 7.5.2    | Op-amps and Bias Generation Circuit | 183 |

|    |       | 7.5.3    | Comparators and Flip-Flop           | 188 |

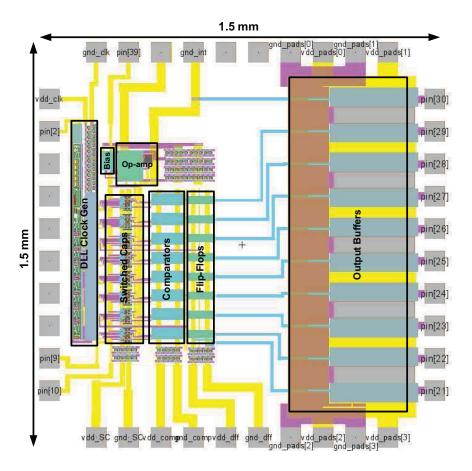

|    | 7.6   | Chip L   | ayouts                              | 190 |

|    | 7.7   | Chip S   | Simulation                          | 193 |

|    |       | 7.7.1    | First-Order KD1S Modulator          | 193 |

|    |       | 7.7.2    | Second-Order KD1S Modulator         | 196 |

|    | 7.8   | Test Se  | etup and Procedure                  | 199 |

|    |       | 7.8.1    | Test Board Design                   | 200 |

|    | 7.9   | Experi   | mental Results                      | 202 |

|    |       | 7.9.1    | Performance                         | 204 |

|    | 7.10  | Conclu   | asion                               | 205 |

| 8  | Conc  | clusions | 5                                   | 206 |

|    | 8.1   | Summa    | ary                                 | 206 |

|    | 8.2   | Future   | Work                                | 208 |

| Re | feren | ces      |                                     | 210 |

8

# LIST OF TABLES

| 5.1 | Comparison of the KD1S Modulator with DT- and CT-DSMs 164                     |

|-----|-------------------------------------------------------------------------------|

| 7.1 | Typical performance of the second-order KD1S modulator (5 V and 25 $^{\circ}$ |

|     | C)                                                                            |

# LIST OF FIGURES

| 1.1 | Classification of Analog-to-Digital Converters based upon their resolu-        |    |

|-----|--------------------------------------------------------------------------------|----|

|     | tion and conversion bandwidth                                                  | 2  |

| 2.1 | Time-interleaved ADCs and the corresponding clock phases                       | 8  |

| 2.2 | Sampling of an input sine wave by a time-interleaved ADC                       | 9  |

| 2.3 | Spectrum of a non-uniformly sampled complex sinusoid                           | 12 |

| 2.4 | ENOB as a function of the standard deviation of the gain mismatch with         |    |

|     | <i>M</i> ADCs in parallel                                                      | 15 |

| 2.5 | ENOB vs clock phase skew for an eight-channel time-interleaved ADC.            |    |

|     | Here, $f_s > 2f_{in}$ , and the ENOB is independent of the sampling frequency. | 18 |

| 3.1 | A 1.5-bit pipelined stage (MDAC) [1]                                           | 22 |

| 3.2 | Diagram showing the concept of digital calibration of a pipelined ADC          |    |

|     | in [1]                                                                         | 24 |

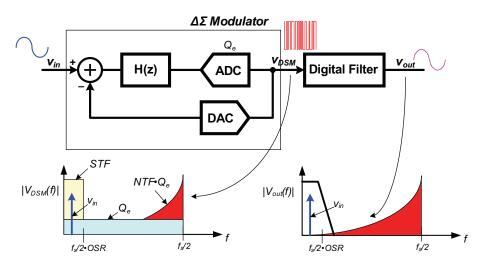

| 3.3 | Block diagram of an ADC employing Delta Sigma Modulation                       | 25 |

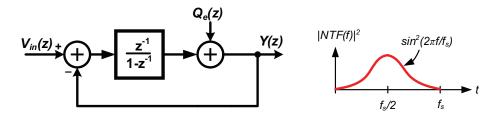

| 3.4 | Block diagram and noise transfer function of a first-order delta-sigma         |    |

|     | modulator                                                                      | 26 |

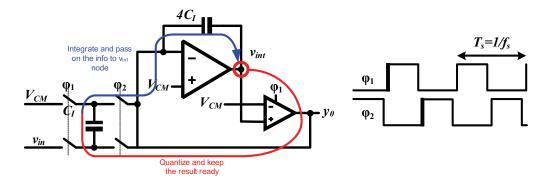

| 3.5 | A first-order discrete-time delta-sigma modulator                              | 27 |

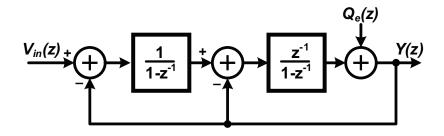

| 3.6 | A discrete-time second-order DSM                                               | 29 |

| 3.7 | A switched-capacitor implementation of the second-order DSM                    | 29 |

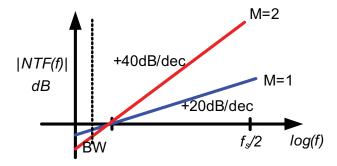

| 3.8  | Comparison of the NTFs of first and second-order DSMs                                 | 30 |

|------|---------------------------------------------------------------------------------------|----|

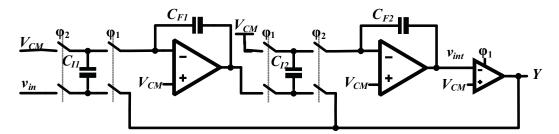

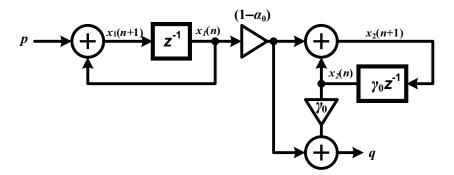

| 3.9  | A first-order delta-sigma modulator employing double-sampling                         | 32 |

| 3.10 | Spectrum (linear and log frequency) for a double-sampling first-order                 |    |

|      | DSM with $f_s = 100$ MHz, $T_c = 5$ ns, op-amp $f_{un} = 3f_s = 300$ MHz, $OSR = 100$ |    |

|      | 16, and $BW = 6.25 \text{ MHz.} \dots$                                                | 33 |

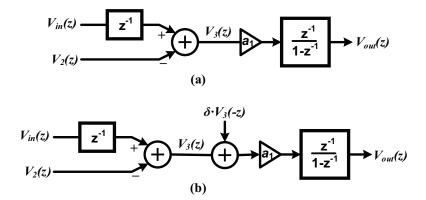

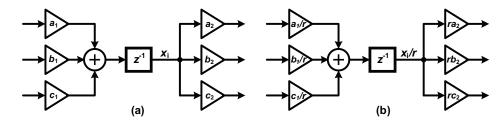

| 3.11 | Signal flow diagram for a double-sampled DSM. (a) case without the                    |    |

|      | path mismatch, and (b) with the folded noise due to the path mismatch                 | 34 |

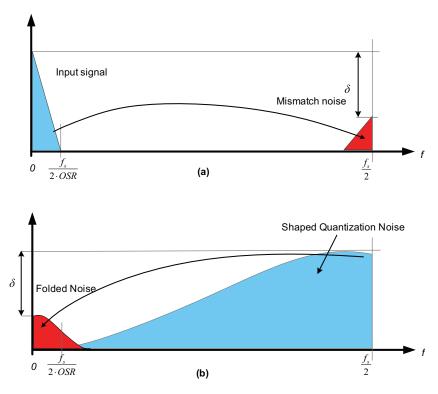

| 3.12 | Noise folding effect due to the path-gain mismatch in a double-sampling               |    |

|      | DSM. (a) Gain mismatch effect on the input path, (b) Gain mismatch                    |    |

|      | effect on the feedback path where the quantization noise is folded back               |    |

|      | into the signal band                                                                  | 37 |

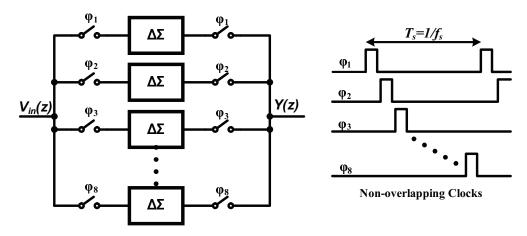

| 3.13 | A time-interleaved delta-sigma modulator array                                        | 38 |

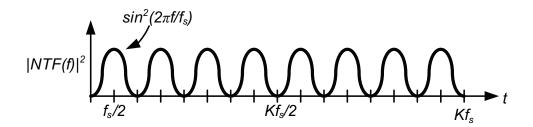

| 3.14 | Noise-shaping for a <i>K</i> -path interleaved delta-sigma modulator                  | 38 |

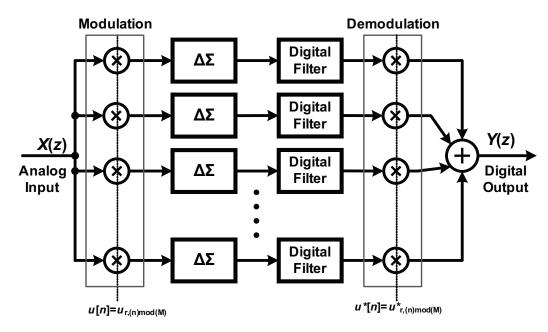

| 3.15 | A generalized block diagram of the parallel delta-sigma ADC employ-                   |    |

|      | ing modulation                                                                        | 40 |

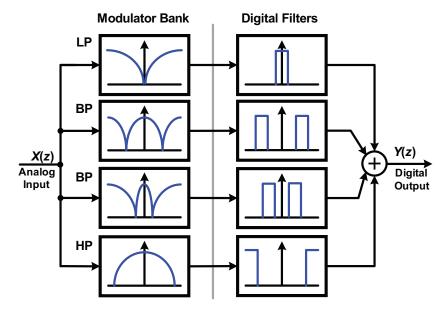

| 3.16 | Block diagram of a four-channel parallel delta-sigma modulator em-                    |    |

|      | ploying frequency band decomposition                                                  | 43 |

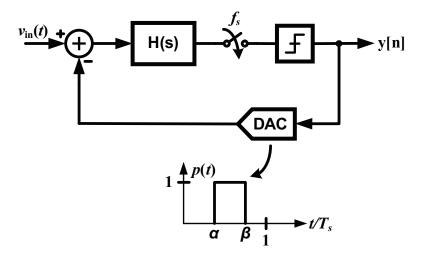

| 3.17 | Block diagram of a continuous-time delta-sigma modulator. Here the                    |    |

|      | feedback DAC pulse shape is shown as a generic rectangular pulse with                 |    |

|      | excess loop delay $(\alpha)$ , encountered in practical CT-DSM designs                | 45 |

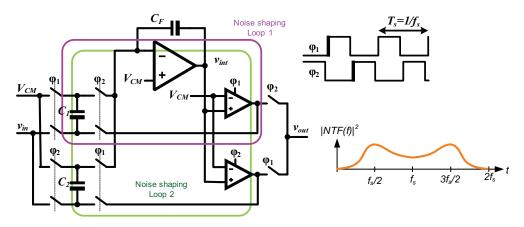

| 3.18 | The architecture of a wideband continuous-time delta-sigma modulator                  |    |

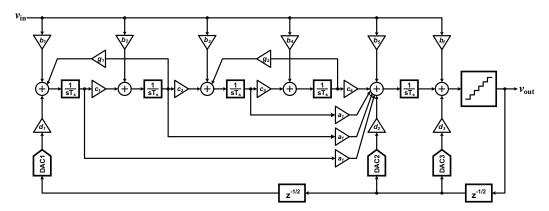

|      | for widehand data conversion                                                          | 46 |

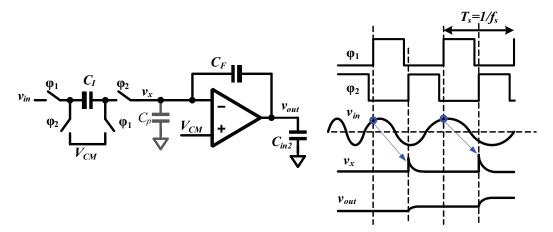

| 4.1 | A switched-capacitor integrator and the waveforms showing its tran-              |    |

|-----|----------------------------------------------------------------------------------|----|

|     | sient dynamics                                                                   | 50 |

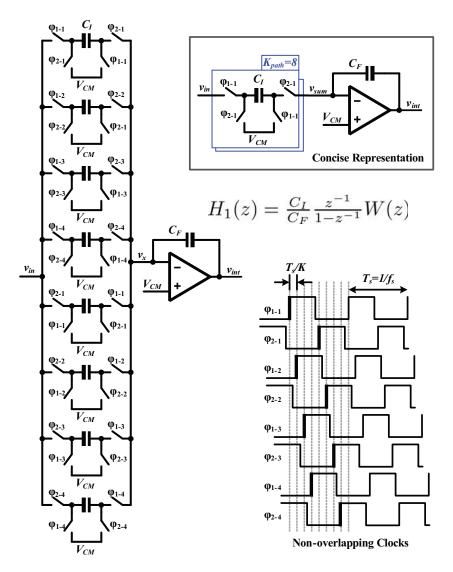

| 4.2 | A K-path switched-capacitor integrator with a shared op-amp with the             |    |

|     | associated time-interleaved clocking scheme. A concise graphical rep-            |    |

|     | resentation for the <i>K</i> -SCI is shown in the inset                          | 54 |

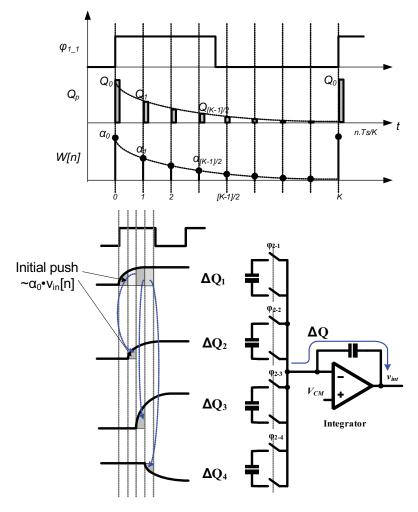

| 4.3 | Illustration of charge-spreading and the equivalent filtering action in a        |    |

|     | <i>K</i> -path SCI                                                               | 56 |

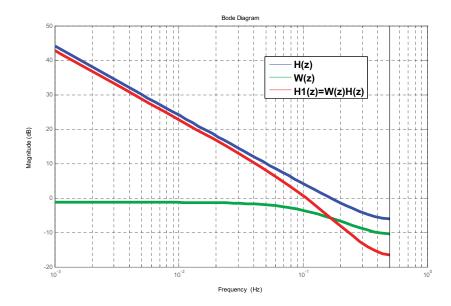

| 4.4 | A plot showing the K-path integrator magnitude response for $f_{un} =$           |    |

|     | 1.5 $f_s$ . Here, $H(z)$ is the near-ideal integrator response, $W(z)$ is the    |    |

|     | response of the charge spreading filter and $H_1(z) = W(z)H(z)$ is the           |    |

|     | response of the <i>K</i> -path integrator                                        | 60 |

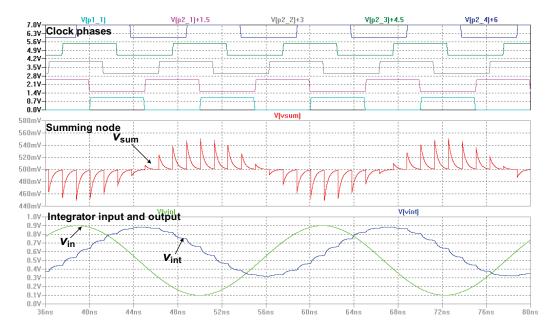

| 4.5 | Transient simulation of a <i>K</i> -path integrator showing the integrator input |    |

|     | and output, the op-amp summing node and the clock phases                         | 61 |

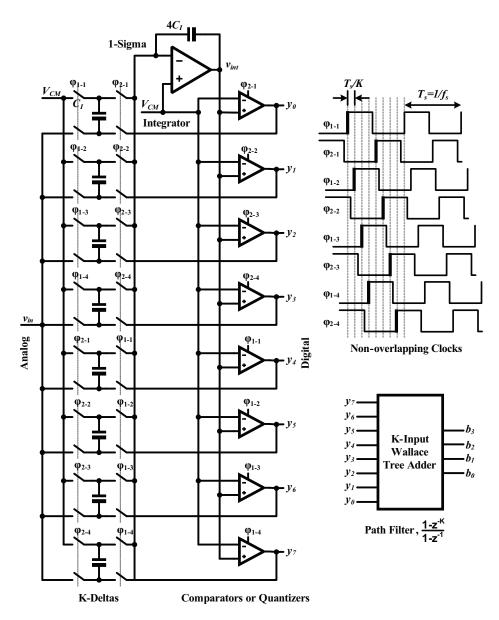

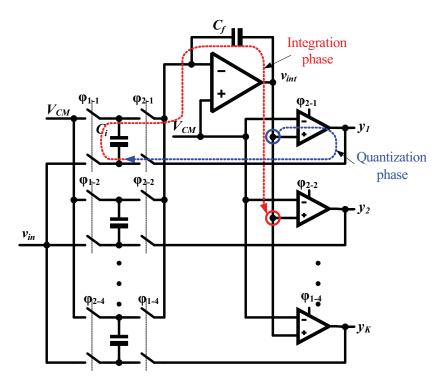

| 4.6 | The <i>K</i> -Delta-1-Sigma modulator topology                                   | 63 |

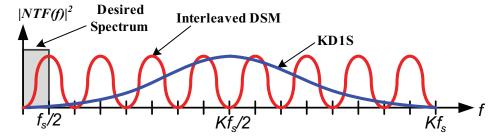

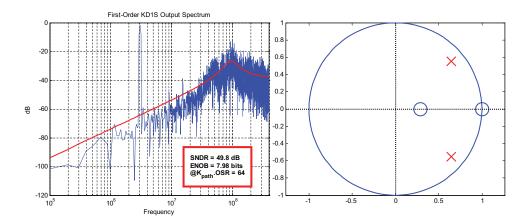

| 4.7 | True wideband noise-shaping using a <i>K</i> -Delta-1-Sigma Modulator            | 65 |

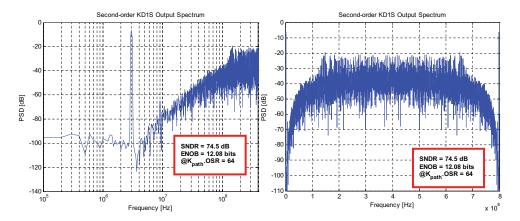

| 4.8 | Simulation results (PSD of the output with linear and log frequency              |    |

|     | axes) for a KD1S modulator with ideal components. Here, $f_s = 100$              |    |

|     | MHz, $K_{path} = 8$ , $f_{s,new} = 800$ MHz, $OSR = 8$ , and $BW = 6.25$ MHz     | 66 |

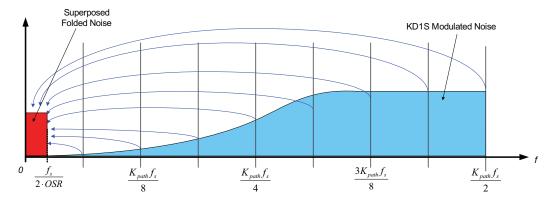

| 10  | Illustration of the noise-shaping flow in a KD1S modulator                       | 67 |

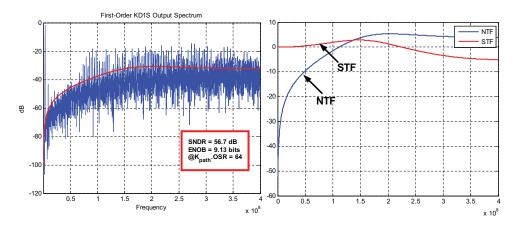

| 4.10 | KD1S noise-shaping with an op-amp with finite unity gain frequency                                                 |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | $(f_{un} = \frac{3}{8}f_{s,new} = 300  MHz)$ . The second plot shows the NTF and STF                               |    |

|      | for the modulator. Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} = 800$ MHz,                                  |    |

|      | OSR = 8, and $BW = 6.25$ MHz                                                                                       | 70 |

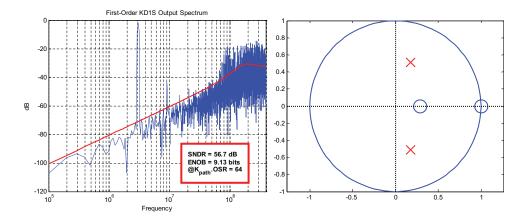

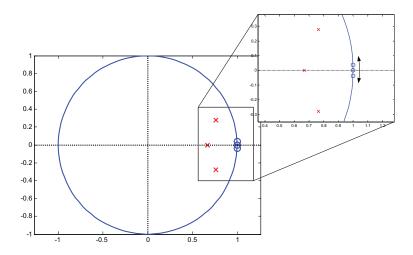

| 4.11 | Simulated PSD of the output and the NTF pole-zero plot for the first-                                              |    |

|      | order KD1S modulator with $f_{s,new} = 800$ MHz, $f_{un} = \frac{3}{8} f_{s,new} = 300$                            |    |

|      | MHz, $K_{path} = 8$ , $OSR = 8$ , and $BW = 6.25$ MHz                                                              | 72 |

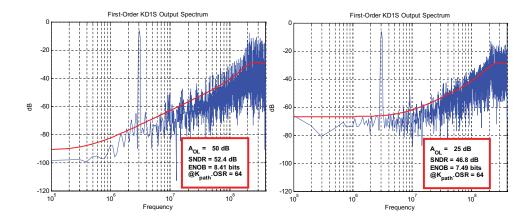

| 4.12 | Simulated NTFs for the first-order KD1S modulator with the op-amp                                                  |    |

|      | open-loop gain $(A_{OL})$ of 50 dB and 25 dB. Again here, $f_{s,new} = 800$                                        |    |

|      | MHz, $f_{un} = \frac{3}{8} f_{s,new} = 300 \text{ MHz}$ , $K_{path} = 8$ , $OSR = 8$ , and $BW = 6.25$             |    |

|      | MHz                                                                                                                | 74 |

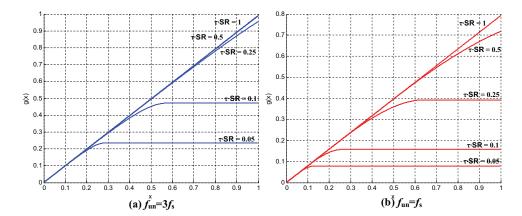

| 4.13 | The behavioral model for the integrator settling with slew-rate limita-                                            |    |

|      | tions. The gain function $g(x)$ is plotted for increasing values of $\tau \cdot SR$                                |    |

|      | and $t_s = T_s/2$                                                                                                  | 76 |

| 4.14 | Slew-rate vs bandwidth contours for the switched-capacitor integrator                                              | 77 |

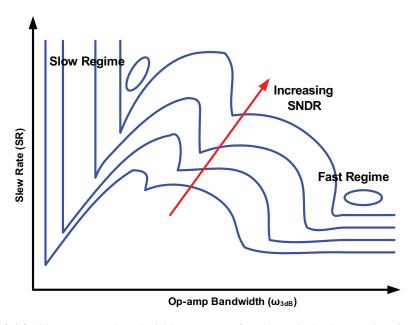

| 4.15 | Illustration of the delay, hysteresis and metastability in a real compara-                                         |    |

|      | tor or quantizer                                                                                                   | 81 |

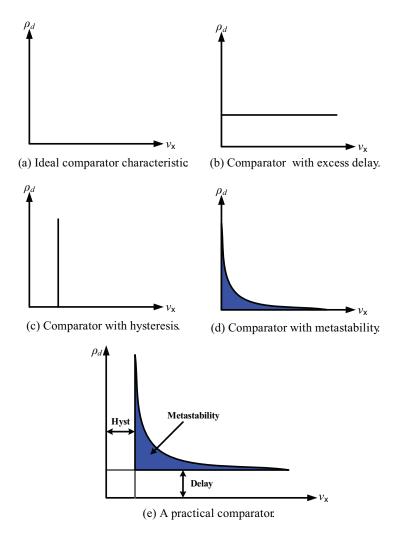

| 4.16 | Effects of comparator delay on the SNR of a first-order KD1S modula-                                               |    |

|      | tor simulated in Spectre with $f_s = 100$ MHz, $f_{un} = 300$ MHz, $K_{path} = 8$ ,                                |    |

|      | OSR = 8, and $BW = 6.25$ MHz. The KD1S modulators were simu-                                                       |    |

|      | lated with a respective clocking scheme to minimize the loop-delay. (a)                                            |    |

|      | $T_c = 625 \text{ ps}$ , (b) $T_c = 1.25 \text{ ns}$ , (c) $T_c = 2.5 \text{ ns}$ , and (d) $T_c = 5.0 \text{ ns}$ | 83 |

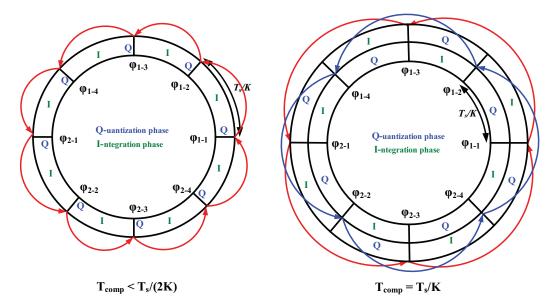

| 4.17 | Circular clock phase diagram for KD1S modulator for two distinct com-                      |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | parator delays                                                                             | 85 |

| 4.18 | Matlab simulated PSD of the output and the NTF pole-zero plot for the                      |    |

|      | first-order KD1S modulator with $f_{s,new} = 800$ MHz, $f_{un} = 300$ MHz,                 |    |

|      | $K_{path} = 8$ , $OSR = 8$ , $BW = 6.25$ , and the comparator delay $T_c = T_s/K_{path} =$ |    |

|      | 1.25 ns                                                                                    | 86 |

| 4.19 | Noise-folding effects in a KD1S modulator due to path gain mismatches.                     |    |

|      | The shaped quantization noise from the frequencies $kf_s$ , $k = 1,K_{path}$               |    |

|      | gets folded into the signal band.                                                          | 88 |

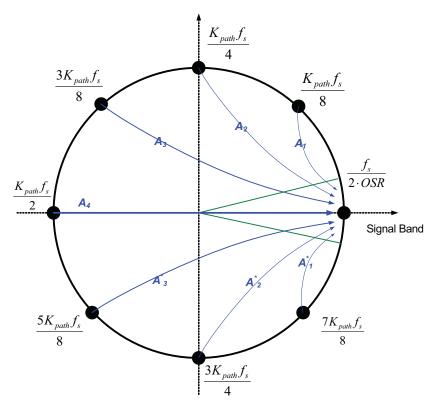

| 4.20 | Graphical illustration of noise folding, in a KD1S modulator with path                     |    |

|      | mismatches, on a <i>z</i> -plane. Here $K_{path} = 8. \dots \dots \dots$                   | 92 |

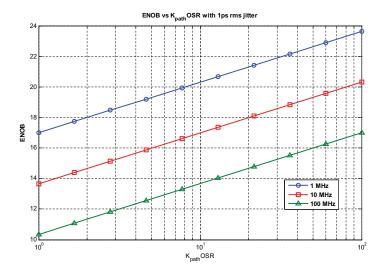

| 4.21 | ENOB vs the effective oversampling ratio for a <i>K</i> -path sampling scheme              |    |

|      | with 1 ps rms clock jitter. The plots are for input frequencies $(f_{in})$ of              |    |

|      | 1 MHz, 10 MHz and 100 MHz. The effective sampling frequency for                            |    |

|      | each of the plots is $f_{s,new} = 2K_{path} \cdot OSR \cdot f_{in}$                        | 94 |

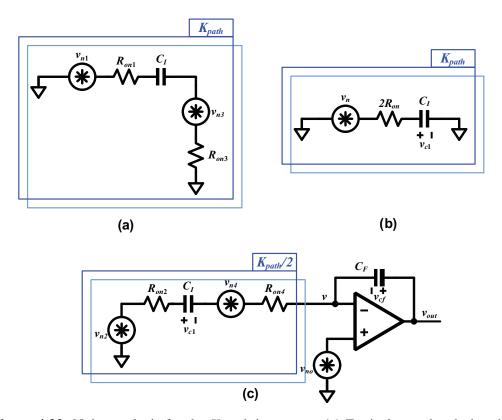

| 4.22 | Noise analysis for the K-path integrator: (a) Equivalent noise during                      |    |

|      | the sampling phase for each of the capacitors. (b) Equivalent noise                        |    |

|      | schematic for (a). (c) Equivalent noise schematic during the integration                   |    |

|      | phase                                                                                      | 99 |

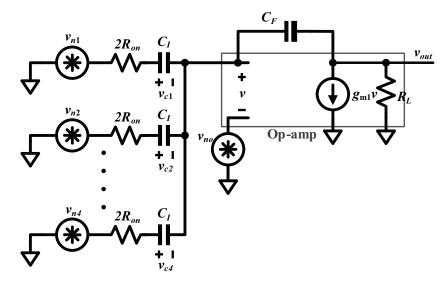

| 4.23 | Equivalent noise schematic during the integration phase with a single-                     |    |

|      | stage op-amp, during the integration phase $\phi_{2-1}$                                    | 01 |

| 4.24 | Noise sources in a first-order KD1S modulator                                              | 05 |

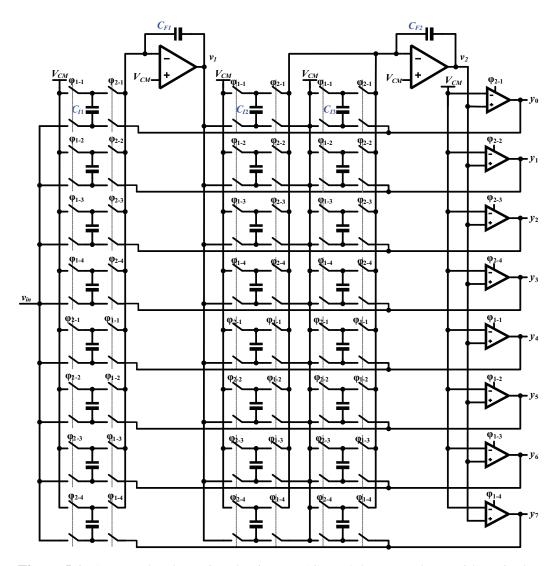

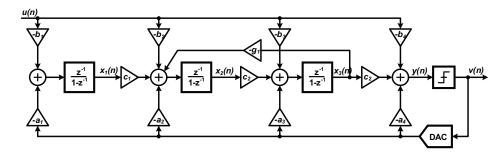

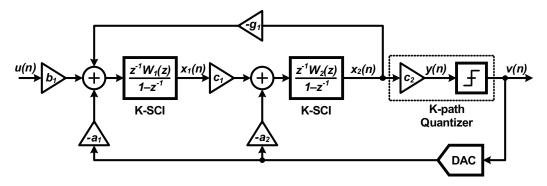

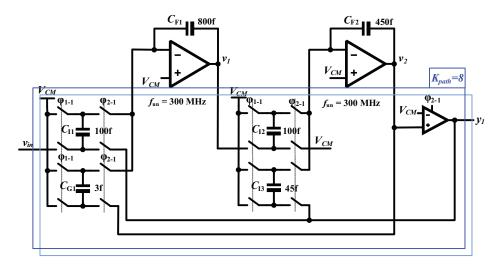

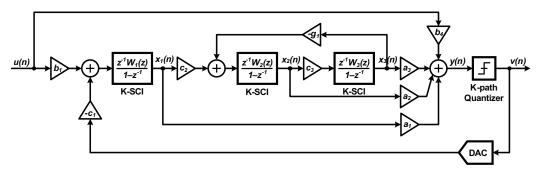

| 5.1 | A second-order noise-shaping KD1S modulator topology with a singly-                                  |     |

|-----|------------------------------------------------------------------------------------------------------|-----|

|     | ended switched-capacitor implementation.                                                             | 109 |

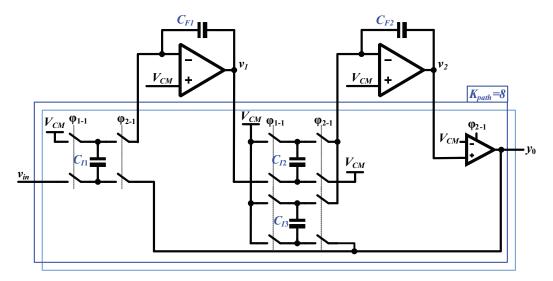

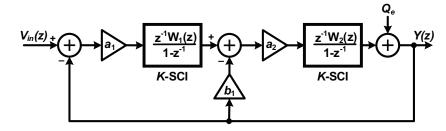

| 5.2 | A concise schematic representation for the second-order KD1S modu-                                   |     |

|     | lator seen in Figure 5.1.                                                                            | 111 |

| 5.3 | Block Diagram for the second-order KD1S modulator seen in Figure                                     |     |

|     | 5.1                                                                                                  | 113 |

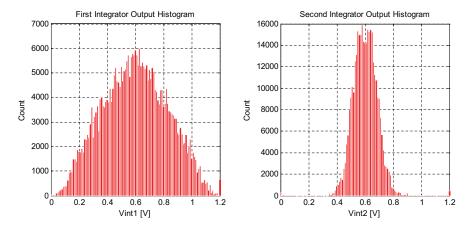

| 5.4 | Spectre behavioral simulation result for the second-order KD1S modu-                                 |     |

|     | lator with ideal components. Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} =$                   |     |

|     | 800 MHz, $OSR = 8$ , and $BW = 6.25$ MHz. The quantizer and op-amps                                  |     |

|     | are ideal                                                                                            | 116 |

| 5.5 | Histogram of the integrator states for the second-order KD1S modulator                               |     |

|     | for the response seen in Figure 5.4                                                                  | 116 |

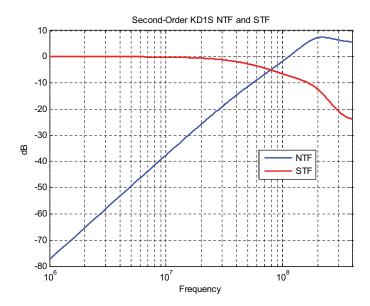

| 5.6 | NTF and STF for the second-order KD1S modulator with $f_s = 100$                                     |     |

|     | MHz, $K_{path} = 8$ , $f_{s,new} = 800$ MHz, $f_{un} = \frac{3}{8} f_{s,new} = 300$ MHz, $OSR = 8$ , |     |

|     | and $T_c = 0$                                                                                        | 118 |

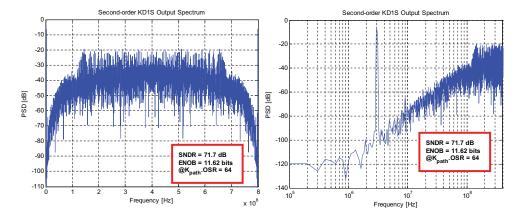

| 5.7 | Spectre behavioral simulation result for the second-order KD1S modu-                                 |     |

|     | lator with ideal components. Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} =$                   |     |

|     | 800 MHz, $OSR = 8$ , and $BW = 6.25$ MHz. The quantizer is ideal and                                 |     |

|     | has zero delay (i.e. $T_c = 0$ )                                                                     | 119 |

| 5.8 | Histogram of the integrator states for the second-order KD1S modulator                               |     |

|     | for the response seen in Figure 5.7                                                                  | 119 |

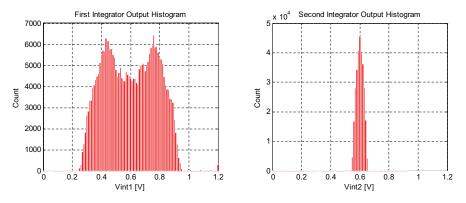

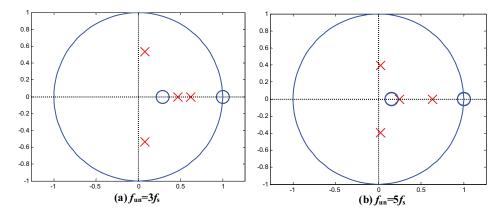

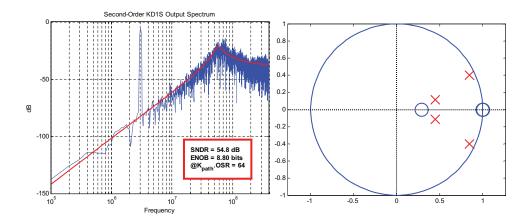

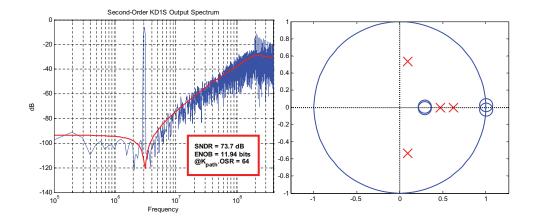

| 5.9  | Matlab simulated PSD of the output and the NTF pole-zero plot for the                             |

|------|---------------------------------------------------------------------------------------------------|

|      | second-order KD1S modulator with $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} =$                  |

|      | 800 MHz, $f_{un} = \frac{3}{8} f_{s,new} = 300$ MHz, $OSR = 8$ , $BW = 6.25$ MHz, and $T_c = 0$ . |

|      |                                                                                                   |

| 5.10 | Effect of the op-amp $f_{un}$ on the pole location of the NTF and STF for a                       |

|      | second-order KD1S modulator                                                                       |

| 5.11 | Simulated NTFs for the second-order KD1S modulator with the op-amp                                |

|      | open-loop gains $(A_{OL})$ of 50 dB and 25 dB                                                     |

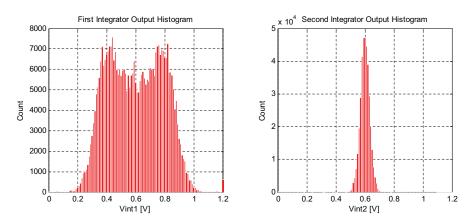

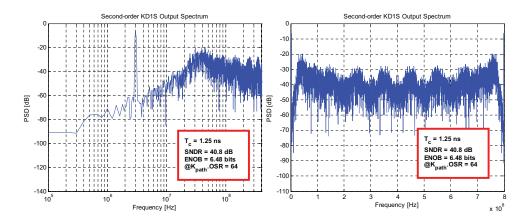

| 5.12 | Spectre simulated PSD (log and linear frequency scales) of the second-                            |

|      | order KD1S modulator with comparator delay $T_c = 625$ ps and the first                           |

|      | comparator is clocked on $\phi_{2-1}$ . Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} =$     |

|      | 800 MHz, $f_{un} = \frac{3}{8} f_{s,new} = 300$ MHz, $OSR = 8$ , and $BW = 6.25$ MHz. 124         |

| 5.13 | Histogram of the integrator states for the second-order KD1S modulator                            |

|      | for the response seen in Figure 5.12                                                              |

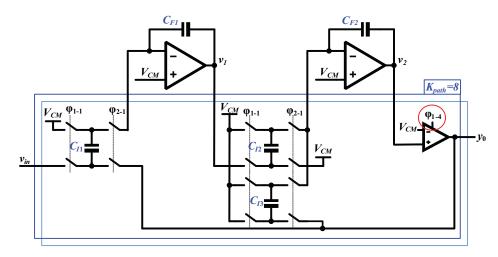

| 5.14 | Spectre simulated PSD (log and linear frequency scales) of the second-                            |

|      | order KD1S modulator with comparator delay $T_c = 1.25$ ns and the first                          |

|      | comparator is clocked on $\phi_{2-1}$ . Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} =$     |

|      | 800 MHz, $f_{un} = \frac{3}{8} f_{s,new} = 300$ MHz, $OSR = 8$ , and $BW = 6.25$ MHz. 126         |

| 5.15 | Histogram of the integrator states for the second-order KD1S modulator                            |

|      | for the response seen in Figure 5.14                                                              |

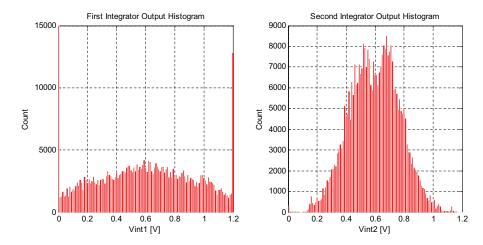

| 5.16 | The second-order KD1S modulator with modified clock scheme to ac-                                 |

|      | commodate the $T_z = T_z/K$ (or $z^{-1}$ ) delay in the comparator                                |

| 5.17 | Spectre simulated PSD (log and linear frequency scales) of the second-                                           |

|------|------------------------------------------------------------------------------------------------------------------|

|      | order KD1S modulator with comparator delay $T_c = 1.25$ ns and the                                               |

|      | first comparator is clocked on $\phi_{1-4}$ . Here, $f_s = 100$ MHz, $K_{path} = 8$ ,                            |

|      | $f_{s,new} = 800 \text{ MHz}, f_{un} = \frac{3}{8} f_{s,new} = 300 \text{ MHz}, OSR = 8, \text{ and } BW = 6.25$ |

|      | MHz                                                                                                              |

| 5.18 | Histogram of the integrator states for the second-order KD1S modulator                                           |

|      | for the response seen in Figure 5.17                                                                             |

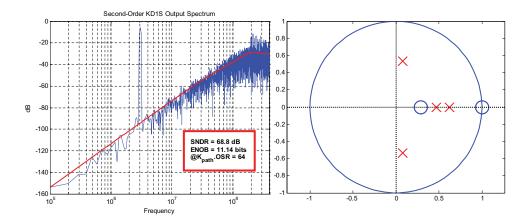

| 5.19 | Matlab simulated PSD of the output and the NTF pole-zero plot for the                                            |

|      | second-order KD1S modulator with $f_{s,new} = 800$ MHz, $f_{un} = \frac{3}{8} f_{s,new}$ ,                       |

|      | $K_{path} = 8$ , $OSR = 8$ , and $T_c = 1.25$ ns (or $z^{-1}$ )                                                  |

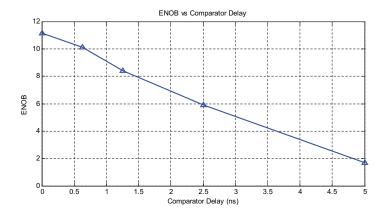

| 5.20 | Effective resolution (ENOB) vs the Comparator delay for the second-                                              |

|      | order KD1S modulator measured with sinusoidal inputs. Here, the ef-                                              |

|      | fective clock frequency is $f_{s,new} = 800 \text{ MHz}$ and $BW = 6.25 \text{ MHz}$ 130                         |

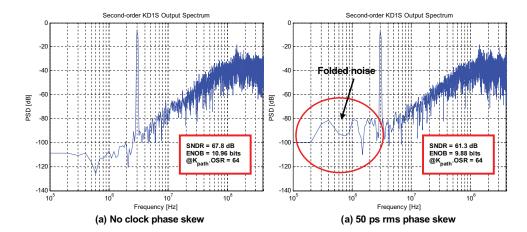

| 5.21 | Spectre simulation showing the noise-folding due to clock-phase skew                                             |

|      | in the second-order KD1S modulator. (a) Spectrum with no phase skew,                                             |

|      | (b) spectrum with Gaussian distributed phase skew with 50 ps standard                                            |

|      | deviation. Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} = 800$ MHz, $f_{un} =$                             |

|      | $\frac{3}{8}f_{s,new} = 300 \text{ MHz}, OSR = 8, \text{ and } BW = 6.25 \text{ MHz}. \dots 132$                 |

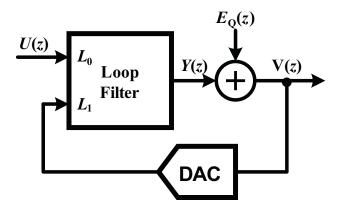

| 6.1  | A generalized structure of a delta-sigma modulator                                                               |

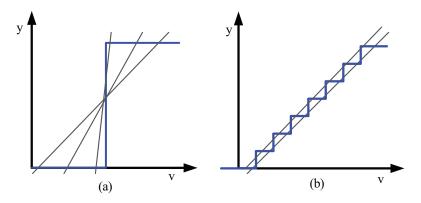

| 6.2  | Illustration of the variation of quantizer gain with respect to the input                                        |

|      | signal for (a) a single-bit quantizer and (b) a multi-bit quantizer 137                                          |

|      |                                                                                                                  |

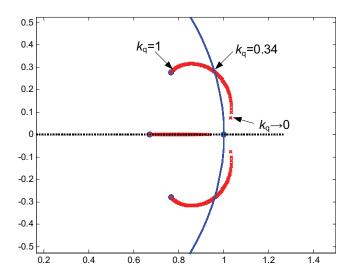

| 6.3  | Root locus of the NTF for a third-order modulator with varying quan-        |    |

|------|-----------------------------------------------------------------------------|----|

|      | tizer gain                                                                  | 38 |

| 6.4  | Example of NTF zero and pole optimization. Here a third-order single-       |    |

|      | bit delta-sigma modulator is synthesized for $OSR = 64$                     | 11 |

| 6.5  | NTF zero spreading in the signal band with SQNR optimization 14             | 12 |

| 6.6  | CIFB (Cascade of Integrators with Distributed FeedBack) modulator           |    |

|      | topology                                                                    | 14 |

| 6.7  | CIFF (Cascade of Integrators with distributed FeedForward) modulator        |    |

|      | topology                                                                    | 15 |

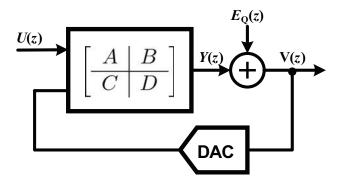

| 6.8  | The ABCD Matrix representation of the loop-filter in a delta-sigma mo-      |    |

|      | dulator                                                                     | 18 |

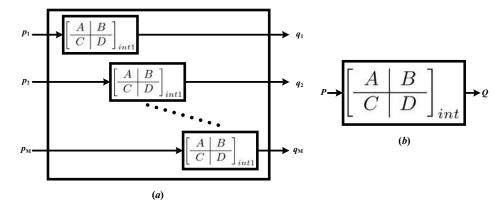

| 6.9  | A discrete-time linear system representation of the $K$ -path integrator 15 | 50 |

| 6.10 | Illustration of the generalized ABCD matrix for a set of M integrators,     |    |

|      | (a) individual ABCD matrices for the integrators with individual inputs     |    |

|      | and outputs, (b) combined ABCD matrix for all the integrators 15            | 51 |

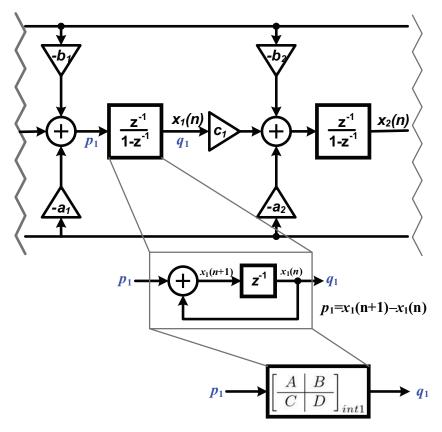

| 6.11 | Illustration of the state-space embedding method for the non-ideal inte-    |    |

|      | grator                                                                      | 55 |

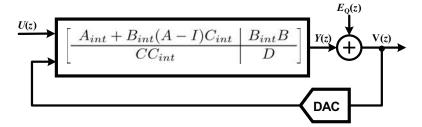

| 6.12 | The equivalent ABCD matrix representation for a KD1S loop-filter after      |    |

|      | incorporating the integrator non-idealities                                 | 55 |

| 6.13 | Dynamic range scaling of a loop-filter state from $x_i$ to $x_i/r$          | 57 |

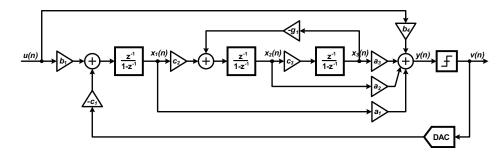

| 6.14 | The synthesized second-order, single-bit, NTF-zero optimized CIFB           |    |

|      | KD1S modulator                                                              | 50 |

| 6.15 | Simulated PSD of the output and the NTF pole-zero plot for the second-            |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | order CIFB-type KD1S modulator. Here, $f_s = 100$ MHz, $K_{path} = 8$ ,           |     |

|      | $f_{s,new} = 800 \text{ MHz}, OSR = 8, \text{ and } BW = 6.25 \text{ MHz}.$       | 160 |

| 6.16 | A concise representation of the singly-ended, switched-capacitor im-              |     |

|      | plementation of the second-order KD1S modulator seen in Fig. 6.15.                |     |

|      |                                                                                   | 161 |

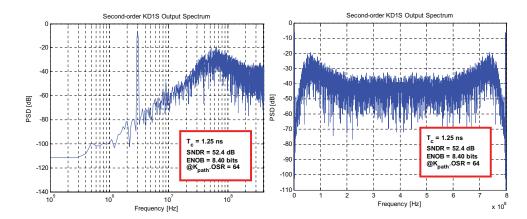

| 6.17 | Spectre simulated spectrum for the second-order KD1S modulator im-                |     |

|      | plemented with switched-capacitors and $f_{un}$ limited op-amp (log and           |     |

|      | linear frequency axes). Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} = 800$ |     |

|      | MHz, $OSR = 8$ , and $BW = 6.25$ MHz                                              | 161 |

| 6.18 | The synthesized third-order, single-bit CIFF KD1S modulator                       | 162 |

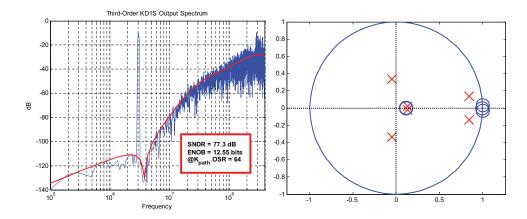

| 6.19 | Simulated output PSD and the NTF pole-zero plot for the third-order               |     |

|      | CIFF-type KD1S modulator. Here, $f_s = 100$ MHz, $K_{path} = 8$ , $f_{s,new} =$   |     |

|      | 800 MHz, $OSR = 8$ , and $BW = 6.25$ MHz                                          | 162 |

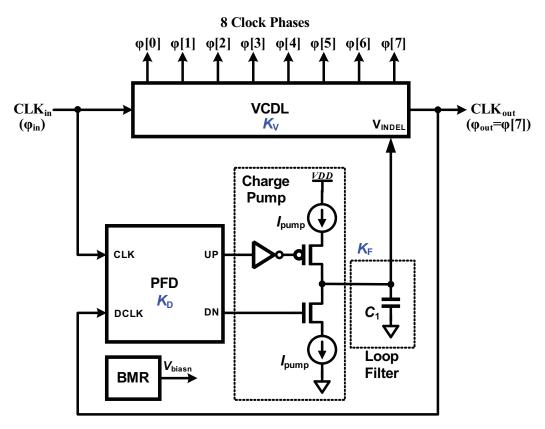

| 7.1  | Block diagram of the delay-locked loop (DLL) used for multi-phase                 |     |

|      | clock generation                                                                  | 167 |

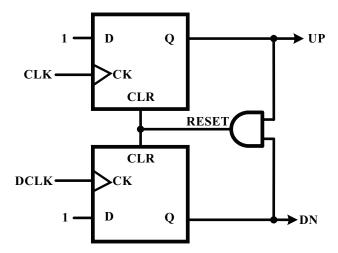

| 7.2  | Block diagram of the phase frequency detector (PFD)                               | 171 |

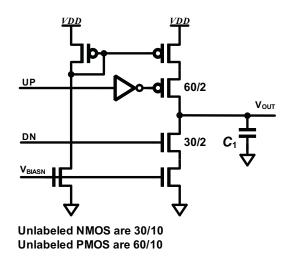

| 7.3  | CMOS implementation of the PFD seen in Figure 7.2                                 | 172 |

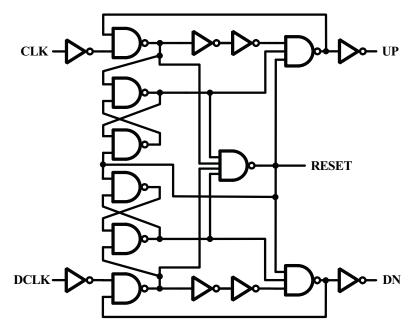

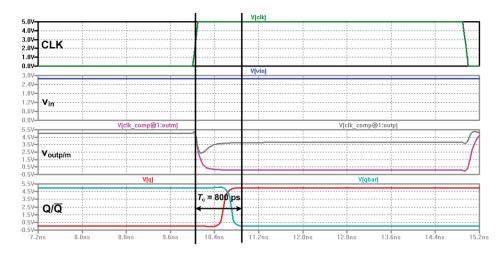

| 7.4  | Simulation results for the PFD seen in Figure 7.3                                 | 172 |

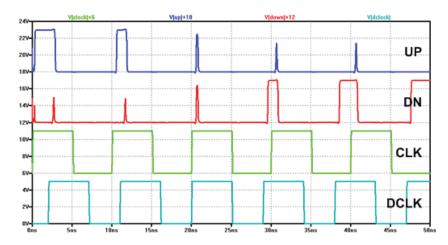

| 7.5  | Charge pump employed in the DLL                                                   | 173 |

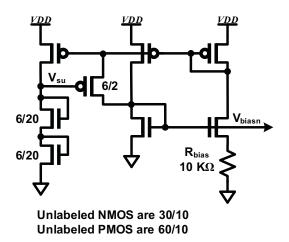

| 7.6  | The self-biased reference (RMR) used in the DLI                                   | 17/ |

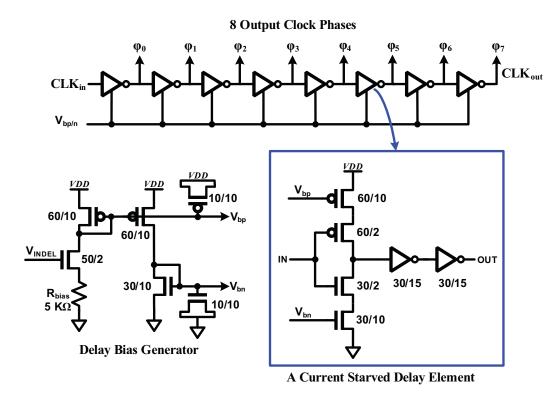

| 7.7  | The voltage controlled delay-line (VCDL) with the delay bias generator                           |

|------|--------------------------------------------------------------------------------------------------|

|      | used in the DLL                                                                                  |

| 7.8  | The non-overlapping clock generator for generating phases $\phi_1[i]$ , $\overline{\phi_1[i]}$ , |

|      | $\phi_2[i]$ and $\overline{\phi_2[i]}$ from the DLL outputs $\phi[i]$ , where $i=0,1,7$ 176      |

| 7.9  | The complete DLL based multi-phase clock generation circuit 176                                  |

| 7.10 | Layout of the multi-phase clock generator using a DLL designed in                                |

|      | 500-nm CMOS process                                                                              |

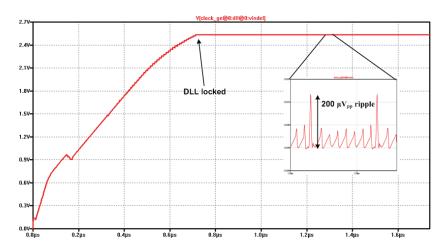

| 7.11 | Transient simulation of the DLL showing the input of the VCDL ( $V_{INDEL}$ ).                   |

|      | Sub-plot shows the peak ripple in the VCDL input in the locked state 177                         |

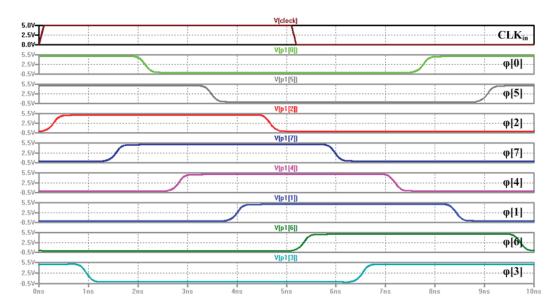

| 7.12 | Eye diagram for the eight clock phases generated from the DLL in the                             |

|      | locked condition. Here the input clock frequency is 100 MHz 178                                  |

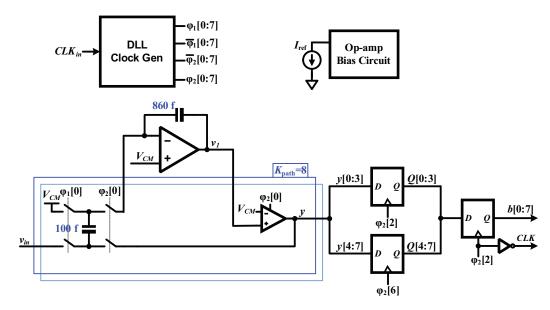

| 7.13 | A concise schematic representation of the single-ended first-order KD1S                          |

|      | modulator with the clock and bias generation circuits 179                                        |

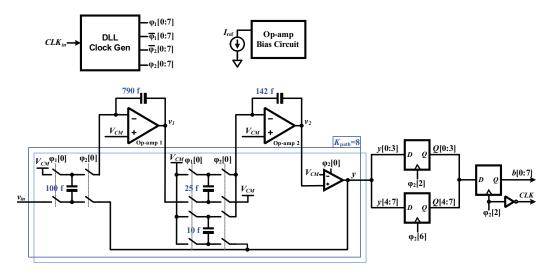

| 7.14 | A concise schematic representation of the single-ended second-order                              |

|      | KD1S modulator with the clock and bias generation circuits 181                                   |

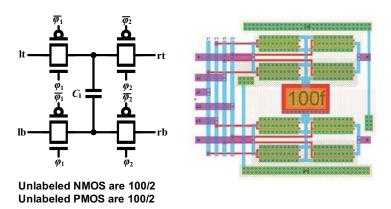

| 7.15 | Switched-capacitor block with the corresponding layout 182                                       |

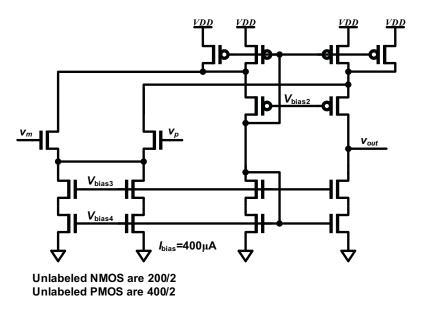

| 7.16 | Single-ended op-amp employed in the first switched-capacitor integra-                            |

|      | tor                                                                                              |

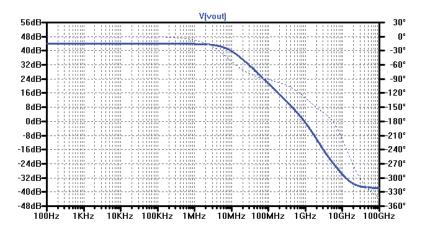

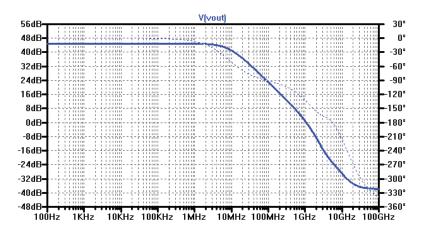

| 7.17 | Magnitude and phase response of the op-amp seen in Figure 7.16 with                              |

|      | 340 fF load. Here, $A_{OL} = 44$ dB, $f_{un} = 940$ MHz, and $PM = 60$ ° 185                     |

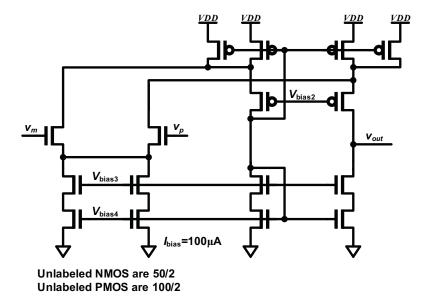

| 7.18 | Single-ended op-amp employed in the second switched-capacitor inte-                              |

|      | grator                                                                                           |

| 7.19 | Magnitude and phase response of the op-amp seen in Figure 7.16 with                             |

|------|-------------------------------------------------------------------------------------------------|

|      | 200 fF load. Here, $A_{OL} = 45$ dB, $f_{un} = 1.15$ GHz and $PM = 58^{\circ}$ 186              |

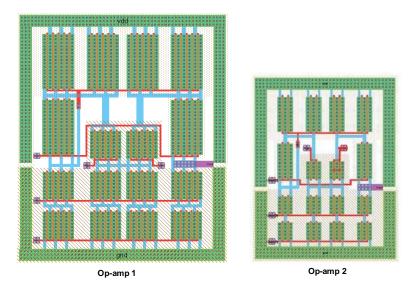

| 7.20 | Layouts of the op-amps used in the KD1S modulators and designed in                              |

|      | 500-nm CMOS                                                                                     |

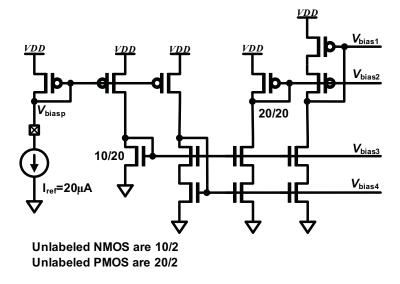

| 7.21 | Bias generation circuit for the op-amps                                                         |

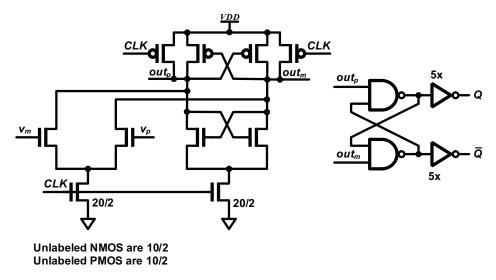

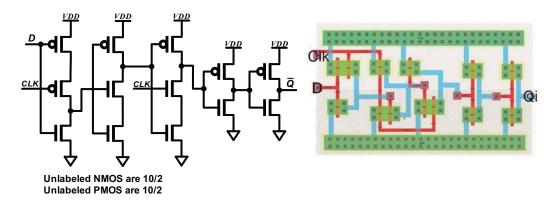

| 7.22 | The clocked comparator with a static latch                                                      |

| 7.23 | Transient simulation of the clock comparator seen in Figure 7.22 189                            |

| 7.24 | Layout of the comparators employed in the KD1S modulators 189                                   |

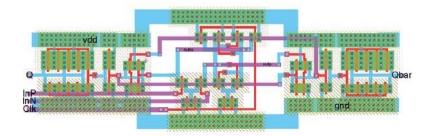

| 7.25 | Schematic and layout TSPC Latch used for synchronizing the KD1S                                 |

|      | outputs                                                                                         |

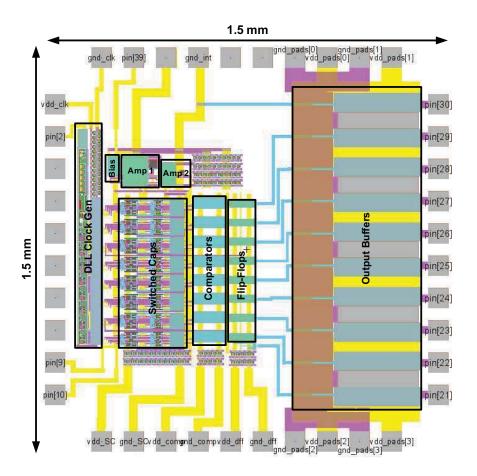

| 7.26 | Labeled layout of the first-order KD1S modulator design in the 500-nm                           |

|      | CMOS process                                                                                    |

| 7.27 | Labeled layout of the second-order KD1S modulator design in the 500-                            |

|      | nm CMOS process                                                                                 |

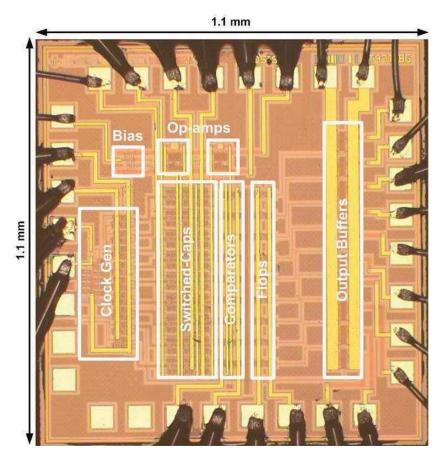

| 7.28 | Die micrograph for a second-order KD1S test chip designed in 500-nm                             |

|      | CMOS process                                                                                    |

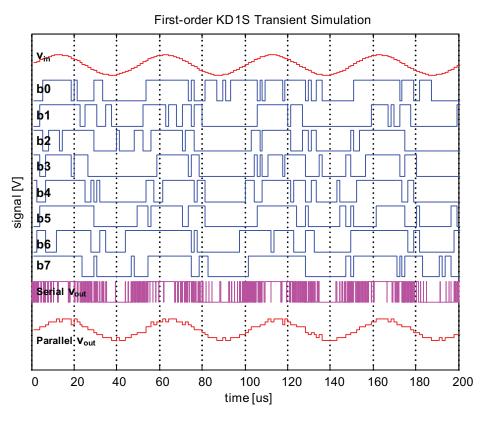

| 7.29 | Plot illustrating the sampled KD1S outputs $Q[0:8]$ , along with the re-                        |

|      | constructed serial and parallel output stream $(v_{out})$                                       |

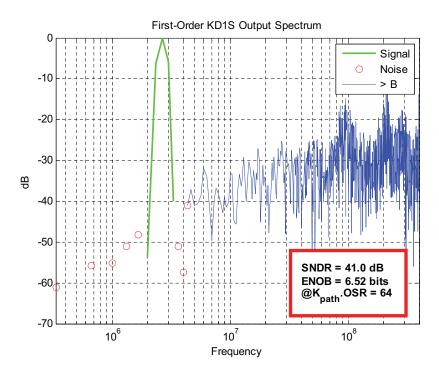

| 7.30 | Simulation results for the first-order KD1S modulator designed in 500-                          |

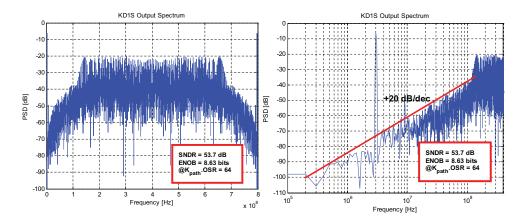

|      | nm CMOS. In these results, $f_{in} = 2.67$ MHz, $f_s = 100$ MHz, $K_{path} = 8$ ,               |

|      | $f_{s,new} = 800 \text{ MHz}, K_{path} \cdot OSR = 64, \text{ and } BW = 6.25 \text{ MHz}.$ 195 |

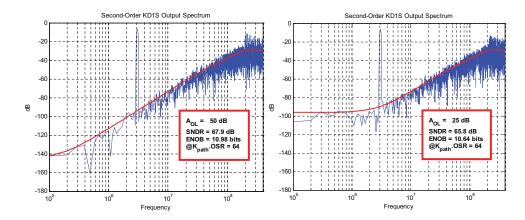

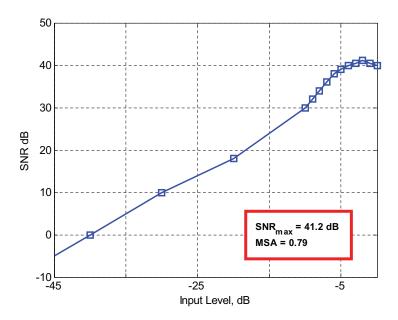

| 7.31 | Simulated SNR vs input sinewave amplitude for the second-order KD1S                            |

|------|------------------------------------------------------------------------------------------------|

|      | modulator                                                                                      |

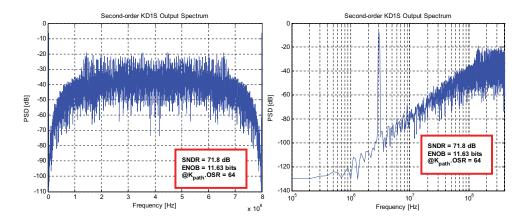

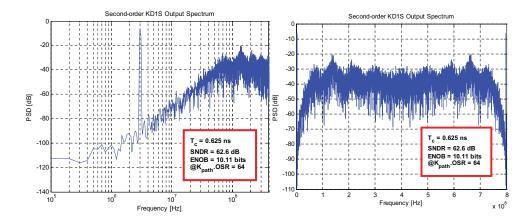

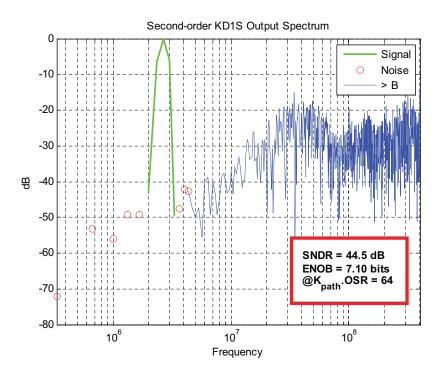

| 7.32 | Simulation results for the second-order KD1S modulator designed in                             |

|      | 500-nm CMOS. IIn these results, $f_{in} = 2.67$ MHz, $f_s = 100$ MHz, $K_{path} =$             |

|      | 8, $f_{s,new} = 800 \text{ MHz}$ , $K_{path} \cdot OSR = 64$ , and $BW = 6.25 \text{ MHz}$ 197 |

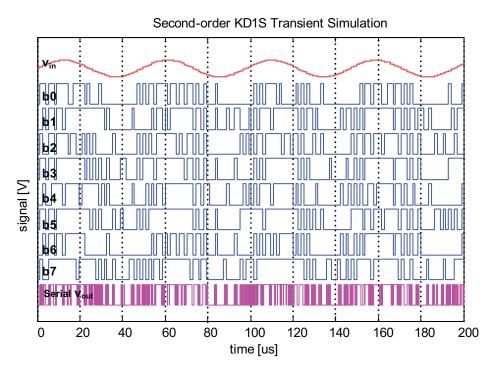

| 7.33 | Plot illustrating the sampled KD1S outputs $b[0:8]$ , along with the re-                       |

|      | constructed serial and parallel output stream $(v_{out})$                                      |

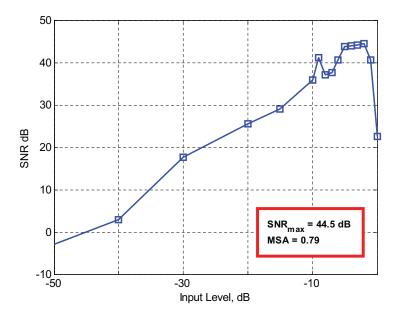

| 7.34 | Simulated SNR vs input sinewave amplitude for the second-order KD1S                            |

|      | modulator                                                                                      |

| 7.35 | Test Setup used for data acquisition from the single-ended KD1S Mod-                           |

|      | ulators on the chip                                                                            |

| 7.36 | Labeled photograph of the test board used for the 500-nm chip 201                              |

| 7.37 | (a) Top layer (power plane) and (b) bottom layer (ground plane) of the                         |

|      | test board                                                                                     |

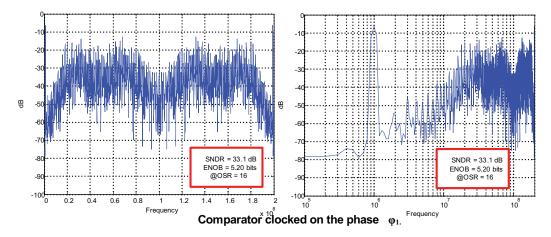

| 7.38 | Measured PSD of the second-order KD1S modulator fabricated in 500-                             |

|      | nm CMOS. Here, $f_{in} = 870$ KHz, $f_s = 100$ MHz, $f_{s,new} = 800$ MHz,                     |

|      | $K_{north} \equiv 8$ $K_{north} \cdot QSR \equiv 64$ and $BW \equiv 6.25$ MHz                  |

## CHAPTER 1 INTRODUCTION

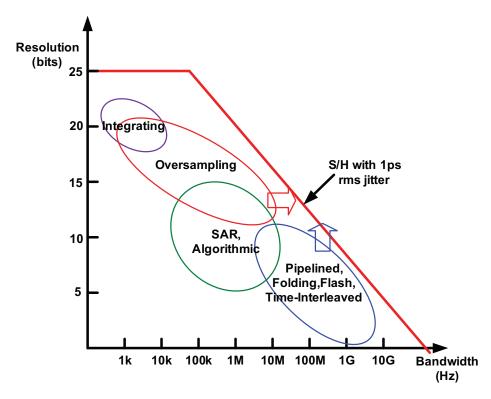

Continued CMOS scaling has enabled ever increasing device speeds leading to numerous applications in wireless, wireline and optical communication. The integrated circuit technologies used to manufacture analog-to-digital converters (ADCs) are shrinking to enable more system functionality in a smaller chip area. This reduction in size comes at the cost of greater manufacturing variances, including transistor characteristics, which limit the availability of precise components often required in an ADC. Further, the large increase in the number of wireless communication standards call for processing of the electromagnetic spectrum from 900 MHz to the GHz's range [2]. The applications include cellular telephony (GSM, EDGE, WCDMA, etc.), ultra-wide band communication (UWB), personal area networks (Bluetooth, ZigBee, etc.), Wireless LAN, WiMAX and Cognitive Radio [3]. Another application of interest is the development of a low-power single-chip software defined radio (SDR) which requires GHz rate data conversion. Figure 1.1 shows the classification of ADCs based upon their bit resolution and conversion bandwidth specifications compiled from [4]. As illustrated in this figure, the fundamental limitation on the achievable ADC resolution is set by the clock jitter and thermal noise.

**Figure 1.1:** Classification of Analog-to-Digital Converters based upon their resolution and conversion bandwidth.

Typically in CMOS technology, Flash ADCs have been used for higher-speed data conversion from 100's of MHz to several GHz's at lower resolution (5-6 bits), pipelined ADCs for moderate resolution (10-12 bits) for 100-250 MHz range and oversampling (Delta-Sigma) ADCs for lower bandwidths (kHz's to MHz's) and high-resolution (12-up to 24 bits).

CMOS scaling benefits the Flash ADCs and the oversampling ADCs by realizing increasing higher sampling rates. However, the resulting high-speed of scaled CMOS transistors is concomitant with the degrading intrinsic transistor gain  $(g_m \cdot r_o)$ , pronounced process variations and poor component matching [5]. In order to design

high-resolution pipelined ADCs in nano-CMOS with significant device offsets, complicated digital-calibration schemes are employed at the cost of increased area, latency and power consumption [1, 6, 7]. Thus, it is imperative to further explore ADC topologies which are inherently tolerant to device-mismatches, lower amplifier gain and other circuit-imperfections in nano-CMOS.

#### 1.1 Motivation

Delta-sigma modulation based ADCs which employ oversampling and a feedback architecture offer possibilities of attaining higher dynamic range as we scale further into the nano-CMOS regime. However due to oversampling, their conversion rates are significantly lower than their Nyquist-rate counterparts. Numerous attempts have been made to employ multiple delta-sigma modulators in parallel (or by using time-interleaving) to achieve Nyquist-rate data conversion. These architectures have their own deficiencies resulting from the path mismatches and a linear increase in power consumption with the number of parallel channels [8].

Recently there has been activity in employing delta-sigma ADCs for next-generation wireless applications which require over 60 dB of dynamic range and greater than 25 MHz conversion bandwidth. Several continuous-time delta-sigma architectures have been proposed for lower power (less than 20 mW) for such wireless applications [9, 10]. Also, there have been efforts in designing reconfigurable delta-sigma ADCs for multistandard operation [11].

This dissertation analyzes a new noise-shaping topology, called the *K*-Delta-1-Sigma (KD1S) modulator, for wideband conversion which was disclosed in [12]. The KD1S topology employs time-interleaved sampling with a shared integrator. The interleaved single-bit quantizers (which is simply an array of comparators) employed in the KD1S modulator allow very high-speed sampling with lower implementation complexity. Due to single-bit quantization, the feedback digital-to-analog converters (DACs) in the modulator are inherently linear and thus the complexity of element mismatch shaping is avoided. Therefore, the KD1S modulator architecture offers several advantages over a multi-bit modulator employing the same number of comparators. However, the quantizer in the KD1S modulator requires the comparator to operate at a higher speed, set by the effective sampling rate of the modulator, which is favorable in the nano-CMOS technologies. In summary, the KD1S architecture trades off high comparator speed with lower implementation complexity of the quantizer and with the lower peformance requirements of the op-amps.

In the traditional time-interleaving ADC architectures, the phase skew, path-offset and gain-mismatch result in severe degradation in the achievable dynamic range and the signal-to-noise ratio (SNR). However in the KD1S modulator, the distortion due to the mismatch and phase skew in the time-interleaved sampling paths is averaged by the number of paths and by the oversampling ratio (OSR) for each path. The noise introduced into the signal band due to clock jitter is also averaged by the number of paths and the OSR which results in a higher SNR in the KD1S modulator. The KD1S

architecture for high-speed data conversion offers other advantages which are analyzed in detail in the subsequent chapters.

The first-order KD1S modulator architecture, presented in [13] and [14], has been extended to a generalized higher-order modulator. A systematic synthesis method for higher-order KD1S modulator has been presented. First- and second-order KD1S designed using this procedure has been fabricated in a 500-nm CMOS technology. The aim of this research is to determine the limitations of the KD1S topology.

## 1.2 Dissertation Organization

This dissertation covers a detailed theoretical analysis of the *K*-Delta-1-Sigma modulators along with a synthesis method for higher-order KD1S topologies. The effects of various circuit non-idealities and their influence on the KD1S performance have been detailed. The design and testing procedure for the prototype chips has been presented. The remaining dissertation has been organized as follows:

Chapter 2 provides a brief background on design issues involved in the time-interleaved analog-to-digital converters (TI-ADCs). The analytical results presented in this chapter are used in subsequent chapters to analyze the time-interleaved sampling structure inherent in the KD1S modulator.

Chapter 3 provides an introduction to delta-sigma modulators and describes the approaches to design wideband ADCs without employing complicated calibration in nano-CMOS processes.

Chapter 4 describes the KD1S modulator and details the effects of circuit nonidealities on the modulator performance. The KD1S modulator performance has been analyzed and simulated for circuit limitations like finite op-amp gain and unity-gain frequency, slewing in op-amps and finite comparator delay. The effect of quantization noise folding due to path mismatch and clock phase skew is also analyzed.

Chapter 5 discusses the design of the second-order KD1S modulator, presents behavioral simulation results and details the effects of circuit non-idealities.

Chapter 6 presents a synthesis and simulation method for generalized higher-order KD1S modulators. A novel state-space embedding method for KD1S modulators has been developed for their rapid simulation and performance estimation.

Chapter 7 details the transistor level design of first- and second-order KD1S modulators, chip design and simulation, test board design and measurement results from the prototype chip.

Chapter 8 concludes the dissertation and discusses future directions for this research.

Appendix A provides the listing of the MATLAB codes used for signal processing throughout the dissertation.

#### CHAPTER 2 TIME-INTERLEAVED ANALOG-TO-DIGITAL CONVERTERS

The effective sampling-rate of analog-to-digital converters (ADCs) can be increased by operating multiple slower ADCs in parallel which results in a faster time-interleaved ADC (TI-ADC). This chapter presents detailed analysis for the TI-ADCs and the resulting non-idealities. The analytical results presented in this chapter will be applied to the analysis of KD1S modulators which employ time-interleaved sampling along with a shared loop-filter.

## 2.1 Time-Interleaved Analog-to-Digital Converters

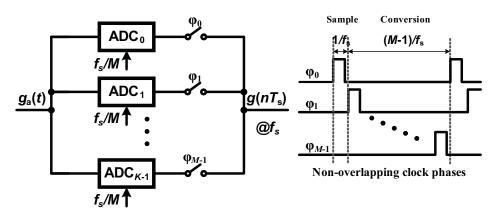

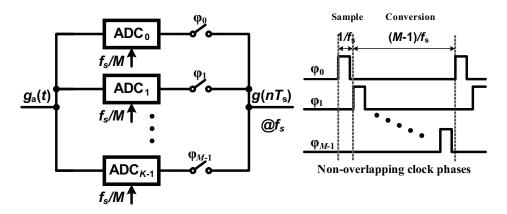

Time-interleaving of slower ADCs in parallel is an attractive way to achieve an increase in the conversion rate [15]. Figure 2.1 illustrates the concept of time-interleaving ADCs. Here, M- ADCs operating at a frequency of  $f_s/M$ , called the *slices*, are clocked on the M-phases of a clock. The outputs of the slices are multiplexed to obtain output digital codes operating at an equivalent clock frequency of  $f_s$ . Thus, the speed requirements on the individual ADC slices are relaxed by a factor of M. The resulting increase in power and area of the time-interleaved ADC (TI-ADC) does not necessarily increase linearly with M when compared to the an equivalent single-path faster ADC. This is due to the fact that the op-amps in each of the slices require smaller bias currents, and also the op-amps can be shared across paths to reduce power consumption and area [5]. Thus, time-interleaving enables much higher speed than allowed by the CMOS

technology used for implementation of a single channel ADC. However, the mismatch between the parallel paths introduces distortion and lowers the resulting signal to noise and distortion ratio (SNDR). The dominant sources of error in TI-ADCs are the clock phase-skew, offset errors, gain and bandwidth mismatch across the paths [5, 15].

**Figure 2.1:** Time-interleaved ADCs and the corresponding clock phases.

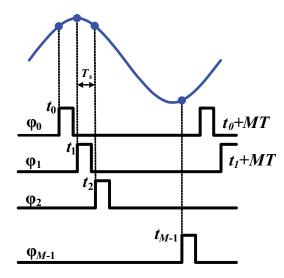

Figure 2.2 depicts the sampling of an input sinewave by a time-interleaved ADC. Here, the samples in the channels m = 0,..., M-1 are ideally sampled at the time instants  $t_m, t_{m+M}, t_{m+2M},...$  where  $t_m = mT$ , and T is the equivalent sampling period of the TI-ADC. Because of the imperfections in the clock phases from skew and jitter, the sampling instants will vary from channel-to-channel. Assuming that the jitter noise for each of the clock phases is uncorrelated from each other and has a flat spectrum (white noise characteristics), the effect of aperture error due to jitter can be treated like the jitter noise for the overall TI-ADC. However, due to clock skew, the sampling instances will vary for each of the channel and is represented as [5, 16]

$$t_m = mT - r_m T \tag{2.1}$$

where  $r_m$  is the relative error in the sampling instant with respect to the overall sampling period  $(T = \frac{1}{f_s})$ , i.e.  $r_m = \frac{T_{skew}}{T}$ . A detailed mismatch analysis using non-linear sampling theory for TI-ADCs is provided in [5, 16], and is briefly derived and re-interpreted in this section for the benefit of the reader.

**Figure 2.2:** Sampling of an input sine wave by a time-interleaved ADC.

Let the analog input signal to the TI-ADC,  $g_a(t)$  have its Fourier spectrum given by  $G_a(f)$ . Then the resulting Fourier transform of the output of the time-interleaved sampling system is given by the following double-summation [16]

$$G(f) = \frac{1}{MT} \sum_{m=0}^{M-1} \left[ \sum_{k=-\infty}^{\infty} G_a \left( f - \frac{k}{MT} \right) e^{-j2\pi \left[ f - \frac{k}{MT} \right] t_m} \right] e^{-j2\pi mfT}$$

(2.2)

which is rewritten in terms of  $r_m$  to give

$$G(f) = \frac{1}{T} \sum_{k=-\infty}^{\infty} \left[ \frac{1}{M} \sum_{m=0}^{M-1} e^{-j2\pi \left[ f - \frac{k}{MT} \right] r_m T} e^{-j2\pi \frac{km}{M}} \right] G_a \left( f - \frac{k}{MT} \right)$$

(2.3)

Equations 2.2 and 2.3 are two generalized representations of the spectra for a non-uniformly sampled signal [16]. If there are no channel-mismatches and timing errors

in the TI-ADC, then we can simplify Equation 2.3 with  $r_m = 0$ , and using the result  $\sum e^{-j2\pi \frac{km}{M}} = M \text{ for } k = 0, M, 2M, \dots, \text{ results in the spectrum}$

$$G(f) = \frac{1}{T} \sum_{k=-\infty}^{\infty} G_a \left( f - \frac{k}{T} \right)$$

(2.4)

which is same as the spectrum for a uniformly sampled signal with a time-period T.

# 2.2 Non-uniformly Sampled Sinusoidal

Sinusoidal signals are generally used as test input signals for ADCs and are used to characterize the resulting distortion and inter-mixing in the system. Thus, it's convenient to derive the spectrum of a non-uniformly sampled sinusoidal signal for use in deriving the characteristics of a TI-ADC. For a complex sinusoidal  $e^{j2\pi f_0t}$ , with a frequency  $f_0$ , the spectrum is given as

$$G_a(f) = \delta(f - f_0) \tag{2.5}$$

Substituting Equation 2.5 in Equation 2.3, we get the resulting discrete-time spectrum [16]

$$G(f) = \frac{1}{MT} \sum_{m=0}^{M-1} \left[ \sum_{k=-\infty}^{\infty} \delta \left( f - f_0 - \frac{k}{MT} \right) e^{-jr_m 2\pi \frac{f_0}{f_s}} e^{-j2\pi \frac{km}{M}} \right]$$

(2.6)

Now, let's define an amplitude sequence A(k), k = 0, 1, ..., M, such that [16]

$$A(k) = \sum_{m=0}^{M-1} \left( \frac{1}{M} e^{-jr_m 2\pi \frac{f_0}{f_s}} \right) e^{-j2\pi \frac{km}{M}}$$

(2.7)

then we can rewrite Equation 2.6 as [16]

$$G(f) = \frac{1}{T} \sum_{k=-\infty}^{\infty} A(k) \delta\left(f - f_0 - \frac{k}{MT}\right)$$

(2.8)

Equations 2.6 and 2.8 comprise the spectral representation of the non-uniformly sampled complex sinusoidal signal [16]. This resulting discrete-time sinusoidal representation has the following properties [16]:

- From Equation 2.7, it can be observed that A(k) is periodic with an index k and a period of M. Thus, the spectrum G(f) given by Equation 2.8 is periodic with a period 1/T = f<sub>s</sub>.

- 2. A single period of the spectrum (from f=0 to 1/T) is comprised of M spectral tones, separated by a frequency difference of  $f_s/M$ . The main sampled signal is located at  $f_0$  with a magnitude |A(0)|, while the  $m^{th}$  tone is located at  $f_0 + \frac{m}{M}f_s$  with a magnitude given by |A(m)|. The TI-ADC sampled spectrum is illustrated in Figure 2.3.

- 3. Note that the discrete sequence A(k) is the discrete-time Fourier transform (DFT) of the sequence  $a(m) = \frac{1}{M}e^{-jr_m2\pi\frac{f_0}{f_s}}$ , m = 0, 1, ..., M-1. Then, by using the Parseval's theorem [17] we have

$$\sum_{k=0}^{M-1} |A(k)|^2 = \sum_{m=0}^{M-1} |a(m)|^2 = 1$$

(2.9)

The sequence a(m) represent the relative complex ratio of the mismatch tones in the TI-ADC, located at frequencies  $f_0 + \frac{m}{M} f_s$ . Also we know that for a DFT, A(M-k) = A(k) due to the circular symmetry property [17].

4. Equation 2.9 leads to the simple calculation of the SNDR for non-uniform sampling, given as

$$SNDR_{ns} = 10\log_{10}\left(\frac{|A(0)|^2}{1 - |A(0)|^2}\right)dB$$

(2.10)

Based on the equations derived in the last section, we can now derive the effects of various mismatch errors in TI-ADCs.

**Figure 2.3:** Spectrum of a non-uniformly sampled complex sinusoid.

From Equation 2.8, we can write the non-uniformly sampled spectrum for a real input signal  $a_0 \cdot sin(2\pi f_{in}t)$  as

$$G(f) = \frac{a_0}{2jT} \sum_{k=-\infty}^{\infty} \left[ A(k)\delta\left(f + f_{in} - \frac{k}{MT}\right) - A^*(M - k)\delta\left(f - f_{in} - \frac{k}{MT}\right) \right]$$

(2.11)

which implies that the spectrum of the input signal repeats at frequencies  $f_{in} + \frac{k}{M}f_s$ , k = 0, ..., M-1 with a multiplier given by  $|A(k)| = |A^*(M-k)|$ , where the index k = 1, ..., M-1 corresponds to the location of the distortion tones.

# 2.2.1 Path Offset Errors

Assuming that there is no phase skew ( $r_m = 0$ ) or gain mismatch in the TI-ADC channels but that there exist fixed offsets in the channels. A distortion term due to the channel offsets in the TI-ADCs results as [5]

$$A(k) = \sum_{m=0}^{M-1} \left(\frac{1}{M}o_m\right) e^{-j2\pi \frac{km}{M}}$$

(2.12)

where  $o_m$  is the offset for path  $m \in \{0, 1, ...M - 1\}$ . Here  $o_m \sim N(0, \sigma_o)$  are identical and independently distributed random (i.i.d.) variables with Gaussian distribution and with zero mean. Thus, the distortion due to channel offsets is not signal dependent and appears at frequencies  $mf_s/M$ . From Parseval's relation we have the distortion power given by

$$P_d = E\left[\sum_{k=0}^{M-1} |A(k)|^2\right] = E\left[\sum_{k=0}^{M-1} o_m^2\right] = \sigma_o^2$$

(2.13)

where E() is the expectation function and  $\sigma_o^2$  is the variance of the channel offsets. From this, we can estimate the offset-limited SNDR for the TI-ADC as

$$SNDR_o < 10 \cdot log\left(\frac{P_s}{P_d}\right) = 20 \cdot log\left(\frac{A_0}{\sigma_o\sqrt{2}}\right)$$

(2.14)

which implies that a large variance in channel offsets linearly degrades the resulting SNDR (in dB).

#### 2.2.2 Gain Mismatch Errors

Assuming that there is only gain mismatch error in the channels of the TI-ADC and that the phase skew and the offsets are absent, we can write the distortion term resulting

from gain mismatch in TI-ADCs as [5]

$$A(k) = \sum_{m=0}^{M-1} \left(\frac{1}{M} a_m\right) e^{-j2\pi \frac{km}{M}}$$

(2.15)

where  $a_m \sim N(a, \sigma_a)$  are i.i.d. random variables representing the gain of each channel. By definition, the channel gains are assumed to be normally distributed with mean a and variance  $\sigma_a$ . From Equation 2.11 we can observe that the distortion tones are located at the frequencies  $f_{in} + k \frac{f_s}{M}$  and  $f_s - (f_{in} + k \frac{f_s}{M})$ , k = 1, ..., M - 1. Thus, all the distortion tones are folded back into the Nyquist baseband from 0 to  $f_s/2$ . The signal amplitude is given by A(0) while A(m), m = 1, ..., M - 1 represent the amplitude of the distortion tones [5].

Now, we estimate the expected value of the total power of signal and distortion tones given as

$$P_{tot} = \frac{1}{2}E\left[\sum_{k=0}^{M-1}|A(k)|^2\right] = E\left[\frac{1}{2M}\sum_{m=0}^{M-1}|a(m)|^2\right]$$

$$= \frac{1}{2M}\sum_{m=0}^{M-1}E\left[a^2(m)\right] = \frac{E\left[a_0^2\right]}{2} = \frac{\sigma_a^2 + a^2}{2}$$

(2.16)

Similarly, the signal power is estimated as [5]

$$P_{s} = \frac{E[A(0) \cdot A^{*}(0)]}{2} = \frac{1}{2M^{2}} \sum_{m=0}^{M-1} \sum_{n=0}^{M-1} E[a_{m} \cdot a_{n}]$$

$$= \frac{1}{2M} E[a_{m}^{2}] + \frac{1}{2M^{2}} (M^{2} - M) (E[a_{m}])^{2}$$

$$= \frac{1}{2M} (\sigma_{a}^{2} + a^{2}) + \frac{1}{2M^{2}} M (M - 1) a^{2} = \frac{1}{2M} (\sigma_{a}^{2} + M \cdot a^{2})$$

(2.17)

Since the distortion power  $P_d$  is equal to  $P_{tot} - P_s$ , we can estimate the SNDR as [5]

$$SNDR = 10 \cdot log \left( \frac{P_s}{P_{tot} - P_s} \right) = 10 \cdot log \left( \frac{\frac{1}{2M} \left( \sigma_a^2 + M \cdot a^2 \right)}{\frac{\sigma_a^2 + a^2}{2} - \frac{1}{2M} \left( \sigma_a^2 + M \cdot a^2 \right)} \right)$$

$$= 10 \cdot log \left( \frac{\frac{1}{M} \left( \sigma_a^2 + M \cdot a^2 \right)}{\left( 1 - \frac{1}{M} \right) \sigma_a^2} \right)$$

(2.18)

Assuming that  $\sigma_a \ll a$ , we can approximate Equation 2.18 as [5]

$$SNDR \approx 20 \cdot log\left(\frac{a}{\sigma_a}\right) - 10 \cdot log\left(1 - \frac{1}{M}\right)$$

(2.19)

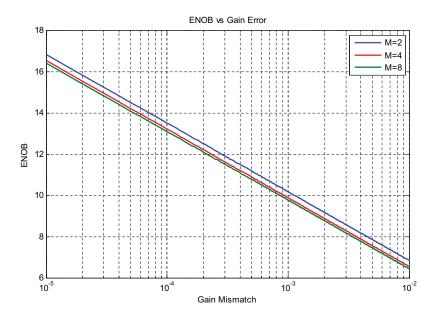

The second term in Equation 2.19 changes by a maximum of 3 dB (or 0.5 bit) as M ranges from 2 to  $\infty$ . Figure 2.4 plots the effective number of bits (ENOB) resulting from the time-interleaved sampling as a function of the gain mismatch error ( $\sigma_a$ ), for time-interleaved sampling with M = 2, 4 and 8 channels and with the mean channel gain a = 1.

**Figure 2.4:** ENOB as a function of the standard deviation of the gain mismatch with *M* ADCs in parallel.

Here, we can observe that with a channel gain mismatch of 0.1%, which is the nominal capacitance ratio mismatch in a CMOS process, the TI-ADC is limited to 10 bits in resolution [5].

### 2.2.3 Phase Skew Errors

Now if we assume that only clock phase skew is present across the TI-ADC channel and the offset and gain errors are absent, we have the distortion term given by

$$A(k) = \sum_{m=0}^{M-1} \left( \frac{1}{M} e^{-j2\pi f_{in} r_m T} \right) e^{-j2\pi \frac{km}{M}}$$

(2.20)

Again, the distortion tones appear at the frequencies  $f_{in} + k \frac{f_s}{M}$  and  $f_s - (f_{in} + k \frac{f_s}{M})$ , k = 1, ..., M-1, and fold back into the Nyquist baseband. Thus, the spectra of the noise introduced due to the phase skew is discrete as opposed to the continuous (white or with skirts) spectrum of the noise introduced due to the clock jitter. If the phase skew errors are assumed to be Gaussian i.i.d. random variables with zero mean and a variance  $\sigma_{skew}^2$ , the SNDR can be derived similarly to the gain mismatch analysis. Let's define the i.i.d. random variables  $\alpha_m = r_m f_{in}/f_s$ , m = 0, 1, ..., M-1 with a PDF (probability density function),  $p(\alpha)$  and its characteristic function given by [16]

$$P(\omega) = E\left(e^{j\omega\alpha}\right) \tag{2.21}$$

Then, the signal power  $P_s$  is estimated as [16]

$$P_{s} = E[A(0) \cdot A^{*}(0)] = \frac{1}{M^{2}} \sum_{m=0}^{M-1} \sum_{n=0}^{M-1} E\left[e^{-j2\pi(\alpha_{m}-\alpha_{n})}\right]$$

$$= \frac{1}{M} + \left(1 - \frac{1}{M}\right) (|P(2\pi)|)^{2}$$

$$= |P(2\pi)|^{2} + \frac{1}{M} \left(1 - |P(2\pi)|^{2}\right)$$

(2.22)

and thus the SNDR is estimated is [16]

$$SNDR_{skew} = 10 \cdot log \left( \frac{E[A(0) \cdot A^{*}(0)]}{1 - E[A(0) \cdot A^{*}(0)]} \right)$$

$$= 10 \cdot log \left( \frac{1 + (M-1)|P(2\pi)|^{2}}{(M-1)\left(1 - |P(2\pi)|^{2}\right)} \right)$$

(2.23)

For a Gaussian distribution  $\alpha_m \sim N(0, \sigma)$ , substituting the  $|P(2\pi)|$  by  $e^{2^{\pi^2 \sigma^2}}$  and then taking Taylor's series expansion of the log term around  $\sigma = 0$  and retaining only the first term, we get the approximated SNDR as [16]

$$SNDR_{skew} = 20 \cdot log\left(\frac{1}{2\pi\sigma}\right) - 10 \cdot log\left(1 - \frac{1}{M}\right)$$

(2.24)

Now we substitute  $\sigma = f_{in}\sigma_{skew}$ , to obtain the final SNDR relation

$$SNDR = 20 \cdot log \left(\frac{1}{2\pi f_{in}\sigma_{skew}}\right) - 10 \cdot log \left(1 - \frac{1}{M}\right)$$

(2.25)

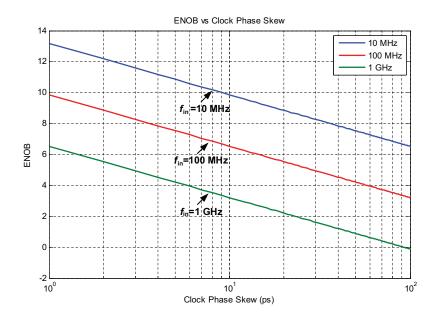

From Equation 2.25 we can see that the SNR drops 20 dB per decade with change in either the signal frequency  $f_{in}$  or the phase-skew standard deviation  $\sigma_{skew}$ . Thus the degradation in the SNDR is 0.5 bit for the complete range of M, while its greater than 3.3 bits per decade increase in  $f_{in}$  or  $\sigma_{skew}$ . Figure 2.5 plots the effective number of bits (ENOB) resulting from the time-interleaved sampling as a function of the phase skew

$(\sigma_{skew})$ , for input signal frequencies of 10 MHz, 100 MHz and 1 GHz. Here, for each of the plots the equivalent clock rate  $(f_s)$  of the TI-ADC is such that the Nyquist sampling criterion is satisfied, i.e.  $f_s > 2f_{in}$ , while each of the 8 channels operate at a clock rate of  $f_s/8$ . Assuming a nominal phase skew of 10 ps, we can not expect more than 10 bits of resolution with  $f_{in} = 10$  MHz and a resolution of 7 bits at  $f_{in} = 100$  MHz. Thus phase skew severely limits the effective resolution of a Nyquist-rate TI-ADC.

**Figure 2.5:** ENOB vs clock phase skew for an eight-channel time-interleaved ADC. Here,  $f_s > 2f_{in}$ , and the ENOB is independent of the sampling frequency.

### 2.2.4 Errors Due to Bandwidth Mismatch

A commonly ignored but rather important source of error in time-interleaved systems results due to mismatch in the bandwidth of the channels [18]. A typical example of a situation with bandwidth mismatch is of the time-interleaved track-and-hold (T/H) circuits. Each track-and-hold has a first-order response set by the switch on-resistance

$(R_{sw})$  and the hold capacitance  $(C_H)$ . The  $R_{sw}C_H$  time-constant sets the frequency response of the T/H and any mismatch in the  $R_{sw}C_H$  product will cause bandwidth mismatch across the channels. The bandwidth mismatch causes AC gain and phase mismatch in the sampled signal in each of the channels. The phase mismatch introduced due to the bandwidth mismatch is a non-linear function of the input frequency. The reader is referred to [18] for analytical expressions derived for the SNDR due to the bandwidth mismatch in time-interleaved systems.

# 2.3 Oversampling in Time-Interleaved ADCs

Note that the distortion tones due to the path-mismatches in a TI-ADC appear at  $f_{in} + k \frac{f_s}{M}$  and  $f_s - (f_{in} + k \frac{f_s}{M})$ , k = 1, ..., M - 1, i.e. at a separation of  $f_s/M$  from the input frequency. Now if we have the situation where  $f_{in} \leq \frac{f_s}{2M}$  implying an oversampling by M, we can avoid the appearance of these distortion tones in the signal band. However, in that case we lose the advantage of M-fold increase in conversion bandwidth obtained by employing time-interleaving although there is an increase in resolution by  $0.5 \cdot \log_2(M)$  bits due to reduction in the quantization noise after filtering. Also, the oversampling ratio (OSR) can not be less than the number of paths M for a distortion free baseband i.e.  $OSR \geq M$ . The distortion tones can be filtered out by digital filters resulting in an  $\frac{1}{2}log_2(OSR)$  bit increase in resolution. We will revisit the effects of channel mismatch errors in a time-interleaved delta-sigma ADC in Chapter 3, where the quantization noise folds back into the baseband due to the channel mismatch errors and thus degrading the SNDR [5].

#### 2.4 Randomization and Calibration

The effects of channel mismatches can be reduced by employing randomization across the M parallel paths. By randomly selecting the channel to convert a given sample, the correlation between the input signal and the channel mismatch is reduced and the energy of the distortion tones is spread across the frequency band from 0 to  $f_s$ , and thus raising the noise floor [19]. A background calibration scheme can also be employed to improve the performance of time-interleaved Nyquist rate ADCs by mitigating offset and gain errors [20, 21]. However the distortion induced by phase skew is difficult to reduce by calibration as the calibration algorithms can not be run in background and require a rather complicated implementation [5].

### 2.5 Conclusion

In this chapter, the offset, gain-mismatch, phase-skew and bandwidth mismatch errors resulting from the time-interleaving of ADCs were discussed and their analytical results were presented. Amongst the errors introduced due to time-interleaving, the distortion due to clock phase-skew is the most detrimental to the resulting SNDR and can not be easily mitigated by calibration.

#### CHAPTER 3 WIDEBAND ANALOG-TO-DIGITAL CONVERTERS

This chapter discusses the issues involved with high-resolution and wideband data conversion using Nyquist rate ADCs in nano-CMOS technologies. Delta-sigma modulation based ADC architectures are gaining prominence due to their lower requirement on opamp gain and component matching requirements although their conversion bandwidth is limited as they employ oversampling. A brief exposition on delta-sigma modulators is provided and later modulation based parallel delta-sigma modulators are discussed which can potentially lead to Nyquist-rate data conversion.

### 3.1 Digital Calibration of ADCs

For conversion speeds of up to 100 - 200 MHz with resolution greater than 10 bits, the pipelined ADC has been the preferred architecture for wideband wireless, instrumentation and data acquisition applications. In the nano-CMOS processes, the performance of the pipelined ADC is constrained by the capacitor mismatch, finite op-amp gain and op-amp nonlinearity. This results from the fact that it is becoming challenging to design op-amps exhibiting high gain and wide swing in nano-CMOS. The capacitor mismatch and finite op-amp gain in the pipelined stages (called a multiplying digital-to-analog converter or simply MDAC) introduce a residue gain error while the op-amp non-linearity results in a non-linear component in the input/output characteristic of the MDAC stage. Recently there has been an emphasis on employing digital calibration to

correct the gain errors and nonlinearity in the pipelined ADC stages. Here, we briefly discuss a representative calibration scheme presented in [1].

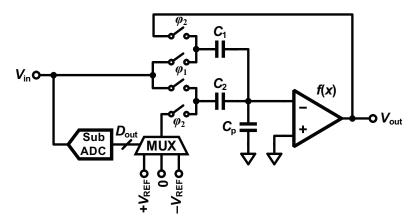

The example MDAC is shown in Figure 3.1 and its input/output relation is derived in [1] and is given by

$$V_{in} = \frac{1}{2} (1 + \varepsilon) V_{out} + f^{-1}(V_{out}) + \frac{1}{2} (1 - \varepsilon) D_{out} V_{REF}$$

$$= \frac{1}{2} (1 + \varepsilon) V_{out} + \left(1 + \frac{C_p}{2C}\right) f^{-1}(V_{out}) + \frac{1}{2} (1 - \varepsilon) D_{out} V_{REF}$$

(3.1)

where  $\varepsilon$  is the mismatch in the capacitor ratio,  $f(\cdot)$  represents the input/output characteristic of the op-amp in closed loop,  $V_{in}$  is the MDAC input voltage,  $D_{out}$  is the digital output of the sub-DAC,  $V_{out}$  is the residue of the stage, and  $V_{REF}$  is the reference used for comparison. Here,  $C_1 = C(1+\varepsilon)$ ,  $C_2 = C(1+\varepsilon)$  and  $C_p$  is the effect of the input capacitance of the op-amp. Using this model, the approximate input of the MDAC can be estimated by the third order polynomial given by [1]

$$V_{in,appx} = \alpha_1 V_{out} + \alpha_3 V_{out}^3 + \frac{1}{2} (1 - \varepsilon) D_{out} V_{REF}$$

(3.2)

Figure 3.1: A 1.5-bit pipelined stage (MDAC) [1].

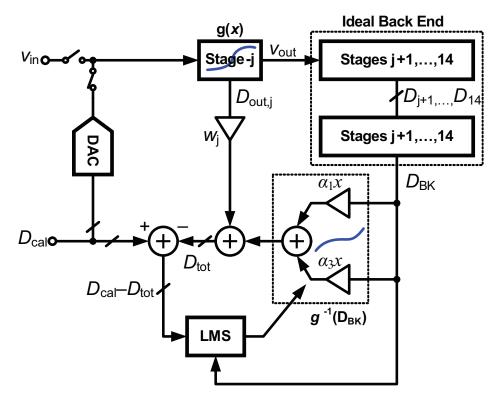

The digital calibration scheme employed in this 14-stage pipelined ADC is shown in Figure 3.2. The coefficients  $w_i$ 's account for the capacitance mismatch for each of the MDAC stages. The digital calibration estimates the values for  $\alpha_1$ ,  $\alpha_3$ , and  $w_j$  for each of the MDAC stages using a least mean square (LMS) adaptive algorithm. The calibration algorithm recursively starts by calibrating the last (and the least critical) stage. The calibrated stages together form an ideal back-end ADC and are used for calibrating the next stage in the sequence. The adaptive function  $(\alpha_1 D_{BK} + \alpha_3 D_{BK}^3)$ estimates the approximate input voltage  $V_{in,appx}$  for each of the stages and undoes the nonlinearity g(x) introduced by the stage. For the LMS algorithm, a predefined digital training input set called  $D_{cal}$  is employed. A reference DAC is used for generating the analog input  $v_{in}$  from  $D_{cal}$  vectors. The sum of all the adaptive function outputs and the weighted MDAC outputs is called  $D_{tot}$ . The difference  $D_{cal} - D_{tot}$  acts as the error term for the LMS engine, and its mean squared value is minimized for the pipelined ADC in a recursive manner. For further details on the calibration algorithm the reader is referred to [6]. Other recent examples of digital calibration of pipelined ADCs are available in [7, 22].

It is evident from the example of a pipelined ADC calibration scheme that the complexity of the system is increased by the need to accurately calibrate each of the MDAC stages. In order to realize such calibration schemes, precise back-end ADC and DACs are required for the digital correction of individual pipelined stages. It can be seen in this example that any error in the back-end ADC stages will cascade across the calibration of the subsequent stages. Thus, the convergence and resulting accuracy of such

**Figure 3.2:** Diagram showing the concept of digital calibration of a pipelined ADC in [1].

schemes is an important concern. Furthermore, besides developing proven digital calibration schemes for pipelined ADCs with good convergence, it is imperative to explore wideband ADC architectures which are inherently tolerant to device mismatches and lower op-amp gain with the continued scaling of CMOS technology.

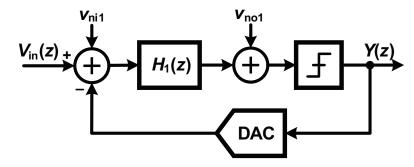

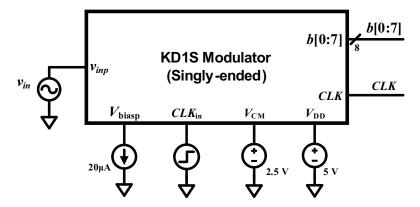

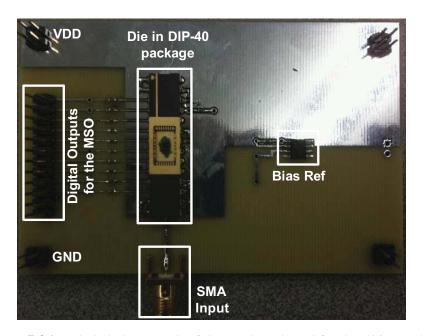

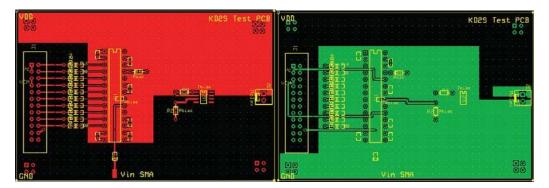

## 3.2 Delta-Sigma Modulation