# A Ka band, static, MCML frequency divider, in standard 90nm-CMOS LP for 60 GHz applications

*Citation for published version (APA):* Cheema, H. M., Mahmoudi, R., Sanduleanu, M. A. T., & Roermund, van, A. H. M. (2007). A Ka band, static, MCML frequency divider, in standard 90nm-CMOS LP for 60 GHz applications. In *IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, 2007 : 3 - 5 June 2007, Honolulu, Hawaii, USA* (pp. 541-544). Institute of Electrical and Electronics Engineers. https://doi.org/10.1109/RFIC.2007.380942

DOI: 10.1109/RFIC.2007.380942

# Document status and date:

Published: 01/01/2007

# Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

# Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# A Ka Band, Static, MCML Frequency Divider, in Standard 90nm-CMOS LP for 60 GHz Applications

Hammad M. Cheema<sup>1</sup>, Reza Mahmoudi<sup>1</sup>, M.A.T. Sanduleanu<sup>2</sup>, Arthur van Roermund<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, Mixed-signal Microelectronics group, Eindhoven University of Technology, 5600 MB, Eindhoven, The Netherlands

<sup>2</sup> Philips Research, Prof. Holstlaan 4, 5656A, Eindhoven, The Netherlands

Abstract — This paper presents a broadband, static, 2:1 frequency divider in a bulk 90nm CMOS LP (low-power) technology with maximum operating frequency of 35.5 GHz. The divider exhibits an enhanced input sensitivity, below 0 dBm, over a broad input range of 31 GHz and consumes 24mA from a 1.2 V supply. The phase noise of the divider is -124.6 dBc/Hz at 1 MHz offset from the carrier.

*Index Terms* — CMOS integrated circuits, Current mode logic, Frequency conversion, Millimeter wave circuits, Phase locked loops.

#### I. INTRODUCTION

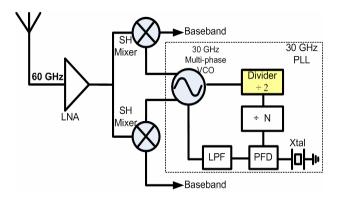

The ongoing research and development in the 60 GHz band has paved way for investigation of various possible transceiver architectures. Fig.1 shows a typical receiver architecture, which relies on sub-harmonic mixers and a 30 GHz phase locked loop. In such a tuning system the first stage of the frequency divider is a critical component due to requirements of high frequency, wide bandwidth and high input sensitivity.

The commonly used high frequency divider architectures are static, Miller and injection locked. Although, the latter two configurations can achieve high frequencies with low power consumption [5]-[6], they are inherently narrow band. Thus, they are not entirely

Fig. 1. Architecture of a 60 GHz receiver

suitable for the 7 GHz bandwidth required worldwide for the 60 GHz band. In comparison, static frequency dividers are broadband but consume more power. Another advantage of static dividers is the availability of highly matched quadrature outputs. The static frequency divider reported in [1] achieves a maximum operation frequency of 27 GHz in 120nm CMOS whereas dividers in [2], [3], [7] have been implemented in SOI technologies. They provide improved high frequency performance, however, CMOS SOI is not the mainstream technology choice. In this paper we present an improved static frequency divider with broadband operation. It is implemented in a bulk CMOS 90nm LP technology suitable for low-power, digital applications. As a key enabling component, a compact, stacked inductor is used in the latch and output buffers. The output buffers, based on  $f_{\scriptscriptstyle T}$  doublers are included for measurement purposes.

### II. CIRCUIT DESIGN

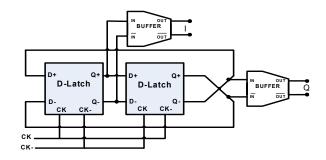

The block diagram of a conventional 2:1 static frequency divider is shown in Fig.2. It consists of two cascaded (master and slave) D-latches. The D-latches are driven by anti-phase clock pulses and the dividing operation is achieved by connecting the inverted slave outputs to master D-latch inputs. Each D-latch is based on MOS current mode logic (MCML) and consists of data

Fig. 2. Static frequency divider with output buffers

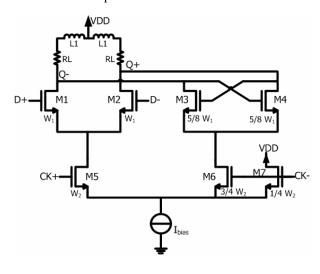

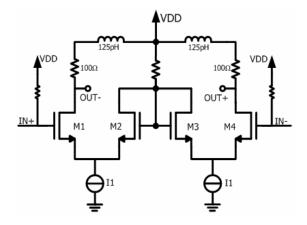

transistors: M1, M2 and latch transistors: M3, M4 as shown in Fig.3. The MCML logic is characterized by small voltage swings, thus high switching speed, constant power consumption and noise immunity due to complete differential architecture.

The maximum operating frequency of the divider depends on the speed of CML latches, which in turn is limited by technology, parasitic capacitances of devices and the layout parasitics. In this paper, effect of the latter two has been minimized by circuit optimization of the Dlatch and optimal layout of the divider.

In comparison with earlier published designs [1]-[4], which employ similar dimensions for the data and latch transistors, this design has different dimensions for the same, as shown in Fig.3. The positive feedback between M3 and M4 implies that only a small current is required by the latch part to take a hard decision between high and low level of the output. Parametric simulations reveal that the optimum width of transistors M3 and M4 is 5/8 times the width of M1 (or M2). In addition, smaller latch transistors offer less parasitic capacitances at the output nodes of M1 and M2 and thus enhance the switching speed of charge transfer between them.

As the latch transistors do not require the same current as the data transistors, selecting different dimensions for transistors M6 and M7 controls the current distribution. The latter transistor is added to maintain the differential structure for the clock inputs and avoid any imbalance. The current consumption in the data and latch transistors is 12mA and 9 mA respectively. The optimal dimensions for transistor M6 and M7 are shown in Fig.3. The shunt peaking inductor L1, in series with resistor  $R_L$ , is included for broadband operation.

Fig. 3. Proposed D-Latch Circuit schematic

#### A. Stacked Inductor design

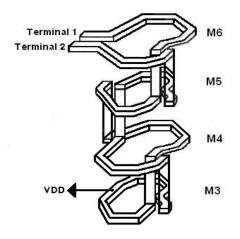

The shunt peaking inductor (L1) is implemented in a differential structure with the center point connected to VDD and has a value of 125pH. A high quality factor (Q) is not required as the load resistor connected in series with the inductor determines the effective Q. Therefore, the area of the inductor is minimized by realizing it as a stacked inductor (Fig.4) by using the top fourmetallization layers. Metal 1 is used as a fish bone structure below the inductor for better isolation.

Compared to planar inductors, this structure offers less (up to 45%) parasitic capacitance. Two consecutive layers (e.g. M6 and M5) are displaced by one metal width by which, the parasitic capacitance is present only between even layers (M6, M4) and odd layers (M5, M3). The metal to substrate capacitance is also limited to M3. Assuming the metal lengths of each half turn of the inductor as  $l_p$ ,  $l_2$ ,...,  $l_{2n}$ , the metal width as W, metal to metal overlap capacitance as  $C_{m\cdot m}(k)$  and metal to substrate capacitance is estimated by the distributed capacitance model using (1) and (2).

$$d_k = \frac{\sum_{i=1}^{k} l_i}{\sum_{i=1}^{2n} l_i} \tag{1}$$

$$C_{total} \approx \frac{1}{4} \sum_{k=n}^{n+1} C_{m-s}(k) \cdot l_k \cdot W \cdot (2 - d_k - d_{k-1})^2 + \frac{1}{4} \sum_{k=1}^{n-2} C_{m-m}(k) \cdot l_k \cdot W \cdot (d_{k+2} - d_k + d_{k+1} - d_{k-1})^2 (2) + \frac{1}{4} \sum_{k=n+1}^{2n-2} C_{m-m}(k) \cdot l_k \cdot W \cdot (d_{k+2} - d_k + d_{k+1} - d_{k-1})^2$$

Fig. 4. Stacked inductor structure used for shunt peaking

# B. Output Buffer

In many cases, output buffers excessively load the critical circuits, degrading their performance. This is true in case of a frequency divider, thus, the design of the output buffer attempts to minimize capacitive loading at the output nodes of the latches. It consists of a differential stage, modified into a  $f_T$  doubler stage by adding transistors M2 and M3 as shown in Fig.5. This setup approximately halves the Cgs capacitance as compared to a standard differential stage (keeping transconductance constant) and also increases the unity-gain bandwidth of the buffer. The compact shunt peaking inductor designed for the D-latch is re-used in the buffer without significant increase in area.

Fig. 5. Output buffer circuit schematic

### III. LAYOUT AND TECHNOLOGY

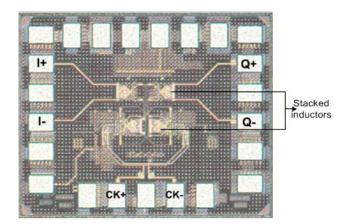

A differential design is adopted both in the D-latch and output buffers; the layout is kept as symmetric as possible. The quadrature outputs use 50 transmission lines to the bond pads. Four RF output and two RF input pads are included for measurements. The circuit was fabricated in a 90nm, bulk, CMOS, LP technology, with six metallization layers. The transistors in this technology have a measured  $f_T$  and  $f_{max}$  of 107 GHz and 280 GHz respectively. Due to bond pad limitations the chip area is 0.9 x 0.7 mm. However, the active area is less than half of the above value. The chip micrograph is shown in Fig.6.

# IV. MEASUREMENT RESULTS

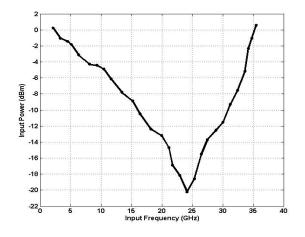

The divider was measured on wafer with high frequency differential probes (GSGSG). A 180° hybrid coupler provides the required anti-phase clock inputs. The measured input sensitivity as a function of frequency is shown in Fig.7. The highest input sensitivity is measured

Fig. 6. Chip micrograph

at 24 GHz and the maximum operating frequency of the divider is 35.5GHz. The maximum frequency division is achieved at a power consumption of 14.4 mW per D-latch from a 1.2 V power supply. Each output buffer consumes 9.6 mW and the total power consumption is 48 mW.

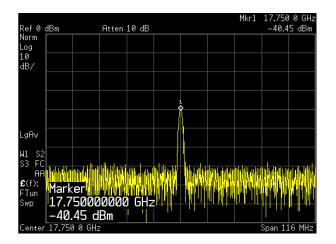

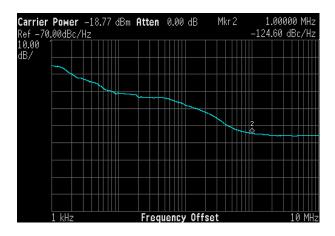

The measured output spectrum at maximum frequency of operation is shown in Fig. 8. The output power of -40 dBm includes the losses from the cables and the 180° hybrid coupler (almost 30dB). Phase noise of the divider is a key performance parameter if it is to be integrated in a phase locked loop. The measured phase noise of the divider output (see Fig.9) is -124.6dBc/Hz at 1 MHz offset from the carrier (for an input CLK of 30 GHz). The input phase noise of the generator is -119.4dBc/Hz at double frequency and same carrier power.

Table 1 shows a comparison between some recently published, static frequency dividers. The presented divider exhibits a wider operating frequency range as compared to

Fig. 7. Measured input sensitivity of the frequency divider

Measured output spectrum for a 35.5 GHz input clock Fig. 8.

SOI implementations in [2], [7] and lesser power consumption (excluding output buffers) than [1], [2], [3] and [7]. The improvement is a consequence of circuit optimization of the D-latch, the stacked inductor approach and the new output buffer implementation.

# V. CONCLUSION

We have presented an improved Ka band, static frequency divider in a standard 90nm CMOS LP technology. A stacked inductor improves the maximum toggle frequency. Compared to planar inductors, this structure offers less (up to 45%) parasitic capacitance and is very compact. The highest input sensitivity is measured at 24 GHz and the maximum operating frequency of the divider is 35.5GHz. The maximum frequency division is achieved at a power consumption of 14.4 mW per D-latch from a 1.2 V power supply. Each output buffer consumes 9.6 mW and the total power consumption is 48 mW.

Measured phase noise of the frequency divider Fig. 9.

| TABLE I<br>Comparison with Published Results |           |       |          |          |

|----------------------------------------------|-----------|-------|----------|----------|

| COM                                          | Operating | Power | Freq.    | Phase    |

|                                              | Freq      | Cons. | Range    | Noise    |

|                                              | Range     | (mW)  | Below 0- | @1MHz    |

|                                              | (GHz)     | . ,   | dBm      | (dBc/Hz) |

|                                              |           |       | (GHz)    |          |

| [1] 120nm                                    | 2-27      | 30    | 24       | N/A      |

| CMOS                                         |           |       |          |          |

| [2] 0.12µm                                   | 4-33      | 44.2  | 29       | N/A      |

| CMOS SOI                                     |           |       |          |          |

| [4] 0.12µm                                   | 1-25      | 22.5  | 6        | N/A      |

| CMOS                                         |           |       |          |          |

| [3] 90 nm                                    | 5-66      | 51    | 54       | -102     |

| CMOS SOI                                     |           |       |          |          |

| [7] 90nm                                     | 13-34     | 60    | 19       | -127     |

| CMOS SOI                                     |           |       |          |          |

#### REFERENCES

28.8

31

-124.6

2 - 35.5

- [1] H.-D. Wohlmuth, D. Kehrer, "A high sensitivity static 2:1 frequency divider up to 27GHz in 120nm CMOS," ESSCIRC 2002, pp. 823-826, Sept., 2002.

- [2] J.-O Plouchart et al., "A 33 GHz 2:1 static frequency divider in 0.12-µm SOI CMOS," IEEE Radio Frequency Integrated Circuit Conference, pp 329-332, June, 2003.

- [3] J.-O Plouchart et al., "Performance variations of a 66GHz static CML divider in 90nm CMOS," IEEE International Solid-State Circuits Conference, pp. 526-527 and 671, Feb., 2006.

- [4] Herbert Knapp et al., "25GHz Static Frequency Divider and 25Gb/s Multiplexer in 0.12µm CMOS," IEEE International Solid-State Circuits Conference, pp. 526-527 and 671, Feb., 2002.

- [5] J.Lee and B.Razavi, "A 40-GHz frequency divider in 0.18-/spl mu/m CMOS technology," IEEE J. Solid-State Circuits, vol.39, pp. 594-601, April 2004.

- [6] M. Tiebout, "A 50 GHz direct injection locked oscillator topology as low power frequency divider in 0.13 /spl mu/m CMOS," Solid-State Circuits Conference, 2003. ESSCIRC '03. Proceedings of the 29th European, pp. 73-76, Sept. 2003.

- [7] M.A.T.Sanduleanu, et al., "A 34GHz/1V prescalar in 90nm CMOS SOI," Solid-State Circuits Conference, 2005. ESSCIRC '05. Proceedings of the 31st European, pp. 109-112, Sept. 2005.

- Wei-Zhen Chen, Da-Shin Lin, "A 90dBQ, 10 Gbps Optical [8] Receiver in a 0.18 µm CMOS technology," Asian Solid-State Circuits Conference, pp. 177-180, Nov. 2005

This work

90nm CMOS