# A Low-Cost Uncooled Infrared Microbolometer Detector in Standard CMOS Technology

Deniz Sabuncuoglu Tezcan, Member, IEEE, Selim Eminoglu, Member, IEEE, and Tayfun Akin, Member, IEEE

Abstract—This paper reports the development of a low-cost uncooled infrared microbolometer detector using a commercial 0.8  $\mu$ m CMOS process, where the CMOS n-well layer is used as the infrared sensitive material. The n-well is suspended by front-end bulk-micromachining of the fabricated CMOS dies using electrochemical etch-stop technique in TMAH. Since this approach does not require any lithography or infrared sensitive material deposition after CMOS fabrication, the detector cost is almost equal to the CMOS chip cost. The n-well has a TCR of 0.5-0.7%/K, relatively low compared to state-of-the-art microbolometer materials; however, it has negligible 1/f noise due to its single crystal structure. The use of polysilicon interconnects on the support arms instead of metal reduces the overall pixel TCR to 0.34%/K, but provides a better performance due to improved thermal isolation. Measurements show that such a fabricated pixel with 74  $\mu$ m imes 74  $\mu$ m pixel area provides a thermal conductance of 0.62  $\mu$ W/K, a thermal time constant of 21 ms, a dc responsivity of 9250 V/W, and a detectivity of  $2.0 \times 10^9$ cmHz<sup>1/2</sup>/W with a total noise of 0.82  $\mu$ V for a 4 kHz bandwidth. Based on this pixel, a  $16 \times 16$  prototype focal plane array (FPA) with 80  $\mu$ m imes 80  $\mu$ m pixel size and 13% fill factor has been implemented, where built-in diodes are used to simplify array scanning, at the expense of reduced overall pixel TCR of 0.24%/K. The n-well microbolometer array with a simple readout scheme provides a responsivity of 2000 V/W, a detectivity of 2.6  $\times$  10<sup>8</sup> cmHz<sup>1/2</sup>/W, and an estimated NETD of 200 mK at 0.5 Hz frame rate. Considering that this performance can be further improved with low noise readout circuits, the CMOS n-well microbolometer is a cost-effective approach to implement very low-cost uncooled infrared detector arrays with reasonable performance.

*Index Terms*—CMOS infrared detectors, low-cost infrared detectors, microbolometers, uncooled infrared detectors.

#### I. INTRODUCTION

U NCOOLED infrared detectors have recently gained wide attention for infrared imaging applications, due to their advantages such as low cost, low weight, low power, large spectral response, and long term operation compared to those of photon detectors. Worldwide effort is still continuing to implement very large format arrays at low cost for use in various applications, including commercial applications like driver's night vision enhancement and fire fighting. One of the main issues for

The authors are with the Department of Electrical and Electronics Engineering, Middle East Technical University, Ankara, Turkey (e-mail: tayfun-akin@metu.edu.tr; http://www.eee.metu.edu.tr/~tayfuna).

Digital Object Identifier 10.1109/TED.2002.807453

achieving low-cost detectors is their monolithic integration and compatibility with CMOS technology.

The most widely used uncooled detector approach is to implement microbolometers using surface micromachined bridges on CMOS processed wafers, where infrared radiation increases the temperature of a material formed on the thermally isolated and suspended bridge, causing a change in its resistance related to its temperature coefficient of resistance (TCR) [1]-[9]. Currently, there are microbolometer arrays with  $640 \times 480$  array formats and 25  $\mu$ m  $\times$  25  $\mu$ m pixel sizes with performance approaching that of cooled photon detectors [1]. However, these detectors require deposition of some high TCR materials after CMOS fabrication and complicated post-CMOS surface micromachining processing, increasing its cost and limiting its use for ultra low-cost commercial applications. For example, vanadium oxide  $(VO_x)$ , which is the most widely known and used microbolometer material, has a high TCR of about 2-3%/K [2]; however,  $VO_x$  is not a standard material in IC fabrication and requires dedicated expensive equipment to prevent contamination of the CMOS line. In addition, it exhibits large 1/f noise due to its noncrystalline structure. There are efforts to implement surface micromachined microbolometers using IC compatible materials such as amorphous silicon [3], amorphous silicon carbide [4], and polycrystalline silicon–germanium [5]; and these materials also have high TCR values of 2.5%/K, 4-6%/K, and 2-3%/K, respectively. However, these materials require high temperature annealing to reduce their residual stress, which is not suitable for post-CMOS processing for monolithic integration. In addition, they exhibit even higher 1/f noise than VO<sub>x</sub>, due to their noncrystalline structures. Another high TCR microbolometer material that is recently used is YBaCuO, which is deposited at room temperature, however, these detectors also require complicated and expensive post-CMOS surface micromachined processes [6], [7]. There are also microbolometers implemented with IC compatible metal films [8], [9], however, these detectors still require deposition and lithography steps after CMOS and their performances are low due to low TCR of metal films. Therefore, although surface micromachined microbolometers are very cheap compared to photon detectors, their price is still high for many commercial applications due to extra processes required for their fabrication.

Low-cost infrared detectors can be implemented with front or back-end bulk-micromachining of CMOS fabricated wafers, and this approach has mostly been used to implement CMOS thermopile arrays [10], [11]. However, thermopile arrays have low responsivity values (5–15 V/W) and large pixel sizes ( $\geq$ 250  $\mu$ m  $\times$  250  $\mu$ m), limiting their use for large detector arrays. In addition, these detectors also require extra processing

Manuscript received May 1, 2002; revised October 28, 2002. This work was initially supported by NATO's Scientific Affairs Division in the framework of the Science for Stability Programme. This work was supported in part by ASELSAN, Inc., and Research and Development Department of Ministry of Defense (MSB ArGe). The review of this paper was arranged by Editor K. Najafi.

steps to form silicon islands [10] or electroplated gold lines [11] for thermal isolation between the pixels when back-end bulk-micromachining is used.

Recently, a new bulk-micromachining approach has been emerged, where silicon p-n diodes are used as uncooled infrared detectors. Up to now, two such approaches have been reported. One of them uses a suspended single p-n diode implemented in a 100  $\mu$ m  $\times$  170  $\mu$ m pixel area and fabricated using a dedicated in-house process technology [12], however, this approach does not seem suitable for large format arrays, due to its large pixel size and its large thermal time constant [13]. The other diode microbolometer approach uses suspended multiple series diodes with 40  $\mu$ m  $\times$  40  $\mu$ m pixel sizes implemented in a SOI CMOS process, and successful implementation of a 320  $\times$ 240 FPA has been reported [14]. Although this approach has very good potential for low-cost high performance uncooled detectors, the fabrication is based on a dedicated in-house SOI process, limiting its cost reduction. For ultra low-cost applications, the best approach would be to implement the detector arrays together with their readout circuitry fully in a standard CMOS process, using some simple post-CMOS etching steps where neither lithography nor detector material deposition is needed.

This paper reports the implementation of such an ultra low-cost bulk-micromachined uncooled microbolometer, where the CMOS n-well layer is used as the active sensor material [15]. The suspended n-well structure is obtained by post-CMOS anisotropic silicon etching. Since this fabrication approach does not require any lithography or advanced detector material deposition, the detector cost is almost equal to the CMOS chip cost. The performance of the n-well microbolometer is acceptable when its TCR and noise are considered together. The n-well layer has a TCR of 0.5-0.7%/K that is lower than that of deposited high TCR materials; however, it has negligible 1/f noise due to its single crystal nature, which is a clear advantage over amorphous materials with large 1/f noise. Using n-well detectors, various prototype FPAs with  $16 \times 16$  array sizes have been implemented in standard CMOS processes [16]-[18]. These studies show that the n-well microbolometer approach allows easy implementation of ultra low cost and highly reproducible CMOS integrated microbolometer FPAs with reasonable performance for commercial infrared imaging applications.

## II. n-Well Microbolometer Structure

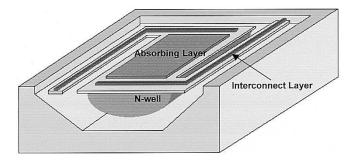

Fig. 1 shows the perspective view of the n-well microbolometer that can be obtained with a standard n-well CMOS process. Infrared radiation heats the absorbing layer on the thermally isolated n-well region, increasing its temperature, which in turn results in a change in its resistance related to its TCR value. The bulk silicon under the n-well is etched away to reduce detector's thermal conductance and to increase its responsivity. This thermally isolated suspended structure is obtained by front-end bulk-micromachining of fabricated CMOS dies, while the n-well is protected from etching by the electrochemical etch-stop technique [15], [19], [20]. The required etch openings are formed without any post-CMOS

Fig. 1. Perspective view of the n-well microbolometer that can be obtained with a standard n-well CMOS process.

TABLE Ι THERMAL CONDUCTIVITY AND HEAT CAPACITY OF THE VARIOUS LAYERS IN A 0.8 μm CMOS PROCESS BASED ON THE DATA IN LITERATURE [23]–[25]

|                                     | N-well | Dielectric | Poly Si | Metal-1 |

|-------------------------------------|--------|------------|---------|---------|

| Thermal Conductivity (W/mK)         | 141    | 1.22       | 24      | 194     |

| Heat Capacity (J/cm <sup>3</sup> K) | 1.63   | 1.74       | 1.6     | 2.23    |

| Density (gr/cm <sup>3</sup> )       | 2.33   | 2.38       | 2.33    | 2.70    |

lithography step, by placing various CMOS layers on top of each other, including active, contact, via, and passivation opening layers [21]. The absorber layer for the detector is formed with various dielectric layers available in CMOS [22]. In summary, the n-well microbolometer structure can be obtained with simple wet etching and without needing any lithography or deposition steps after CMOS fabrication, resulting in very low-cost detectors monolithically integrated with readout electronics.

The performance of the n-well microbolometer is affected by a number of design parameters and material characteristics, including pixel size, fill factor, opening width, support arm width, interconnect layer on the support arms, and the absorbing layer. The most important design parameters are the thermal isolation and effective pixel TCR. The use of metal interconnects on the support arms provides a better effective pixel TCR approaching that of n-well, however, it results in poor thermal isolation. In contrast, the use of polysilicon interconnects results in much better thermal isolation and responsivity, even though it reduces the effective pixel TCR.

The performance and structure of the n-well microbolometers are optimized using detailed simulations with various programs. Table I shows the thermal conductivity and heat capacity values of the various layers in a 0.8  $\mu$ m CMOS process based on the data in literature [23]–[25]. CoventorWare simulations show that the thermal conductance and thermal time constant of the pixel with 74  $\mu$ m × 74  $\mu$ m pixel size and 15% fill factor are 5.10  $\mu$ W/K and 3.6 ms, respectively, when metal interconnect is used. The thermal conductance decreases to 1.16  $\mu$ W/K, and thermal time constant increases to 14.3 ms, when polysilicon interconnects are used. These simulations verify that the polysilicon interconnects provide about five times improvement in thermal isolation. It should be noted that polysilicon interconnect provides a larger electrical resistance and therefore in-

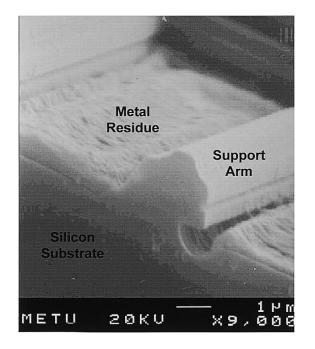

Fig. 2. SEM photograph of one opening just after the CMOS process, where the aluminum residue is clearly visible.

creases the pixel noise, but it is still preferred over metal arms considering the overall pixel performance. Various simulations have also been performed using Kidger Optics Software to estimate the performance of the absorber layer, which is chosen as the oxide-metal-passivation sandwich layer. These simulations verify that the absorptance is in the 8–14  $\mu$ m band, having a peak at 10.5  $\mu$ m wavelength. It should be noted that it is possible to implement different absorber structures in CMOS to increase the absorptance of CMOS infrared detectors [22].

# **III. DETECTOR FABRICATION**

Various n-well microbolometers with different sizes and structures are designed and sent to fabrication in a standard  $0.8 \ \mu m$  CMOS process. After CMOS fabrication, the detectors are suspended and thermally isolated using a post-CMOS process. First, any metal residue in etch openings are removed, so that the silicon etchant can reach and etch the bulk silicon underneath the n-well. The metal residue is left in the narrow opening areas especially in submicron processes due to thicker dielectric and metal layers. Fig. 2 shows an SEM photograph of one opening just after the CMOS process, where the aluminum residue is clearly visible. This residue is removed with a standard aluminum etchant, while bonding pads are protected. In the second step, the die is exposed to an anisotropic silicon etchant, while a four-terminal electrochemical etch-stop technique is used to prevent the etching of the n-well [26]. Among various anisotropic silicon etchants, TMAH has been chosen since it is safe to use and is selective to silicon dioxide. A 5 wt.% TMAH solution at 85 °C is used, while ammonium peroxidisulfate [(NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>8</sub>] is added to prevent hillock formation. An additional 1.6 wt.% powder silicon is dissolved to prevent etching of the aluminum pads [27]. The details of this post-CMOS etching process can be found elsewhere [15], [19], [20].

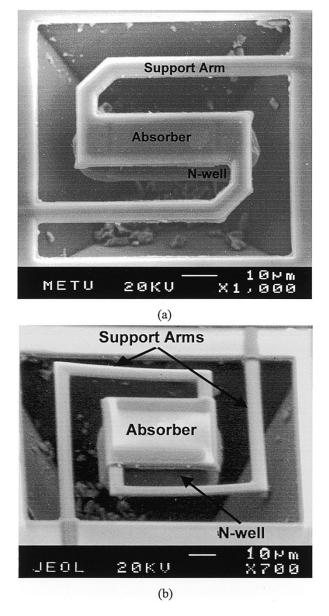

Fig. 3. SEM photographs of the post-processed single pixel n-well microbolometers: (a) with 74  $\mu$ m × 74  $\mu$ m pixel size and 15% fill factor, and (b) with 100  $\mu$ m × 100  $\mu$ m pixel size and 17% fill factor having longer arms to obtain better thermal isolation of the n-well.

Fig. 3 shows SEM photographs of post-processed single pixel n-well microbolometers. Fig. 3(a) shows a pixel with a 74  $\mu$ m × 74  $\mu$ m area and 15% fill factor, and Fig. 3(b) shows a pixel with a 100  $\mu$ m × 100  $\mu$ m area and 17% fill factor, where longer arms are implemented to obtain better thermal isolation. It should be noted here that the fill factors are low due to 10  $\mu$ m-wide openings, which are necessary to reduce the undesired metal residue.

## IV. TEST RESULTS OF SINGLE PIXEL DETECTORS

A number of electrical and optical tests are performed to characterize the n-well microbolometers. Electrical measurements show that the sheet resistances of the n-well and polysilicon layers are 1.19 k $\Omega$ /sq. and 24  $\Omega$ /sq., respectively. The TCR of the n-well and polysilicon layers are measured as 0.58%/K and 0.09%/K, respectively. The effective TCR of a pixel is the

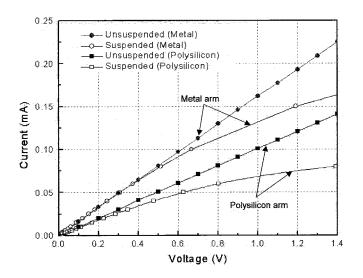

Fig. 4. Resistance variation of two pixels with polysilicon and metal interconnects upon the applied electrical power for the structure shown in Fig. 3(a). The resistance of the suspended n-well microbolometers increase with the applied bias; the I-V curves of the unsuspended pixels remain linear, giving the resistance of pixels with metal and polysilicon interconnect layers as 6.05 k $\Omega$  and 10.07 k $\Omega$ , respectively.

weighted average of the n-well and interconnect TCR values: it is equal to the TCR of the n-well layer for detectors with metal interconnect and it is lower for detectors with polysilicon interconnect. For example, the TCR of the n-well microbolometer structure given in Fig. 3(a) is measured as 0.34%/K when implemented with polysilicon interconnects.

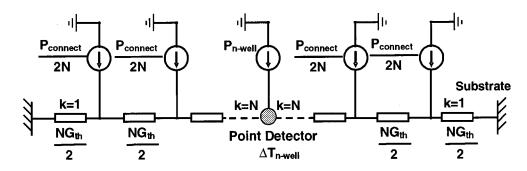

The thermal conductance of the pixels is measured using selfheating effect of the suspended pixels in vacuum. Fig. 4 shows resistance variation of two pixels with polysilicon and metal interconnects upon the applied electrical power for the structure shown in Fig. 3(a). The graphs in Fig. 4 verify that only the resistance of the suspended n-well microbolometers increase with the applied bias; the I-V curves of the unsuspended pixels remain linear, giving the resistance of pixels with metal and polysilicon interconnect layers as  $6.05 \text{ k}\Omega$  and  $10.07 \text{ k}\Omega$ , respectively. Using the data of the suspended structures and knowing the effective TCR of the pixels, the thermal conductance of the n-well microbolometers with metal and polysilicon interconnects are measured as 4.6  $\mu$ W/K and 0.62  $\mu$ W/K at 10 mtorr, respectively. In these measurements, care is taken when determining the amount of power that causes temperature increase. In detectors with metal interconnect, almost all the applied power is dissipated in the n-well, contributing fully on the temperature increase of the pixel. However, in detectors with polysilicon interconnects, the applied power is dissipated both in the n-well and polysilicon arms, reducing the temperature increase of the pixel. Fig. 5 shows the distributed thermal model of the pixel used in the analysis of self-heating upon applied bias. In this model, the suspended n-well is assumed to be a point detector with thermal conductance of  $G_{th}$ , and each support arm is divided into N units with thermal conductance of  $NG_{th}/2$ . The temperature rise of the pixel can be determined using superposition of individual power sources in the distributed model as

$$\Delta T_{n\text{-well}} = \frac{P_{n\text{-well}}}{G_{th}} + \frac{P_{connect}N(N+1)}{2G_{th}N^2} \tag{1}$$

where  $P_{n-well}$  is the power dissipated in the n-well, and  $P_{connect}$  is the power dissipated on the support arms. When the number of units (N) goes to infinity, the temperature increase can be found as

$$\lim_{N \to \infty} \Delta T_{n\text{-well}} = \frac{P_{n\text{-well}}}{G_{th}} + \frac{P_{connect}}{2G_{th}}.$$

(2)

This result indicates that effective thermal conductance for the support arms actually doubles, resulting in less temperature rise than expected. For example, for the pixel in Fig. 3(a) with polysilicon arm, only 78% of the total applied power effectively contributes to the temperature rise.

Optical tests are performed to determine the responsivity of the detectors. Detector responsivity depends on biasing and readout scheme, and in the case of a simple constant current biasing, it can be given as

C

$$\Re = \frac{\eta \alpha_{pixel} i_{bias} R_{pixel}}{G_{th} \sqrt{\left(1 + (2\pi f \tau)^2\right)}} \tag{3}$$

$$\alpha_{pixel} = \frac{\alpha_{connect} R_{connect} + \alpha_{n-well} R_{n-well}}{R_{pixel}}$$

(4)

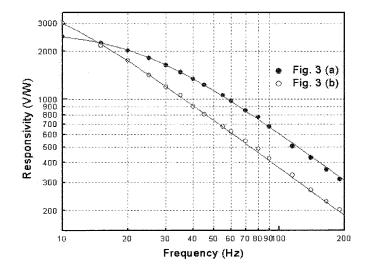

$$R_{pixel} = 2R_{connect} + R_{n-well} \tag{5}$$

where  $\eta$  is absorptance,  $G_{th}$  is thermal conductance,  $\tau$  is the thermal time constant of the pixel,  $R_{n-well}$  is n-well resistance,  $R_{connect}$  is interconnect resistance of each arm,  $R_{pixel}$  is the total pixel resistance,  $\alpha_{n-well}$  is the TCR of the n-well layer,  $\alpha_{connect}$  is the TCR of the interconnect material,  $\alpha_{pixel}$  is the total effective TCR of the suspended pixel, f is the modulation frequency of the infrared radiation, and  $i_{bias}$  is the applied bias current. As it is seen from (3), responsivity depends on the infrared modulation frequency due to the thermal time constant of the pixel. Using this equation and measuring the responsivity at different modulation frequencies, both the dc responsivity and thermal time constant of the pixels can be measured. For example, Fig. 6 shows the responsivity data for the two structures in Fig. 3 with metal arms measured with respect to infrared modulation frequency, where dc bias currents are selected to provide 2.5 V across the detector pixel. From this data, the dc responsivity and thermal time constant of the pixel in Fig. 3(a) are extracted as 2700 V/W and 6.9 ms, respectively; for the pixel in Fig. 3(b) the same parameters are extracted as 5100 V/W and 22 ms, respectively. Having a high responsivity alone is not that important, instead, detectivity is a more important parameter to evaluate the performance of the n-well microbolometer.

The detectivity  $(D^*)$  of the n-well microbolometer can be obtained as

$$D^* = \frac{\Re\sqrt{A_{det}\Delta f_e}}{V_n} \tag{6}$$

where  $\Re$  is the responsivity,  $A_{det}$  is the active area of the detector,  $\Delta f_e$  is the electrical bandwidth, and  $V_n$  is the total rms noise voltage. To determine the detectivity of the n-well microbolometers, their noise values are measured for different structures.

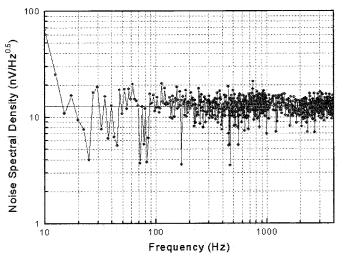

N-well resistor noise principally consists of thermal (Johnson) and 1/f noise. Since n-well layer is single crystal, it is expected that 1/f noise to be low and thermal noise to be dominant. This is a major advantage of the n-well

Fig. 5. Distributed thermal model of the pixel used in the analysis of self-heating upon applied bias.

Fig. 6. Measured responsivity of the two n-well microbolometers with metal interconnects shown in Fig. 3 with respect to infrared modulation frequency.

microbolometer over the other microbolometers implemented with amorphous microbolometer materials. It should be mentioned here that the detector structures with polysilicon interconnect exhibit some 1/f noise due to its noncrystalline structure, however, the measurements show that even these structures have negligible 1/f noise with a knee frequency below 20 Hz (Fig. 7).

The noise of the n-well microbolometers are measured using HP4395A Spectrum Analyzer through a custom preamplifier that has a gain of 1000 V/V with 3 dB points at 20 Hz and 13.7 kHz. Fig. 7 shows the measured noise spectral density of the n-well microbolometer for the structure in Fig. 3(a) with polysilicon interconnects. The average noise spectral density is measured to be 12.8 nV/Hz<sup>1/2</sup> and 10.5 nV/Hz<sup>1/2</sup> for the pixels with polysilicon and metal interconnects, resulting in a total rms noise voltage of 0.82  $\mu$ V and 0.67  $\mu$ V for a 4 kHz electrical bandwidth, respectively. These overall noise values are very close to the thermal noise component of the n-well microbolometers, showing that 1/f noise component of the single crystal n-well microbolometers are very small indeed. Based on these measurements, the detectivities of the n-well microbolometers with polysilicon and metal interconnect are determined as 2.0  $\times$  10<sup>9</sup> cmHz<sup>1/2</sup>/W and 7.3  $\times$  10<sup>8</sup>  $cmHz^{1/2}/W$ , respectively. Table II shows the summary of the device parameters and performance results of the single-pixel n-well microbolometer structure shown in Fig. 3(a) with metal and polysilicon interconnect layers.

Fig. 7. Measured noise spectral density of the n-well microbolometer with polysilicon interconnect having an average value of  $12.8 \text{ nV/Hz}^{1/2}$ . This value is very close to the thermal noise component, showing that 1/f noise of the single crystal n-well is very small.

TABLE II SUMMARY OF THE DEVICE PARAMETERS AND PERFORMANCE RESULTS OF THE n-Well Microbolometer Structure Shown in Fig. 3(a) With Metal AND Polysilicon Interconnect Layers

| Interconnect Material                 | Metal               | Poly Si             |

|---------------------------------------|---------------------|---------------------|

| Resistance @ 300K (kΩ)                | 6.05                | 10.07               |

| TCR (%/K)                             | 0.58                | 0.34                |

| Thermal Conductance (µW/K)            | 4.6                 | 0.62                |

| Thermal Time Constant (msec)          | 6.9                 | 21                  |

| Responsivity (V/W)                    | 2700                | 9250                |

| Average Noise (nV/Hz <sup>1/2</sup> ) | 10.5                | 12.8                |

| $D^*$ (cm.Hz <sup>1/2</sup> /W)       | 7.3x10 <sup>8</sup> | 2.0x10 <sup>9</sup> |

## V. ARRAY IMPLEMENTATION

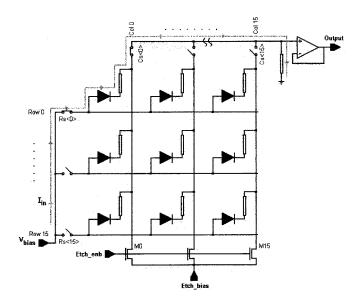

Various 16  $\times$  16 n-well microbolometer array prototypes have been implemented together with their readout circuitry in a 0.8  $\mu$ m CMOS process [16]–[18]. Fig. 8 shows the schematic view of the electronic pixel connection inside the array. To

Fig. 8. Schematic view of the electronic pixel connection inside the array and the circuitry used for etching process.

simplify the readout scheme and to reduce the number of interconnects, built-in diodes are used within the pixels instead of MOS switches. Fig. 8 also shows the required etching circuitry that is used to connect all the n-wells in the array to passivation potential during etching. This is achieved by turning on transistors  $M_0-M_{15}$  [19]. Under normal operation conditions, transistors  $M_0-M_{15}$  are turned off, and each pixel connected to the output by the scanning circuitry, which is monolithically integrated with the detector array. Microbolometer pixels in the array have polysilicon interconnect layers to have better thermal isolation, at the expense of increased noise and reduced pixel TCR.

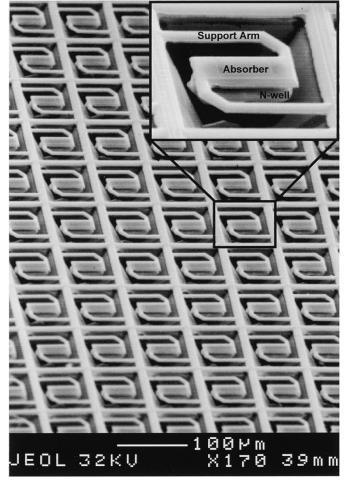

Fig. 9 shows an SEM photograph of a fabricated and post-processed array die verifying that all n-well structures are suspended and none of the support arms are broken. The suspended structures remain flat without any extra stress-reducing process steps after CMOS fabrication. It should be noted that the bulk silicon regions between the suspended n-wells reduce the thermal cross-talk, eliminating the need for gold stripes or silicon islands between the pixels, which have been used in other low-cost CMOS imagers that use thermocouples as detection mechanism [10], [11].

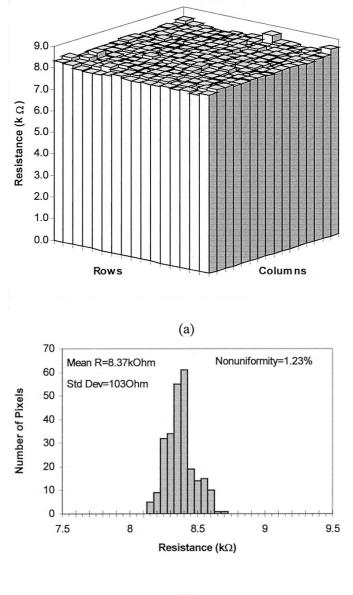

The array pixel uniformity is determined by measuring the resistance values of the individual pixels. Fig. 10(a) and (b) shows the resistance measurement results and the histogram plot of the 256 pixels, respectively, verifying their high uniformity. The mean value of the pixel resistances is 8.37 k $\Omega$  with a standard deviation of 103  $\Omega$  and a nonuniformity of 1.23%. This nonuniformity is expected to determine the overall nonuniformity of the arrays, as the other parameters, like the thickness and dimensions of the dielectric absorber layer, are usually very uniform in mature CMOS processes.

The performance of the n-well microbolometers decreases when implemented in an array format, due to the diode that is incorporated inside the pixel. The effective TCR of the pixel

Fig. 9. SEM photograph of a fabricated and post-processed array die verifying that all n-well structures are suspended and none of the support arms are broken. The suspended structures remain flat without any extra stress-reducing process steps after CMOS fabrication.

reduces due the negative TC of the diode, which modifies the effective pixel TCR in (3) and (4) as

$$\alpha_{pixel} = \frac{1}{i_{bias}R_{pixel}} \frac{dV_D}{dT} + \frac{\alpha_{poly}R_{poly} + \alpha_{n-well}R_{n-well}}{R_{pixel}}$$

(7)

where  $R_{n-well}$  is n-well resistance,  $R_{poly}$  is polysilicon resistance in each arm,  $R_{pixel}$  is the total pixel resistance,  $\alpha_{n-well}$  is TCR of n-well layer,  $\alpha_{poly}$  is TCR of polysilicon layer,  $i_{bias}$  is the applied bias current, and  $V_D$  is diode voltage. Since the diode term  $dV_D/dT$  is negative with a typical value of -2 mV/K, the effective pixel TCR in the array is reduced to about 0.24%/K.

Based on above measurements, the responsivity and detectivity of the n-well microbolometer in the array are determined as 2000 V/W and 2.6 × 10<sup>8</sup> cmHz<sup>1/2</sup>/W, respectively. The overall noise voltage at the array output with the simple readout scheme is calculated as 0.174  $\mu$ V for 0.5 frames per second scanning rate, considering the pixel and readout circuit noise. The expected NETD value of the array is 200 mK, with f/1optics and an array bias voltage of 5 V. Table III summarizes the device parameters and performance results of the 16 × 16 n-well microbolometer array with a simple readout circuit.

These results show that the performance of the n-well microbolometer FPAs is lower than that of the high-cost high-TCR

(b)

Fig. 10. Measured uniformity results of the  $16 \times 16$  prototype array: (a) resistance measurement results and (b) the histogram plot of the 256 pixels. The mean value of the pixel resistances is 8.37 k $\Omega$  with a standard deviation of 103  $\Omega$  and a nonuniformity of 1.23%.

TABLE III COMPARISON OF CMOS n-WELL MICROBOLOMETER DETECTOR ARRAY WITH POST-CMOS BULK MICROMACHINED THERMOPILE ARRAYS

| Parameter                            | Ref. [10]           | Ref. [11]            | N-well              |  |

|--------------------------------------|---------------------|----------------------|---------------------|--|

| Process (CMOS)                       | 3µm                 | lμm                  | 0.8µm               |  |

| Array Size (# of pixels)             | 32 x 32             | 10 x 10              | 16 x 16             |  |

| Pixel Size (µm <sup>2</sup> )        | 375 x 375           | 250 x 250            | 80 x 80             |  |

| Chip Size (mm <sup>2</sup> )         | 16 x 16             | 5.5 x 6.2            | 2.1 x 2.1           |  |

| Responsivity (V/W)                   | 15                  | 4                    | 2000                |  |

| Detectivity (cmHz <sup>1/2</sup> /W) | 1.6x10 <sup>7</sup> | 1.56x10 <sup>7</sup> | 2.6x10 <sup>8</sup> |  |

| NETD                                 | 500mK*@ 6.7fps      | 320mK @ 0.5fps       | 200mK*@ 0.5fps      |  |

|                                      | *Expecte            | d.                   | l                   |  |

surface micromachined microbolometers. However, n-well microbolometer FPAs still show a better performance than other very low cost and simple post-CMOS processed infrared detector arrays, like bulk-micromachined CMOS thermopile arrays. Table III shows the comparison of the CMOS n-well microbolometer detector array with post-CMOS bulk-micromachined thermopile arrays reported in literature [10], [11]. The pixel size of the n-well microbolometer is  $80 \,\mu\text{m} \times 80 \,\mu\text{m}$ , which is much smaller than 375  $\mu$ m imes 375  $\mu$ m and 250  $\mu$ m imes250  $\mu$ m. The responsivity of n-well is 2000 V/W, which is much larger than 15 V/W and 4 V/W, while the detectivity of the n-well is  $2.6 \times 10^8$  cmHz<sup>1/2</sup>/W, which is an order of magnitude larger than the thermopile arrays. The n-well microbolometer array performance can be improved further by using a low noise preamplifier circuit, even at higher scanning rates. Another advantage of the n-well microbolometers is that the pixels are thermally isolated due to front-side bulk-micromachining, however, thermopile detector arrays require extra processing steps to form silicon islands [10] or electroplated gold lines [11] for thermal isolation between the pixels when back-end bulk-micromachining is used. It should be noted here that the main advantage of the thermopiles is that they do not require a thermoelectric temperature stabilizer, but the temperature stabilizers can also be eliminated from microbolometers using temperature compensated readout design or using digital signal processor based temperature compensation [28].

# VI. CONCLUSION

Low-cost uncooled infrared microbolometer detectors and FPAs have been developed using a commercial CMOS process without requiring any masking or photolithography steps. The microbolometer uses the CMOS n-well layer as the infrared sensitive material. The n-well layer is suspended by front-end bulk-micromachining of the fabricated CMOS dies, while the n-well region is protected from etching by electrochemical etch-stop technique using a TMAH solution. Various single pixel n-well microbolometers with different pixel sizes and different interconnect layers have been implemented in a 0.8  $\mu$ m CMOS process. Pixels with polysilicon interconnect provide much better thermal isolation, resulting in a better overall pixel performance, despite the fact that polysilicon interconnect reduces the overall pixel TCR and increases the overall noise and thermal time constant. Such a pixel with a 74  $\mu$ m  $\times$  74  $\mu$ m pixel size and a fill factor of 15% provides a measured responsivity of 9250 V/W and a detectivity of  $2.0 \times 10^9$  cmHz<sup>1/2</sup>/W. The pixel fill factors are low due to the limitations coming from bulk-micromachining and required wide etch openings. Various  $16 \times 16$  prototype arrays have been implemented, where the pixel size is increased to 80  $\mu$ m  $\times$  80  $\mu$ m and the fill factor is reduced to 13% due to the routing metals. The effective TCR of the array pixel is reduced to 0.24%/K due to the built-in diode and polysilicon interconnect layer. The array provides a responsivity of 2000 V/W, a detectivity of  $2.6 \times 10^8 \text{ cmHz}^{1/2}$ /W, and an estimated NETD of 200 mK at 0.5 Hz frame rate. The CMOS n-well microbolometer performance can be increased significantly by using advanced readout techniques and high fill factor structures which can be obtained with finer CMOS

technologies and different post-CMOS processing approaches. Therefore, the CMOS n-well microbolometer detector is a promising approach to implement very low-cost uncooled infrared detector arrays with reasonable performance.

#### ACKNOWLEDGMENT

The authors would like to thank O. S. Akar and M. Y. Tanrikulu for their help in process and CoventorWare simulations, the Physics Department of METU, and ASELSAN, Inc., for help and equipment support.

#### REFERENCES

- D. Murphy, M. Ray, R. Wyles, J. Asbrock, N. Lum, J. Wyles, C. Hewitt, G. Graham, W. Radford, J. Anderson, D. Bradley, R. Chin, and T. Kostrzewa, "High sensitivity (25 μm pitch) microbolometer FPA's and application development," *Proc. SPIE*, vol. 4369, pp. 222–234, 2001.

- [2] R. A. Wood, "Uncooled thermal imaging with monolithic silicon focal planes," *Proc. SPIE*, vol. 2020, pp. 322–329, 1993.

- [3] E. Mottin, J. Martin, J. Ouvrier-Buffet, M. Vilain, A. Bain, J. Yon, J. L. Tissot, and J. P. Chatard, "Enhanced amorphous silicon technology for 320 × 240 microbolometer arrays with a pitch of 35 μm," *Proc. SPIE*, vol. 4369, pp. 250–256, 2001.

- [4] T. Ichihara, Y. Watabe, Y. Honda, and K. Aizawa, "A high performance amorphous  $Si_{1-x}C_x$ : H thermistor bolometer based on micro-machined structure," in *Int. Conf. on Solid-State Sensors & Actuators (TRANSDUCERS*'97), 1997, pp. 1253–1256.

- [5] S. Sedky, P. Fiorini, K. Baert, L. Hermans, and R. Mertens, "Characterization and optimization of infrared poly SiGe bolometers," *IEEE Trans. Electron Devices*, vol. 46, pp. 675–682, Apr. 1999.

- [6] H. Wada, T. Sone, H. Hata, Y. Nakaki, O. Kaneda, Y. Ohta, M. Ueno, and M. Kimata, "YBaCuO uncooled microbolometer IR FPA," *Proc. SPIE*, vol. 4369, pp. 297–304, 2001.

- [7] M. Almasri, D. P. Butler, and Z. C. Butler, "Semiconducting YBCO bolometers for uncooled IR detection," *Proc. SPIE*, vol. 4028, pp. 17–26, 2000.

- [8] A. Tanaka, S. Matsumoto, N. Tsukamoto, S. Itoh, T. Endoh, A. Nakazato, Y. Kumazawa, M. Hijikawa, H. Gotoh, T. Tanaka, and N. Teranishi, "Silicon IC process compatible bolometer infrared focal plane array," in *Int. Conf. on Solid-State Sensors & Actuators (TRANSDUCERS*'95), 1995, pp. 632–635.

- [9] H.-K. Lee, J.-B. Yoon, E. Yoon, S.-B. Ju, Y.-J. Yong, W. Lee, and S.-G. Kim, "A high fill-factor infrared bolometer using micromachined multilevel electrothermal structures," *IEEE Trans. Electron Devices*, vol. 46, pp. 1489–1491, July 1999.

- [10] A. D. Oliver and K. D. Wise, "A 1024-element bulk-micromachined thermopile infrared imaging array," *Sens. Actuators A*, vol. 73, pp. 222–231, 1999.

- [11] A. Schaufelbuhl, N. Schneeberger, U. Munch, M. Waelti, O. Paul, O. Brand, H. Baltes, C. Menolfi, Q. Huang, E. Doering, and M. Loepfe, "Uncooled low-cost thermal imager based on micromachined CMOS integrated sensor array," *J. Microelect. Syst.*, vol. 10, pp. 503–510, Dec. 2001.

- [12] J. Kim and C. Han, "A new uncooled thermal infrared detector using silicon diode," Sens. Actuators A, vol. 89, pp. 22–27, 2001.

- [13] J. C. Brasunas, B. Lakew, and R. Fettig, "A comment on reported detectivity of a new uncooled thermal infrared detector," *Sens. Actuators A*, vol. 96, pp. 211–213, 2002.

- [14] T. Ishikawa, M. Ueno, Y. Nakaki, K. Endo, Y. Ohta, J. Nakanishi, Y. Kosasayama, H. Yagi, T. Sone, and M. Kimata, "Performance of 320 × 240 uncooled IRFPA with SOI diode detectors," *Proc. SPIE*, vol. 4130, pp. 1–8, 2000.

- [15] D. S. Tezcan, F. Kocer, and T. Akin, "An uncooled microbolometer infrared detector in any standard CMOS technology," in *Int. Conf.* on Solid-State Sensors & Actuators (TRANSDUCERS'99), 1999, pp. 610–613.

- [16] D. S. Tezcan, S. Eminoglu, O. S. Akar, and T. Akin, "A low cost uncooled infrared microbolometer focal plane array using the CMOS n-well layer," in *Int. Conf. on Micro Electromechanical Systems (MEMS* 2001), 2001, pp. 566–569.

- [17] —, "An uncooled microbolometer infrared focal plane array in standard CMOS," *Proc. SPIE*, vol. 4288, pp. 112–121, 2001.

- [18] S. Eminoglu, D. S. Tezcan, and T. Akin, "A CMOS n-well microbolometer FPA with temperature coefficient enhancement circuitry," *Proc. SPIE*, vol. 4369, pp. 240–249, 2001.

- [19] E. H. Klaassen, R. J. Reay, C. Storment, and G. T. A. Kovacs, "Micromachined thermally isolated circuits," *Sens. Actuators A*, vol. 58, pp. 43–50, 1997.

- [20] T. Akin, Z. Olgun, O. Akar, and H. Kulah, "An integrated thermopile structure with high responsivity using any standard CMOS process," *Sens. Actuators A*, vol. 66, pp. 218–224, 1998.

- [21] M. Parameswaran, H. Baltes, L. Ristic, D. Dhaded, and A. Robinson, "A new approach for the fabrication of micromechanical structures," *Sens. Actuators A*, vol. 19, pp. 289–307, 1989.

- [22] N. Schneeberger, O. Paul, and H. Baltes, "Spectral infrared absorption of CMOS thin film stacks," in *Int. Conf. on Micro Electromechanical Systems (MEMS'99)*, 1999, pp. 106–111.

- [23] O. Paul, M. von Arx, and H. Baltes, "CMOS IC: Complete set of thermal conductivities," in *Semiconductor Characterization—Present Status and Future Needs, American Institute of Physics*, 1996, pp. 197–201.

- [24] M. von Arx, O. Paul, and H. Baltes, "Test structures to measure the heat capacity of CMOS layer sandwiches," in *Proc. IEEE Int. Conf. Microelectronic Test Structures*, 1997, pp. 203–208.

- [25] —, "Determination of the heat capacity of CMOS layers for optimum sensor design," *Sens. Actuators A*, vol. 46/47, pp. 428–431, 1995.

- [26] B. Kloeck, S. D. Collins, N. F. Rooij, and R. Smith, "Study of electrochemical etch-stop for high-precision thickness control of silicon membranes," *IEEE Trans. Electron Devices*, vol. 36, pp. 663–669, Apr. 1989.

- [27] G. Yan, P. C. H. Chan, I. Hsing, R. K. Sharma, and J. K. O. Sin, "An improved TMAH Si-etching solution without attacking exposed aluminum," in *Int. Conf. on Micro Electromechanical Systems (MEMS'00)*, 2000, pp. 562–567.

- [28] W. Parrish and J. T. Woolaway, "Methods and circuitry for correcting temperature-induced errors in microbolometer focal plane array," U.S. Patent 5 756 999, May 26, 1998.

**Deniz Sabuncuoglu Tezcan** (M'02) was born in Ankara, Turkey, in 1973. She received the B.S., M.S., and Ph.D. degrees in electrical engineering with honors from Middle East Technical University (METU), Ankara, in 1995, 1997, and 2002, respectively. Her doctoral studies focused on fabrication, modeling, and characterization of n-well microbolometer type uncooled infrared detectors implemented in CMOS technology. From September 1998 to January 1999, she continued her studies in IMEC, Belgium through the Integrated Ph.D.

Scholarship Program from the Scientific and Technical Research Council of Turkey (TUBITAK).

From 1995 to 2002, she was employed as a Teaching and Research Assistant in the Electrical and Electronics Engineering Department of METU. Currently she is working as an Instructor in Electrical and Electronics Engineering Department of METU.

Selim Eminoglu (M'02) was born in Ankara, Turkey, in 1973. He received the B.S. and M.S. degrees in electrical engineering with honors from Middle East Technical University (METU), Ankara, in 1996 and 1998, respectively. Currently he is pursuing the Ph.D. degree in the Electrical and Electronics Engineering Department of METU on the design and implementation of uncooled infrared focal plane arrays in CMOS technology.

From 1995 to 1998, he worked as a part-time Researcher in the VLSI Design Center of

TUBITAK-BILTEN where he has contributed to the development of a programmable mixed-signal ASIC chip for audio band signal processing applications. Since 1996, he has been a Teaching and Research Assistant in the Electrical and Electronics Engineering Department of METU.

**Tayfun Akin** (M'97) was born in Van, Turkey, in 1966. He received the B.S. degree in electrical engineering with high honors from Middle East Technical University, Ankara, in 1987 and went to the USA in 1987 for his graduate studies with a graduate fellowship provided by the NATO Science Scholarship Program through the Scientific and Technical Research Council of Turkey (TUBITAK). He received the M.S. degree in 1989 and the Ph.D. degree in 1994 in electrical engineering, both from the University of Michigan, Ann Arbor.

Since 1995 and 1998, he has been employed as an Assistant Professor and Associate Professor, respectively, in the Department of Electrical and Electronics Engineering at Middle East Technical University, Ankara, Turkey. He is also the technical coordinator of METU-MET, an IC fabrication factory which is transferred to Middle East Technical University by the government for MEMS related production. His research interests include MEMS (Micro-Electro-Mechanical Systems), Microsystems Technologies, infrared detectors and readout circuits, silicon-based integrated sensors and transducers, and analog and digital integrated circuit design. He has served in various MEMS, EUROSENSORS, and TRANSDUCERS conferences as a Technical Program Committee Member. He is the designate co-chair of IEEE MEMS Conference to be held in 2006. He is the winner of the First Prize in Experienced Analog/Digital Mixed-Signal Design Category at the 1994 Student VLSI Circuit Design Contest organized and sponsored by Mentor Graphics, Texas Instruments, Hewlett-Packard, Sun Microsystems, and Electronic Design Magazine. He is the co-author of the symmetric and decoupled gyroscope project which won the first prize award in the operational designs category of the international design contest organized by DATE Conference and CMP in March 2001.