# A low-power accelerometer IC with high sensitivity

Wang, Yan Mei

2015

Wang, Y. M. (2015). A low-power accelerometer IC with high sensitivity. Doctoral thesis, Nanyang Technological University, Singapore.

https://hdl.handle.net/10356/62234

https://doi.org/10.32657/10356/62234

Downloaded on 24 Aug 2022 21:07:20 SGT

## A LOW-POWER ACCELEROMETER IC WITH

## HIGH SENSITIVITY

WANG YAN MEI

SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

2015

A LOW-POWER ACCELEROMETER

## A LOW-POWER ACCELEROMETER IC WITH HIGH SENSITIVITY

WANG YAN MEI

2015

A LOW-POWER ACCELEROMETER

IC WITH HIGH SENSITIVITY

School of Electrical and Electronic Engineering

A thesis submitted to the Nanyang Technological University in partial fulfilment of the requirement for the degree of Doctor of Philosophy

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my deepest and sincere gratitude to my project supervisor, Associate Professor Chan Pak Kwong for all his knowledgeable supervision, most patient and detailed guidance and continual constructive criticism through my whole PhD project. With super dedication and enthusiastic pure attitude towards academic research and professionalism, he has always continually inspired and stimulated each student working with him. Feeling privileged to be one of his students, I could not have imagined having a better supervisor and mentor for my study.

I would like to give my warmest appreciation to Prof. Li King Ho Holden and Dr Ong Soon-Eng for all their most kindly cooperation and support on providing the mechanical sensor as well as giving their invaluable advice and suggestions throughout my project. It is a great fortune to work together with them. Their invaluable friendship has made my PhD life most enjoyable and memorable.

I would also like to give my special thanks to the technical staffs Mr. Sia Liang Poo, Mr. Seow Yong Hing in VLSI lab and Ms. Seow-Guee Geok Lian and Mr. Goh Mia Yong in IC Design II lab for all their uncountable help and assistance.

My sincere thanks also goes to Dr Chong Sau Siong and Mr. Tan Xiao Liang for their kind friendship, valuable suggestions and constant encouragement on my study and work.

Last but not least, I would like to express my deepest gratitude to all my family members for having always been there providing me with the warmest and strongest support and have always been the most encouraging motivation on my study all these years.

## **TABLE OF CONTENTS**

| AcknowledgmentsI                                                            |

|-----------------------------------------------------------------------------|

| List of FiguresVI                                                           |

| List of TablesX                                                             |

| AbstractXI                                                                  |

| Chapter 11                                                                  |

| Introduction1                                                               |

| 1.1 Background and Motivations1                                             |

| 1.2 Objectives                                                              |

| 1.3 Major Contributions of the Thesis                                       |

| 1.4 Organization of the Thesis                                              |

| Chapter 29                                                                  |

| Capacitive Micromechanical Accelerometer Sensor9                            |

| 2.1 Silicon Based MEMS Micromachining Technologies9                         |

| 2.2 Micromechanical Accelerometer Sensors                                   |

| 2.3 Capacitive Micromechanical Accelerometer                                |

| 2.3.1 Surface-Micromachined Capacitive Accelerometer                        |

| 2.3.2 Bulk-Micromachined Capacitive Accelerometer                           |

| 2.4 Single-Beam Cantilever Suspension Structure                             |

| 2.4.1 Sensor Structure and Fabrication Process                              |

| 2.4.2 Sensor Modeling in Verilog-AHDL                                       |

| 2.4.3 Verification of the Sensor Model                                      |

| Chapter 3                                                                   |

| Circuit Techniques for Capacitive Accelerometer Interface                   |

| 3.1 Introduction                                                            |

| 3.2 Review of Capacitive Sensing Interface Circuit Schemes                  |

| 3.2.1 Continuous-Time Chopper Stabilization Sensing Scheme                  |

| 3.2.2 Discrete-Time Switched-Capacitor Correlated Double Sampling Scheme 39 |

| 3.2.3 Switch Errors in SC Design                                            |

| 3.2.4 Comparison of CHS and SC-CDS Schemes                                  |

| 3.3 Review of Switched-Capacitor Interface Circuits                         |

| 3.3.1 Offset-Canceled Cascade Capacitance-to-Voltage Converter (OCC-CVC) 46 |

| 3.3.2 Zoom-In Capacitance-to-Voltage Converter (ZI-CVC)                               | . 54 |

|---------------------------------------------------------------------------------------|------|

| 3.3.3 Single-Ended-to-Fully-Differential Capacitance-to-Voltage Converter (SETFD-CVC) |      |

| 3.4 Summary                                                                           | . 63 |

| Chapter 4                                                                             | . 64 |

| System Architecture and Core Building Blocks                                          | . 64 |

| 4.1 System Architecture                                                               | . 64 |

| 4.2 Auto-Zero Time-Multiplexed Differential Capacitance-to-Voltage Converter          | . 65 |

| 4.2.1 Operation Principle of the Auto-Zero TMD-CVC                                    | . 66 |

| 4.2.2 Low Frequency Error and Finite Gain Error Analysis of AZTMD-CVC                 | .72  |

| 4.2.3 Thermal Noise Analysis & Noise-Power Optimization of the AZTMD-CVC              | .76  |

| 4.2.4 Single Voltage Reference Based AZTMD-CVC and Multiple-Channel Implementation    |      |

| 4.2.5 Comparison of the OCC-CVC, ZI-CVC, SETFD-CVC and AZTMD-CVC                      | . 89 |

| 4.3 Differential-to-Single-Ended Programmable SC Gain Amplifier                       | . 96 |

| 4.4 Low-Offset Low-Noise Output Buffer                                                | . 98 |

| 4.4.1 Low-Offset Design Considerations                                                | . 98 |

| 4.4.2 Circuit Description                                                             | . 99 |

| 4.5 Summary 1                                                                         | 101  |

| Chapter 5 1                                                                           | 103  |

| Peripheral House-Keeping Circuits 1                                                   | 103  |

| 5.1 Introduction1                                                                     | 103  |

| 5.2 Compact CMOS Ring Oscillator with Temperature and Supply Compensation 1           | 104  |

| 5.2.1 Temperature Variation Analysis of the Inverter Based Ring Oscillator            | 105  |

| 5.2.2 Proposed Voltage Source Follower with Temperature Compensation 1                | 109  |

| 5.2.3 Supply Noise Reduction1                                                         | 114  |

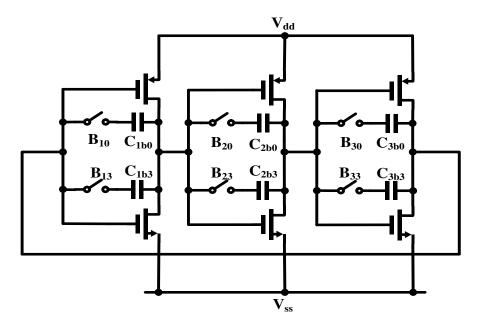

| 5.2.4 Trimming Circuit for Process Variation 1                                        | 115  |

| 5.2.5 Simulation Results and Discussions 1                                            | 116  |

| 5.3 Low-Power Vdd-Tracking Temperature-Compensated Relaxation Oscillator 1            | 123  |

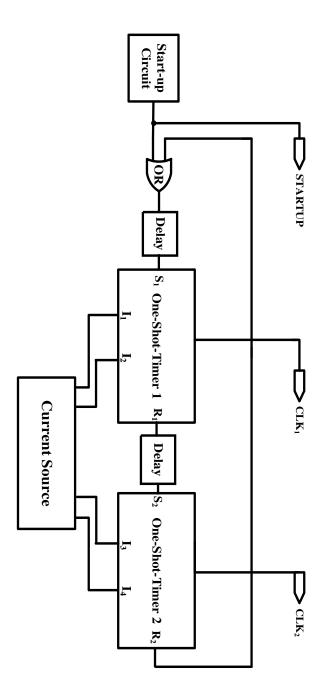

| 5.3.1 Relaxation Oscillator Circuit Architecture1                                     | 124  |

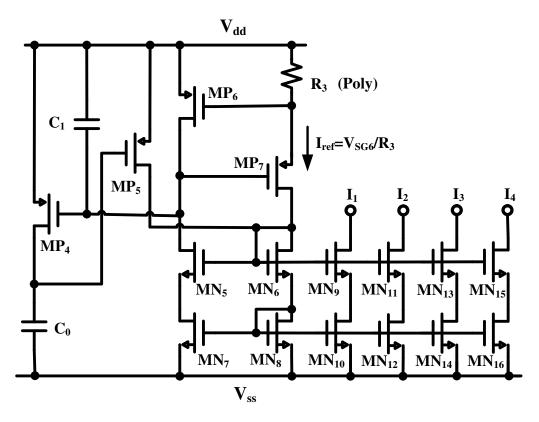

| 5.3.2 Current Source Generator 1                                                      | 126  |

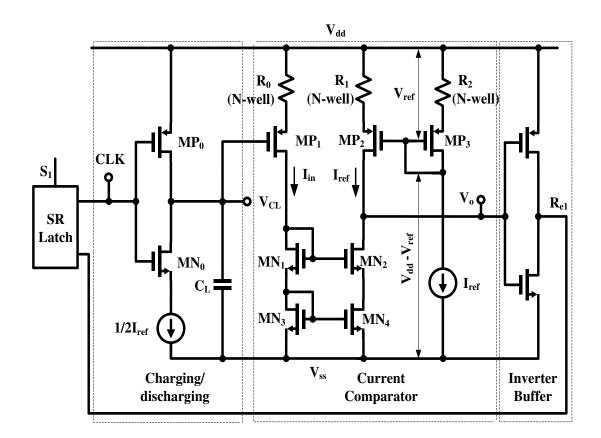

| 5.3.3 V <sub>dd</sub> -Tracking Temperature-Compensated Current Comparator Based One- |      |

| Shot-Timer 1                                                                          |      |

| 5.3.4 Results and Discussions 1                                                       | 134  |

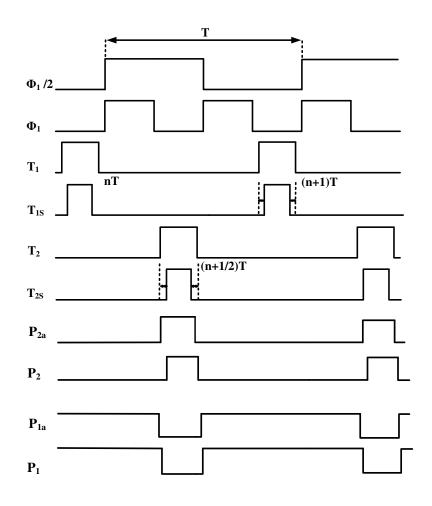

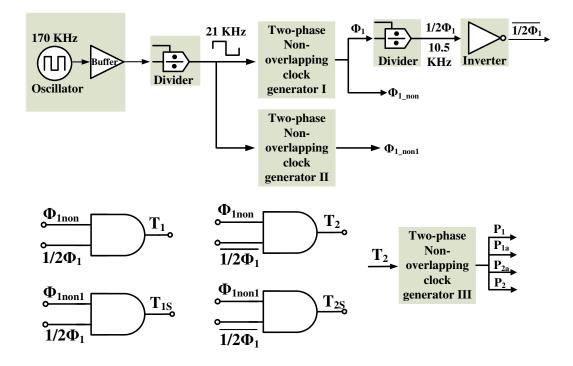

| 5.4 Digital Control Logic for Multi-Phase Clock Generator                                        |  |

|--------------------------------------------------------------------------------------------------|--|

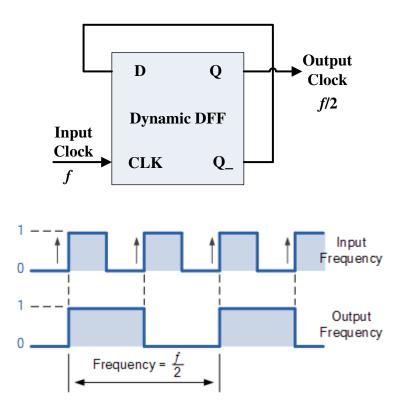

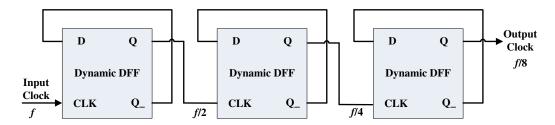

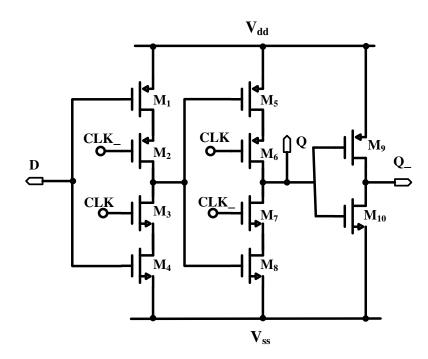

| 5.4.1 Frequency Divider                                                                          |  |

| 5.4.2 Two-Phase Non-Overlapping Clock Generator                                                  |  |

| 5.5 Summary                                                                                      |  |

| Chapter 6                                                                                        |  |

| Mixed-Signal Accelerometer ASIC System Layout Considerations                                     |  |

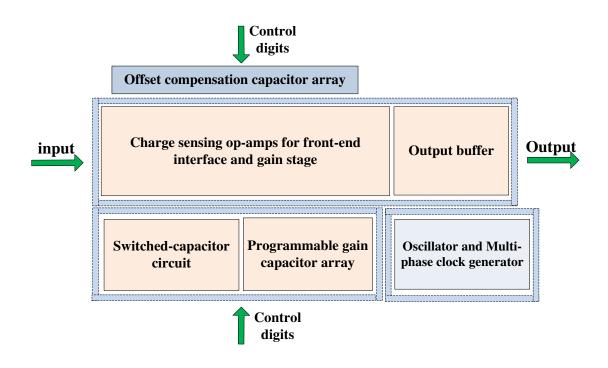

| 6.1 Floor Plan of the Accelerometer ASIC Interface                                               |  |

| 6.2 Low-Noise CMOS IC Layout Techniques                                                          |  |

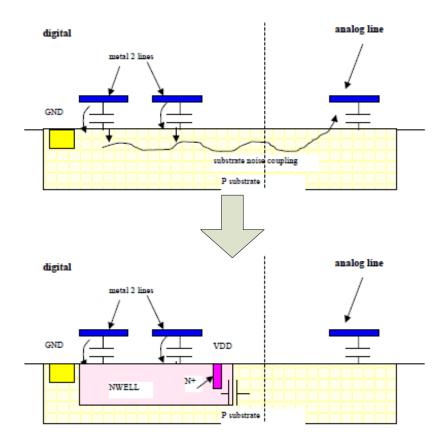

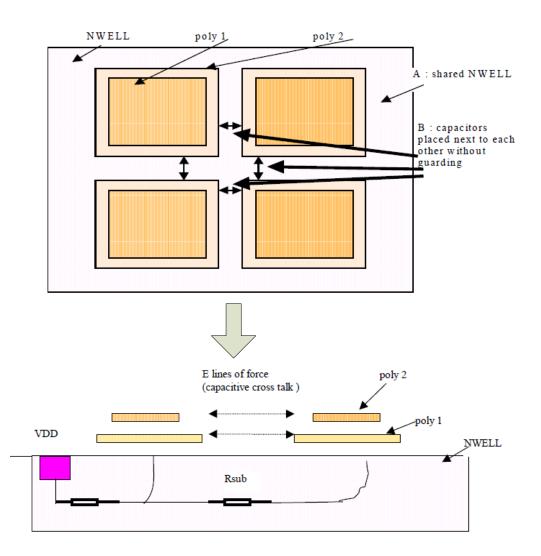

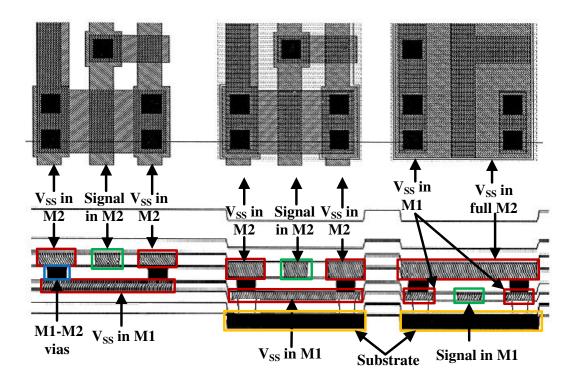

| 6.2.1 Reduction of Digital Signal Coupling Through Substrate                                     |  |

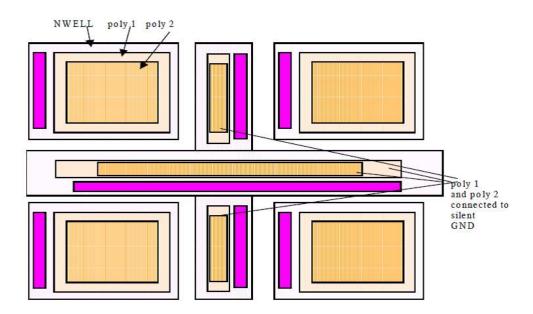

| 6.2.2 Cross-Talk Reduction Between Integration Capacitors                                        |  |

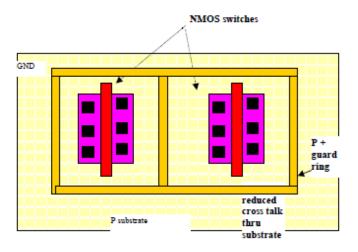

| 6.2.3 Guard Rings for Analog Switches                                                            |  |

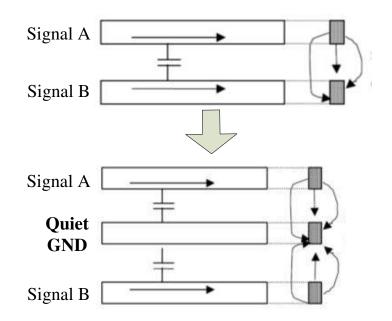

| 6.2.4 Shielding Structure for Critical Analog Paths                                              |  |

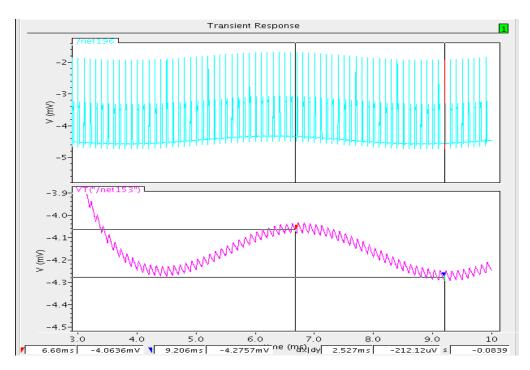

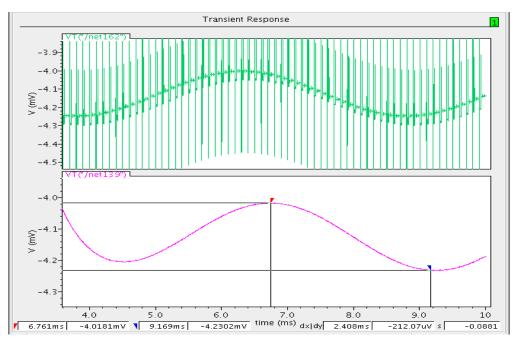

| 6.2.5 Post-Layout System Simulation Results With and Without the C<br>Reduction Layout Technique |  |

| 6.3 Low-Noise PCB Layout                                                                         |  |

| Chapter 7                                                                                        |  |

| Measurement Results & Discussions                                                                |  |

| 7.1 Accelerometer ASIC                                                                           |  |

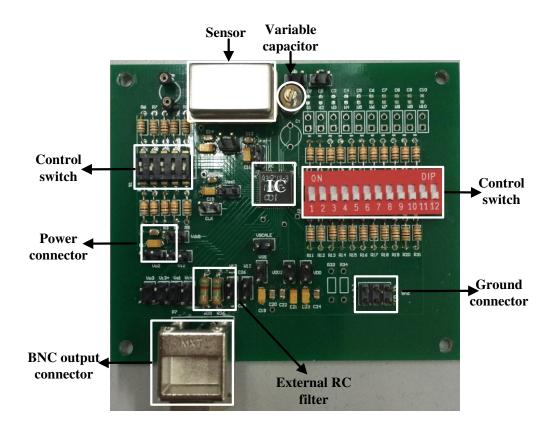

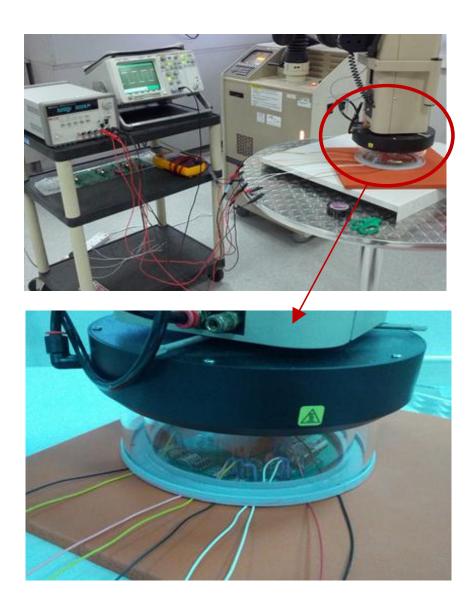

| 7.2 PCB Prototype and Test Setup                                                                 |  |

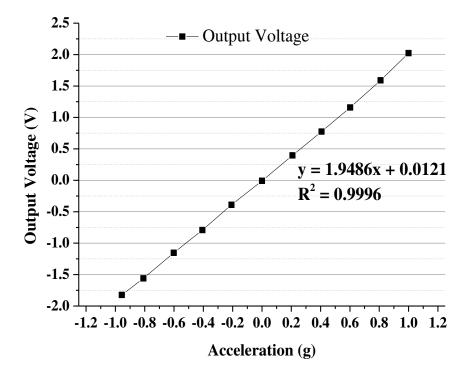

| 7.2.1 System Sensitivity                                                                         |  |

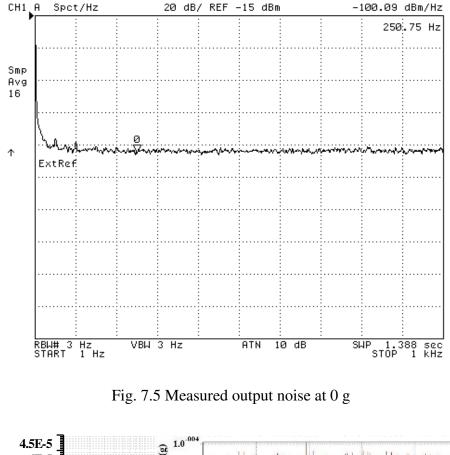

| 7.2.2 Output Noise and In-Run Bias Instability                                                   |  |

| 7.2.3 Performance Comparison with Prior-Art Works                                                |  |

| 7.3 Low-Offset Low-Noise Buffer                                                                  |  |

| 7.4 On-Chip Relaxation Oscillator                                                                |  |

| Chapter 8                                                                                        |  |

| Conclusions and Future Works                                                                     |  |

| 8.1 Conclusions                                                                                  |  |

| 8.2 Future Works                                                                                 |  |

## LIST OF FIGURES

| Fig. 2.1 Lumped element model of accelerometer                                     | 12   |

|------------------------------------------------------------------------------------|------|

| Fig. 2.2 Basic steps of micromachining processes                                   | . 16 |

| Fig. 2.3 Planar view of a lateral accelerometer device and its membrane layout     | 17   |

| Fig. 2.4 Planar view of a typical bulk micromachined vertical accelerometer        | 19   |

| Fig. 2.5 Cross-sectional diagram of the bulk micro-machined accelerometer sensor   | 20   |

| Fig. 2.6 Cross-sectional view (a) and top view (b) of the single beam cantilever   |      |

| structure                                                                          | 21   |

| Fig. 2.7 Gap distance changes with proof mass movement under external acceleration | 24   |

| Fig. 2.8 Behavioral model of a two node capacitor                                  | 27   |

| Fig. 2.9 Equivalent electrical circuit symbol for the accelerometer sensor device  | 27   |

| Fig. 2.10 Sensor model test circuit                                                | 30   |

| Fig. 2.11The output ac currents of the two sensing nodes                           | 32   |

| Fig. 3.1 Chopper-Stabilization amplifier for reduction of noise and offset         | 37   |

| Fig. 3.2 Typical implementation of CHS capacitive sensing scheme[13]               | 37   |

| Fig. 3.3 A fully differential implementation of CHS sensing scheme                 | 39   |

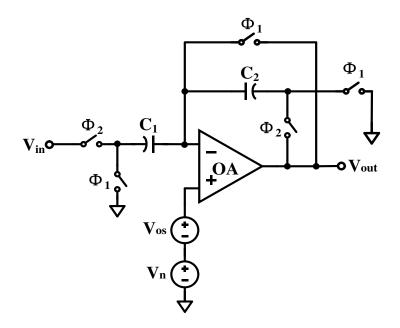

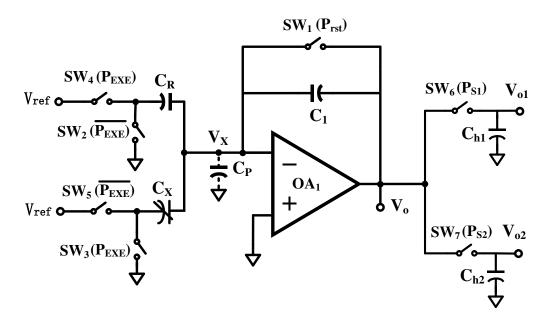

| Fig. 3.4 SC circuit using CDS technique                                            | 40   |

| Fig. 3.5 Configuration of SC-CDS Circuit in Reset mode                             | 41   |

| Fig. 3.6 Configuration of SC-CDS Circuit in Charge transfer mode                   | 42   |

| Fig. 3.7 Charge injection mechanism when the NMOS switch is turned off             | 43   |

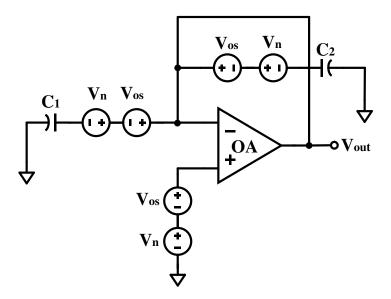

| Fig. 3.8 Offset-canceled cascade capacitance-to-voltage converter (OCC-CVC) [39]   | 47   |

| Fig. 3.9 Control clock waveforms for OCC-CVC [39]                                  | 48   |

| Fig. 3.10 OCC-CVC with offset and flicker noise error sources [39]                 | 49   |

| Fig. 3.11 OCC-CVC with parasitic capacitance at the middle sensing node            | 53   |

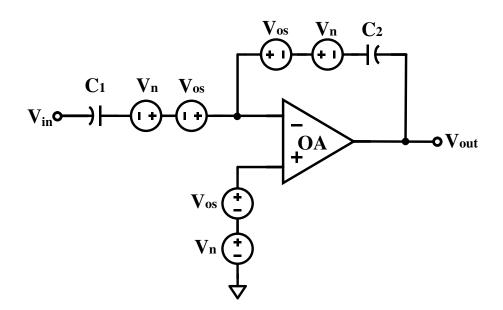

| Fig. 3.12 Zoom-in capacitance-to-voltage converter (ZI-CVC) [40]                   | 55   |

| Fig. 3.13 Control clock waveforms for ZI-CVC                                       | 55   |

| Fig. 3.14 ZI-CVC with offset and flicker noise error sources [40]                  | 56   |

| Fig. 3.15 ZI-CVC with parasitic capacitance at the middle sensing node             | 58   |

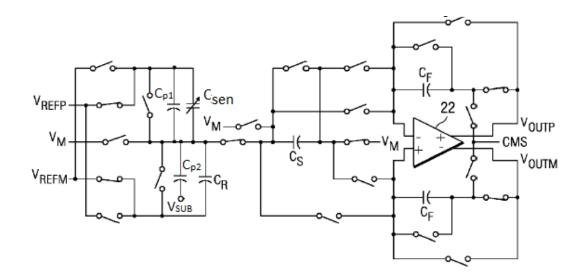

| Fig. 3.16 Single-ended-to-fully-differential capacitance-to-voltage converter      | 62   |

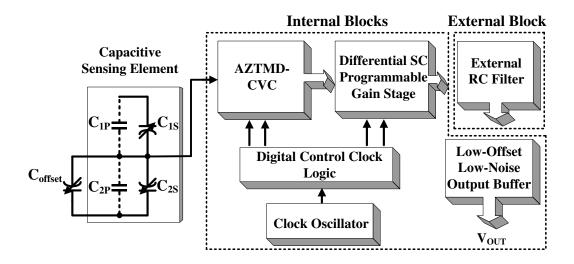

| Fig. 4.1 Simplified block diagram of the capacitive accelerometer IC               | 65   |

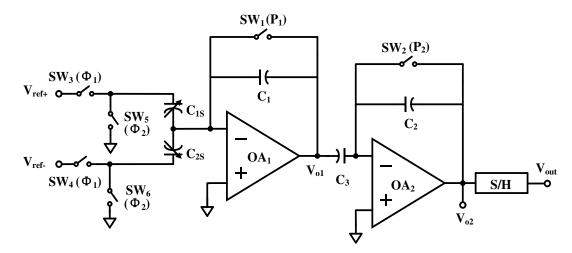

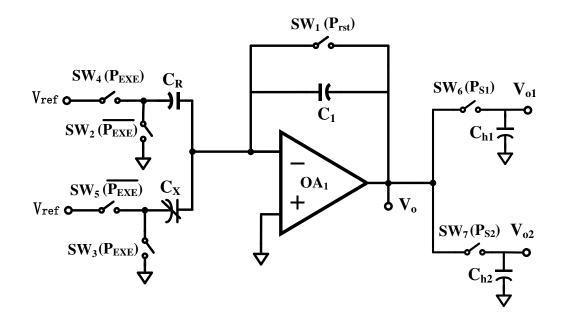

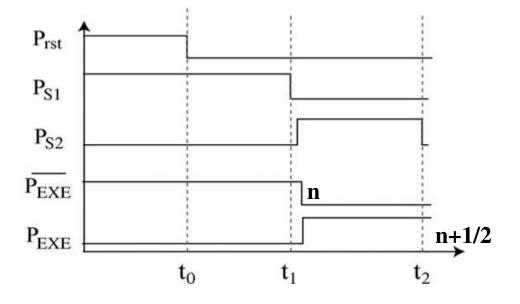

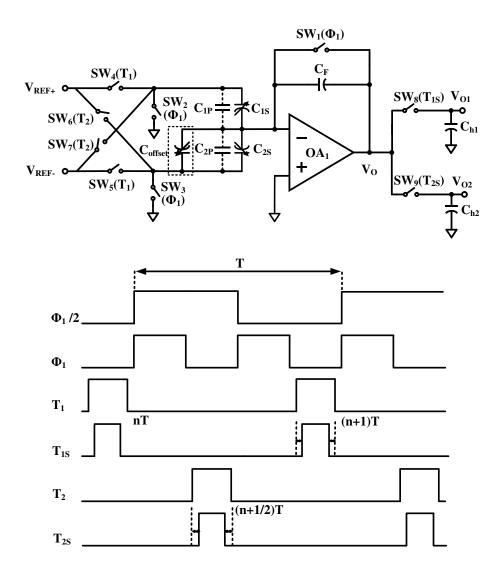

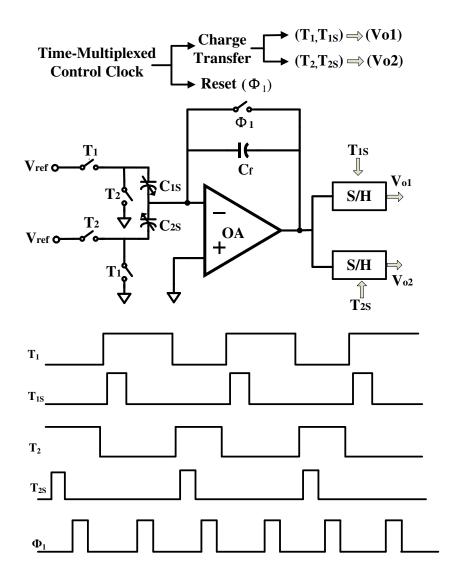

| Fig. 4.2 Schematic diagram of the AZTMD-CVC with its control clocks                | 67   |

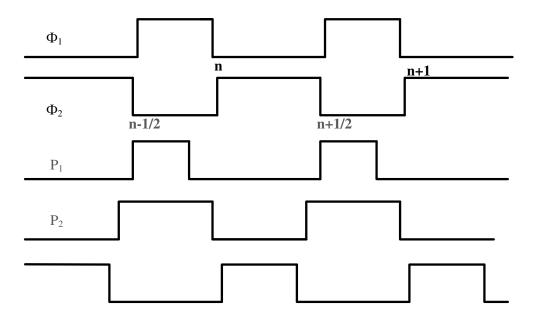

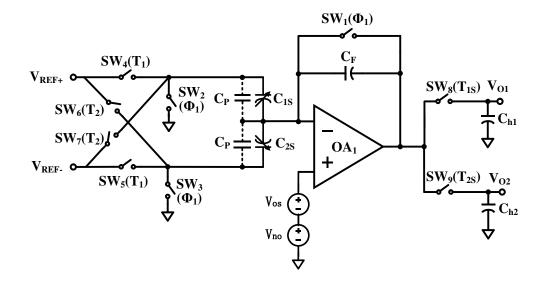

| Fig. 4.3 TMD-CVC with offset and flicker noise error sources                       | 72   |

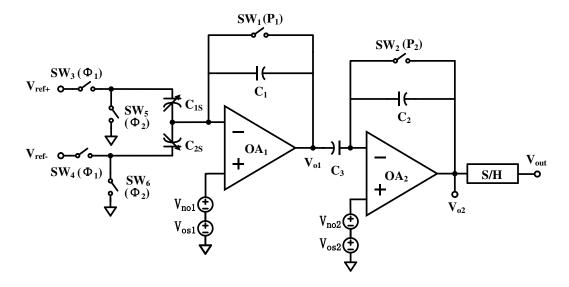

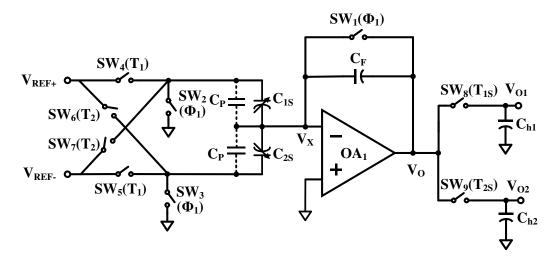

| Fig. 4.4 AZTMD-CVC for finite gain error analysis                                  | 75   |

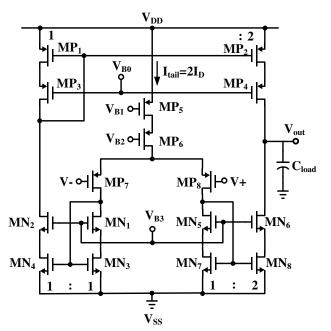

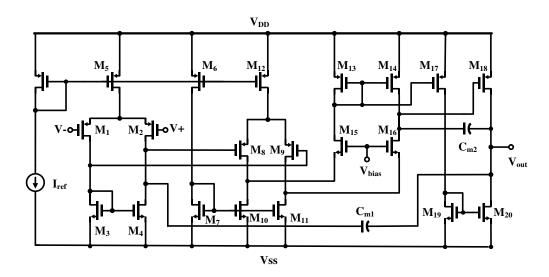

| Fig. 4.5 Schematic of the push-pull current mirror core OTA                        | 78   |

|                                                                                    |      |

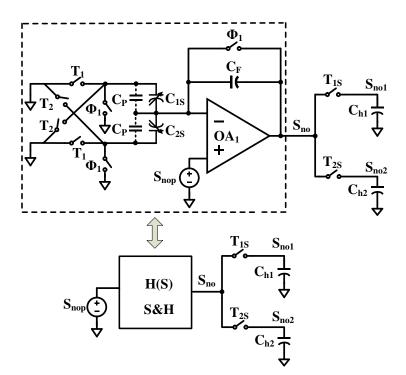

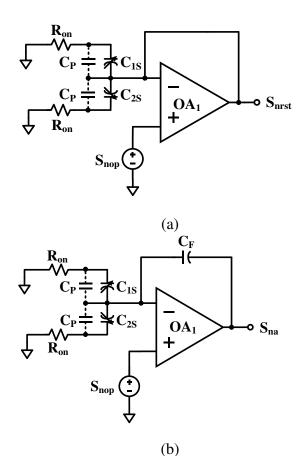

| Fig. 4.6 Noise signal processing in the TMD-CVC interface                                    | . 79 |

|----------------------------------------------------------------------------------------------|------|

| Fig. 4.7 Equivalent circuit configuration for noise calculation during (a) reset phase       |      |

| and (b) charge transfer phase                                                                | . 80 |

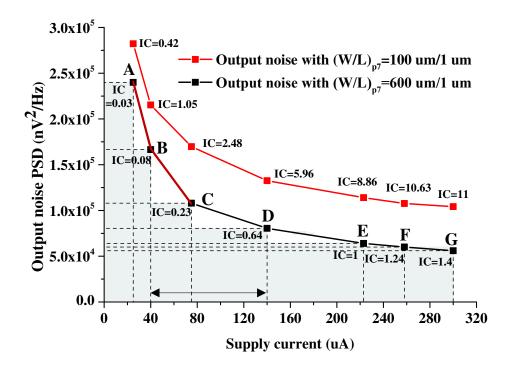

| Fig. 4.8 AZTMD-CVC output noise PSD under different supply currents                          | . 83 |

| Fig. 4.9 Single voltage reference based AZTMD-CVC and its control clocks                     | . 86 |

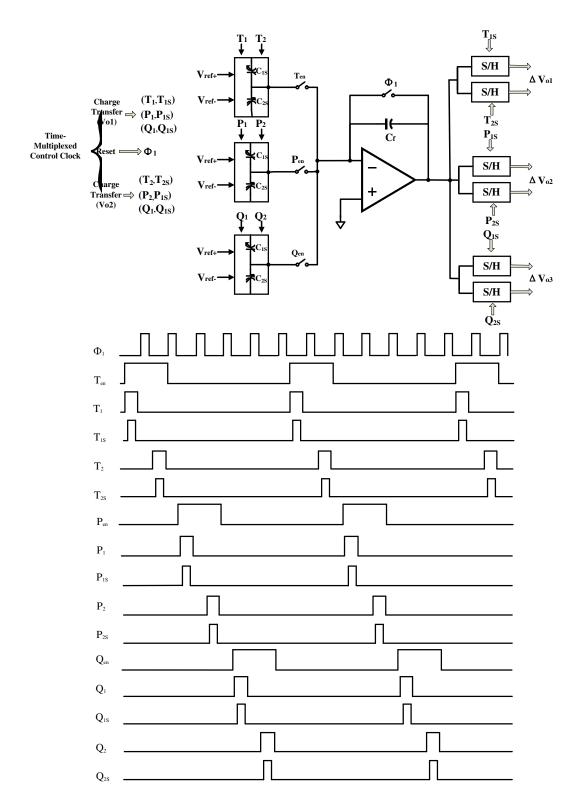

| Fig. 4.10 Multi-channel AZTMD-CVC and its control clocks based on Fig. 2                     | . 87 |

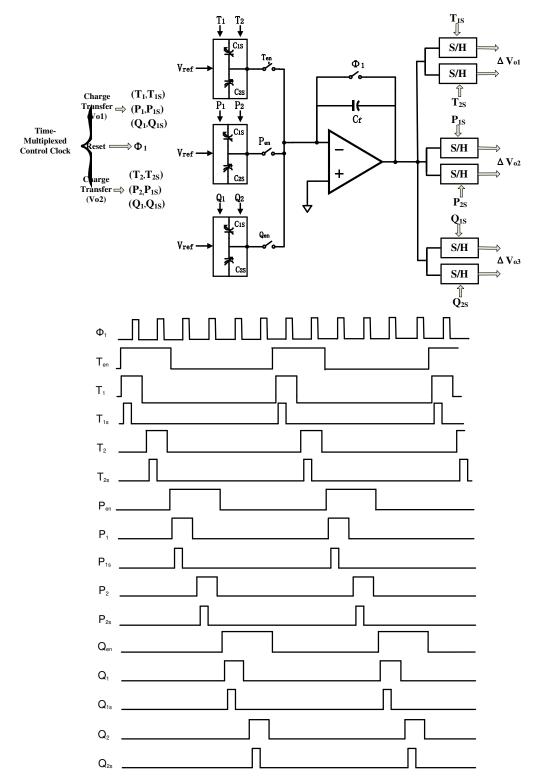

| Fig. 4.11 Multi-channel single reference voltage based AZTMD-CVC and its control             |      |

| clocks                                                                                       | . 88 |

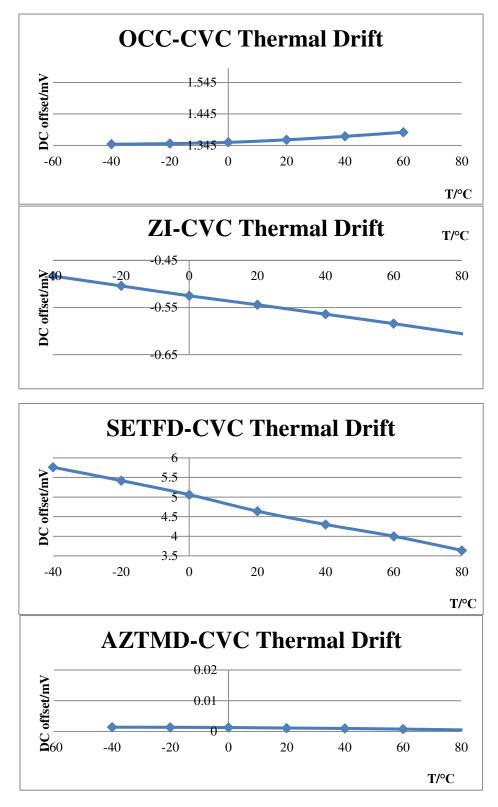

| Fig. 4.12 Simulated thermal drift of the DC offset for the four CVC circuits                 | . 92 |

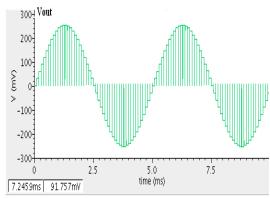

| Fig. 4.13 Output waveform Vout of OCC-CVC after S&H                                          | . 93 |

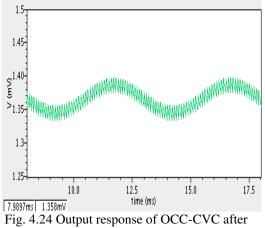

| Fig. 4.14 Output response of OCC-CVC after an ideal 330HZ filter                             | . 93 |

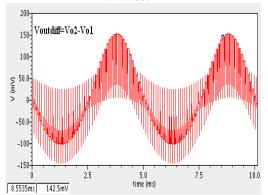

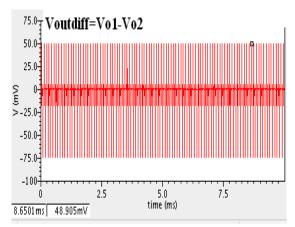

| Fig. 4.15 Differential output waveform Voutdiff of ZI-CVC after S&H                          | . 93 |

| Fig. 4.16 Output response of ZI-CVC after an ideal 330Hz filter                              | . 93 |

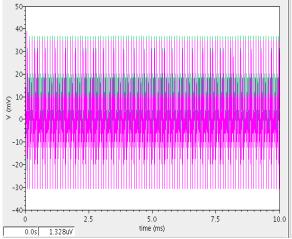

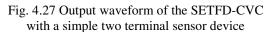

| Fig. 4.17 Output waveform of the SETFD-CVC with a simple two terminal sensor                 |      |

| device                                                                                       | . 93 |

| Fig. 4.18 Differential output waveform of the SETFD-CVC with a simple two terminal           |      |

| sensor device                                                                                | . 93 |

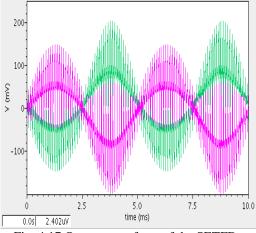

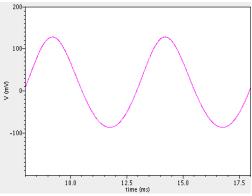

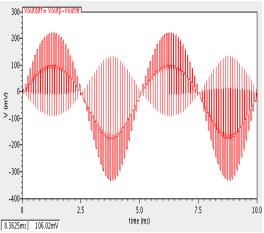

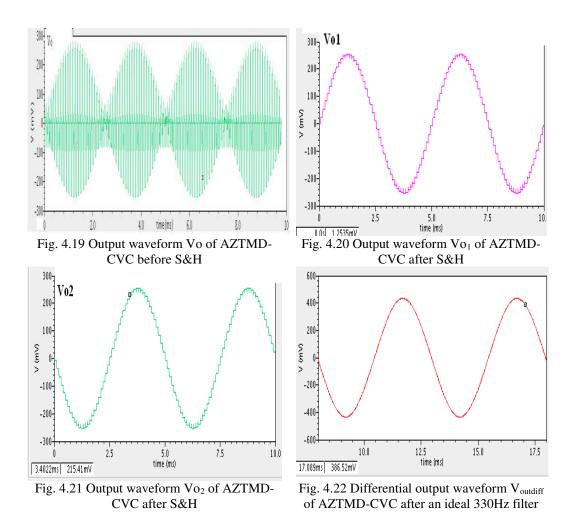

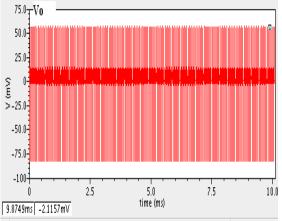

| Fig. 4.19 Output waveform Vo of TMD-CVC before S&H                                           | . 94 |

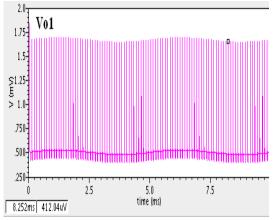

| Fig. 4.20 Output waveform Vo1 of TMD-CVC after S&H                                           | . 94 |

| Fig. 4.21 Output waveform Vo2 of TMD-CVC after S&H                                           | . 94 |

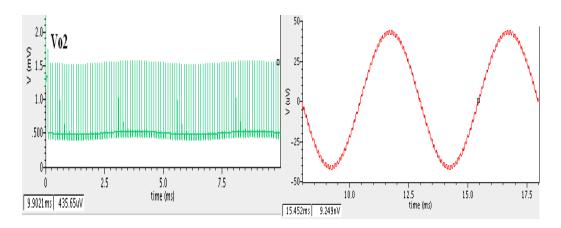

| Fig. 4.22 Differential output waveform $V_{outdiff}$ of TMD-CVC after an ideal 330Hz filter. | . 94 |

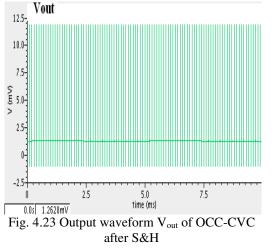

| Fig. 4.23 Output waveform Vout of OCC-CVC after S&H                                          | . 94 |

| Fig. 4.24 Output response of OCC-CVC after an ideal 330HZ filter                             | . 94 |

| Fig. 4.25 Differential output waveform V <sub>outdiff</sub> of ZI-CVC after S&H              | . 95 |

| Fig. 4.26 Output response of ZI-CVC after an ideal 330Hz filter                              | . 95 |

| Fig. 4.27 Output waveform of the SETFD-CVC with a simple two terminal sensor                 |      |

| device                                                                                       | . 95 |

| Fig. 4.28 Differential output waveform of SETFD-CVC with a simple two terminal               |      |

| sensor device                                                                                | . 95 |

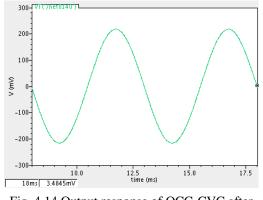

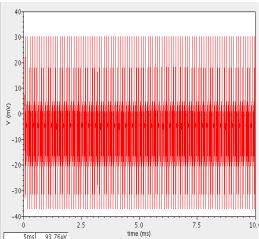

| Fig. 4.29 Output waveform Vo of AZTMD-CVC before S&H                                         | . 95 |

| Fig. 4.30 Output waveform Vo1 of AZTMD-CVC after S&H                                         | . 95 |

| Fig. 4.31 Output waveform Vo2 of AZTMD-CVC after S&H                                         | .96  |

| Fig. 4.32 Differential output waveform Voutdiff of AZTMD-CVC after an ideal 330Hz            |      |

| filter                                                                                       | . 96 |

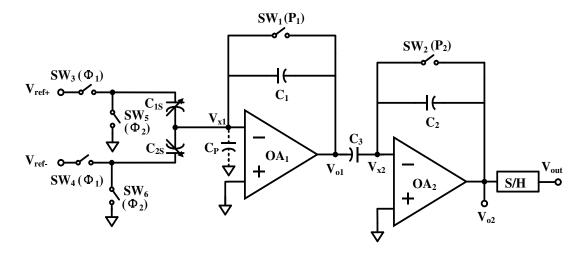

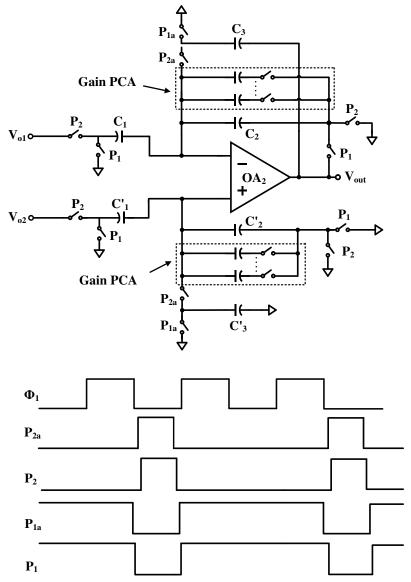

| Fig. 4.33 Schematic of the differential-to-single-ended programmable SC-CDS gain                                      |

|-----------------------------------------------------------------------------------------------------------------------|

| stage with its control clocks with respect to reset clock $\Phi_1$                                                    |

| Fig. 4.34 Low-offset low-noise output buffer                                                                          |

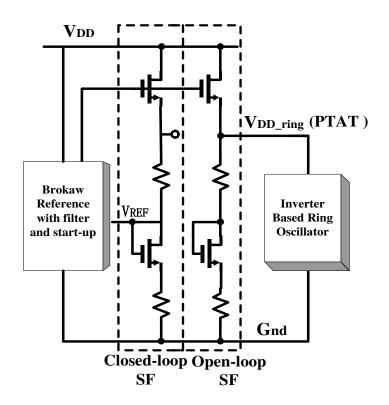

| Fig. 5.1 Conceptual diagram of the proposed circuit 105                                                               |

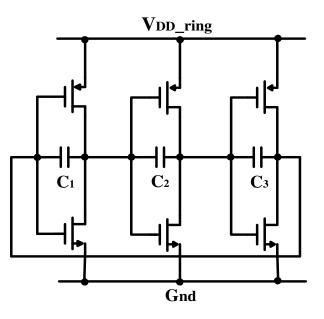

| Fig. 5.2 Schematic of the three-stage inverter with Miller capacitors 106                                             |

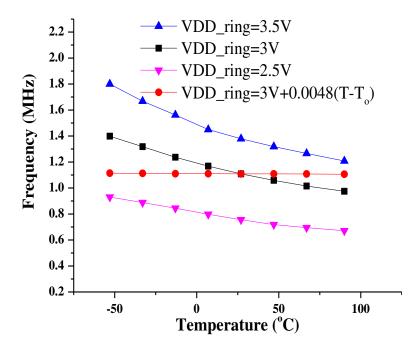

| Fig. 5.3 Frequency dependence on temperature with different supply voltages 109                                       |

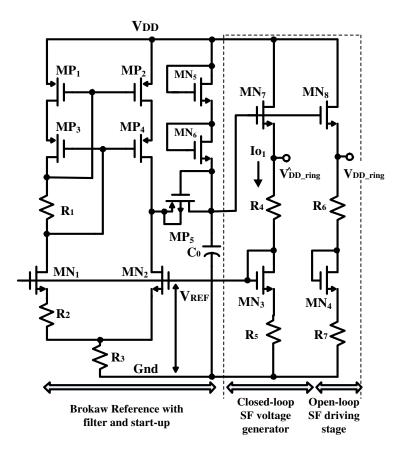

| Fig. 5.4 The proposed temperature compensation voltage source circuit                                                 |

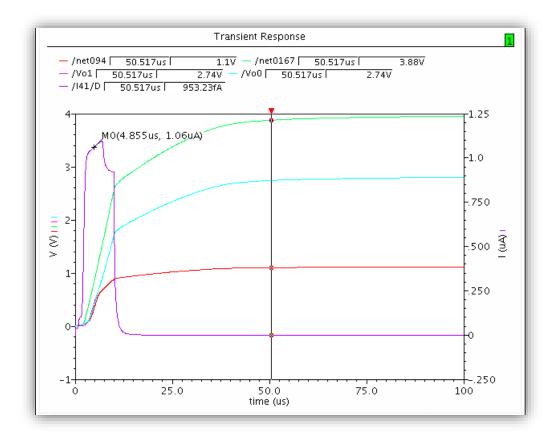

| Fig. 5.5 Start-up response                                                                                            |

| Fig. 5.6 Ring oscillator with data bits controlled Miller capacitor array 115                                         |

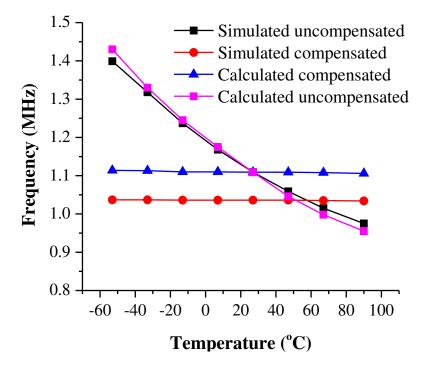

| Fig. 5.7 Simulation and calculation results of the temperature characteristic of the                                  |

| oscillation frequency with and without compensation117                                                                |

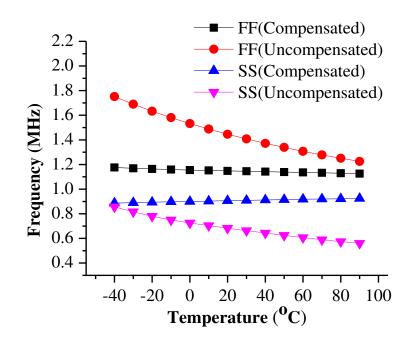

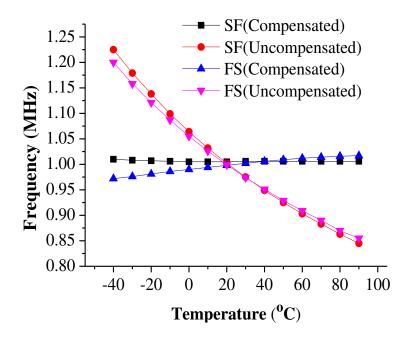

| Fig. 5.8 Simulation results for frequency versus temperature variation under (a) FF, SS                               |

| corners and (b) SF, FS corners                                                                                        |

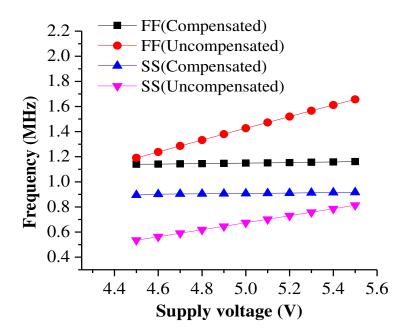

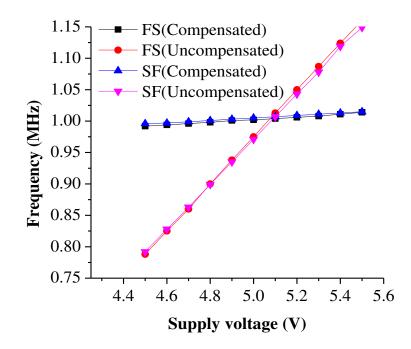

| Fig. 5.9 Simulation results for frequency versus $\pm 10\%$ supply variation under (a) FF                             |

| and SS corners and (b) SF and FS corners119                                                                           |

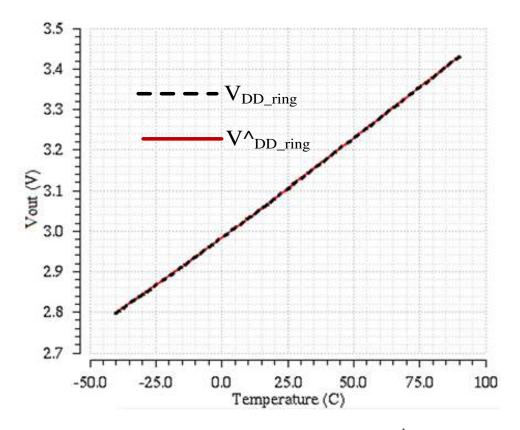

| Fig. 5.10 Temperature sweep of the generated $V_{\text{DD}}\textsc{ring}$ and $V^{}\textsc{DD}\textsc{ring}$ under 1% |

| mismatch in the source follower pair                                                                                  |

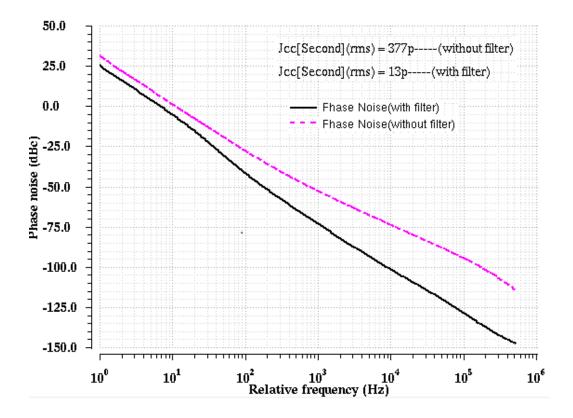

| Fig. 5.11 Simulated phase noise due to intrinsic circuit noise with and without filter 120                            |

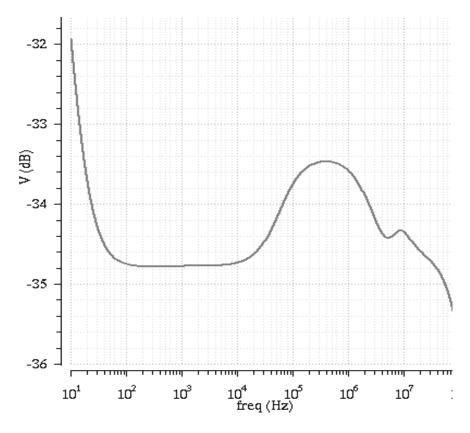

| Fig. 5.12 Simulated PSRR response of the proposed temperature compensated SF 121                                      |

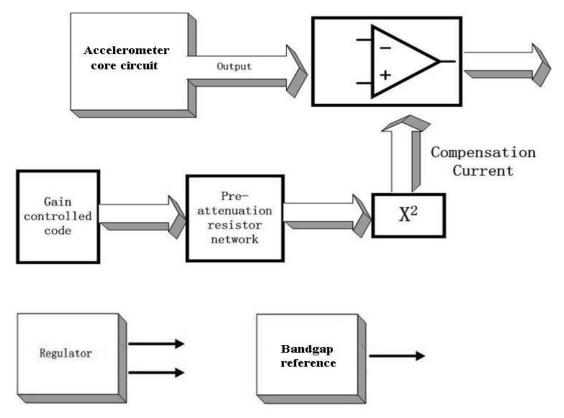

| Fig. 5.13 Block diagram of the oscillator circuit                                                                     |

| Fig. 5.14 Schematic of the current source generator (startup not shown)128                                            |

| Fig. 5.15 One-shot-timer circuit based on $V_{dd}$ -tracking temperature-compensated                                  |

| current comparator                                                                                                    |

| Fig. 5.16 Control clock signals for the SC readout out circuit                                                        |

| Fig. 5.17 The digital control logics for multi-phase clock generator                                                  |

| Fig. 5.18 Dynamic DFF configured as a divide-by-2 counter                                                             |

| Fig. 5.19 Divide-by-8 counter                                                                                         |

| Fig. 5.20 Schematic of the dynamic DFF                                                                                |

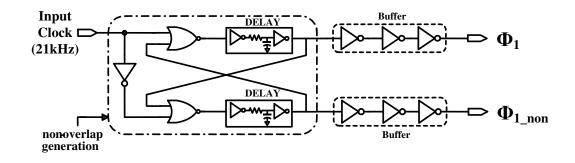

| Fig. 5.21 Non-overlapping clock generator                                                                             |

| Fig. 6.1 Floor plan of sensing interface system layout                                                                |

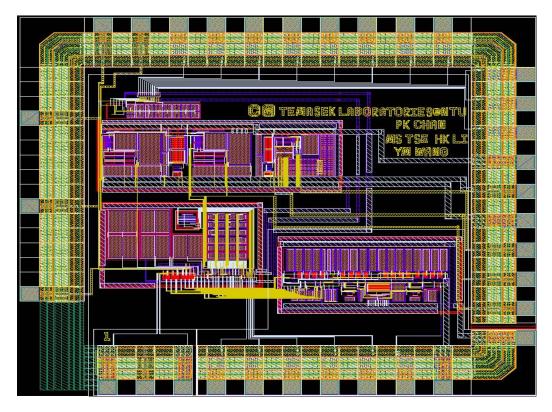

| Fig. 6.2 System layout in AMS 0.35um CMOS technology146                                                               |

| Fig. 6.3 Digital signal coupling mechanism through substrate and its reduction                                        |

| Fig. 6.4 Various cross-talk mechanisms in the layout of integration capacitors (a)                                    |

| between capacitors carrying different signals, (b) substrate resistive coupling 147                                   |

| Fig. 6.5 Capacitor layout with shielding dummy capacitors                                                             |

| Fig. 6.6 Analog switches with individual guard rings                                      |

|-------------------------------------------------------------------------------------------|

| Fig. 6.7 Shielding the critical analog signal lines with a quiet signal line              |

| Fig. 6.8 Shielding examples in two metal process [83]149                                  |

| Fig. 6.9 Post-layout system simulation result under 0.1mg without cross-talk reduction    |

| technique                                                                                 |

| Fig. 6.10 Post-layout system simulation result under 0.1mg with cross-talk reduction      |

| technique                                                                                 |

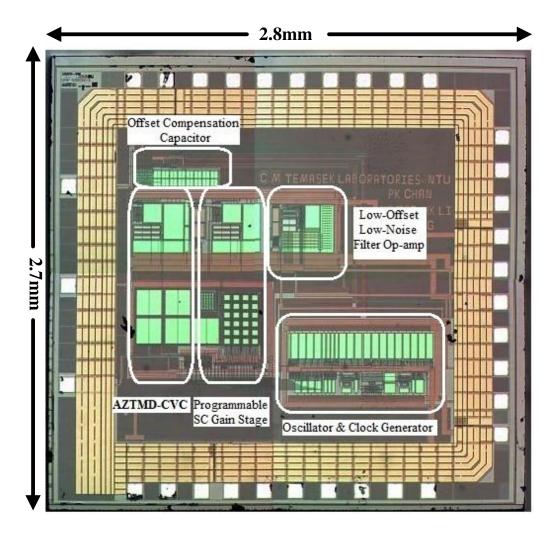

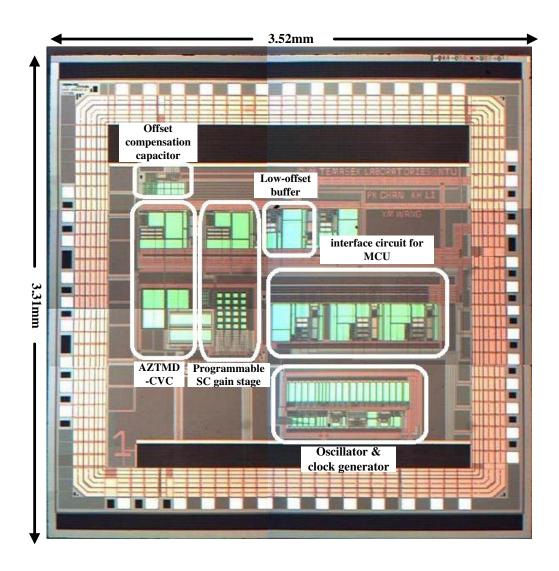

| Fig. 7.1 Microphotograph of the first-version accelerometer ASIC                          |

| Fig. 7.2 Microphotograph of the second-version accelerometer ASIC with added              |

| interface for MCU                                                                         |

| Fig. 7.3 PCB prototype for test                                                           |

| Fig. 7.4 Output voltage of the micro-accelerometer system against acceleration            |

| Fig. 7.5 Measured output noise at 0 g                                                     |

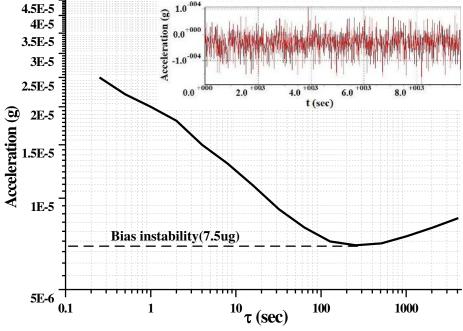

| Fig. 7.6 Measured in-run bias instability                                                 |

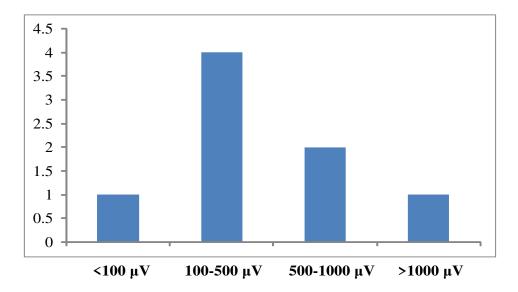

| Fig. 7.7 Offset distribution of the low-offset buffer                                     |

| Fig. 7.8 Experimental setup for temperature performance testing of on-chip oscillator 163 |

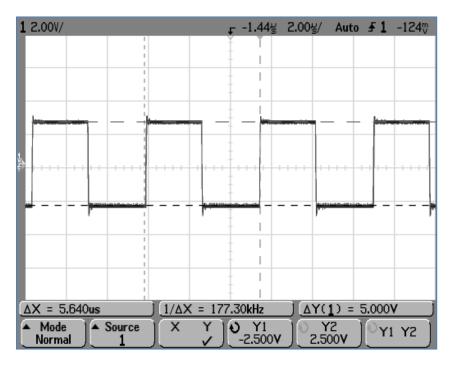

| Fig. 7.9 Measured clock signal in one sample                                              |

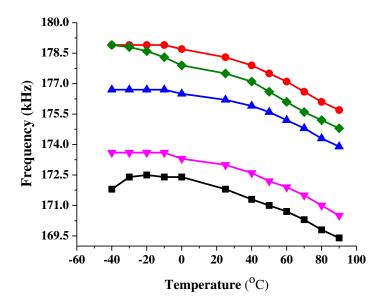

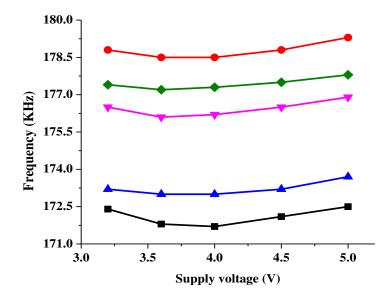

| Fig. 7.10 Measured 5 samples' clock frequency against (a) temperature variation and       |

| (b) supply variation                                                                      |

| Fig. 8.1 Circuit blocks for future highly-linear accelerometer IC with wide g range 171   |

## LIST OF TABLES

| Table 2.1 Specifications of accelerometers for different applications          | 14     |

|--------------------------------------------------------------------------------|--------|

| Table 2.2 Specifications of Accelerometer IC                                   |        |

| Table 2.3 Percentage errors of the capacitance between the first-order model a | nd the |

| ideal case at different acceleration levels                                    |        |

| Table 4.1 Comparison of simulated circuit performance for the four CVCs        |        |

| Table 5.1 Jitter performance comparison with benchmarks                        |        |

| Table 5.2 Performance comparison with prior-art works                          |        |

| Table 5.3 Simulation results of frequency stability                            |        |

| Table 7.1 Equipment and instruments used in the test                           |        |

| Table 7.2 Performance comparison of the proposed accelerometer IC with re      | ported |

| works                                                                          |        |

| Table 7.3 Measured results of the low-offset low-noise amplifier               |        |

| Table 7.4 Performance comparison of the proposed relaxation oscillator with re | ported |

| works                                                                          |        |

#### Abstract

The objective of this project is to design a low-power, low-noise, highlysensitive accelerometer ASIC interface using standard CMOS technology. The capacitive acceleration sensor is based on Micro-Electro-Mechanical Systems (MEMS) technology. For the targeted security applications, the bulkmicromachined accelerometer which has been developed by Temasek Laboratory@NTU, is employed as the sensing element to couple with the abovementioned ASIC readout circuit.

The auto-zero time-multiplexed differential technique is able to tolerate a number of circuit non-idealities. These include operational amplifier (op-amp) offset, offset thermal drift and switch errors of switched-capacitor (SC) circuits. The unique single-ended circuit architecture avoids the stringent requirement for component matching and eliminates the common-mode problem in conventional fully differential interface circuitry. Ultimately, it improves S/N ratio and cancels the common-mode errors in the sensing system with low power consumption.

For the implementation of the ASIC design to the intended accelerometer application, it involves several circuit building blocks. They are readout circuit, oscillator, differential-to-single-ended SC gain amplifier stage, passive RC filter and low-offset low-noise op-amp buffer.

A novel Auto-Zero Time-multiplexed Capacitance-to-Voltage Converter (AZTMD-CVC) is proposed for the readout circuit in this project. The circuit architecture achieves differential output performance whilst using only singleended CVC topology. This approach eliminates the use of bulky full Wheatstone bridge sensing element in the MEMS sensor as required in conventional fully differential sensor interface architecture, with additional benefit in reducing the fabrication cost of the MEMS sensor and readout circuit, as well as the power consumption. Besides, a low-power design strategy, pertaining to power versus noise in the readout circuit, is proposed. It permits the design to attain low noise without using excessive power consumption. This offers the optimal power-noise product in a form of figure-of-merit (FOM) on the AZTMD-CVC.

Two new oscillator circuits have been presented in this work. Both the oscillator designs offer clock signals with good temperature and supply variation immunity. The first oscillator design is a compact low-power CMOS ring oscillator with temperature and supply compensation whereas the second oscillator design deals with the relaxation oscillator using the tracking current comparator. The second design is adopted in this AZTMD-CVC circuit together with the silicon implementation for prototype testing. The key feature of the second oscillator is that of the temperature compensation without resorting to any external resistor component. The tracking current comparator based oscillator provides a 172 kHz clock for the interface circuit. This clock signal displays a 0.17% variation within the supply range from  $\pm 1.6$ V to  $\pm 2$ V whereas the mean temperature compensated coefficient for 5 samples of this oscillator frequency is around 0.018%/°C with a temperature range of -40 to 90°C. The power consumption of this oscillator circuit is only 4.2uA (21uW), demonstrating low-power consumption feature.

The accelerometer ASIC has been designed and implemented using the AMS  $0.35\mu m$  CMOS 3.3/5V process technology. This accelerometer interface IC features both the offset and gain trimming which enable the IC to operate correctly even under the process variation of the fabricated MEMS capacitance

sensor. The prototype testing results have shown that the accelerometer readout system achieves a sensitivity of 1.95V/g. The system achieves a low noise level of -100 dBm/Hz, which corresponds to an equivalent acceleration noise of 1.16  $\mu g/\sqrt{Hz}$ . The total power consumption including the clock generator is only 1.2 mW with  $\pm 2.5V$  dual supplies. The measured in-run bias stability under 0g acceleration is 7.5  $\mu g$  over around 3 hours' time. This is comparable with other reported highly-sensitive accelerometers. This measurement results have validated that the proposed design can meet low-power low-noise objectives with very high sensitivity. It outperforms the reported state-of-art works in performance comparison.

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 Background and Motivations**

Micro-Electro Mechanical System (MEMS) is an enabling technology that can integrate both mechanical components and small electrical/electronic devices onto the same silicon substrate using semiconductor wafer fabrication technology. After several decades' research and development effort, more and more miniaturized MEMS devices nowadays permits the realization at a lower cost, lower power consumption, much smaller package size and better stability. Micro-sensors and Micro-actuators, which are well-known in the transducers, are the most notable and well-developed elements among such a variety of MEMS functional products. In miniaturized micro-sensor system, the micromechanical device fabricated using micromachining process can sense physical signals like temperature, pressure, inertial forces, chemical species, magnetic fields, radiation and so forth. At the same time, the electronic circuits fabricated using CMOS process technologies provide the readout function for interface circuit designs and the control function for mechanical components. These micro-system devices have demonstrated in a wide range of commercial markets at a rapid rate due to their exceptional performance at low cost.

MEMS accelerometer is a kind of micro-sensor system that can sense the system acceleration onto which the sensing element is attached and convert the physical parameter to an electrical signal. Accelerometers can be integrated together with gyroscopes for angular rotation measurement. This is called the inertial measurement unit (IMU) for the measurement of linear and angular acceleration, velocity and displacement. Accelerometers can also be used for vibration and shock measurement as well as the tilt and inclination measurements. They have been widely used in consumer electronics, automobile, industrial electronics as well as navigation and portable devices. An exemplary application is the area of automobiles in which accelerometers are used for crash detection to activate the deployment of airbags, active suspension and adaptive brake and anti-skiing application. Turning to industrial applications, accelerometers are employed in machine condition monitoring, such as the vibration monitoring for the prediction of operation condition of moving machine that helps to improve the machine stability and safety. Besides, the tilt and inclination measurements can be applied in robotics and instrumentation area. With the fast development of the micromachining process technologies, the cost of accelerometer goes down rapidly in view of the push from the market demand.

Through the research and development efforts over the past decades, a lot of sensing mechanisms have been developed and realized in MEMS based accelerometer devices. These mechanisms include the piezoresistive, capacitive, piezoelectric, electromagnetic, tunneling and so on. Among the choices of these various sensing techniques, the capacitive micro-accelerometers have the advantages of high sensitivity, low drift, low temperature dependence, low power consumption and good compatibility with IC process technology. These strengths ensure a big market for capacitive accelerometers. For precision applications like inertial grade navigation system, platform stabilization, low cost inertial measurement units (IMUs) as well as microgravity measurement systems [1], they push for the demand of  $\mu g$  level based micro-accelerometers.

incorporated with a large number of sensing interfaces, hence the power-aware concern becomes one of the design priorities.

Of the two main micromachining processes for MEMS accelerometers, the bulk micro-machined accelerometers [2]-[4] have higher sensitivity as well as lower mechanical thermal noise performance than that of the surface micro-machined counterpart [5]-[8] due to the inherent large seismic or proof mass in bulk micro-machined devices. The sensor device developed in this work is a bulk micro-machined capacitive sensing element which is based on a cantilever suspension structure. The out-of-plane sensing scheme results in a much higher capacitive sensing devices will be unavoidable. They contribute to the noise issue in a form of high noise gain factor associated with the interface electronics. To circumvent the drawbacks, low-power low-noise circuit architecture, low-noise amplifier design and noise-power optimization become the design agenda.

Continuous-time chopper stabilization (CHS) [9], discrete-time switchedcapacitor auto-zero (SC-AZ) and switched-capacitor correlated double sampling (SC-CDS) [10], [11] are well-known circuit design techniques suitable for capacitive sensing applications. CHS, SC-AZ and SC-CDS techniques can all effectively reduce the dc offset as well as the low frequency 1/f noise associated with the MOS devices in CMOS circuits. CHS has the advantage of a lower baseband noise level since it is not affected by the thermal noise folding effect which is always associated with SC sampling based circuits. Despite of the merit, the technique suffers from the residual offset [12] usually caused by the clock feed-through and charge injection in a form of spikes. For the application in MEMS sensors with large sensing and parasitic capacitances in form of large time constant formed together with the MOS switches, it tends to have a larger mismatch effect. This gives rise to unavoidable big AC spikes to the sensitive input of chopper amplifier whilst displaying potential large dc offset as well as chopper ripple in the demodulation process that may deteriorate the CHS technical merit. Therefore, it is common to see that the CHS sensing interfaces [13]-[16], are mainly applied in small sensing elements using surface micro-machined mechanical sensors.

For an electronic interface dedicated to couple with a bulk micro-machined MEMS device involving large capacitances as well as large charging/discharging time constants, the SC sensing method is preferred because of its nature supporting fast charging/discharging on capacitances without significantly jeopardizing the front-end interface performance.

#### **1.2 Objectives**

The objectives of this work are to research, design and realization a highlysensitive accelerometer ASIC dedicated to the security sensing system which is able to tolerate large parasitic capacitances from the sensing element whist addressing low noise performance metric in along with power-aware implementation. The scope of the research project is listed as follows:

- To review and investigate of two main capacitive interface circuit techniques applicable for highly-sensitive accelerometers which are based on continuous-time chopper stabilization and discrete-time switched-capacitor approach.

- To study the representative switched-capacitor interface circuits and identify the imperfections associated with the circuits together with their detailed analyses.

- 3. To investigate, design and analyze a new switched-capacitor front-end readout circuit that can be interfaced with a large parasitic based capacitive sensor whilst sustaining good performance metrics.

- 4. To design and realize the back-end electronic circuits that form the accelerometer ASIC with the proposed readout circuit.

- To conduct the prototype testing of the accelerometer ASIC interfaced with the sensing element developed by Temasek Laboratory@NTU

#### **1.3 Major Contributions of the Thesis**

The major contributions of the research work are summarized as follows:

- 1. A novel Auto-Zero Time-multiplexed Capacitance-to-Voltage Converter (AZTMD-CVC) is proposed for the readout circuit in this project. The circuit architecture achieves differential output performance whilst using only single-ended CVC topology. This approach eliminates the use of bulky full Wheatstone bridge sensing element in the MEMS sensor as required in conventional fully differential sensor interface architecture, with additional benefit in reducing the fabrication cost of the MEMS sensor and readout circuit, as well as the power consumption.

- A low-power design strategy, pertaining to power versus noise in the readout circuit, is proposed. It permits the design to attain low noise without using excessive power consumption. This offers the optimal power-noise product in a form of figure-of-merit (FOM) on the AZTMD-CVC.

- 3. Two new oscillator circuits have been presented in this work. Both the oscillator designs offer clock signals with good temperature and supply variation immunity. The first oscillator design is a compact low-power CMOS ring oscillator with temperature and supply compensation whereas the second oscillator design deals with the relaxation oscillator using the tracking current comparator. The second design, which offers significantly low power consumption, is adopted in this AZTMD-CVC circuit together with the silicon implementation for prototype testing.

- 4. The signal processing block is designed and integrated together with the proposed AZTMD-CVC to form the accelerometer ASIC.

#### **1.4 Organization of the Thesis**

This thesis comprises nine chapters. Following the introduction, Chapter 2 describes the micro-machining fabrication technology for capacitive MEMS accelerometer devices and the structure of bulk micro-machined sensor device developed in this research project. Behavioral model based on Verilog-A language is developed for the capacitive sensor in order to permit system-level simulation and verification whilst incorporating the transistor-level circuits.

Chapter 3 reviews two representative capacitive sensing methods: continuoustime chopper stabilization (CHS) scheme and discrete-time switched-capacitor (SC) sensing scheme with an in-depth study of the strength and weakness encountered in each scheme. This gives the rationale to the design of accelerometer ASIC using SC design approach. The fundamental switch error mechanism in SC circuit design is discussed. Three representative SC interface circuits are analyzed and discussed in details. These include additional imperfect circuit effects such as 1/f noise, dc offset and finite gain of operational amplifier (op-amp).

Chapter 4 presents overall system architecture in conjunction with its core building blocks. They are the new AZTMD-CVC, the low-noise operational transconductance amplifier (OTA), the differential-to-single-ended amplifier and the on-chip low-noise buffer dedicated to form a signal-conditioning circuit with an external passive filter. Apart from the basic operation principle, the cancellation of the 1/f noise, dc offset, charge injection and clock feed-through effect are discussed in detail. The thermal noise effect, with particular emphasis in the presence of strong sensor parasitic capacitances, is analyzed to serve as the design basis for the low-noise low-power interface circuit. The noise-power optimization is given on how to obtain the optimal figure-of-merit (FOM) in terms of noise-power product on the AZTMD-CVC. Finally, the simulation study for comparison with the three interface circuits, as discussed in Chapter 3, is presented.

Chapter 5 presents the peripheral house-keeping circuitries that include the design and analysis of two integrated clock oscillators with emphasis on both temperature and supply variation compensation for sensor applications. The comparison with other reported counterparts are also given. Besides, another digital control logic module for multi-phase clock generator is also discussed.

Chapter 6 deals with the low-noise layout issues for mixed-signal sensor system. Several layout techniques for low noise consideration are discussed. These include cross-talk reduction between integration capacitors, guard rings for analog switches, sandwich shielding structure for critical analog input paths and power supply decoupling.

7

Chapter 7 presents the measurement results of the accelerometer ASIC, the integrated oscillator and the low-noise low-offset buffer. The performance of the AZTMD-CVC based accelerometer ASIC system is compared with other prior-art reported works.

Chapter 8 summarizes the concluding remarks of research work and discusses the future work of this project.

#### **CHAPTER 2**

### CAPACITIVE MICROMECHANICAL ACCELEROMETER SENSOR

#### 2.1 Silicon Based MEMS Micromachining Technologies

Micromachining is the process technology used to create micromechanical structures with the aid of etching techniques to remove part of the substrate or a thin film. Silicon, one of the nature's cheapest and most abundant elements, has long been exploited as the most commonly used material for semiconductor and IC manufacturing [17]. It is also the ideal substrate material for micromachining of micro-mechanical devices due to its excellent mechanical properties in being ideally elastic, having small thermal expansion coefficient and good functioning stability over a wide temperature range. Hence, most of today's MEMS technology is based on silicon even though not restricted to.

The similar process technologies and compatible equipment used for IC manufacturing and micro-mechanical device development make it possible the monolithic integration of the micro-mechanical devices and electronic functional blocks on to the same silicon wafer or a single chip [18]. Processes like photolithography, growth, deposition and doping are the most basic micro-fabrication technologies commonly used in both micromachining and microelectronics fabrication. Photolithography is always combined with etching to pattern parts of a thin film or the bulk of a flat substrate to create specific shapes. Growth and deposition are methods to make structures in or on silicon with additional materials to achieve certain material properties or to shield the underlying parts under some specific fabrication process. Doping some certain

dopant ions into silicon can change the electrical properties of silicon. It can also change the mechanical properties such as etching rate and can achieve a well-defined stopping position during etching process. Wafer bonding and chemical mechanical polishing are also commonly used techniques in MEMS device fabrication as well as IC packaging and assembly. However, despite these fundamental process technologies in common, specific micro-fabrication processes must be developed for the mechanical device and microelectronics in order to ensure a successful design and development of a monolithic MEMS system, which may need multi-disciplinary efforts and approaches.

Bulk-micromachining and surface-micromachining are the two main wellexplored micro-fabrication process techniques in the development of the silicon based micromachining technologies [19]. In bulk-micromachining, the structures are made in the silicon substrate by selectively removing material while surface-machining is to make small features above the silicon substrate through etching away layers deposited on top of it. The most important aspect for both of these two technologies is the etching of silicon. Among various etching methods, the most widely used techniques are wet-chemical etching and dry etching. Wet etching uses aqueous chemicals to etch away the wafer surface and can be classified into two categories based on the etching etchant's properties: isotropic wet-chemical etching and anisotropic wet-chemical etching. The isotropic silicon etchants have the same etching rates at all directions in the silicon crystal such that the silicon can be etched equally in all directions. Unlikely, the etching rates of anisotropic etchants depend on the crystal orientation and hence anisotropic etching is direction sensitive. The etchants for wet-etching are chosen on the basis of the desired etching rate and the level of anisotropy as well as selectivity required for specific task. An etch stop is adopted to define the required structure. Dry etching employs accelerated ions

or atoms for etching and the process is usually performed in a vacuum chamber under low pressure environment. It includes two techniques: vapor-phase and plasma-phase etching (RIE etching). Although both wet etching and dry etching or the combination of these two etching techniques are available for both bulk and surface micromachining, wet etching is predominantly used in bulk micromachining while dry etching is the primary choice for surface micromachining.

Both bulk micro-machining and surface-micromachining techniques have been widely used in the MEMS device fabrication, but there exists big differences in the two techniques' processing technologies. Hence, it results in considerable differences in the microstructures created. The most significant difference of the devices fabricated in the two technologies lies in the structure dimensions. The vertical dimensions of the bulk micro-machined device are determined by the thickness of the wafer used (typically 500-700 µm), while that of surface micro-machined counterpart is the thicknesses of the film deposited onto the substrate (around 1 µm). Similar difference is observed in the lateral dimensions. Bulk micromachining is usually used to create microstructures like trenches and holes. The bulk wet etching technique can quickly and uniformly etch a large wafer surface area which makes it less time-consuming and relatively low cost process. However, bulk micromachining using wet etching techniques has difficulties in monolithic integration with IC process technology: isotropic wet etching limits the line width resolution while anisotropic etchants is not compatible with the clean room service. Surface micromachining is widely applied in free-moving microstructures fabrications such as basic rotating structures that cannot be realized using bulk micromachining and shows better compatibility with microelectronics process. Unfortunately, surface micro-machined devices may encounter bigger process variations in

both mechanical and electrical properties since the device is using deposited structural and sacrificial layers. Therefore, both of these two micromachining technologies have their own advantages in different aspects. With their own unique process properties, each of these two technologies may dominate the other when involved in various application directions.

#### 2.2 Micromechanical Accelerometer Sensors

A variety of MEMS functioning products have been developed and widely applied in various areas since the emergence of silicon based MEMS micromachining technology. Among them, the micro-sensor-system is the most successfully developed for a vast sales volume and it still embraces great growth potential in commercial markets in the coming years. Micromechanical accelerometer can sense the system acceleration and convert the external force to a physical signal being read by the electronic interface. Fig. 2.1 shows the simplified lumped element model of an accelerometer.

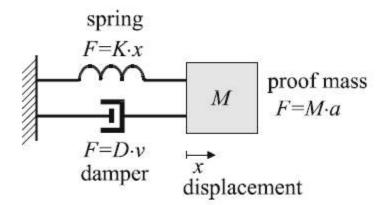

Fig. 2.1 Lumped element model of accelerometer

The accelerometer is a mass-spring-damper system which is composed of a proof mass, a frame and a suspension structure modeled as a spring and a

damper. When an external acceleration is exerted, the proof mass will exert an inertial force on the suspension structure and cause the deformation of the frame as well as the displacement of the mass relative to the fixed electrode. The resulting displacement of the proof mass can be expressed using differential equations as follows:

$$F_x = m\frac{d^2x}{dt^2} + b\frac{dx}{dt} + kx = ma$$

(2.1)

(2.1) can be transformed to s-domain as

$$\frac{X(s)}{F_x(s)} = \frac{1}{ms^2 + bs + k}$$

(2.2)

$$\frac{X(s)}{a(s)} = \frac{1}{s^2 + \frac{b}{m}s + \frac{k}{m}}$$

(2.3)

where m is the mass of the proof mass, b is the damping factor and k is the spring constant. The damper will also affect the motion of the proof mass. The squeeze film damping will occur when two plates are moving towards each other in parallel structures. When the plate is moving slow, the gas is squeezed out causing dissipation loss. When the plate moves fast, the gas will be compressed, leading to spring force. In order to reduce the damping caused viscous loss, the mechanical device is packaged under low pressure or vacuum condition. Brownian noise caused by the gas molecular motions around the proof mass limits the performance of the accelerometer device. By the laws of thermodynamics, the Brownian noise equivalent acceleration is calculated as [20]

$$BNEA = \sqrt{\frac{a_n^2}{\Delta f}} = \frac{\sqrt{4k_B bT}}{m} = \sqrt{\frac{4k_B T\omega_r}{Qm}}$$

(2.4)

where Q is the quality factor,  $\omega_r$  is the resonance-frequency of mass-springdamper system. Hence, it is clearly from (2.4) that in order to achieve a low Brownian noise level, a large proof mass with high quality factor is required.

Accelerometers have been widely used in consumer electronics, automobile, industrial electronics as well as navigation and portable devices. For an exemplary application such as automobile, accelerometers can be utilized for crash detection to activate the deployment of airbags, active suspension and adaptive brake and anti-skiing application. Turning to industrial applications, accelerometers have found in machine condition monitoring, such as the vibration monitoring for the prediction of operation condition of moving machine that aims to improve the machine stability and safety. The tilt and inclination measurement can be used in robotics and instrumentation area. Basing on these applications, MEMS accelerometers are made to have a large range of performance specifications. Table 2.1 shows different performance specifications of accelerometers required for various application categories ranging from the low-cost automobile application to high accuracy navigation application.

| Parameter                 | Automotive | Stability | Navigation |

|---------------------------|------------|-----------|------------|

| Range (g)                 | 50-100     | ±1        | 1          |

| Frequency range (Hz)      | 0-400      | 0-400     | 0-200      |

| Resolution (mg)           | <100       | <10       | <0.004     |

| Maximum shock in 1 ms (g) | >2000      | >2000     | >20        |

| Off axis sensitivity      | <5%        | <5%       | <0.1%      |

| Temperature range (°C)    | -40-85     | -40-85    | -40-80     |

| Temp. Co. of sensitivity  | <900       | <900      | <50        |

| (ppm/ºC)                  | .,00       |           | .50        |

Table 2.1 Specifications of accelerometers for different applications

#### 2.3 Capacitive Micromechanical Accelerometer

Through the research and development efforts, a lot of sensing mechanisms have been developed and realized in MEMS based accelerometer devices. These mechanisms include the piezoresistive, capacitive, piezoelectric, electromagnetic, tunneling and so forth. Among various sensing techniques, capacitive micro-accelerometers have the key advantages of simple structure, high sensitivity, low drift, low temperature dependence, low power consumption and good compatibility with IC process technology. Capacitive accelerometers can offer more sensitivity levels and more resolution choices than similar piezoresistive counterparts. These strengths ensure an ever growing commercial market. The capacitive accelerometer products can cover the lowend application requirement of less than 1g sensing resolution up to the highend accuracy application requirement of micro-g resolution. In recent years, high accuracy accelerometers with micro-g resolution have found many applications in high precision systems like inertial grade navigation system, platform stabilization, low cost inertial measurement units (IMUs) as well as microgravity measurement systems. As a result, they are in big demand.

#### 2.3.1 Surface-Micromachined Capacitive Accelerometer

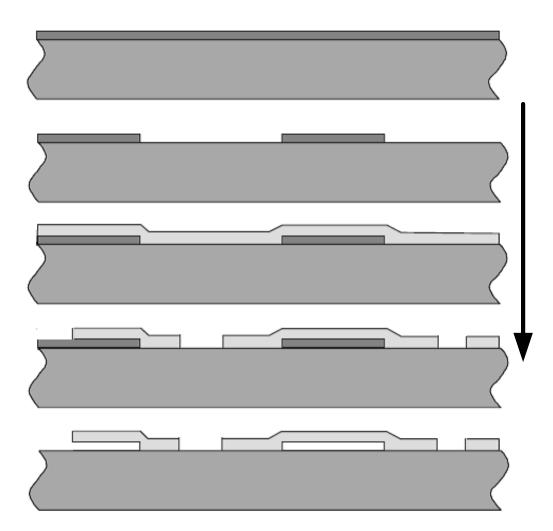

Both bulk micromachining and surface micromachining techniques have been successfully applied to capacitive micromechanical accelerometer sensor design and fabrication. Surface micro-machined accelerometer is formed by selectively etching the sacrificial layer deposited on the silicon substrate, which is typically around 1µm thick. Fig. 2.2 shows the basic surface micromachining process [21]. First, a sacrificial layer is deposited on the silicon substrate. This layer is then patterned using photolithographic and etching techniques. Subsequently, a

structural layer is deposited over the sacrificial layer. This layer will be shaped again using photolithographic and etching techniques. Finally, the sacrificial layer is removed from under the mechanical structures either through the side of the structure or the etch holes.

Fig. 2.2 Basic steps of surface micromachining processes

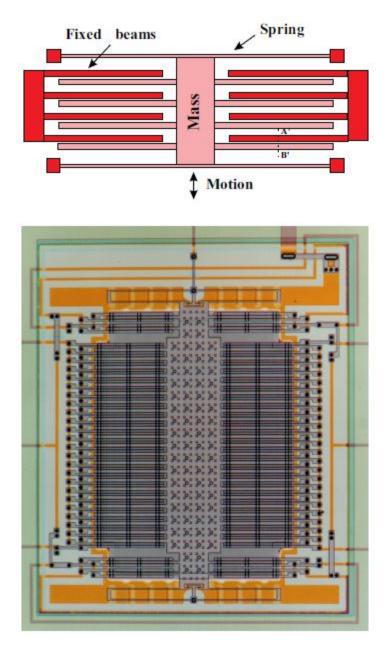

Surface micromachining lends itself well to lateral accelerometer structure fabrication. Fig. 2.3 shows the planar view of a lateral surface micromachined accelerometer and its membrane [19]. A number of moving fingers attached to

the proof mass and the fixed beams attached to the substrate form the comb structures.

Fig. 2.3 Planar view of a lateral accelerometer device and its membrane layout Since the mass of surface micromachined accelerometer is formed by the deposited sacrificial layer, the thickness of comb structures is only on the order of 1 to 2  $\mu$ m. Except for the small sensing mass, under most cases, the motion of the proof mass in surface micromachined device is in the wafer plane. Hence,

the resulting nominal sensing capacitance as well as capacitive sensitivity are both small. Besides, the small mass weighing in a range of from 0.03 to 0.3 mg leads to a much higher mechanical noise as well as lower stability when compared to bulk micromachined devices. In order to increase the nominal capacitance as well as the capacitive sensing sensitivity, hundred finger pairs may be implemented in a lateral accelerometer device. Surface micromachining have also been applied to vertical accelerometer fabrication using double mechanical layer structures by Motorola [22]. Those vertical accelerometers typically have bigger sensing capacitance as well as capacitive signal than lateral structures. Typical surface micromachined accelerometers have noise floors varying from hundreds of  $\mu g/\sqrt{Hz}$  to mg/ $\sqrt{Hz}$  level [23].

#### 2.3.2 Bulk-Micromachined Capacitive Accelerometer

Bulk micromachining techniques usually etch through the wafer from the back side to form the desired structures. Therefore, the whole wafer thickness can be utilized for seismic mass in bulk micromachined device. As such, the bulk micromachined accelerometers have much bigger device sizes than that of surface micromachined counterparts. The thick proof mass typically weighs in the range of from several mg to more than 10 mg. The large proof mass provides much larger capacitances and ensures significantly lower Brownian noise and higher stability for bulk micromachined accelerometer devices. Bulk micromachining process is well suited for vertical accelerometer fabrication. A typical bulk micromachined vertical accelerometer is illustrated in Fig. 2.4. This device is based on a 3-wafer structure assembled by low pressure silicon fusion bonding. In this structure, the top and bottom wafers create the damping needed to prevent excessive moving when an external acceleration approaching the resonant frequency is exerted. Besides, these two wafers also act as counter electrodes while they provide shock protection for the sensor device at the same time. The proof mass of bulk micromachined accelerometers moves perpendicularly to the wafer plane, resulting in a much higher sensing sensitivity.

Fig. 2.4 Planar view of a typical bulk micromachined vertical accelerometer

#### 2.4 Single-Beam Cantilever Suspension Structure

#### 2.4.1 Sensor Structure and Fabrication Process

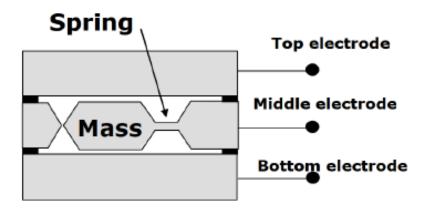

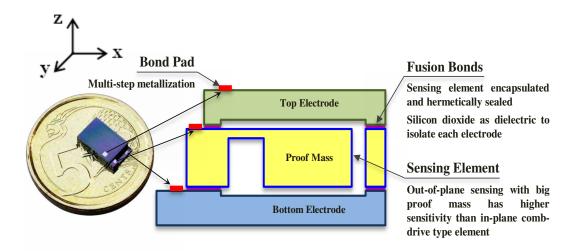

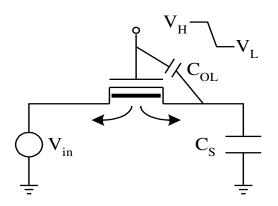

The micro-mechanical accelerometer device adopted in this research project is shown in Fig. 2.5. It is based on a single beam cantilever suspension structure which is fabricated using bulk micromachining process. The middle part of this sensor is a movable proof mass suspended by one cantilever beam at one end, while the top and bottom plates are fixed elements.

Fig. 2.5 Cross-sectional diagram of the bulk micro-machined accelerometer sensor

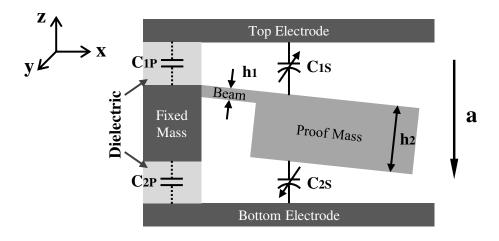

In this structure, the external acceleration perpendicular to the plane of the proof mass causes the proof mass to move in the z-direction, resulting in capacitance changes between the proof mass and two fixed conductive electrodes as illustrated in Fig. 2.6. Variable capacitors  $C_{1S}$  and  $C_{2S}$  represent the differential sensing capacitances while  $C_{1P}$  and  $C_{2P}$  are the parasitic capacitances consisting of bonding capacitances as well as stray capacitances contributed from the oxide insulator between two conducting electrodes.

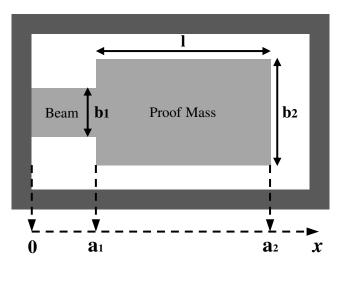

Fig. 2.6 Cross-sectional view (a) and top view (b) of the single beam cantilever structure

Under small deflections condition, the deflection of the proof mass end can be expressed as

$$w(a_2) = \frac{2ma}{Eb_1 h_1^3} \left( 15La_1 - 5a_1^2 - 12L^2 \right) a_1$$

(2.5)

where *E* is the modulus of elasticity for silicon  $(1.7 \times e^{11} \text{ Pa})$ , *a* is the external acceleration,  $h_1$  is the thickness of beam,  $b_1$  is the width of the beam,  $a_1$  is the length of beam,  $a_2$  is the distance of the proof mass end from the frame and L is the distance of the proof mass center from the support. The sensing capacitance  $C_{1S}$  and  $C_{2S}$  can be estimated by integrating along the length of proof mass [24] as follows:

$$C_{1S} = \int_{a_1}^{a_2} \frac{\mathcal{E}\mathcal{E}_0 b_2}{d_0 + w(x)} dx$$

(2.6)

$$C_{2S} = \int_{a_1}^{a_2} \frac{\mathcal{E}\mathcal{E}_0 b_2}{d_0 - w(x)} dx$$

(2.7)

where  $d_0$  is the nominal distance between the proof mass and the fixed

electrodes and  $b_2$  is the width of the proof mass. Hence, the external acceleration is converted to the sensing capacitance changes which can be measured by the electronic front-end interface circuit. The out-of-plane sensing scheme significantly increases the capacitance sensitivity for bulk micro-machined device than any in-plane sensing scheme. High sensor sensing sensitivity is desired for low-noise sensor system [25]. Mechanical thermal noise caused by the Brownian motion of proof mass is another important factor that will limit the system noise performance. This can be reduced by increasing the mass of the movable electrode. Since the bulk micromachining process creates micro-mechanical structures through selectively etching a whole silicon wafer, the vertical dimensions of the created structures can be made of the typical wafer thickness of 500-700 µm. This makes the fabrication of large proof mass possible, which is critical to ensure a lower Brownian noise floor.

Referring to Fig. 2.5, the fabrication of the mechanical sensor device is based on three silicon wafers. The center wafer is made as the middle moving electrode whilst the upper and lower wafers are dry-released as the external fixed electrodes. These three wafers are fusion bonded together with an optimal gas damping and bandwidth control whilst at the same time allowing the sensing element to be encapsulated and hermetically sealed. Silicon dioxide is buried as the dielectric to isolate these three electrodes. Sensor bonding pad are made through multi-step metallization. The sensor device is wire bonded to a standard DIP package to mount together with the readout integrated circuit (IC) on the PC board for system integration. The specifications of the accelerometer IC targeted for security application are summarized in Table 2.2.

| Parameter                               | Security<br>(gravity tilting sense) |  |

|-----------------------------------------|-------------------------------------|--|

| Range (g)                               | +/-1g                               |  |

| Frequency range<br>(Hz)                 | 0-300                               |  |

| <b>Resolution</b> (ug/ $\sqrt{Hz}$ )    | <5µg/√Hz                            |  |

| Maximum shock in 1<br>ms (g)            | 10 g                                |  |

| Temperature range<br>(°C)               | -40 to 90                           |  |

| Temp. Coeff. of<br>sensitivity (ppm/°C) | <50                                 |  |

Table 2. 2 Specifications of Accelerometer IC

### 2.4.2 Sensor Modeling in Verilog-AHDL

In order to perform circuit simulation for proper analysis and design of the sensor system composed of the accelerometer device and electronic interface block, a sensor model must be established. Sensor sensitivity, nominal sensing capacitances and parasitic capacitances are essential model parameters for a sensor model. Compared with those mixed-signal simulators with built-in mechanical-type models, the electrical sensor model is much easier to be implemented since the algorithm is efficient and compatible with electrical simulators [26]. This Section introduces the Verilog-AHDL based behavioral modeling for the single beam cantilever based accelerometer sensor device.

Under 0 g acceleration condition, the nominal capacitance value is characterized as follows:

$$C_{1S} = C_{2S} = \frac{\varepsilon_0 A_M}{d_0}$$

(2.8)

where  $A_M$  is the proof mass area. Figure 2.7 illustrates the movement of the proof mass under external force with the change of the gap distances between middle to top electrode and middle to bottom electrode respectively.

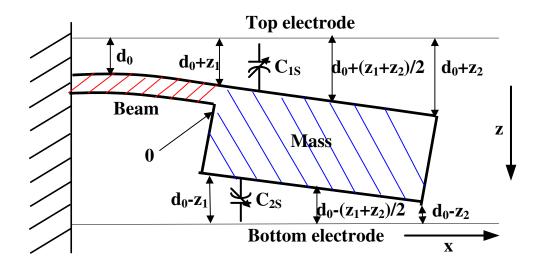

Fig. 2.7 Gap distance changes with proof mass movement under external acceleration

In a cantilever structure, the accelerated proof mass is tilting instead of moving parallel to the fixed electrodes. Hence, as depicted in Fig. 2.7, the displacement varies from  $z_1$  to  $z_2$  along the length of the proof mass. Under real conditions, both the movable proof mass and the beam will bend due to the exerted force. However, the displacement of the proof mass is thousand times of that of the cantilever beam [27]. Thus, the change of the beam capacitance can be deemed as negligible which means  $z_1\approx 0$ . Hence, in the sensor modeling equation, only the deflection of the proof mass is considered. As discussed in the single beam cantilever structure, the exact equations (2.6) and (2.7) characterizing sensing capacitance under acceleration should be obtained through integrating methodology. However, the equations embedded with integration are too complex to be described using Verilog-A language. Since the displacement along z axis is much smaller than the length of the proof mass along x axis. Hence, the variation of the gap distance along the proof mass can be deemed as linear, thus one can simply assume a constant displacement along the proof mass and use the displacement value z at the mid-point of the proof mass to represent the total capacitance change. Hence, the equations of sensing capacitance under external acceleration can be simplified as follows:

$$C_{1S} = \frac{\varepsilon_0 A_M}{d_0 + z} \tag{2.9}$$

$$C_{2S} = \frac{\varepsilon_0 A_M}{d_0 - z} \tag{2.10}$$

Based on the simulation results of the given bulk micromachined MEMS accelerometer, the maximum displacement at the tip of the proof mass under 1 g acceleration is around 0.483 µm or  $z_2 = 0.483 µm$ . Thus, the displacement at the mid-point of the proof mass is  $z_2/2=0.2416 µm$  ( $z_1 = 0 µm$ ) under 1g acceleration. Since the displacement is proportional to external acceleration, the average displacement z under an external acceleration  $\alpha$  can be expressed as

$$z = 0.2416\alpha \tag{2.11}$$

Substitute (2.11) to (2.9) and (2.10) to characterize the relationship between the sensing capacitance and the external acceleration  $\alpha$  (in g), we obtain

$$C_{1S} = \frac{\varepsilon_0 A_M}{d_0 + 0.2416\alpha}$$

(2.12)

$$C_{2S} = \frac{\varepsilon_0 A_M}{d_0 - 0.2416\alpha} \tag{2.13}$$

(2.12) and (2.13) can be described using Verilog-A language. Following is the introduction of the Verilog-A language.

Verilog-A language characterizes the behavior model of differential sensing capacitance structure and generates a sensor model symbol for the simulation [28]. The model description is summarized as follows:

- The Verilog-A module is a text file with code statements written in Verilog-A syntax.

- The text file describes the function of the Verilog-A module.

- The text file is saved as a Verilog-A view of the cell.

- A corresponding symbol view for the module will be generated and used as an instance in a schematic for simulation.

The major types of Verilog-A modules include:

- Behavioral models The model is defined by mathematical descriptions relating output signal behavior to the input signals.

- Structural models The model is defined by instantiation of components.

- Mixed structural and behavioral models— The model is defined by instantiation of the primitives and by mathematical descriptions relating output signal behavior to input signals.

The behavioral description is a mathematical mapping which relates the output signals of the module to input signals in terms of a large-signal or time-domain behavioral description. The mapping uses the Verilog-A language contribution operator "<+" which assigns an expression to a signal. The assigned expression can be linear, non-linear, algebraic and/or differential functions of the input

signals. These large-signal behavioral descriptions define the constitutive relationship of the module, and take the form of following:

output\_signal <+ f ( input\_signal );</pre>

In signal contribution, the right-hand side expression, or f ( input\_signal ), is evaluated, and its value is assigned to the output signal. The connection points of the module are defined by the port signal interface declarations.

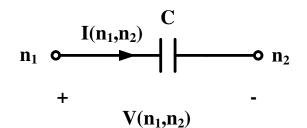

For illustration of the large signal behavioral model, a simple charge-based model for capacitive component is introduced. As shown in Fig. 2.8, for a capacitive component with two connection nodes  $n_1$  and  $n_2$ , the proper approach to build a large-signal behavior is to reconstruct q as a function of the capacitance C as well as the voltage V( $n_1$ , $n_2$ ) across it. It is also to make charge q as the right-hand signal to be evaluated while the current I( $n_1$ , $n_2$ ) is the output signal.

Fig. 2.8 Behavioral model of a two node capacitor

The current through a capacitor is the time derivative of the capacitance charge which is expressed as [29]

$$i(t) = \frac{dq(v(t))}{dt}$$

(2.14)

Hence, for the two node capacitor component shown in Fig. 2.8, one can write:

$$i_c = \frac{d}{dt} \left( C \cdot V(n_1, n_2) \right) \tag{2.15}$$

Converting (2.15) to signal contribution form used in large-signal behavioral descriptions, it yields

$$I(n_1, n_2) < + ddt(C \cdot V(n_1, n_2))$$

(2.16)

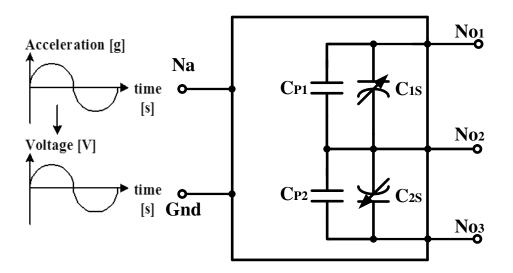

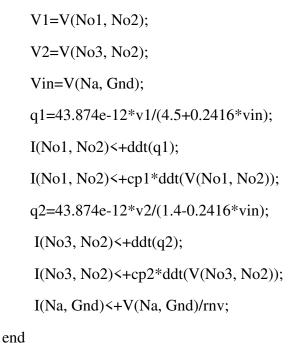

where ddt() performs time-differentiation of its argument. The simplified electrical circuit model [30] for the bulk micro-machined sensor developed in this research project is shown in Fig. 2.9, which is consisted of the two differential sensing capacitors  $C_{1S}$  and  $C_{2S}$  as well as the parasitic capacitances  $C_{1P}$  and  $C_{2P}$  connected between node  $N_{o1}$ ,  $N_{o2}$  and node  $N_{o3}$ ,  $N_{o2}$  respectively. Node Na and Gnd belong to the input signal port. In this electrical sensor model, a variable voltage source is used to simulate the external acceleration signal. 1 V input voltage is treated equal to 1g acceleration in the model.

Fig. 2.9 Equivalent electrical circuit symbol for the accelerometer sensor device

Following is the Verilog-A text file of the large signal description of the electrical circuit model shown in Fig. 2.9.

VerilogA for sensormodeling, sensor model, veriloga

'include "constants.vams"

'include "disciplines.vams"

Module sensormodel(Na, No1, No2, No3, Gnd): (Module interface declaration)

Inout Na, No1, No2, No3, Gnd;

electrical Na, No1, No2, No3, Gnd;

(Port directions)

(Port disciplines)

parameter real cp1=50p;

parameter real cp2=50p;

parameter real rnv=10T;

real V1, V2, q1, q2, Vin;

analog begin;

- --

endmodule

Behavioral description of the sensing and the parasitic

### 2.4.3 Verification of the Sensor Model

The two expressions of q1 and q2 of the Verilog-A syntax are the equations describing the variable capacitance and capacitance sensitivity, respectively. Vin is used to model the physical acceleration and 1V represents 1g acceleration on the sensor device. Hence, it is easy to calculate the capacitance sensitivity using these two expressions. Under 1g acceleration, the capacitance change is calculated in the following:

$$\Delta C(N_{o2}, N_{o3}) = \frac{43.874}{4.5 + 0.2416} - \frac{43.874}{4.5} = -0.495 \, pF \tag{2.17}$$

$$\Delta C(N_{o1}, N_{o2}) = \frac{43.874}{1.4 - 0.2416} - \frac{43.874}{1.4} = 6.54 \, pF \tag{2.18}$$

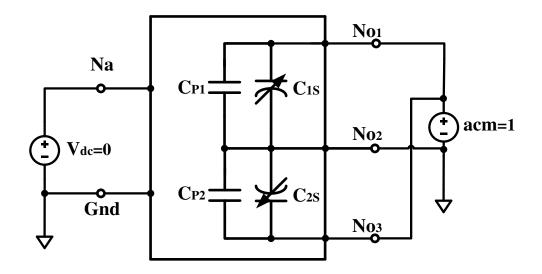

In order to verify the correctness of the capacitance behavioral description based equation, a simple circuit setup shown in Fig. 2.10 is implemented incorporating the generated sensor symbol for the verification.

Fig. 2.10 Sensor model test circuit

- Driving the sensing capacitor with a voltage source with unity AC magnitude.

- Perform an AC analysis at  $1000/2\pi$  Hz while sweeping the DC source voltage from -1V to 1V.

- Plot the current through the capacitor and change the units from Amperes to Farads.

The relationship between current, capacitance and the voltage across the capacitor is

$$I = \omega^* C^* V = 2\pi f^* C^* V$$

(2.19)

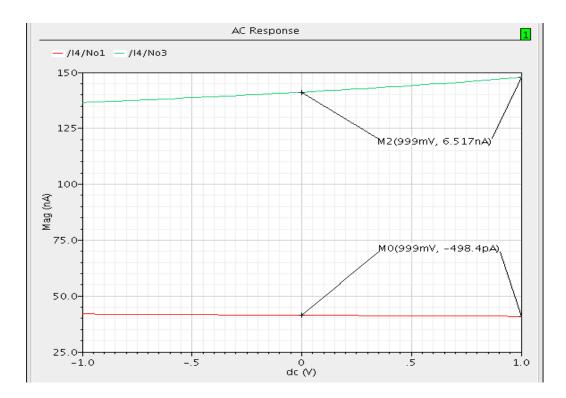

According to (2.19), for f=1000/2 $\pi$  Hz, V=1V, we will obtain C=I/1000, yielding  $\Delta$ C= $\Delta$ I/1000. This means that one can get the capacitance sensitivity through measuring the current change between 0 and 1V voltage input (1V input represents 1 g acceleration). Fig. 2.11 shows the simulation result. Under 1V voltage change, the current change is 6.5nA and -0.5nA for the node N<sub>o1</sub> and N<sub>o2</sub> respectively. As a result, the capacitance change between N<sub>o1</sub> and N<sub>o2</sub> is 6.5/1000nF=6.5pF. On the other hand, the capacitance change between N<sub>o2</sub> and N<sub>o3</sub> is -0.5/1000nF=-0.5pF. This simulation result is close to the calculations according to (2.17) and (2.18). Therefore, it has verified the modeling equations.

Fig. 2.11 The output ac currents of the two sensing nodes

The equation is a simplified first-order approximation of the cantilever sensor structure. In practice, the structure will suffer from higher-order nonlinear dependence between the acceleration and gap distance deflection. As such, there exists a certain error in the simplified model result. The percentage errors between the model capacitance sensitivity value and the ideal value at different levels of acceleration are listed in Table 2.3. The average percentage error for  $C_{1S}$  is 4.48% with a standard deviation of 0.04 whereas the average percentage error for  $C_{2S}$  is 3.58% with a standard deviation of 0.02. Since the percentage errors are reasonably small, the simplified model is adequate to predict the capacitance values for obtaining reasonable good accuracy.

| Acceleration (g) | Percentage error (%) |                 |

|------------------|----------------------|-----------------|

|                  | C <sub>1S</sub>      | C <sub>2S</sub> |

| 0                | 4.3961               | 3.5456          |

| 0.05             | 4.4084               | 3.5490          |

| 0.1              | 4.4201               | 3.5527          |

| 0.15             | 4.4312               | 3.5568          |

| 0.2              | 4.4416               | 3.5610          |

| 0.25             | 4.4515               | 3.5654          |

| 0.3              | 4.4606               | 3.5698          |

| 0.35             | 4.4692               | 3.5742          |

| 0.4              | 4.4771               | 3.5785          |

| 0.45             | 4.4844               | 3.5826          |

| 0.5              | 4.4910               | 3.5866          |

| 0.55             | 4.4970               | 3.5902          |

| 0.6              | 4.5023               | 3.5937          |

| 0.65             | 4.5070               | 3.5967          |

| 0.7              | 4.5111               | 3.5995          |

| 0.75             | 4.5146               | 3.6018          |

| 0.8              | 4.5174               | 3.6038          |

| 0.85             | 4.5196               | 3.6053          |

| 0.9              | 4.5211               | 3.6065          |

| 0.95             | 4.5221               | 3.6071          |

| 1                | 4.5224               | 3.6074          |

Table 2.3 Percentage errors of the capacitance between the first-order model

and the ideal case at different acceleration levels

## **CHAPTER 3**

# CIRCUIT TECHNIQUES FOR CAPACITIVE ACCELEROMETER INTERFACE

### **3.1 Introduction**

As discussed in the preceding Chapter, a capacitive micro-accelerometer system is composed of a mechanical sensor device and an electrical capacitance-to-voltage converter (CVC). The capacitance-to-voltage converter interfaced with the sensor device will convert the capacitance changes, caused by external forces exerted onto the micro-sensor system, to an electrical output for further signal processing. The electronic interface plays the most important role in determining the overall system performance such as the power consumption, sensing resolution, system noise level as well as linearity and distortion. For a high resolution microsystem, design considerations of the interface circuit are necessary to ensure a high quality system performance.

The electronic interface circuit techniques suitable for capacitive sensing can be roughly divided into the continuous time (CT) chopper stabilization (CHS) [31] sensing scheme and the discrete time (DT) auto zero (AZ) sensing scheme (or the switched-capacitor (SC) scheme) [32],[33]. Both schemes can be implemented in either open-loop architecture or closed-loop architecture in a system. A variety of highly-sensitive interface circuits had been reported in the literatures. In this Chapter, the CHS scheme and switched-capacitor correlated double sampling (SC-CDS) scheme as a special case of AZ technique will be firstly reviewed. Besides, the strength and weakness of each circuit technique

are discussed and compared. It is then followed by the detailed analysis and discussion on several recently published works on SC-CDS sensing scheme.

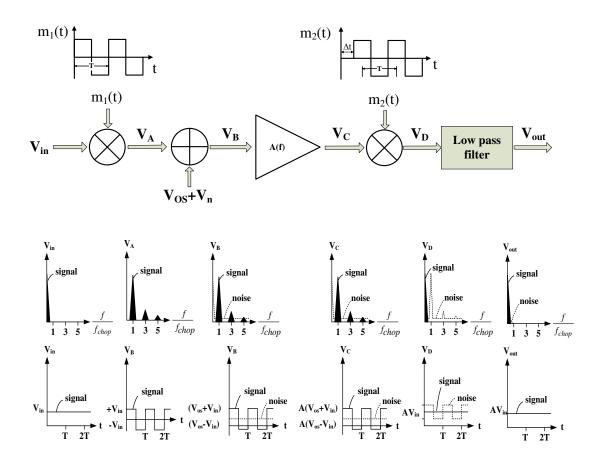

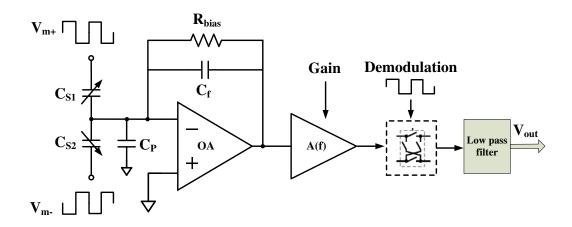

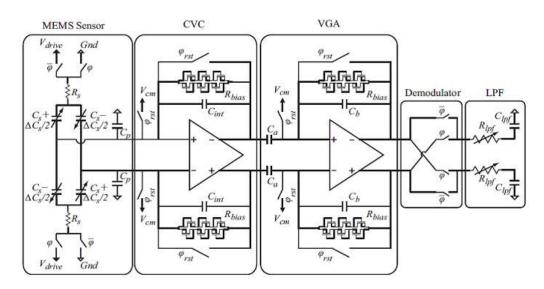

# **3.2 Review of Capacitive Sensing Interface Circuit** Schemes