This is an electronic reprint of the original article.

This reprint may differ from the original in pagination and typographic detail.

Kempi, I.; Ahmed, N.; Hammer, A.; Olabode, O.; Unnikrishnan, V.; Kosunen, M.; Ryynänen, J. A Low-Power Hardware Stack for Continuous Data Streaming from Telemetry Implants

Published in:

2018 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC)

DOI:

10.1109/NORCHIP.2018.8573522

Published: 01/01/2018

Document Version

Peer reviewed version

Please cite the original version:

Kempi, I., Ahmed, N., Hammer, A., Olabode, O., Unnikrishnan, V., Kosunen, M., & Ryynänen, J. (2018). A Low-Power Hardware Stack for Continuous Data Streaming from Telemetry Implants. In *2018 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC)* (pp. 1-6). IEEE. https://doi.org/10.1109/NORCHIP.2018.8573522

This material is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

# A Low-Power Hardware Stack for Continuous Data Streaming from Telemetry Implants

Ilia Kempi, Nouman Ahmed, Andreas Hammer, Olaitan Olabode, Vishnu Unnikrishnan, Marko Kosunen, Jussi Ryynänen Department of Electronics and Nanoengineering Aalto University School of Electrical Engineering, Espoo, Finland Email: ilia.kempi@aalto.fi

Abstract—This paper describes the hardware implementation of a custom communication protocol tailored for low-power telemetry data streaming over an inductive link. The application-specific features of typical RFID implementations such as random number generation and variable data rate support are omitted from the proposed implementation, focusing only on the continuous data transfer. The post-synthesis results of proposed communication scheme implemented on 28nm CMOS FDSOI process show power consumption of 3.11  $\mu W$  while running from a 845.7 kHz clock and occupying 0.0048  $mm^2$  of die area. The current implementation provides an uplink rate of 8 kbit/s, sufficient for streaming of 1-channel 1 kHz 12-bit sample recording.

## I. INTRODUCTION

IRELESS data transmission capability over an inductive [1] or acoustic link [2] is a de-facto standard for implantable biomedical systems. Modern subcutaneous implants are designed to operate solely on DC power extracted through the same inductive link [3], [4], making the magnetically-coupled coils an essential part of the readerimplant interface. Being in a low-power device, telemetry implant still requires fast and resilient uplink channel in order to reliably transmit the data acquired at the front end. The uplink bit rate and the power consumption can be considered as the key design specifications for the communication system of an implant [5]. In addition, error detection and correction are indispensable for a communication protocol targeted at transmission over a lossy and noisy medium such as skin tissue.

A standard implementation of a Radio-Frequency Identification (RFID) processor has a set of communication primitives namely, donwlink decoder, uplink encoder, and state control together with additional protocol-specific features such as random-number generation [6] and encryption [7] which may not be necessary in context of a low-power sensor implant. The design of a transceiver for sensor implants can do away with such overheads to obtain a power efficient yet robust communication link.

In this paper we present an uplink-intensive communication stack which provides the means to communicate with an external reader device and mitigate data loss. The paper is organized as follows. Section II introduces the key properties of the proposed communication scheme. Section III describes the implementation of the scheme in digital logic and Section IV

presents the results of hardware synthesis. The conclusions will be given in Section V.

# II. PROPOSED COMMUNICATION SCHEME

This section describes the requirements on a communication system that needs to acquire a continuous stream of data and introduces the key properties of the proposed communication scheme.

# A. Buffering and Error Mitigation

In context of telemetry implants, the data payload often comes as an uniformly sampled signal. The task of the communication subsystem, especially in implants without storage is to ensure that all the data arrives at the reader device. In order to preserve the order and integrity of the sampled sequence transmitted through a noisy medium, the communicating entities must incorporate a mechanism to avoid data loss and corruption. Two necessary protocol features required for this are the error detection and the acknowledgment procedure [8]. When the error cannot be corrected, the received samples shall be stored in buffer memory for retransmission. The data can be discarded from the buffer only after the receiving acknowledgment from the reader.

# B. Communication System Architecture

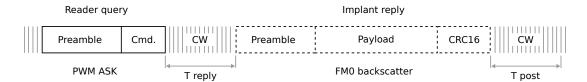

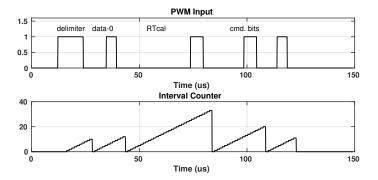

The Amplitude-Shift Keying (ASK) and backscattering are considered to be techniques of choice in context of low-power inductive implants [9], [10]. In proposed communication scheme, the downlink commands are sent with Pulse-Width Modulated (PWM) ASK and the implant response is backscattered to the reader with an On-Off Keying (OOK) sequence encoded with FM0 [11]. As a generic convention on PWM, the Pulse-Interval Encoding (PIE) is used [11]. Fig. 1 illustrates a typical reader-implant interaction.

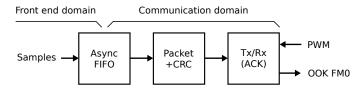

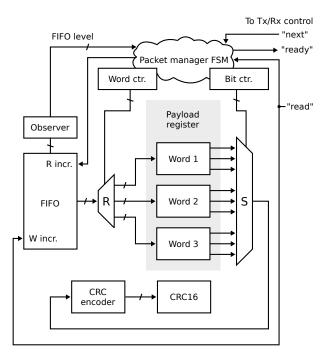

To avoid data loss, the minimum set of streaming functionality outlined in section II-A is implemented along with communication primitives. Fig. 2 shows the structure of the communication system. For the communication clock frequencies are considered that are derivable from a 866 MHz carrier Ultra-high frequency (UHF) RFID band allocation in Finland [12]. As a solution for transferring the data from the sampling clock domain, the asynchronous first-in first-out (FIFO) model is utilized as the uplink buffer. The error

Fig. 1. Communication between the reader and the implant. CW stands for continuous wave emitted by the reader. The reader query is amplitude modulated while implant reply is transmitted using backscatter modulation (dashed line). The periods of transmission by reader and implant are followed by delays of  $T_{\text{reply}}$  and  $T_{\text{post}}$  accordingly.

Fig. 2. Structure of the communication system.

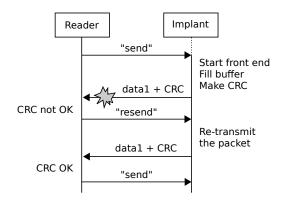

Fig. 3. Example communication scenario. Reader requests the previous packet in case CRC recovery fails.

detection is realized by padding the packet with a Cyclic Redundancy Check (CRC) pattern, allowing for recovery of 1-bit payload errors at the receiver [13], [14]. The acknowledgment logic (ACK) is implemented as a part of the transceiver state machine. A minimalistic acknowledgment procedure is formulated with two reader commands, namely "send" and "resend". The former instruction is issued for both requesting the new data and approving the previous transmission. When transmission fails, the last packet is requested instead with the "resend" instruction as shown in Fig. 3.

To reduce the design footprint, the proposed implementation utilizes only protocol features that are relevant for data transmission between the implant and the reader. Functionalities such as support for variable data rate and memory operations commonly present in RFID processor designs [6], [15], are excluded, optimizing this communication scheme specifically for wireless data streaming.

## III. IMPLEMENTATION

This section describes the implementation of the proposed communication scheme in digital hardware and substantiates

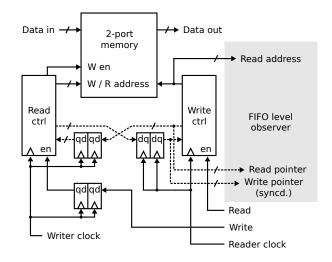

Fig. 4. Asynchronous FIFO with a level observer. The reader handles both ends of the queue via synchronized one-bit line. The dashed lines denote the gray-coded pointer data.

the decisions made during the design process.

# A. Asynchronous FIFO Buffer

The access to the state of the data buffer is crucial for timely transmission of accumulated readings. The state of an asynchronous FIFO is represented by read and write pointers and is distributed across separate clock domains and needs to be re-synchronized after each event [16]. Fig. 4 shows the structure of an asynchronous FIFO with the level observer. The level observer logic determines the amount of words in the buffer based on the information obtained from the read control unit. The FIFO level is found with binary subtraction between read and write addresses and the full condition is resolved by pointer comparison [16]. In order to avoid losing samples at the input of the buffer, it is mandatory to dispatch the data sooner than FIFO becomes full. The synchronization of the read pointer lasts two cycles of the sampling clock, causing a delay in removing the "full" condition at the reader side. As a requirement, the FIFO capacity should be strictly larger than the payload size to be read from the buffer.

In this work, a 8-word deep FIFO is utilized to store 12-bit samples arriving at 1 kHz. The threshold of packet manager is two samples per payload, which ensures that the data is flushed before the FIFO is full. The selected buffer depth

Fig. 5. Packet manager module. The registers which store payload and CRC are further accessible for the transceiver.

allows up to 7 ms (i.e. 7 samples in memory) of delay due to retransmission.

## B. Communication Packet Manager

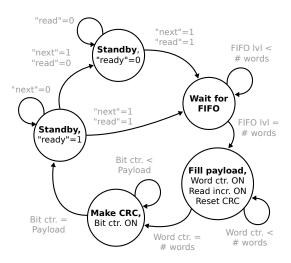

The packet manager provides the transceiver with the uplink data by populating the payload from the buffer and appending it with the CRC checksum. The structure of the packet manager module is shown in Fig. 5. The difference between sampling and communication clock domains provides enough time in between samples to use a serial-type CRC encoder [17], thus allowing to further minimize the physical area of the system [18]. The packet manager FSM is controlling the packet assembly process according to state diagram shown in Fig. 6. Once enough samples are accumulated in the buffer, the payload register is rewritten with a number of consecutive samples from the FIFO through the routing (R) demultiplexer. The contents of the new payload are serialized into the CRC encoder with the serializer (S) multiplexer.

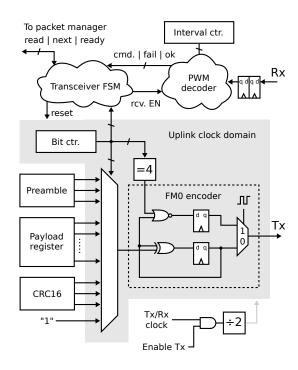

# C. Transceiver

The transceiver control is distributed between two state machines, namely the Transceiver FSM and the PWM decoder FSM, as shown on Fig. 7. The PWM sampling resolution is the most restricting factor for the transceiver clock rate [6]. Since the variable data rate support is excluded in this implementation (section II-B), the downlink PWM time constants are fixed at values listed in table I. The selection of such coarse downlink constants allows to run the transceiver clock as slow as 845.7 kHz (derived from carrier) further reducing the dynamic power consumption of the system. In order to keep the backscattering frequency within limits specified in

Fig. 6. Packet manager state diagram

Fig. 7. Transciever structure

TABLE I COMMUNICATION TIME CONSTANTS

| Wait Periods        |              |

|---------------------|--------------|

| Treply              | $40~\mu s$   |

| Tpost               | $40~\mu s$   |

| PWM Parameters [11] |              |

| Delimiter           | $12.5~\mu s$ |

| data-0              | $15 \mu s$   |

| data-1              | $25 \mu s$   |

| PW                  | $5 \mu s$    |

| RTcal               | $40~\mu s$   |

the EPC RFID C1 G2 [11], the FM0 uplink rate is set to 422.85 kHz. The transceiver generates uplink clock with a

Fig. 8. FM0 preamble. The intentional encoding violation "v" is used to aid the frame synchronization.

Fig. 9. Value of the Interval counter during the decoding of command from the reader.

divider, providing a phase-coherent subdomain for safe register comparisons at the FSM side. The packet is serialized into the FM0 encoder as shown in Fig. 7. This 2-flipflop encoder structure is derived from the FM0 state transition diagram [19]. The NOR gate suppresses the output of the encoder for the next high cycle of the uplink clock, producing the desired encoding violation during the transmission of FM0 preamble symbols "101001" as shown in Fig. 8. At the end of the packet, a dummy "1" is appended to indicate the end of FM0 signaling [11].

# D. PWM Decoding

The PWM decoder is built as an FSM which utilizes a fast Interval counter to measure the incoming symbols. The state transitions are tailored such that the counter value is compared against the pre-defined interval values and then reset for the new measurement. Fig. 9 shows the behaviour of the Interval counter during the decoding.

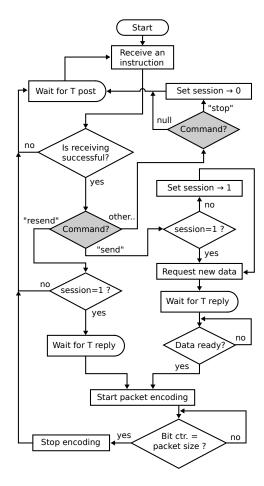

#### E. Transceiver FSM

The transceiver FSM implements the proposed communication protocol as shown in flowchart on Fig. 10. Mandatory delay intervals  $T_{\rm reply}$  and  $T_{\rm post}$  are measured with a dedicated delay counter (not on Fig. 7). In order to control the state of implant transceiver, an exclusive "session" bit in transceiver memory is set or reset with commands "send" and "stop" respectively. Initialized with zero, this flag controls the writing into FIFO as the "read" input to the packet manager.

# IV. RESULTS

This section presents the evaluation of the design by means of hardware synthesis and simulations.

Fig. 10. Flowchart of the Transceiver FSM operation. Gray blocks indicate decisions based on the command from the reader.

# A. Hardware Synthesis

The hardware description of the proposed communication system was implemented in VHDL and synthesized for CMOS 28nm FD-SOI process using Synopsis Design Compiler. The layout of the digital circuit is done in Cadence Innovus. The timing of implemented design is verified by Synopsis Prime Time static timing analysis (STA) tool. The functionality of the communication system is tested using behavioural simulation with back-annotated delays extracted from the layout.

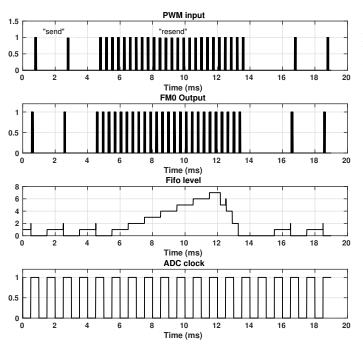

## B. Behavioural Simulation

Figure 11 demonstrates the operation of the implemented system as it communicates with the reader emulator. Upon reader request, the implant accumulates the incoming data and dispatches it shortly. The reader acknowledges the successful transmission by requesting new data, and the procedure repeats. Upon issuing the "resend" command continuously, the reader forces the implant to reuse the packet while accumulating the data in FIFO. After the reader starts acknowledging the incoming packets again, the implant will continue the communication by dispatching all of the FIFO entries first.

Fig. 11. Simulation of data loss and retransmission.

## C. Power and Area

The average power consumption of the system is estimated with a transient simulation of a synthesized netlist. The simulation reconstructs the typical transceiver activity during active communication. Table II shows the relevant statistics.

## TABLE II POST-SYNTHESIS RESULTS

| Technology        | CMOS 28nm FD-SOI |

|-------------------|------------------|

| Supply voltage    | 0.7 V            |

| Transceiver clock | 845.7 kHz        |

| Uplink rate       | 8 kbit/s         |

| Area              | $0.0048 \ mm^2$  |

| Average power     | $3.11~\mu W$     |

| Leakage power     | $2.7~\mu W$      |

## V. CONCLUSION

This is a custom implementation of inductive link communication protocol especially targeted for telemetry data transfer in the context of implants. The proposed communication scheme provides the means to communicate with an external reader and mitigate data loss while utilizing minimal hardware resources. The design target was achieved by incorporating only the functionality which is necessary for reliable data transmission.

The post-synthesis simulation shows power consumption of  $3.11~\mu W$  at clock rate of 845.7 kHz and supply of 0.7 V. The achieved layout area is  $0.0048~mm^2$ . The uplink rate of 8 kbit/s is sufficient for transmission of 1-channel 1 kHz 12-bit sample, and up to 7 ms time is allowed for retransmission during channel failures.

The power consumption estimates of indicate that the proposed hardware implementation fits well in the implant power budget down to 1 mW [20], leaving sufficient energy resource for the signal acquisition front-end.

#### ACKNOWLEDGEMENTS

The authors would like to thank Academy of Finland (project 269196) for supporting this research work.

#### REFERENCES

- [1] C. M. Zierhofer and E. S. Hochmair, "High-Efficiency Coupling-Insensitive Transcutaneous Power and Data Transmission Via an Inductive Link," *IEEE Transactions on Biomedical Engineering*, 1990.

- [2] F. Mazzilli, M. Peisino, R. Mitouassiwou, B. Cotté, P. Thoppay, C. Lafon, P. Favre, E. Meurville, and C. Dehollain, "In-vitro platform to study ultrasound as source for wireless energy transfer and communication for implanted medical devices," in 2010 Annual International Conference of the IEEE Engineering in Medicine and Biology, Aug 2010, pp. 3751–3754.

- [3] G. Wang, W. Liu, M. Sivaprakasam, and G. A. Kendir, "Design and analysis of an adaptive transcutaneous power telemetry for biomedical implants," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 52, no. 10, pp. 2109–2117, Oct 2005.

- [4] P. Cong, N. Chaimanonart, W. H. Ko, and D. J. Young, "A Wireless and Batteryless 10-Bit Implantable Blood Pressure Sensing Microsystem With Adaptive RF Powering for Real-Time Laboratory Mice Monitoring," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, pp. 3631– 3644, Dec 2009.

- [5] M. Sawan, Y. Hu, and J. Coulombe, "Wireless smart implants dedicated to multichannel monitoring and microstimulation," *IEEE Circuits and Systems Magazine*, vol. 5, no. 1, pp. 21–39, 2005.

- [6] D. Wei, C. Zhang, Y. Cui, H. Chen, and Z. Wang, "Design of a low-cost low-power baseband-processor for UHF RFID tag with asynchronous design technique," in 2012 IEEE International Symposium on Circuits and Systems, May 2012, pp. 2789–2792.

- [7] A. Ricci, M. Grisanti, I. D. Munari, and P. Ciampolini, "Design of a 2 uW RFID baseband processor featuring an AES cryptography primitive," in 2008 15th IEEE International Conference on Electronics, Circuits and Systems, Aug 2008, pp. 376–379.

- [8] B. Smith, Z. Tang, M. W. Johnson, S. Pourmehdi, M. M. Gazdik, J. R. Buckett, and P. H. Peckham, "An externally powered, multichannel, implantable stimulator-telemeter for control of paralyzed muscle," *IEEE Transactions on Biomedical Engineering*, vol. 45, no. 4, pp. 463–475, April 1998.

- [9] R. Bashirullah, "Wireless Implants," *IEEE Microwave Magazine*, vol. 11, no. 7, pp. S14–S23, Dec 2010.

- [10] M. A. Hannan, S. M. Abbas, S. A. Samad, and A. Hussain, "Modulation Techniques for Biomedical Implanted Devices and Their Challenges," *Sensors*, vol. 12, no. 1, pp. 297–319, dec 2011.

- [11] GS1, "EPC TM Radio-Frequency Identity Protocols Generation-2 UHF RFID Specification for RFID Air Interface," pp. 1–152, 2013.

- [12] —, "Regulatory status for using RFID in the EPC Gen 2 band (860 to 960 MHz) of the UHF spectrum," pp. 1–22, 2018.

- [13] P. S. P, R. A, and A. S. Kotain, "Article: FPGA Implementation of Single Bit Error Correction using CRC," *International Journal of Computer Applications*, vol. 52, no. 10, pp. 15–19, August 2012.

- [14] S. Shukla and N. W. Bergmann, "Single bit error correction implementation in CRC-16 on FPGA," in *Proceedings*. 2004 IEEE International Conference on Field- Programmable Technology (IEEE Cat. No.04EX921), Dec 2004, pp. 319–322.

- [15] A. S. W. Man, E. S. Zhang, H. T. Chan, V. K. N. Lau, C. Y. Tsui, and H. C. Luong, "Design and Implementation of a Low-power Basebandsystem for RFID Tag," in 2007 IEEE International Symposium on Circuits and Systems, May 2007, pp. 1585–1588.

- [16] C. E. Cummings, "Simulation and Synthesis Techniques for Aynchronous FIFO Design," Synopsys Users Group (SNUG), pp. 1–23, 2002.

- [17] Y. C. Hung and H. J. Hung, "RFID design with CRC programmable capability, dual encode functions and dual modulation outputs," in 2010 International Symposium on Next-Generation Electronics, ISNE 2010 -Conference Program, 2010.

- [18] T. . Pei and C. Zukowski, "High-speed parallel CRC circuits in VLSI," IEEE Transactions on Communications, vol. 40, no. 4, pp. 653-657, April 1992.

[19] S. Jyothirmai Gali and S. Terlapu, "On the Implementation of VLSI

- Architecture of FM0/Manchester Encoding and Differential Manchester

- Coding for Short-Range Communications," *Proceedings of ICMEET* 2017, pp. 551–558, January 2018.

[20] K. Agarwal, R. Jegadeesan, Y. X. Guo, and N. V. Thakor, "Wireless Power Transfer Strategies for Implantable Bioelectronics," 2017.