Received May 4, 2019, accepted June 27, 2019, date of publication July 9, 2019, date of current version July 29, 2019.

Digital Object Identifier 10.1109/ACCESS.2019.2927514

# A Low-Power High-Speed Dynamic Comparator With a Transconductance-Enhanced Latching Stage

# YAO WANG<sup>10</sup>, (Member, IEEE), MENGMENG YAO<sup>1</sup>, BENQING GUO<sup>2</sup>, (Member, IEEE), ZHAOLEI WU<sup>3</sup>, WENBING FAN<sup>1</sup>, AND JUIN JEI LIOU<sup>10</sup>, (Fellow, IEEE)

<sup>1</sup>School of Information Engineering, Zhengzhou University, Zhengzhou 450001, China

<sup>2</sup>College of Communication Engineering, Chengdu University of Information Technology, Chengdu 610225, China

<sup>3</sup>Naneng Microelectronics Company Ltd., Chengdu 610000, China

Corresponding author: Yao Wang (ieyaowang@zzu.edu.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 61704022 and Grant 61871073, in part by the Science and Technology Project of Henan Province under Grant 0517, and in part by the Scientific Research Start-up Foundation of Zhengzhou University under Grant 32210904.

**ABSTRACT** Low-power, high-speed dynamic comparators are highly desirable in the design of highspeed analog-to-digital converters (ADC) and digital I/O circuits. Most dynamic comparators use a pair of cross-coupled inverters as the latching stage, which provides strong positive feedback, to accelerate the comparison and reduce the static power consumption. The delay of the comparator is mainly determined by the total effective transconductance of the latching stage. The delay not only limits the maximum operating frequency but also extends the period of the metastable state of the latching stage; hence, it increases energy consumption. However, at the beginning of the comparison phase, the conventional latching stage has two transistors with zero gate-to-source voltage, which degrade the total effective transconductance of the latching stage. In this paper, a novel low-power, high-speed dynamic comparator with a new latching stage is presented. The proposed latching stage uses separated gate-biasing cross-coupled transistors instead of the conventional cross-coupled inverter structure. The simple proposed latching stage improves its effective total transconductance at the beginning of the comparison phase, which leads to a much faster comparison and lowers energy consumption. The comparator is analyzed and compared to its prior type in terms of delay and power consumption via simulations and measurements. The experimental results demonstrate that the proposed comparator operates from a 1.2-V supply and consumes 110-fJ energy per comparison, with sampling speeds up to 2 GS/s.

**INDEX TERMS** Dynamic comparator, high-speed, low-power, two-stage comparator.

### I. INTRODUCTION

The latch-based dynamic comparator is a crucial module in analog-to-digital converters (ADC) [1]–[3], high-speed digital I/O circuits [4], memory sensing amplifiers [5] and analog built-in-self-testing (BIST) circuits [6]. Compared with static comparators, dynamic comparators utilize positive feedback and dynamic bias; therefore, have higher speed and lower static power consumption [7].

The conventional single-stage dynamic comparators directly stack the input transistors with the cross-coupled latch circuit; hence, they require large voltage headroom [8]. Moreover, they suffer from severe kickback noise introduced by the capacitive paths from the output nodes to the input nodes, and there is a challenging tradeoff between speed and power consumption. Several design techniques for lowvoltage, low-power dynamic comparators have been reported, including the charge-steering technique [9], techniques using body-driven transistors [10], and supply boosting methods [11]. As an alternative, the two-stage dynamic comparator topology employs a fully dynamic preamplifier as the input stage, which is separated from the latching stage [5]. This structure has less stacking, so it is more suitable for low-voltage operation. In addition, it reduces the kickback noise by providing additional shielding between the input and the output and enables independent optimization of the input stage (which mainly affects the offset) and latching stage (which mainly affects the speed). Several modified

The associate editor coordinating the review of this manuscript and approving it for publication was Xiaoguang Liu.

two-stage comparators have been reported to achieve faster speed and lower power consumption. In [12], positive feedback is introduced in the preamplifier of the two-stage comparator to strengthen the regeneration, which reduces the delay. However, it suffers from higher kickback noise than the conventional two-stage comparator. A common-mode insensitive dynamic comparator is presented in [13]. The latch is activated with an intentional delay to reduce power consumption. However, it suffers from a larger required area and higher kickback noise. The two-stage comparator in [14] employs a dynamic bias preamplifier, which only partially discharges the internal nodes and reduces the energy consumption. However, its delay is larger than that of the conventional structure. In [15], an additional positive feedback and a special clocking pattern are used in the preamplifier to improve the preamplifier gain.

All of the aforementioned dynamic comparators employ similar cross-coupled latching stages. In [16], we show that the delay and energy consumption can be greatly reduced by using a novel transconductance-enhanced latching stage. The proposed latching stage provides separated gate-biasing to the cross-coupled transistors, which improves the effective total transconductance at the beginning of the comparison phase; hence, it achieves higher speed and lower power consumption. In this paper, we present the detailed analysis of the novel two-stage dynamic comparator using the transconductance-enhanced latching stage. Various dynamic comparator circuits were designed and simulated in a 0.18- $\mu$ m CMOS process for comparison in terms of delay and power consumption. In addition, the proposed comparator was fabricated and measured, and the measured results verify that the proposed comparator operates from a 1.2-V supply and consumes 110 fJ per comparison with sampling speeds up to 2 GS/s.

The remainder of the paper is organized as follows. Section II presents the operation and delay analysis of the conventional two-stage comparators. The proposed comparator and design considerations are described in Section III. The simulation and measurement results are presented in Section IV, and the paper is concluded in Section V.

## II. CONVENTIONAL TWO-STAGE DYNAMIC COMPARATOR

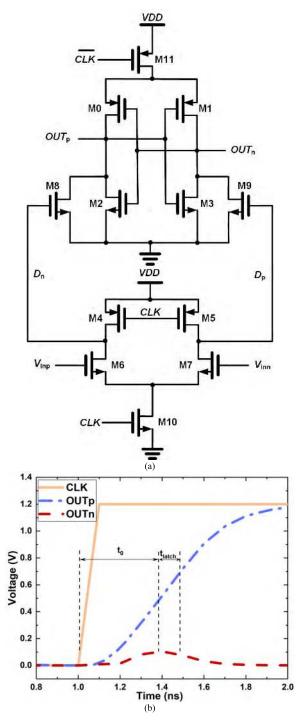

Fig. 1 presents the conventional two-stage dynamic comparator. It consists of a preamplifier stage and a latching stage. The low-tail current of the preamplifier stage is preferred to reduce the input offset voltage. The latching stage is usually optimized to have a large operational current to enhance the speed. The operation of the comparator is as follows. During the reset phase when CLK = 0, M4 and M5 are on, and M10 and M11 are off. Therefore, nodes  $D_n$  and  $D_p$  are charged to VDD, which causes nodes  $OUT_p$  and  $OUT_n$  to discharge to the ground through M8 and M9. In the comparison phase, when CLK = VDD, M10 and M11 are on, and M4 and M5 are off. Nodes  $D_n$  and  $D_p$  start to discharge with two different discharging currents, depending on the corresponding

**FIGURE 1.** (a) Conventional two-stage dynamic comparator and (b) its typical waveforms.

input voltage ( $V_{inn}$  and  $V_{inp}$ ). The voltage difference between  $D_n$  and  $D_p$  builds up the initial differential voltage at the output nodes ( $OUT_p$  and  $OUT_n$ ), which is further amplified by the strong positive feedback of the cross-coupled latching structure. The two-stage structure has several advantages, including lower kickback noise, better suitability for low-voltage operation and more flexible trade-off between speed and offset.

The delay of the comparator is defined as the time that the output difference takes to reach 0.5*VDD* and can be divided into two parts:  $t_0$  and  $t_{latch}$ , as shown in Fig. 1 (b).  $t_0$  is the period from the rising edge of *CLK*to the time when  $OUT_p$  and  $OUT_n$  are charged to  $V_{THN}$ . During this period, the pMOS transistors M0 and M1 are in the saturation region, while the nMOS transistors M2 and M3 are off. Therefore, the total transconductance of the latch is approximately equal to the transconductance of M0 and M1, and  $t_0$  can be calculated from (1).

$$t_{0} = \frac{V_{\text{THN}}C_{\text{OUT}}}{I_{\text{p}}} = \frac{V_{\text{THN}}C_{\text{OUT}} \cdot 2\mu_{\text{p}}C_{\text{OX}}\frac{w_{\text{p}}}{L_{\text{p}}}}{g_{\text{mp}}^{2}}$$

$$\approx \frac{V_{\text{THN}}C_{\text{OUT}} \cdot 2\mu_{\text{p}}C_{\text{OX}}\frac{w_{\text{p}}}{L_{\text{p}}}}{g_{\text{m,eff}}^{2}}$$

(1)

117

where  $C_{OX}$  is the gate oxide capacitance,  $\mu_p$  is the hole mobility,  $V_{THN}$  is the threshold voltage of M2 and M3,  $C_{OUT}$ is the load capacitance at the output nodes,  $I_p$  is the current that passes through M1,  $g_{mp}$  is the transconductance of the pMOS transistor M1,  $W_p$  and  $L_p$  are the channel width and length of M1, respectively.  $g_{m,eff}$  is the effective total transconductance of the inverter consisting of M1 and M3, and is given by

$$g_{\rm m,\,eff} = g_{\rm mp} + g_{\rm mn} \tag{2}$$

where  $g_{mn}$  is the transconductance of the nMOS device of the inverter. Since the nMOS transistor M3 is off during this period,  $g_{mn}$  is negligible.

The second part of the delay  $t_{latch}$ , which is defined as the time between the end of  $t_0$  and the time when the differential voltage of the output nodes reaches  $V_{DD}/2$ , is the latching delay of two cross-coupled inverters.  $t_{latch}$  is given by

$$t_{\text{latch}} = \frac{C_{\text{OUT}}}{g_{\text{m,eff}}} \cdot \ln \frac{\Delta V_{\text{out}}}{\Delta V_0} = \frac{C_{\text{OUT}}}{g_{\text{m,eff}}} \cdot \ln \frac{V_{\text{DD}}/2}{\Delta V_0}$$

(3)

where  $\Delta V_0$  is the initial voltage difference between the two output nodes at  $t = t_0$ . During this period, all the transistors of the cross-coupled inverters are turned on. Therefore, the effective total transconductance of the inverter can be expressed as

$$g_{m, eff} = g_{mp} + g_{mn} = \mu_p C_{OX} \frac{W_p}{L_p} \left( |V_{GSP}| - V_{THP} \right)$$

$$+ \mu_n C_{OX} \frac{W_n}{L_n} \left( V_{GSN} - V_{THN} \right)$$

(4)

The total delay of the comparator can be expressed as

$$t_{\text{delay}} = \frac{V_{\text{THN}}C_{\text{OUT}} \cdot 2\mu_{\text{p}}C_{\text{OX}}\frac{W_{1}}{L_{1}}}{g_{\text{m,eff}}^{2}} + \frac{C_{\text{OUT}}}{g_{\text{m,eff}}} \cdot \ln \frac{V_{\text{DD}}/2}{\Delta V_{0}}$$

(5)

Note that enhancing the total transconductance  $g_{m,eff}$  is an effective method to reduce the delay, particularly for  $t_0$  when the comparator first enters the comparison phase. However, for the conventional two-stage dynamic comparator, only the

pMOS transistors in the latch are on during  $t_0$ , so the nMOS transistors make no contribution to  $g_{m,eff}$ , which leads to a lower regeneration speed at the beginning of the comparison phase. Furthermore, this phenomenon causes a longer time of the metastable state of the cross-coupled inverters and results in higher energy consumption.

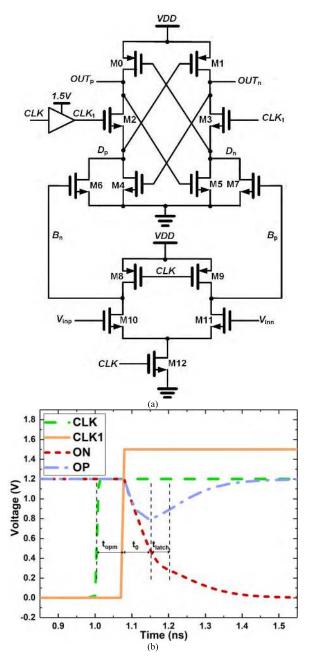

**FIGURE 2.** (a) Schematic of the proposed dynamic comparator and (b) its typical waveforms.

# **III. PROPOSED DYNAMIC COMPARATOR**

### A. CIRCUIT DESCRIPTION

Fig. 2 presents the schematic of our proposed dynamic comparator with a new latching stage and its typical waveforms.  $CLK_1$  is the level-shifted signal of CLK with 95 ps delay. In the reset phase, when CLK = 0, nodes  $B_n$  and  $B_p$  are charged to VDD, M6, M7, M0 and M1 are on, and M2 and M3 are off. Nodes  $D_n$  and  $D_p$  are discharged to ground via transistors M6 and M7, and nodes  $OUT_p$  and  $OUT_n$  are charged to VDDvia transistors M0 and M1.

In the reset phase, compared with other cross-coupled structures that bias only two transistors in the stronginversion region and leave the other two transistors in the cut-off region, all cross-coupled transistors M0, M1, M4 and M5 in the proposed regenerative structure are biased in the strong-inversion region. At the beginning of the comparison phase, as described below, the proposed regenerative stage has a much higher effective total transconductance than the conventional structure, which accelerates the regeneration speed. Furthermore, the faster comparison leads to a shorter metastable period of the cross-coupled inverters, which reduces the energy consumption.  $CLK_1$  is delayed by  $t_{\text{opm}}$  in purpose, so that M2 and M3 are turned on later to minimize the short current through M6 and M7 at the rising edge of CLK.

The delay of the proposed dynamic comparator is expressed as

$$t_{\rm delay} = t_{\rm opm} + t_0 + t_{\rm latch} \tag{6}$$

In the period of  $t_0$ ,  $OUT_p$  and  $OUT_n$  are discharged from *VDD*, while  $D_p$  and  $D_n$  are increasing from *GND*. Therefore, all transistors (M0-1 and M4-5) of the cross-coupled inverters are on and working in the triode region at first. The effective total transconductance of the latch is given by

$$g_{\rm m,eff} = g_{\rm mn} + g_{\rm mp} = \mu_{\rm n} C_{\rm OX} \left(\frac{W}{L}\right)_{\rm n} V_{\rm dsn} + \mu_{\rm p} C_{\rm OX} \left(\frac{W}{L}\right)_{\rm p} |V_{\rm dsp}| \qquad (7)$$

where  $V_{dsn}$  and  $V_{dsp}$  are the drain-to-source voltages of the nMOS and pMOS transistors in the latch, respectively. Equation (5) shows that  $g_{m,eff}$  linearly depends on the drain-to-source voltages of the transistors of the latch. After *CLK*<sub>1</sub> increases to *VDD*, switches M2 and M3 are turned on; hence,  $OUT_{p/n}$  are rapidly discharged to  $D_{p/n}$ , which causes a rapid increase in  $V_{dsn}$  and  $|V_{dsp}|$ . For the conventional cross-coupled latch, only pMOS transistors are on and working in the saturation region. Its  $g_{m,eff}$  is given by

$$g_{\rm m,eff} = g_{\rm mp} = \mu_{\rm p} C_{\rm OX} \left(\frac{W}{L}\right)_{\rm P} \left(|V_{\rm GSP}| - V_{\rm THP}\right) \qquad (8)$$

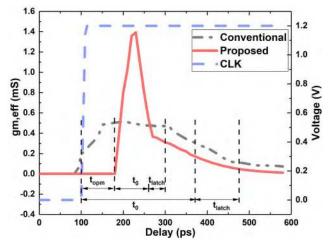

Therefore,  $g_{m,eff}$  of our proposed latch structure increases much faster than the conventional cross-coupled latch at the beginning of the comparison phase. Fig. 3 presents the transient simulation results of  $g_{m,eff}$  of the conventional and proposed two-stage dynamic comparators. For a fair comparison, both circuits are optimized to achieve an offset of approximately 7 mV, designed with similar transistor sizes of the latch circuit, and simulated with identical input signals. The effective total transconductance of the proposed structure increases much faster and higher than its counterpart,

**FIGURE 3.** Simulated  $g_{m,eff}$  of the conventional and proposed comparators.

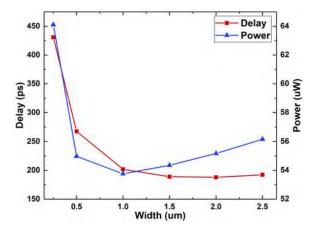

FIGURE 4. Simulated delay and power consumption of the proposed comparator versus the width of switches M2 and M3.

and its peak value is improved to approximately  $3\times$ . This advantage makes our proposed dynamic comparator achieves faster comparison, shorter period of the metastable state and lower energy consumption.

#### **B. DESIGN CONSIDERATIONS**

Some design issues must be considered in the design of the proposed comparator. The most unique part of this structure is the modified cross-coupled latch and associated switches M2-3. In the comparison phase, M2-3 are turned on, and the drain-to-source voltage of these switches must be minimized to enable a full discharge of the output nodes. Therefore, a pair of nMOS switches with a boosted control voltage is used. The boosted control voltage is set to be VDD + 0.3 V. Since the parasitic capacitance of M2-3 is a part of the load capacitance, a trade-off between switch-on resistance and parasitic capacitance must be considered. Fig. 4 shows the simulated delay and power consumption of the proposed comparator with different widths of switches M2-3. When the width of M2-3 is larger than 1  $\mu$ m, increasing the width cannot help to significantly reduce the delay but causes

higher power consumption. Therefore, we set the width of M2-3 to 1  $\mu$ m.

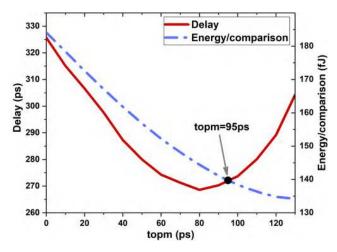

The control signal  $CLK_1$  is a boosted and delayed signal generated from CLK, and the delay between CLK and  $CLK_1$  is defined as  $t_{opm}$ , as previously mentioned. A shorter  $t_{opm}$  may lead to a higher short current through M6 and M7, whereas a longer  $t_{opm}$  may lead to a significant degradation of speed. The delay  $t_{opm}$  is determined by the transistor sizes of the level shifter in Fig. 2 (a). The delay and energy consumption with different  $t_{opm}$  is simulated, as shown in Fig. 5. We make a tradeoff between energy consumption and speed and set  $t_{opm}$ to 95 ps according to the simulation results.

FIGURE 5. Simulated delay and energy consumption versus topm.

| TABLE 1. | Transistor sizes | in the proposed | dynamic comparator. |

|----------|------------------|-----------------|---------------------|

|----------|------------------|-----------------|---------------------|

| Transistor ID | Size of transistor (µm) |  |  |

|---------------|-------------------------|--|--|

| M0-1          | 2/0.18                  |  |  |

| M2-3          | 1/0.18                  |  |  |

| M4-5          | 0.5/0.18                |  |  |

| M6-7          | 2/0.18                  |  |  |

| M8-9          | 1.8/0.18                |  |  |

| M10-11        | 4/0.18                  |  |  |

| M12           | 0.44/0.18               |  |  |

### **IV. EXPERIMENTAL RESULTS**

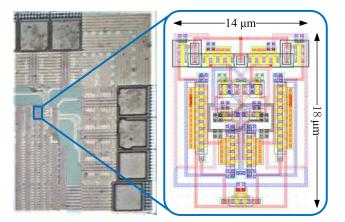

To compare the new and conventional double-tail comparators, all circuits were simulated in 0.18- $\mu$ m CMOS technology with 1.2 V supply voltage and 20 fF load capacitance. For a fair comparison, the transistor dimensions of the comparators were optimized to obtain an equal offset standard variation of 7 mV at an input common-mode voltage  $(V_{cm})$ of 1.1 V. The clock frequency was set at 500 MHz. The transistor sizes of the proposed comparator are presented in Table 1. To verify the low-power and high-speed feature of the proposed comparator, we also fabricated and measured the proposed comparator. The microphotograph and layout of the proposed comparator are shown in Fig. 6. The circuit was laid out in a fully symmetric fashion to avoid the static offset voltage caused by the layout mismatch. We used an Agilent E8267C Vector Signal Generator to generate the clock signal, and a Keysight 6626A Precision Power Supply to generate the

FIGURE 6. Microphotograph and layout of the proposed comparator.

**FIGURE 7.** (a) Postlayout simulated delay and (b) energy consumption versus  $V_{cm}$  (*VDD* = 1.2 V;  $V_{id}$  = 50 mV).

input voltages. The output of the comparator was measured by a Keysight DSO90254A Oscilloscope.

#### A. SIMULATION RESULTS

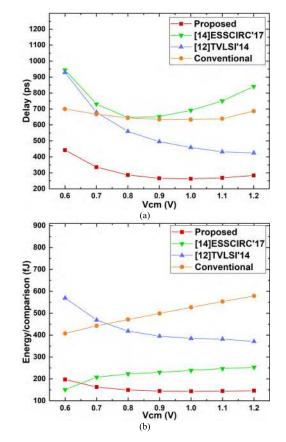

Figs. 7 (a) and (b) show the postlayout simulated delay and energy consumption versus  $V_{cm}$  at  $V_{id} = 50$  mV, respectively. The proposed comparator is faster than the others by more than 150 ps. Meanwhile, the energy consumption of the proposed comparator is comparable to that of the comparator in [14] and only approximately 30% of that of the conventional circuit and comparator in [12]. Since the proposed

**FIGURE 8.** (a) Postlayout simulated delay and (b) energy consumption versus *VDD* ( $V_{id} = 50$  mV;  $V_{cm} = VDD - 0.1$  V).

comparator uses a conventional input stage, the performance improvements are due to its novel latching stage.

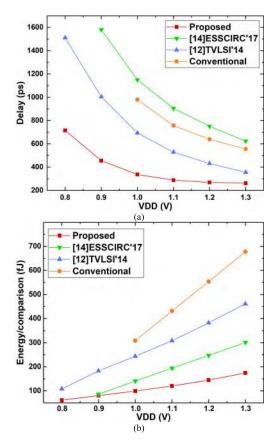

Fig. 8 (a) and (b) present the postlayout simulation results of the delay and energy consumption of the mentioned dynamic comparators versus the *VDD*variation at  $V_{id}$  = 50 mV and  $V_{cm} = VDD - 0.1$  V. Fig. 8 (a) shows that in comparison with the other three structures, the delay and energy consumption of the proposed dynamic comparator is significantly reduced in low-voltage supplies, which makes it more suitable for low-voltage low-power applications than the other structures. For example, the proposed comparator can operate with 0.8-V supply and 500-MHz sampling frequency at the cost of 55 fJ/conversion with 710 ps delay.

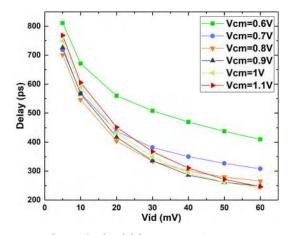

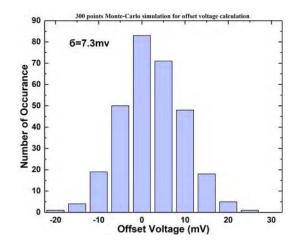

Fig. 9 depicts the dependence of the comparator delay on the differential input voltage at VDD = 1.2 V and multiple input common-mode voltages. The delay remains moderate and comparable for the input common-mode voltage in the range of 0.7–1.1 V. It decreases with the decrease in differential input voltage. Fig. 10 shows the standard deviation of the offset of the proposed comparator, which is 7.3 mV using Monte Carlo simulations for a run of 300 samples. Based on our simulation results, Table 2 presents the comparison between the proposed comparator achieves the smallest power consumption, delay, and area with the same offset budget and similar transistor sizing as its counterparts.

**FIGURE 9.** Postlayout simulated delay versus  $V_{id}$  (*VDD* = 1.2 V;  $V_{cm}$  = 0.7 V).

**FIGURE 10.** Monte Carlo simulation results of the offset in the proposed comparator.

**FIGURE 11.** Delay and energy consumption versus  $V_{cm}$  ( $V_{id} = 0.1$  V; VDD = 1.2 V; the operating frequency is 2 GHz).

### **B. MEASUREMENT**

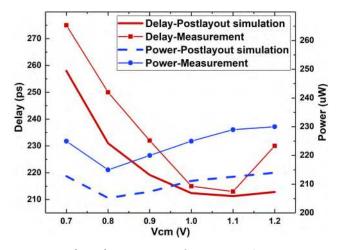

Fig. 11 presents the measured and simulated delay and power consumption at 2 GHz operating frequency and 0.1 V input differential voltage. In the input common-mode voltage range

#### TABLE 2. Performance comparison based on our simulations.

|                            | Conventional [5] | TVLSI'14 [12] | ESSCIRC'17 [14] | Proposed |

|----------------------------|------------------|---------------|-----------------|----------|

| Operating frequency (MHz)  | 500              | 500           | 500             | 500      |

| Average power( $\mu$ W)    | 276.62           | 190.88        | 123.51          | 72.2     |

| Delay(ps)                  | 638.91           | 431.74        | 750.13          | 268.6    |

| Estimated area $(\mu m^2)$ | 1407             | 877           | 541             | 252      |

| Offset(mV)                 | 7.11             | 7.26          | 7.25            | 7.3      |

#### TABLE 3. Comparison between the proposed comparator and other comparators.

|                                  | TCAS-I'13 | TVLSI'14 | Microelectron. J. '14 | EL'15 | TVLSI'18 | Proposed* |

|----------------------------------|-----------|----------|-----------------------|-------|----------|-----------|

|                                  | [18]*     | [12]†    | [17]†                 | [13]† | [15]*    |           |

| Supply voltage (V)               | 5         | 1.2      | 1                     | 1.2   | 1.8      | 1.2       |

| Maximum operating frequency (Hz) | 33.3 M    | 2.5 G    | 1G                    | 1.25  | 0.5 G    | 2 G       |

| Offset (mV)                      | 50.57 uV  | 7.8      | 11                    | 7.78  | 2        | 7.3†      |

| Area (µm <sup>2</sup> )          | 64000     | 392      | 180                   | -     | 530      | 252       |

| Energy per conversion (fJ)       | 23000     | 560      | 51                    | 480   | 460      | 112.5     |

| Technology (nm)                  | 500       | 180      | 180                   | 130   | 180      | 180       |

Measurement results.

<sup>†</sup>Simulation results.

**FIGURE 12.** Power consumption versus the operating frequency  $(V_{id} = 0.1 \text{ V}; VDD = 1.2 \text{ V};$  the operating frequency is 2 GHz).

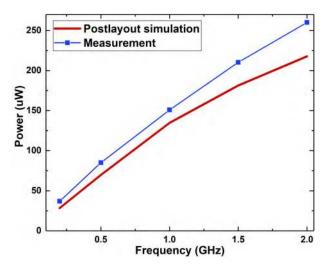

of 0.7-1.2 V, the delay is less than 275 ps, and the average power consumption is approximately 225  $\mu$ W. Fig. 12 shows the measured and simulated power consumption at different operating frequencies. The proposed comparator maintains the feature of low power consumption at different frequencies. The test results are basically consistent with the simulation results. Table 3 presents the performance comparison of the proposed and other dynamic comparators. The proposed comparator achieves a low-power behavior with high speed and small area. The dynamic comparator in [12] has a higher maximum operating frequency of 2.5 GHz (from simulation results), but its energy consumption is approximately  $5 \times$ higher than that of our proposed comparator. The comparator in [17] has lower energy consumption (from the simulation results) but suffers from a lower speed and a larger offset voltage.

#### **V. CONCLUSION**

We presented a new dynamic comparator with a novel transconductance-enhanced latching stage, which is suitable for low-power high-speed operation. The cross-coupled transistors in the proposed latch structure are biased in the strong inversion region during the reset phase, which improves the total effective transconductance of the latch at the beginning of the comparison phase and significantly decreases the delay and energy consumption. Postlayout simulations and measurement results confirm that the delay and energy consumption of the proposed comparator are strongly reduced compared to those of the conventional comparator structures. In addition, this simple structure is area-efficient and can work at a low supply voltage.

#### REFERENCES

- L. B. Leene and T. G. Constandinou, "A 0.016 mm<sup>2</sup> 12 b ΔΣS SAR with 14 fJ/conv. for ultra low power biosensor arrays," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 10, pp. 2655–2665, Oct. 2017.

- [2] K. Yoshioka, T. Sugimoto, N. Waki, S. Kim, D. Kurose, H. Ishii, M. Furuta, A. Sai, and T. Itakura, "28.7 A 0.7V 12b 160 MS/s 12.8 fJ/conv-step pipelined-SAR ADC in 28nm CMOS with digital amplifier technique," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 478–479.

- [3] C. Wulff and T. Ytterdal, "A compiled 9-bit 20-MS/s 3.5-fJ/conv.step SAR ADC in 28-nm FDSOI for Bluetooth low energy receivers," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1915–1926, Jul. 2017.

- [4] K. Huang, D. Luo, Z. Wang, X. Zheng, F. Li, C. Zhang, and Z. Wang, "A 190 mW 40 Gbps SerDes transmitter and receiver chipset in 65 nm CMOS technology," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2015, pp. 1–4.

- [5] D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18ps setup+hold time," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2007, pp. 314–605.

- [6] S. Lee, C. Shi, J. Wang, A. Sanabria, H. Osman, J. Hu, E. Sánchez-Sinencio, "A built-in self-test and *in situ* analog circuit optimization platform," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 10, pp. 3445–3458, Oct. 2018.

- [7] T. B. Cho and P. R. Gray, "A 10 b, 20 Msample/s, 35 mW pipeline A/D converter," *IEEE J. Solid-State Circuits*, vol. 30, no. 3, pp. 166–172, Mar. 1995.

- [8] B. Wicht, T. Nirschl, and D. Schmitt-Landsiedel, "Yield and speed optimization of a latch-type voltage sense amplifier," *IEEE J. Solid-State Circuits*, vol. 39, no. 7, pp. 1148–1158, Jul. 2004.

- [9] B. Razavi, "Charge steering: A low-power design paradigm," in Proc. Custom Integr. Circuits Conf. (CICC), Sep. 2013, pp. 1–8.

- [10] B. J. Blalock, H. W. Li, P. E. Allen, and S. A. Jackson, "Body-driving as a low-voltage analog design technique for CMOS technology," in *Proc. Southwest Symp. Mixed-Signal Design*, Feb. 2000, pp. 113–118.

- [11] A. Mesgarani, M. N. Alam, F. Z. Nelson, and S. U. Ay, "Supply boosting technique for designing very low-voltage mixed-signal circuits in standard CMOS," in *Proc. 53rd IEEE Int. Midwest Symp. Circuits Syst.*, Aug. 2010, pp. 893–896.

- [12] S. Babayan-Mashhadi and R. Lotfi, "Analysis and design of a low-voltage low-power double-tail comparator," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 22, no. 2, pp. 343–352, Feb. 2014.

- [13] J. Gao, G. Li, and Q. Li, "High-speed low-power common-mode insensitive dynamic comparator," *Electron. Lett.*, vol. 51, no. 2, pp. 134–136, Jan. 2015.

- [14] H. S. Bindra, C. E. Lokin, A.-J. Annema, and B. Nauta, "A 30fJ/comparison dynamic bias comparator," in *Proc. 43rd IEEE Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2017, pp. 71–74.

- [15] A. Khorami and M. Sharifkhani, "A low-power high-speed comparator for precise applications," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 26, no. 10, pp. 2038–2049, Oct. 2018.

- [16] Y. Wang, H. Yang, W. Fan, and J. J. Liou, "Low-power high-speed dynamic comparator using a new regenerative stage," in *Proc. IEEE Int. Conf. Electron Devices Solid State Circuits (EDSSC)*, Jun. 2018, pp. 1–2.

- [17] M. Hassanpourghadi, M. Zamani, and M. Sharifkhani, "A low-power lowoffset dynamic comparator for analog to digital converters," *Microelectron. J.*, vol. 45, no. 2, pp. 256–262, Feb. 2014.

- [18] J. Lu and J. Holleman, "A low-power high-precision comparator with timedomain bulk-tuned offset cancellation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 5, pp. 1158–1167, May 2013.

**BENQING GUO** received the B.Sc. degree from Zhengzhou University, China, in 2001, and the M.Sc. and Ph.D. degrees from the University of Electronic Science and Technology, China, in 2005 and 2011, respectively.

He was an RF Engineer with the UTstarcom Corporation and an RFIC Engineer with the East China Institute of Electronic Engineering, during the past years. Since 2014, he has been a Researcher with the University of Electronic Sci-

ence and Technology, China. He is also with the Chengdu University of Information Technology. From 2017 to 2018, he held a Visiting Scholar Position with the Microelectronic Research Group, Department of Electrical Computer and Biomedical Engineering, University of Pavia, Italy. He had over 40 publications of journals and conferences. His research interest includes CMOS RF/Analog integrated circuits and systems. He also served as a Technical Reviewer for almost 30 international journals and conferences, including the IEEE JOURNAL OF SOLID-STATE CIRCUITS, the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, the IEEE TRANSACTIONS IN KISTEMS I, the IEEE International Symposium on Circuits and Systems, and the IEEE International Midwest Symposium on Circuits and Systems.

**ZHAOLEI WU** received the B.S. degree from the University of Electronic Science and Technology of China, in 2007. He was a Senior Analog Engineer at Fujitsu. He is currently the Technical Director at Naneng Microelectronics Company Ltd., Chengdu, China. His research interests include high-speed SerDes and PLL.

**WENBING FAN** received the Ph.D. degree from the East China University of Science and Technology, Shanghai, China, in 2003. He is currently a Professor with the School of Information Engineering, Zhengzhou University, Zhengzhou, China. His current research interests include mixed signal circuits and embedded systems.

**YAO WANG** (M'16) was born in Henan, China, in 1983. He received the M.S. degree from Zhengzhou University, Zhengzhou, China, in 2009, and the Ph.D. degree from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2013.

From 2014 to 2017, he was a Lecturer with UESTC, then, he joined Zhengzhou University, where he has been an Associate Professor with the School of Information Engineering, since 2018.

His research interests include the IoT integrated circuits, low-power analog, and mixed-signal integrated circuits.

**MENGMENG YAO** received the B.S. degree from the Chongqing University of Technology, Chongqing, China, in 2018. She is currently pursuing the master's degree with Zhengzhou University, China. Her current research interest includes analog integrated circuit design.

JUIN JEI LIOU (F'11) received the B.S. (Hons.), M.S., and Ph.D. degrees in electrical engineering from the University of Florida, Gainesville, FL, USA, in 1982, 1983, and 1987, respectively.

He was with the School of EECS, University of Central Florida (UCF), from 1985 to 2011. Since 2016, he has been a Professor with the School of Information Engineering, Zhengzhou University, Zhengzhou, China. He has published 12 books, 2 book chapter, 280 journal papers, and

230 papers in international conference proceedings. His research interests include microelectronic reliability, modeling, and optimization for semiconductor devices.

Dr. Liou has been awarded 11 U.S. patents. He was named the UCF Pegasus Distinguished Professor, in 2009—the Highest Honor Bestowed to a Faculty Member at UCF. He received the IEEE Joseph M. Biedenbach Outstanding Engineering Educator Award, in 2004, and the IEEE Electron Devices Society Education Award, in 2014. His other honors are Fellow of IET, and a Chang Jiang Endowed Professor of the Ministry of Education, China—the Highest Honorary Professorship in China. He has served as the IEEE EDS Vice-President of Regions/Chapters, Treasurer, and Member of Board of Govern.