### A Low-Power Pipeline ADC with Front-End Capacitor-Sharing

by

Guangzhao Zhang

A thesis submitted in conformity with the requirements for the degree of Masters of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright  $\bigodot$  2012 by Guangzhao Zhang

#### A Low-Power Pipeline ADC with Front-End Capacitor-Sharing

Guangzhao Zhang

Master of Applied Science, 2012

Graduate Department of Electrical and Computer Engineering University of Toronto

### Abstract

This thesis presents the design and experimental results of a low-power pipeline ADC that applies front-end capacitor-sharing. The ADC operates at 20 MS/s, resolves 1.5 bits/stage, and is implemented in IBM  $0.13\mu$ m technology. The purpose of the technique is to reduce power consumption in the front-end S/H. This work is a proof-of-concept and it concentrates on the front-end design. A comparison is conducted between a capacitor-sharing ADC and a regular ADC and as a result, the technique reduces the power consumption in the front-end S/H by 39%. At an input frequency of 9.53 MHz and a sampling rate of 20 MS/s, the fabricated capacitor-sharing ADC consumes 4.7 mW at 1.2 V, and it achieves an ENOB of 8.5 bits and a FOM of 0.68 pJ/step. It has an ENOB as high as 8.67 bits at 0.4 MS/s and a FOM as low as 0.6 pJ/step when sub-sampling at 20 MS/s.

# Acknowledgements

There were many people who played a crucial role in contributing to the success of this work.

Firstly, this thesis would not have been possible without the continual guidance and support of my supervisor, Professor David Johns.

I am also very grateful to Karim Abdelhalim, Mike Bichan, Yunzhi (Rocky) Dong, Safeen Huda, Sadegh Jalali, Hamed Mazhab-Jafari, Bert Leesti, Mario Milicevic, Alireza Nilchi, Alain Rousson, Amer Samarah, Ioannis Sarkas, Shayan Shahramian, Ravi Shivnaraine, Colin Tse, Kentaro Yamamoto, Hemesh Yasotharan, and Meysam Zargham for their advice and technical support that helped me get past those seemingly insurmountable obstacles. A special thanks to Rocky, the BA5000 circuits guru, for the countless invaluable discussions we had.

To all the students of BA5000 and BA5158, I thank you for making my graduate experience a fun and enjoyable adventure that I will forever remember.

I would also like to thank Professor Glenn Gulak, Professor Wai Tung Ng, and Professor Sean Victor Hum for being on my defense committee.

Finally, I owe my deepest gratitude to Mandy and my family for their understanding and unquestioning support when I needed it the most.

# Contents

| 1        | Intr | oducti  | on                                           | 1  |

|----------|------|---------|----------------------------------------------|----|

|          | 1.1  | Thesis  | Objectives                                   | 1  |

|          | 1.2  | Thesis  | Outline                                      | 2  |

| <b>2</b> | Bac  | kgrour  | nd                                           | 3  |

|          | 2.1  | Pipelin | ne ADC                                       | 3  |

|          |      | 2.1.1   | Figure of Merit                              | 3  |

|          |      | 2.1.2   | One-Stage pipeline                           | 4  |

|          |      | 2.1.3   | 1-bit/Stage Pipeline                         | 6  |

|          |      | 2.1.4   | Digital Error Correction                     | 7  |

|          |      | 2.1.5   | 1.5-bit/Stage Pipeline                       | 11 |

|          |      | 2.1.6   | Sample and Hold                              | 12 |

|          |      | 2.1.7   | Thermal Noise and Scaling of Pipeline Stages | 13 |

|          | 2.2  | Survey  | v of Recently Published 10-bit Pipeline ADCs | 14 |

|          | 2.3  | Design  | Application and Target Specifications        | 14 |

| 3        | Pip  | eline A | DC Building Blocks and Design Methodology    | 17 |

|          | 3.1  | Opam    | p Design                                     | 17 |

|          |      | 3.1.1   | Gain                                         | 17 |

|          |      | 3.1.2   | Bandwidth                                    | 18 |

|          |      | 3.1.3   | Output Voltage Swing                         | 19 |

|          | 3.2 | Buildi  | ng Blocks                                 | 20 |

|----------|-----|---------|-------------------------------------------|----|

|          |     | 3.2.1   | Sub-ADC                                   | 21 |

|          |     | 3.2.2   | Sample and Hold                           | 22 |

|          |     | 3.2.3   | Multiplying DAC                           | 24 |

|          |     |         | 3.2.3.1 Flip-Around MDAC                  | 24 |

|          |     |         | 3.2.3.2 Integrator MDAC                   | 25 |

|          | 3.3 | Desigr  | Procedure                                 | 26 |

| 4        | Cap | oacitor | -Sharing Pipeline Design and Simulation   | 30 |

|          | 4.1 | Front-  | End Capacitor-Sharing                     | 30 |

|          | 4.2 | Power   | Comparison                                | 34 |

|          |     | 4.2.1   | Regular versus Capshare ADC               | 35 |

|          |     | 4.2.2   | Analysis                                  | 36 |

|          |     |         | 4.2.2.1 Initial Assumptions               | 36 |

|          |     |         | 4.2.2.2 Choosing the Sampling Capacitance | 36 |

|          |     |         | 4.2.2.3 Two-Stage Opamp Design            | 37 |

|          |     |         | 4.2.2.4 Conclusions                       | 39 |

|          | 4.3 | Circui  | t Implementation                          | 40 |

|          |     | 4.3.1   | General Description                       | 40 |

|          |     | 4.3.2   | Two-Stage Opamp                           | 41 |

|          | 4.4 | Schem   | atic Simulations                          | 44 |

| <b>5</b> | Exp | perime  | ntal Results                              | 48 |

|          | 5.1 | Test S  | etup                                      | 48 |

|          | 5.2 | Exper   | imental Data                              | 49 |

|          |     | 5.2.1   | Measurement Results                       | 49 |

|          |     | 5.2.2   | Differential and Integral Non-Linearity   | 54 |

|          |     | 5.2.3   | Conclusions                               | 56 |

|   | 5.3        | Dynamic Range Degradation | 56 |  |

|---|------------|---------------------------|----|--|

| 6 | Cor        | nclusions and Future Work | 60 |  |

|   | 6.1        | Conclusions               | 60 |  |

|   | 6.2        | Future Work               | 61 |  |

| R | References |                           |    |  |

# **List of Tables**

| 2.1 | Previous 10-bit pipeline ADCs                                                                   | 15 |

|-----|-------------------------------------------------------------------------------------------------|----|

| 2.2 | Design specifications targeted for this work                                                    | 16 |

| 4.1 | Power of capshare pipeline ADC                                                                  | 38 |

| 4.2 | Power of regular pipeline ADC                                                                   | 39 |

| 4.3 | Transistor sizes in $W/L \ [\mu m/\mu m]$ within capshare ADC opamps                            | 42 |

| 4.4 | Transistor sizes in $W/L \ [\mu m/\mu m]$ within regular ADC opamps                             | 43 |

| 4.5 | $A\beta$ , phase margin, and $f_{3dB}$ of opamp closed-loop circuits in capshare ADC            | 43 |

| 4.6 | $A\beta$ , phase margin, and $f_{3dB}$ of opamp closed-loop circuits in regular ADC             | 43 |

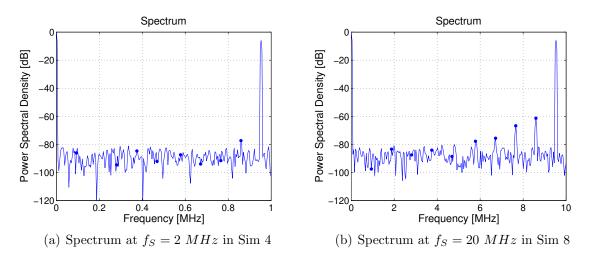

| 4.7 | SNDR and SNR at $fin = 61/128 \cdot f_S$                                                        | 44 |

| 4.8 | Power consumption of capshare versus regular ADC at $f_S=2\ MHz$                                | 46 |

| 4.9 | Power consumption of capshare versus regular ADC at $f_S=20\ MHz$                               | 47 |

| 5.1 | List of input/output pins for the DUT $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 51 |

| 5.2 | Experimental results of capshare ADC measured at different $f_{in} \mbox{ and } f_S \ .$        | 51 |

| 5.3 | Comparing this work to other 1.5-bit/stage 10-bit pipeline ADCs $~$                             | 56 |

| 5.4 | SNDR and SNR at $f_{in} = 61/128 \cdot f_S$ after post-layout extraction                        | 57 |

# **List of Figures**

| 2.1 | One-stage pipeline ADC                                                                        | 5  |

|-----|-----------------------------------------------------------------------------------------------|----|

| 2.2 | Ten-stage pipeline ADC that resolves 1-bit/stage                                              | 7  |

| 2.3 | Transfer function of a 1-bit MDAC                                                             | 8  |

| 2.4 | Transfer function of a 1-bit MDAC with comparator offset $\ldots$                             | 9  |

| 2.5 | Transfer function of a 1.5-bit MDAC                                                           | 10 |

| 2.6 | Transfer function of a 1.5-bit MDAC with comparator offset $\ . \ . \ . \ .$                  | 11 |

| 2.7 | A 10-bit 1.5-bit/stage pipeline ADC with digital error correction                             | 12 |

| 2.8 | Digital error correction in a 1.5-bit/stage 10-bit pipeline ADC $\ldots$ .                    | 12 |

| 2.9 | General block diagram for a wireless radio receiver                                           | 15 |

| 3.1 | Single-stage opamp with gain-boosting                                                         | 19 |

| 3.2 | Two-stage opamp with a folded-cascode and a common source stage                               | 20 |

| 3.3 | Three-level sub-ADC                                                                           | 21 |

| 3.4 | Charge distribution comparator                                                                | 21 |

| 3.5 | A commonly used S/H                                                                           | 22 |

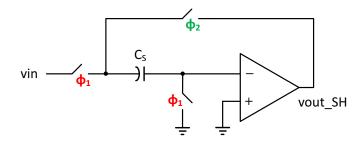

| 3.6 | Clock waveform with phases $\Phi_1$ and $\Phi_2$ labeled $\ldots \ldots \ldots \ldots \ldots$ | 23 |

| 3.7 | Flip-around MDAC                                                                              | 25 |

| 3.8 | Integrator MDAC                                                                               | 26 |

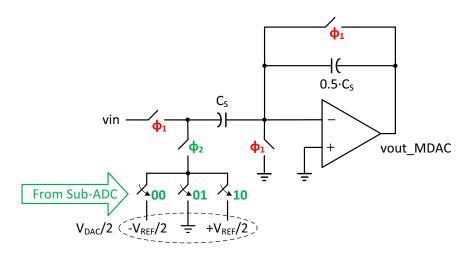

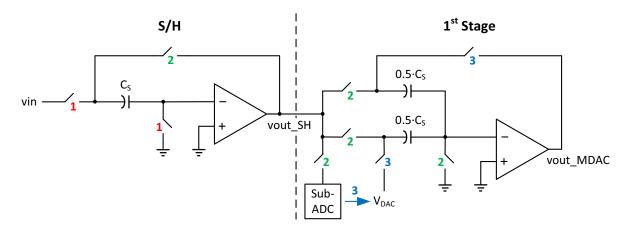

| 4.1 | Front-end S/H and first stage flip-around MDAC $\ldots \ldots \ldots \ldots \ldots$           | 31 |

| 4.2 | Front-end S/H and first stage integrator MDAC                                                 | 32 |

|     |                                                                                               |    |

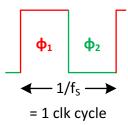

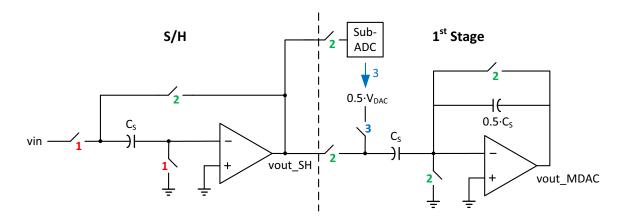

| 4.3  | Front-end S/H sharing Cs with first stage MDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

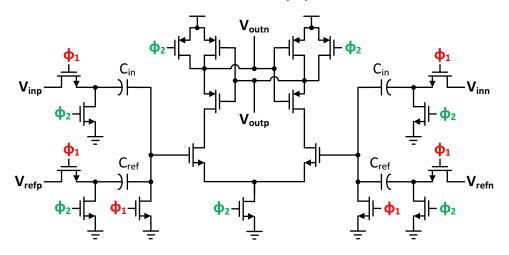

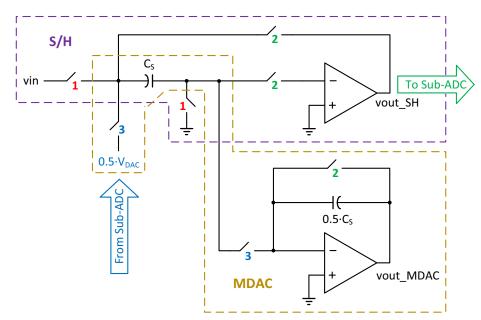

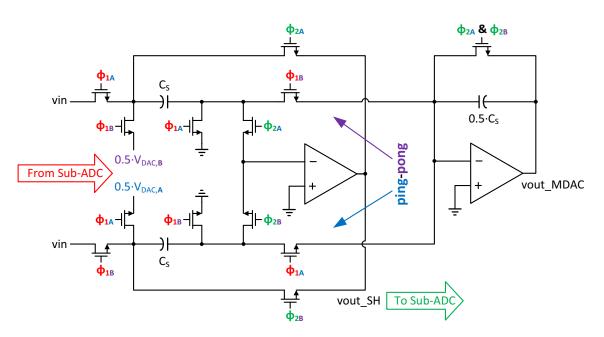

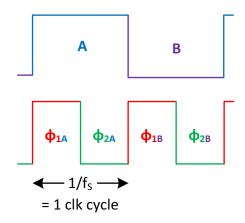

| 4.4  | Capacitor-sharing front-end with ping-pong scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33 |

| 4.5  | Clock waveform with clock cycle phases and ping-pong phases labeled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

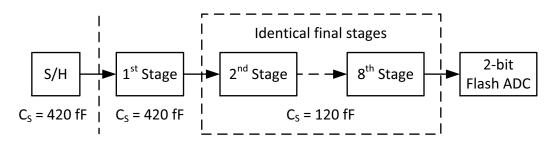

| 4.6  | Regular pipeline ADC with a flip-around MDAC in the first stage $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

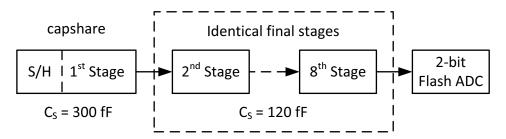

| 4.7  | Pipeline ADC with capacitor-sharing front-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

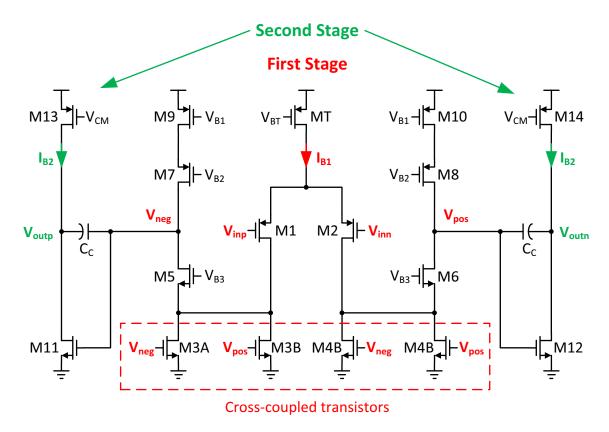

| 4.8  | Two-stage opamp with with CMFB on second stage only $\hdots \hdots \hdo$ | 42 |

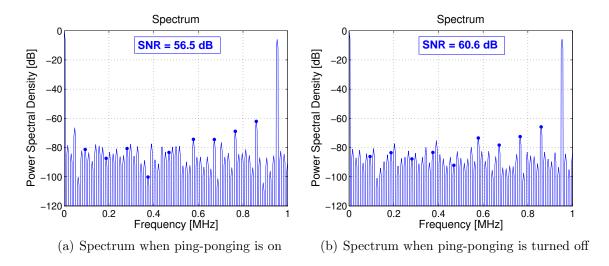

| 4.9  | Spectrum of Simulations 4 and 8 in Table 4.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46 |

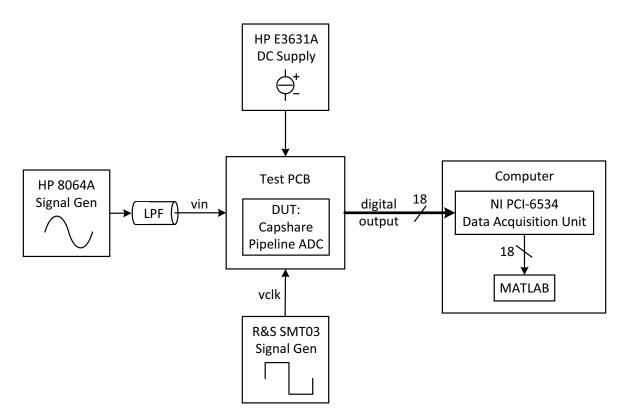

| 5.1  | Test setup for capshare pipeline ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49 |

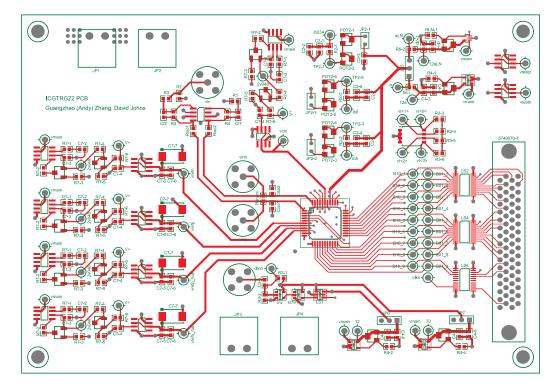

| 5.2  | PCB used to test capshare pipeline ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50 |

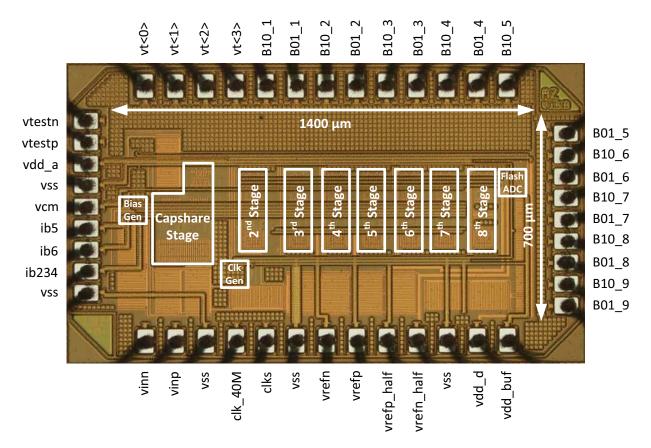

| 5.3  | Die micrograph of pipeline ADC with front-end capacitor-sharing $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 |

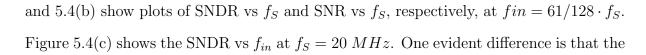

| 5.4  | Comparison of simulated and measured SNDR and SNR $\ .\ .\ .\ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52 |

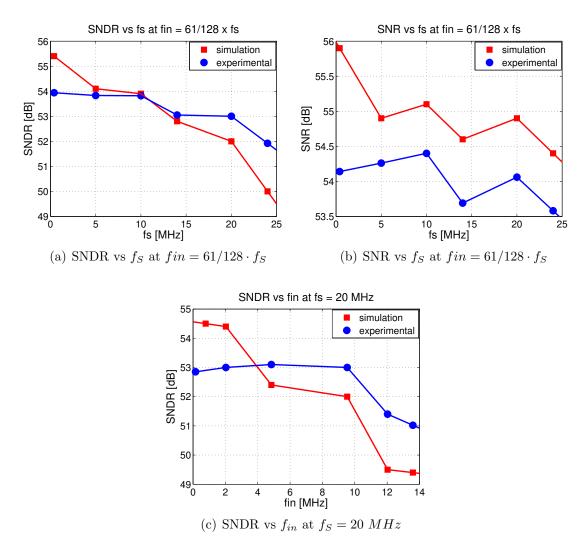

| 5.5  | Spectrum and SNDR vs Input Level at $f_{in} = 9.53 \ MHz$ and $f_S = 20 \ MHz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53 |

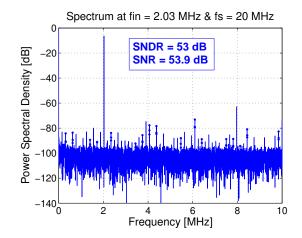

| 5.6  | Spectrum at $f_{in} = 2.03 \ MHz$ and $f_S = 20 \ MHz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54 |

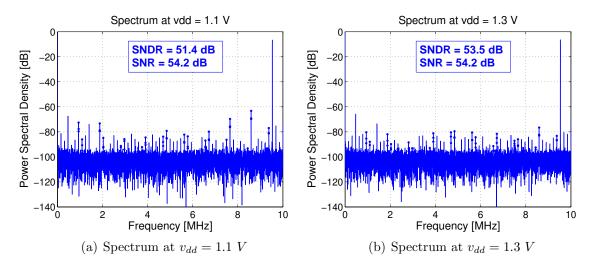

| 5.7  | Spectrums at $f_{in} = 9.53 \ MHz$ and $f_S = 20 \ MHz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |

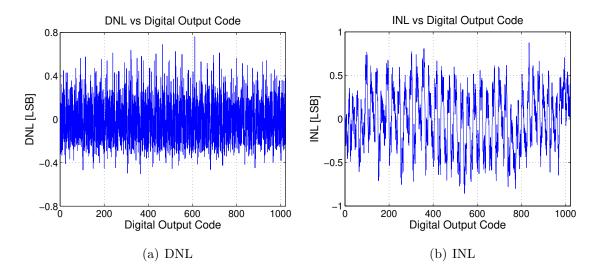

| 5.8  | DNL and INL using histogram test at $fin = 2.03 \ MHz$ and $f_S = 20 \ MHz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55 |

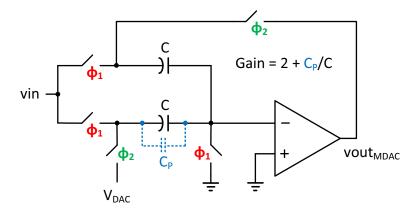

| 5.9  | MDAC gain error caused by parasitics across sampling capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57 |

| 5.10 | Spectrum of Simulations 5 and 6 in Table 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

# List of Acronyms

**ADC** Analog to Digital Converter

${\bf BPF}\,$  Band-Pass Filter

${\bf capshare} \ {\bf capacitor}{\rm -sharing}$

${\bf CM}\,$  Common-Mode

${\bf CMFB}\,$  Common-Mode Feedback

**DAC** Digital to Analog Converter

${\bf DEC}\,$  Digital Error Correction

**DNL** Differential Non-Linearity

**DSP** Digital Signal Processing

$\mathbf{DUT}$  Device Under Test

**ENOB** Effective Number of Bits

${\bf FFT}$  Fast Fourier Transform

FOM Figure of Merit

${\bf GBW}\,$ Gain Bandwidth

**INL** Integral Non-Linearity

LNA Low-Noise Amplifier

LPF Low-Pass Filter

**LSB** Least Significant Bit

**MDAC** Multiplying Digital to Analog Converter

**MIM** Metal Insulator Metal

${\bf MSB}\,$  Most Significant Bit

MS/s Mega Samples per Second

NMOS N-type Metal Oxide Semiconductor

PCB Printed Circuit Board

**PMOS** P-type Metal Oxide Semiconductor

**PSD** Power Spectral Density

${\bf RF}\,$  Radio Frequency

S/H Sample and Hold

${\bf SR}\,$  Slew Rate

**SNDR** Signal to Noise and Distortion Ratio

**SNR** Signal to Noise Ratio

$\mathbf{T}/\mathbf{H}$  Track and Hold

VGA Variable Gain Amplifier

WLAN Wireless Local Area Network

# Chapter 1

# Introduction

### 1.1 Thesis Objectives

The front-end Sample and Hold (S/H) in a pipeline Analog to Digital Converter (ADC) typically makes up a large portion of total power consumption. This has motivated research into reducing the power consumption of this power-hungry block. For instance, [1] embeds the S/H within the first stage of the pipeline ADC. This thesis presents a novel front-end capacitor-sharing (capshare) technique that significantly reduces the power consumption in the front-end S/H. The technique is demonstrated in a 10-bit pipeline ADC that resolves 1.5 bits/stage. The goal of this thesis is a proof-of-concept of the technique and hence, it concentrates on the front-end design and not on attaining the best raw performance. The objectives of this thesis are as follows:

- Provide a background on pipeline ADCs.

- Introduce a novel front-end capshare technique that saves power in the front-end S/H.

- Show the theoretically power savings of the technique through a design comparison.

• Demonstrate via simulations and experimental results that the technique achieves the expected performance.

### 1.2 Thesis Outline

The next chapters in this thesis are organized as follows:

- Chapter 2 provides a background on pipeline ADCs.

- Chapter 3 presents the building blocks and the design methodology for pipeline ADCs. Then, an example design is done using the principles discussed in the chapter.

- Chapter 4 conducts the design of a pipeline ADC with front-end capshare and a regular pipeline ADC. Their theoretical and simulated performance is compared.

- Chapter 5 shows the experimental results of the capshare ADC fabricated in IBM 0.13 μm technology and analyzes a dynamic range issue through post-layout simulations.

- Chapter 6 summarizes the main conclusions and discusses the potential areas for future work.

# Chapter 2

# Background

This chapter introduces the pipeline ADC. Section 2.1 presents background material on pipeline ADCs, Section 2.2 provides a brief survey of previous work, and Section 2.3 describes the application and design specifications of this work.

### 2.1 Pipeline ADC

This section presents background material on pipeline ADCs.

### 2.1.1 Figure of Merit

An ADC quantizes an analog input signal into a digital output at a specific conversion resolution and accuracy. The resolution is equal to the number of bits, N, that are resolved, while the accuracy refers to how precise the output bits represent the input. The accuracy is typically measured in terms of Signal to Noise and Distortion Ratio (SNDR), which is the ratio of signal power to noise and distortion power, or alternatively in Effective Number of Bits (ENOB):

$$ENOB = \frac{SNDR - 1.76}{6.02} \ [bits]$$

(2.1)

The noise power in the system comes from quantization noise, the conversion limit set by the resolution, and random noise (e.g. thermal noise). Inaccuracies in the ADC's physical components will appear in the output as distortion power. If an ADC is designed with perfectly accurate components, the distortion power is zero and the conversion accuracy is limited by the Signal to Noise Ratio (SNR) or the dynamic range. Dynamic range is the ratio of the maximum signal power to noise power. If all sources of random noise is below the N-bit level, the dynamic range is limited by the quantization limit set by the resolution. In general, ADCs are quantitatively compared using a Figure of Merit (FOM) defined by:

$$FOM = \frac{P_{total}}{2^{ENOB} \cdot 2f_{in}} \quad [pJ/step]$$

(2.2)

$P_{total}$  is the total power consumed by the system and  $f_{in}$  is the frequency of the input signal. There are many types of ADCs, each suitable for different accuracies and conversion rates as discussed in [2]; however, this thesis will concentrate on the pipeline ADC.

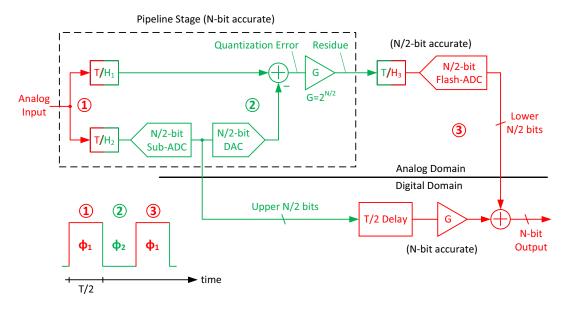

#### 2.1.2 One-Stage pipeline

A pipeline ADC is a type of switched-capacitor circuit that divides the quantization of an input signal into multiple steps. It does this by distributing the conversion over multiple stages so that each stage converts only a subset of the total number of bits, N. Pipeline ADCs are more power efficient than ADCs that quantize in only one step, like a flash ADC. Typically, the pipeline stages function in a two-step or two-phase cycle. To demonstrate this, Figure 2.1 shows a basic one-stage N-bit pipeline ADC. The flash-ADC inside the pipeline stage is called a sub-ADC as not to get mixed-up with the final flash-ADC. In the first half cycle (T/2), the ADC is in phase 1,  $\Phi_1$ , and Track and Hold (T/H)  $T/H_1$  and  $T/H_2$  track the analog input. At the end of the half cycle,  $T/H_1$ and  $T/H_2$  sample the input. In the second half cycle, the ADC is in phase 2,  $\Phi_2$ , and  $T/H_1$  and  $T/H_2$  output the voltages they sampled for the sub-ADC and summer block. The sub-ADC takes the input and quantizes it create the upper N/2 bits, which is the

Figure 2.1: One-stage pipeline ADC

digital output of the pipeline stage. The upper N/2 bits are referred to as the Most Significant Bit (MSB)s. The MSBs are immediately converted back into an analog signal via the Digital to Analog Converter (DAC), which gets subtracted from the original analog input in the summer block to produce the quantization error for the conversion. The quantization error is then amplified by the stage gain,  $G = 2^{N/2}$ , to bring the voltage swing back to the input range. The output of the stage gain is called the residue output and is the analog output of the pipeline stage. At the end of the second half cycle,  $T/H_3$ samples the residue output. In the third and final half cycle, the ADC is back in  $\Phi_1$ .  $T/H_3$  outputs the residue signal and the final flash-ADC quantizes it to create the lower N/2 bits. The lower N/2 bits are referred to as the Least Significant Bit (LSB)s. The MSBs, which are held in the digital domain so that they are available during this half cycle, are digitally scaled by the gain, 'G', to bring them to the correct magnitude, and combined with the LSBs to create a N-bit digital output. The input signal sampled in the first half cycle has now been converted. While this is happening at the end of the pipeline ADC,  $T/H_1$  and  $T/H_2$  track the next analog input and sample it at the end of the third half cycle. The process then repeats itself.

Ideally, the N-bit digital output should be be accurate to N bits (i.e. the ADC has an ENOB of 10-bits) as that would ensure the ADC is perfectly linear and not missing any conversion codes [3]. The analog and digital components in Figure 2.1 must be accurate to at least a certain number of bits to ensure N-bit accuracy. In the analog domain, all the components in the pipeline stage must be N-bit accurate to ensure the MSBs are N-bit accurate and the residue output settles to a value accurate to N bits.  $T/H_3$  and the final flash-ADC must be N/2-bit accurate to ensure the LSBs are accurate to N/2 bits. In the digital domain, the T/2 delay, gain 'G', and summer should be N-bit accurate as they process and generate data accurate to N bits. The main design challenge is meeting the accuracy requirements in the analog domain. If the accuracy requirements are not met, there will be distortion in the digital output that limits the ADC's ENOB to below N bits.

In general, a pipeline stage outputs a sub-set of the total number of output bits and a residue signal, which are its digital and analog outputs respectively.

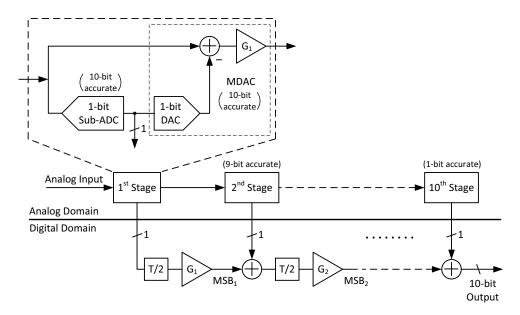

#### 2.1.3 1-bit/Stage Pipeline

The procedure in Section 2.1.2 can be extended to multiple pipeline stages. Figure 2.2 shows a 10-bit pipeline ADC that resolves 1-bit per stage. Within the pipeline stage,  $T/H_1$  and  $T/H_2$  are integrated into the summer and sub-ADC respectively. The process in the analog domain is very similar to that of the one-stage pipeline. Starting from the first stage, the input signal is sampled by the sub-ADC and the summer. Next, the sub-ADC generates a 1-bit output. It immediately gets converted back into an analog voltage so it can be subtracted from the input sample to generate the quantization error. The quantization error is then amplified by the stage gain ( $G_i = 2$ ) to bring it back to the input range, which produces the residue output for the next stage. The next stage and every stage afterwards repeat the cycle until all 10-bits are generated. The accuracy requirement in the first pipeline stage is the same as in the one-stage pipeline; however,

Figure 2.2: Ten-stage pipeline ADC that resolves 1-bit/stage

the accuracy requirement in every subsequent stage decreases by one bit. This is further discussed in Section 2.1.7.

Digital circuitry in the digital domain processes the digital bits as it is outputted from each pipeline stage. As a single bit is generated by each subsequent stage every T/2, it is added to  $MSB_i$  generated previously. The sum is delayed by T/2 and the delayed sum gets scaled by the stage gain of the corresponding pipeline stage to generate the next  $MSB_{i+1}$ . This process ensures that, in the end, each bit has the correct magnitude weighting and all 10 bits corresponding to a specific input sample are aligned in time.

Because the first input sample must propagate through the pipeline before the first 10-bit output is generated, each stage contributes T/2 of latency to the pipeline ADC. After the first digital output is generated, a new output is generated every clock cycle, T. Thus, the conversion rate or sampling speed of a pipeline ADC,  $f_S = 1/T$ , is limited by the delay through a single pipeline stage.

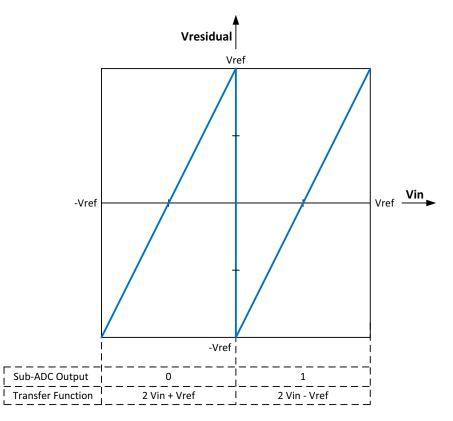

#### 2.1.4 Digital Error Correction

This section presents a technique called Digital Error Correction (DEC) [4] that reduces the accuracy requirement in the sub-ADC. When building a pipeline stage, typically the DAC, summer block, and stage gain are combined into a single block called a Multiplying Digital to Analog Converter (MDAC). In a two phase process, the MDAC samples the input in the first phase and uses the digital bit(s) from the sub-ADC to generate the residue signal in the second phase. Figure 2.3 shows the transfer function of a 1-bit MDAC, which is used in the 10-bit pipeline ADC in Figure 2.2. The analog input has a

Figure 2.3: Transfer function of a 1-bit MDAC

maximum range defined from  $-V_{ref}$  to  $V_{ref}$ , which is referred to as the full-scale range. Due to the stage gain, the residue signal will also span this full-scale range.  $V_{ref}$  is the reference voltage of the ADC. The 1-bit sub-ADC, which is simply a single comparator, generates the digital output for the pipeline stage and tells the MDAC whether the input is greater or less than zero. Using this information, the MDAC applies the corresponding residue transfer function. However, typically the comparator will have some threshold offset. Figure 2.4 shows the transfer function of a 1-bit MDAC when there is a threshold offset in the comparator. An offset results in the residue voltage exceeding the full-scale

Figure 2.4: Transfer function of a 1-bit MDAC with comparator offset

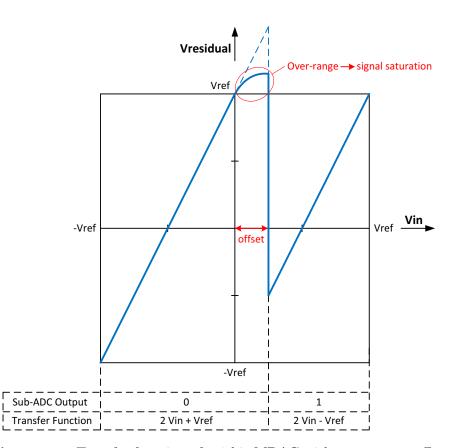

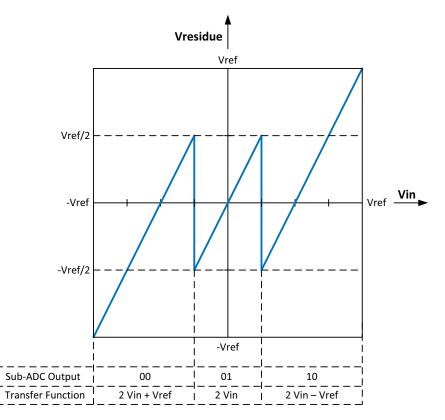

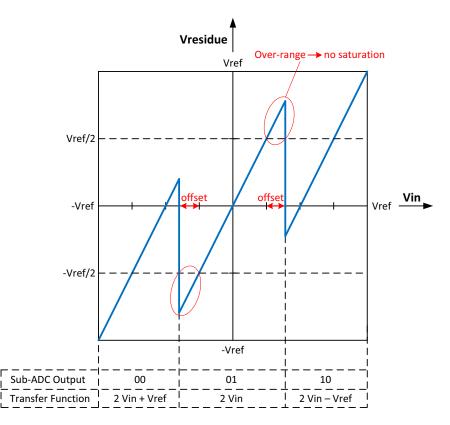

range. Consequently, the residue output saturates and no longer follows the transfer function. This is because the stage gain is implemented by an opamp in a closed-loop circuit and this circuit has a maximum voltage swing equal to the full-scale range. Section 3.1.3 will discuss this further. Because the residue is not accurately passed onto the next stage, the pipeline has significantly reduced conversion accuracy. To maintain N-bit accuracy, the sub-ADC in the first pipeline stage must have an accuracy of N bits. That is to say, for a 10-bit pipeline with  $V_{ref} = 0.8 V$ , the comparator must have a threshold accurate to less than 2 mV. This is very difficult to achieve. A technique called DEC greatly reduces the accuracy requirement of the sub-ADC. Figure 2.5 shows the transfer function of a 1.5-bit MDAC that applies DEC. A 1.5-bit sub-ADC quantizes the input

Figure 2.5: Transfer function of a 1.5-bit MDAC

to 3-levels and the residue is limited to half the full-scale range. If comparator threshold offsets cause the residue signal to fall outside it's normal range, the residue signal will be accurately passed onto the next stage provided the offset is within  $\pm V_{ref}/4$ . Figure 2.6 demonstrates this by showing the transfer function of a 1.5-bit MDAC when there are threshold offsets in the sub-ADC. The additional bit from each adjacent stage is

Figure 2.6: Transfer function of a 1.5-bit MDAC with comparator offset

overlapped to correct the over-range error. The fourth level is removed because the MDAC only needs to indicate whether the residue output is above or below Vref/2 and therefore, there is technically only an overlap of half a bit. As a result, the accuracy of the 1.5-bit sub-ADC is reduced from N to 2 bits with DEC. In general, with DEC, the accuracy of the sub-ADC can be reduced if fewer bits are resolved in each stage.

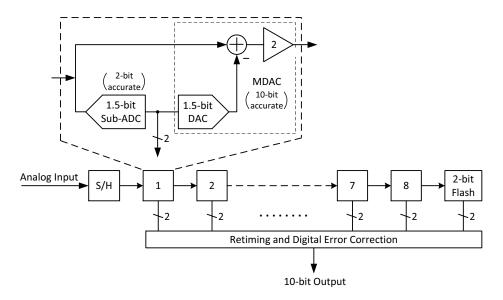

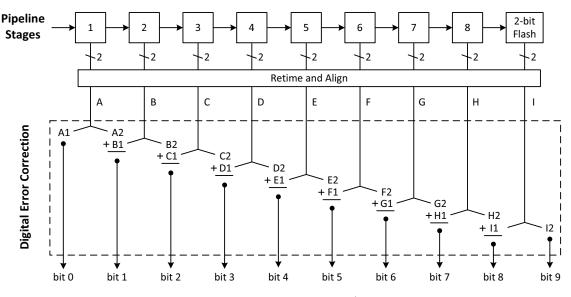

#### 2.1.5 1.5-bit/Stage Pipeline

DEC is a very popular technique because it significantly reduces the accuracy requirements of the sub-ADC. Figure 2.7 shows a more practical version of the pipeline ADC in Figure 2.2. The pipeline ADC applies DEC and consists of a front-end S/H, 8 pipeline stages, and a 2-bit flash ADC at the end. Each pipeline stage resolves 1.5 bits, which is

Figure 2.7: A 10-bit 1.5-bit/stage pipeline ADC with digital error correction

represented by a 2-bit output. In the end, a total of 18-bits are generated from a single input sample. To apply DEC, the bits from each adjacent pipeline stage overlap by half a bit and form the expected 10-bit output. This is demonstrated in Figure 2.8.

Figure 2.8: Digital error correction in a 1.5-bit/stage 10-bit pipeline ADC

#### 2.1.6 Sample and Hold

As shown in Figure 2.7, a T/H is typically placed before the first stage. It is called a S/H to avoid confusion with the T/Hs discussed previously. The S/H needs to be

accurate to N bits so that it can provide the first stage with an input signal accurate to N bits. The function of the S/H is to ensure that, in the first stage, the sub-ADC and the MDAC sample the same input voltage. Typically the sampling capacitors in the MDAC are much larger than those in the sub-ADC. Therefore, if both were tracking and sampling a changing input signal, the MDAC would always lag the sub-ADC and thus sample a different voltage. For lower input signal frequencies, a pipeline ADC can function without a S/H since the input is changing slow enough for the sub-ADC and MDAC to sample the same value. However, a S/H is typically needed when the ADC is sampling high-frequency input signals, such as when the ADC is sub-sampling. Subsampling is where a pipeline ADC is sampling an input that has spectral content above it's Nyquist frequency. The signal frequency above the Nyquist rate gets aliased back into the in-band region, which is from DC to half the sampling frequency  $f_S/2$ . Once the signal is quantized, it spectral location is lost in the digital domain as there are many possible bands it could have originated from. However, if you limit the input frequencies to within a known region of half the sampling frequency, the in-band region will then correspond to only one possible band. Hence, the signal can be identified exactly in the digital domain.

#### 2.1.7 Thermal Noise and Scaling of Pipeline Stages

The total input-referred noise referenced at the input of the front-end S/H is typically used to evaluate the thermal noise level of a pipeline ADC. Once formulated, it will be a combination of kT/C terms where k is the Boltzmann's constant, T is the operating temperature, and C is one of the capacitors used in the analog to digital conversion (such as the sampling capacitor). Therefore, increasing C will decrease the thermal noise level and increase the dynamic range of the ADC. However, the opamps are the devices that must drive this capacitance and thus increasing C also increases the power consumed by the opamps. Moreover, since opamps consume most of the system power, increasing C significantly increases the power consumption of the entire system. Therefore, it is sub-optimal to increase C unnecessarily. Generally, setting the thermal noise level to just above the 10-bit level is done to maximize the dynamic range.

Input-referring the output noise of a gain block reduces the noise power by the square of the gain. Therefore, the effect of thermal noise originating further down the pipeline is reduced by each stage gain that is passed. For example, suppose each pipeline stage is identical and has a stage gain of two, then the contribution of noise at the output of the first stage is four times more than the contribution at the output of the second stage. Similarly, other sources of error that originate further down the pipeline have a reduced effect on total accuracy. This is why the accuracy requirement of the pipeline stages in Figure 2.2 can decrease along the pipeline. Similarly, in the 1.5-bit/stage pipeline ADC in Figure 2.7, the accuracy requirement of the MDAC decreases by one bit as you go down the pipeline. As a result, the power consumption and design complexity of the pipeline stage can be scaled. Once the pipeline has been scaled for optimal power consumption, the front-end dominates total power consumption. This is why the front-end S/H makes up a large portion of total power consumption. If the number of bits resolved per stage is increased, the subsequent stages can be relaxed even more and the front-end becomes even more dominant in power; however, the first stage becomes more difficult to design.

### 2.2 Survey of Recently Published 10-bit Pipeline ADCs

Table 2.1 presents some of the recently published 10-bit pipeline ADCs. The table is limited to conversion rates from 10 to 50 Mega Samples per Second (MS/s).

### 2.3 Design Application and Target Specifications

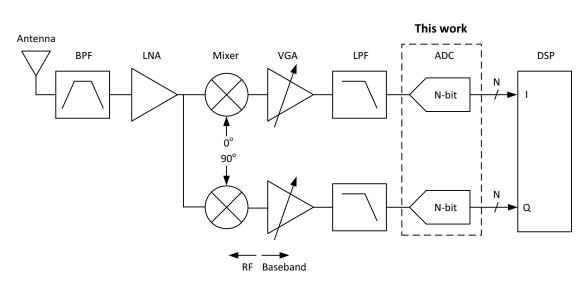

Figure 2.9 shows a general block diagram of a wireless radio receiver used in many popular receiver architectures today (e.g. WLAN, Bluetooth, etc). A wireless transmitter transmits the raw data packets across a physical channel, which is then received by the

| Reference | Conversion rate | Supply | Peak ENOB | Power | FOM       |

|-----------|-----------------|--------|-----------|-------|-----------|

|           | [MS/s]          | [V]    | [bits]    | [mW]  | [pJ/step] |

| [5]       | 10              | 1.0    | 8.9       | 8.1   | 1.7       |

| [6]       | 12              | 1.2    | 8.4       | 3.3   | 0.80      |

| [7]       | 20              | 1.2    | 9         | 5     | 0.68      |

| [8]       | 20.5            | 1.5    | 9         | 19.5  | 0.19      |

| [9]       | 30              | 1.0    | 8.8       | 4.7   | 0.43      |

| [10]      | 40              | 1.2    | 9.5       | 18.3  | 0.63      |

| [11]      | 50              | 1.8    | 9.4       | 9.9   | 0.30      |

| [12]      | 50              | 1.0    | 8.0       | 1.9   | 0.15      |

Table 2.1: Previous 10-bit pipeline ADCs

Figure 2.9: General block diagram for a wireless radio receiver

antenna. The signal content from a certain carrier frequency is selected by the Band-Pass Filter (BPF) and put through a Low-Noise Amplifier (LNA) to amplify the signal and suppress noise. The high-frequency Radio Frequency (RF) signal is then mixed down to the low-frequency baseband range. A Variable Gain Amplifier (VGA) scales the analog signal to a full-scale range before the spectral content above the baseband range is filtered by a Low-Pass Filter (LPF). The filtered signal is inputted to the ADC and converted into a digital signal. Once the signal is digitized, it gets processed in the Digital Signal Processing (DSP) block according to the receiver architecture. This thesis describes the design of a pipeline ADC with front-end capacitor-sharing for the ADC blocks within the radio receiver. In [13], a 10-bit pipeline ADC is designed in IBM 0.13  $\mu$ m for a 802.11a/g Wireless Local Area Network (WLAN) receiver. It operates at 25 MS/s, resolves 1.5 bits/stage, and accepts an input signal up to a maximum range of 1.4  $V_{PP}$  and a frequency of 12.5 MHz. This thesis uses these specifications as a guideline. Table 2.2 summarizes the target specifications for the pipeline ADC in this work. In [14], a capacitor-sharing technique similar to the one that was independently

| Design Parameter        | Specification       |

|-------------------------|---------------------|

| Technology              | $0.13~\mu{ m m}$    |

| Resolution              | 10  bits            |

| Sampling rate           | $20 \mathrm{~MS/s}$ |

| Maximum input frequency | 10 MHz              |

| Stage resolution        | 1.5 bits per stage  |

| Reference voltage       | $0.8 \mathrm{V}$    |

| Maximum input swing     | $1.6 V_{PP}$        |

| Supply                  | $1.2 \mathrm{V}$    |

| FOM                     | 0.5  pJ/step        |

Table 2.2: Design specifications targeted for this work

devised in this work is presented; however, the capacitor-sharing is performed between the pipeline stages and not between the front-end S/H and first stage.

# Chapter 3

# Pipeline ADC Building Blocks and Design Methodology

This section shows how to design a pipeline ADC for a specific operating speed and (thermal noise and settling) accuracy. In Section 3.1, opamp design considerations will be presented. Then in Section 3.2, three major pipeline building blocks are characterized. Finally, an example design of a N-bit pipeline ADC is described in Section 3.3.

### 3.1 Opamp Design

The opamp is used in the MDAC to implement the stage gain. It's configured in a closedloop circuit where the closed-loop gain is equal to the stage gain. The three opamp design parameters that are discussed next are gain, bandwidth, and output swing.

#### 3.1.1 Gain

As discussed in Section 2.1.2, the accuracy of the stage gain determines the settling accuracy of the residue signal. The settling accuracy refers to how close the residue output settles to it's intended value and therefore, it can limit the accuracy of the ADC. Assuming the opamp has sufficient time to settle to it's final value, the opamp's openloop gain, 'A', sets the settling accuracy. This is because a higher open-loop gain results in a more accurate stage gain and in turn, the residue output follows a more accurate transfer function. To ensure the residue settles to within  $\Delta LSB$ , the loop gain of the closed-loop circuit,  $A\beta$ , must be:

$$A\beta > \frac{2^N}{\Delta} \tag{3.1}$$

where  $\beta$  is the feedback factor of the closed-loop circuit and 1  $LSB = 1/2^N$ . The loop gain, as the name suggests, is the gain around the opamp closed-loop circuit. Considering there are other sources of error (e.g. thermal noise), a reasonable choice is  $\Delta = 0.25 LSB$ . For instance, the front-end S/H and first pipeline stage in a 10-bit pipeline ADC requires a loop gain of:

$$\frac{2^{10}}{0.25} = 4096 \ or \ 72dB \tag{3.2}$$

#### 3.1.2 Bandwidth

Assuming the opamp has sufficient gain to accurately settle to it's final value, the opamp speed, which determines how fast the residue output settles to a final value, sets the settling accuracy. The bandwidth must be high enough for the opamp to settle to a sufficiently accurate value within the required time of half a sampling period,  $0.5/f_S$ . Equation 3.3 sets the bandwidth of the opamp closed-loop circuit,  $f_{3dB}$ , so that the residue settles to within 0.5 LSB in half a sampling period.

$$f_{3dB} = \frac{(N+1) \cdot ln2 \cdot f_S}{\pi} \tag{3.3}$$

Like with loop gain, the bandwidth of the opamp closed-loop circuit is the product of the opamp's Gain Bandwidth (GBW) product and  $\beta$ :

$$f_{3dB} = GBW\beta \tag{3.4}$$

#### 3.1.3 Output Voltage Swing

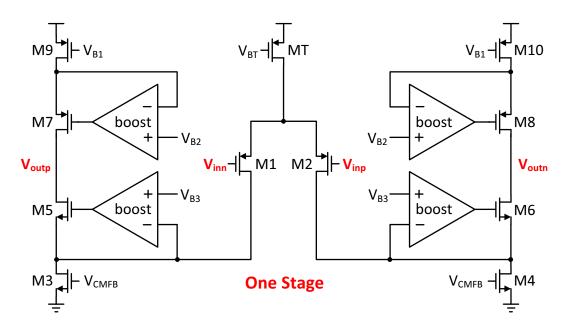

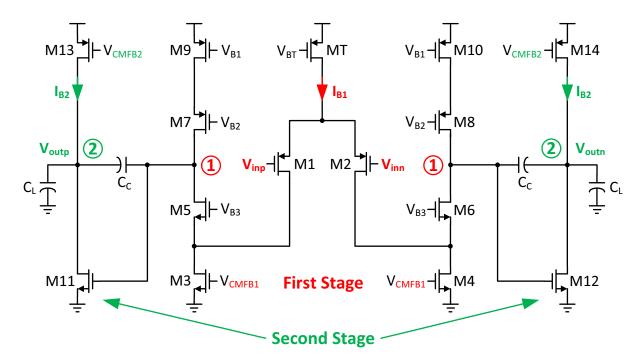

Clearly, high opamp gain is needed at the front-end to achieve the desired settling accuracy. Previous publications ([6], [8], [1] have typically used single-stage opamps with gainboosting (Figure 3.1) or two-stage Miller-compensated opamps (Figure 3.2) to achieve these gains. In Figures 3.1 and 3.2,  $V_{CMFB}$  is a signal generated by a Common-Mode Feedback (CMFB) circuit to control the Common-Mode (CM) output voltage.

Figure 3.1: Single-stage opamp with gain-boosting

The two-stage opamp has more output swing than the single-stage opamp because the output transistors in the two-stage opamp are cascoded. Each transistors must have a drain-to-source voltage,  $V_{DS}$ , of at least one overdrive voltage,  $V_{eff}$ ; otherwise, the transistors drop out of saturation and the gain dramatically decreases. A transistor's  $V_{eff}$  is the difference between its gate-to-source voltage,  $V_{GS}$ , and its threshold,  $V_t$ . At a supply voltage of 1.2 V and a  $V_{eff}$  of 150 mV, the differential output swing in Figure 3.1 is limited to:

$$2(1.2 - 4V_{eff}) = 1.2 V_{pp} \tag{3.5}$$

Figure 3.2: Two-stage opamp with a folded-cascode and a common source stage

For the two-stage case, the differential output swing in Figure 3.2 is limited to:

$$2 (1.2 - 2V_{eff}) = 1.8 V_{pp}$$

(3.6)

Equations 3.5 and 3.6 specify the absolute maximum swing; however, the gain drops even as the output transistors near the edge of saturation. Instead of designing a much higher gain to accommodate for the drop, a simpler method is to design for greater swing. For a full-scale range of 1.6  $V_{pp}$ , this work adopts a two-stage opamp like the one in Figure 3.2. The first stage is a folded cascode, which will generate most of the gain, and the second stage is a simple common source, which supports an output swing of up to 1.8  $V_{pp}$ .

### 3.2 Building Blocks

In this section, the 1.5-bit sub-ADC and choice of comparator are presented. The frontend S/H and two 1.5-bit MDAC blocks are then analyzed to show that their thermal noise level sets the dynamic range of the pipeline ADC.

#### 3.2.1 Sub-ADC

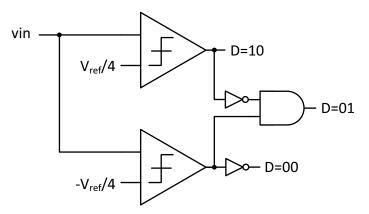

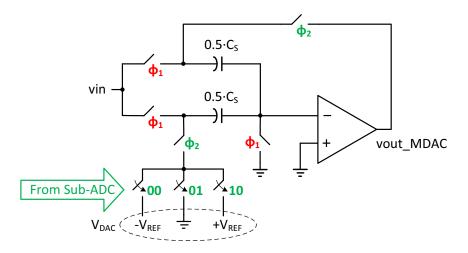

As described in Section 2.1.3, the sub-ADC samples the input voltage in  $\Phi_1$  and then in  $\Phi_2$ , digitizes it to a sub-resolution equal to the number of bits resolved per stage. The bits are used by the MDAC in  $\Phi_2$  to calculate the residue for the next stage. In this work, a 1.5-bit sub-ADC is used in each pipeline stage. A 1.5-bit sub-ADC is composed of two comparators and digital logic as shown in Figure 3.3. The comparator used in this

Figure 3.3: Three-level sub-ADC

work is the Charge-Distribution comparator [15] shown in Figure 3.4. The threshold

Figure 3.4: Charge distribution comparator

of this comparator is set by:

$$V_{thres} = \frac{C_{ref}}{C_{in}} (V_{refp} - V_{refn})$$

(3.7)

The total input capacitance of the sub-ADC during  $\Phi_1$  is  $C_{iT,subADC}$ , which is equal to  $2C_{in}$ . It is desirable to make  $C_{in}$  small because  $C_{iT,subADC}$  loads the opamp in the previous stage. Since the sub-ADC only needs to be accurate to 2 bits, the sampling capacitors  $C_{in}$  and  $C_{ref}$  can be made small without worrying about thermal accuracy. In fact, the smallest value  $C_{in}$  and  $C_{ref}$  can be is most likely limited by the fabrication technology.

The comparators in a 1.5-bit sub-ADC have thresholds at  $V_{thres} = \pm V_{ref}/4$  as shown in the transfer function of the 1.5-bit MDAC in Figure 2.5. If only flip-around MDACs [16] are used and only  $V_{ref}$  is made available for the MDAC, then from Equation 3.7,  $C_{in}/C_{ref} = 4$ . Thus,  $C_{in} = 4C_{ref}$  and  $C_{iT,subADC} = 8C_{ref}$ . However, if an integrator MDAC [16] is used and  $V_{ref}/2$  is made available, then  $C_{in}/C_{ref}$  can be reduced to 2 and hence,  $C_{in} = 2C_{ref}$  and  $C_{iT,subADC} = 4C_{ref}$ . Therefore, making a fraction of  $V_{ref}$ available on-chip reduces  $C_{iT,subADC}$ .

#### 3.2.2 Sample and Hold

The S/H located at the front of the pipeline performs the first step of sampling the external input signal. Figure 3.5 shows a commonly used S/H. Phase  $\Phi_1$  and  $\Phi_2$  are

Figure 3.5: A commonly used S/H

indicated on the clock waveform in Figure 3.6. The total input sampling capacitance the external source must drive in  $\Phi_1$  is  $C_{iT,S/H} = C_S$ . In  $\Phi_2$ , the S/H opamp drives a load capacitance to hold the sampled voltage for the first pipeline stage. The capacitor  $C_S$  does not load the opamp because it's top plate has no path to ground. As a result, the

**Figure 3.6:** Clock waveform with phases  $\Phi_1$  and  $\Phi_2$  labeled

feedback factor of the S/H is:

$$\beta_{S/H} = \frac{C_S}{C_S + 0} = 1 \tag{3.8}$$

However, the total input sampling capacitance of the sub-ADC,  $C_{iT,subADC}$ , and of the MDAC,  $C_{iT,MDAC}$ , in the next stage does load the S/H opamp. The opamp is also loaded by an additional capacitance,  $C_{n2}$ , which is the total parasitic capacitance connected to node 2 in Figure 3.2. It consists of the drain capacitance of M11 and M13, and the wire capacitance of the metal used to connect voutp/voutn. Therefore, the total output load on the S/H opamp is:

$$C_{L,S/H} = C_{iT,subADC} + C_{iT,nextstageMDAC} + C_{n2}$$

(3.9)

From [17], the differential input-referred thermal noise power of a S/H or an MDAC is:

$$\overline{v_{i/p}}^2 = \left(2\frac{kT}{C_S} + \frac{4}{3}\frac{kT}{C_c}(\beta)(1+n_f)\right)$$

(3.10)

where  $C_C$  is the compensation capacitor used to stabilize the opamp closed-loop circuit.

As you can see, the size of the sampling and compensation capacitors set the thermal noise level and hence, the dynamic range of the pipeline ADC. Specifically looking at the S/H, as the input signal is being sampled in  $\Phi_1$ , thermal noise from the transistors is sampled across  $C_S$ . The opamp is not used and therefore, does not contribute any noise. The first term in Equation 3.10 is the noise contribution from transistors generated during  $\Phi_1$ . Because a differential configuration is used, the term becomes  $2kT/C_S$ . In  $\Phi_2$ , both the opamp and transistors contribute thermal noise. However, the dominate source of noise is from the opamp's first stage in Figure 3.2. The noise from the second stage is negligible because, once input-referred, it is greatly reduced by the gain of the opamp. Therefore, the second term in Equation 3.10 is the noise contribution from the opamp's first stage generated during  $\Phi_2$ . The noise fraction,  $n_f$ , is defined in Equation 3.11 and it's presence in Equation 3.10 accounts for the noise contributed by transistors M3/M4 and M9/M10 in Figure 3.2. The formula is based on a similar calculation performed on a simple opamp in [18].

$$nf = \frac{g_{m3} + g_{m9}}{g_{m1}} \tag{3.11}$$

Since typically  $n_f = 1$  [17] and  $\beta_{S/H} = 1$ , the input-referred thermal noise power of the S/H block is:

$$\overline{v_{i/p,S/H}}^2 = \left(2\frac{kT}{C_S} + \frac{4}{3}\frac{kT}{C_c}(1)(2)\right)$$

(3.12)

#### 3.2.3 Multiplying DAC

In this work, a 1.5-bit MDAC is used in each pipeline stage. This section analyzes two well-known 1.5-bit MDACs.

#### 3.2.3.1 Flip-Around MDAC