### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# A low voltage micropower digital Class D amplifier modulator for hearing aids

Adrian, Victor; Chang, Joseph Sylvester; Gwee, Bah Hwee

2009

Adrian, V., Chang, J. S., & Gwee, B. H. (2009). A low voltage micropower digital Class D amplifier modulator for hearing aids. IEEE Transactions on Circuits And Systems—II. 56(2), 337-349.

## https://hdl.handle.net/10356/92040

## https://doi.org/10.1109/TCSI.2008.2001831

© 2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder. http://www.ieee.org/portal/site This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright holder. http://www.ieee.org/portal/site This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.

Downloaded on 23 Aug 2022 14:37:07 SGT

## A Low-Voltage Micropower Digital Class-D Amplifier Modulator for Hearing Aids

Victor Adrian, Joseph S. Chang, and Bah-Hwee Gwee, Senior Member, IEEE

Abstract-We present a micropower digital modulator for class-D amplifiers for power-critical digital hearing aids. The modulator design embodies a proposed Lagrange interpolation (a combined first- and second-order Lagrange) algorithmic pulsewidth modulation (PWM) and a third-order  $\Delta\Sigma$  noise shaper. By means of double-Fourier-series analysis, we analyze and determine the harmonic nonlinearities of the proposed algorithmic PWM. At 48-kHz sampling, 96-kHz PWM output, 997-Hz input, and input modulation index = 0.9, the modulator circuit achieves a total harmonic distortion + noise (THD + N)of -74 dB (0.02%) over an 8-kHz voice bandwidth-a 12-dB THD + N improvement over a reported design and yet dissipates only  $\sim$ 50% of the power. The proposed modulator dissipates the lowest power dissipation of all modulators compared, and by means of a proposed figure of merit, the proposed modulator exhibits very competitive performance. The modulator IC is fabricated in a 0.35- $\mu$ m digital CMOS process with a core area of 0.46 mm<sup>2</sup>.

*Index Terms*—Amplifiers, class D, digital circuits, hearing aids, modulators, pulsewidth modulation (PWM).

#### I. INTRODUCTION

DIGITAL hearing instrument (hearing aid) is a low-voltage (1.1-1.4-V) power-critical medical instrument whose power supply is limited by the energy capacity of the small pill-sized battery, which is typically 100 mA  $\cdot$  h. Its micropower attribute is largely achieved by employing power minimization techniques, including micropower circuit techniques [2], asynchronous-logic processors [3], power-efficient class-D amplifiers (CDAs) [4]–[6], etc., and using nanoscaled processes for IC fabrication.

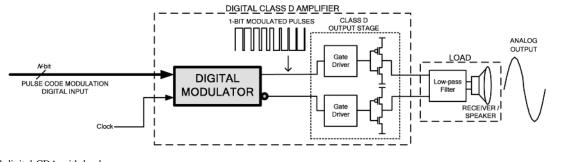

From hardware and power perspectives, the digital CDA is particularly advantageous, as the traditional approach comprising a hardware-intensive mixed-signal digital-to-analog converter and a power-inefficient linear amplifier is replaced by the simpler (in terms of hardware) and power-efficient all-digital CDA. The digital CDA, as shown in Fig. 1, comprises a digital modulator and an output stage. The digital signal processor embodied in a hearing instrument usually outputs 16-bit data in linear pulse-code modulation (PCM) to the digital modulator of the CDA. This modulator subsequently converts

The authors are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, Singapore (e-mail: victorad@pmail.ntu.edu.sg).

Digital Object Identifier 10.1109/TCSI.2008.2001831

the 16-bit PCM input into 1-bit output modulated pulses that are buffered by a high-power-efficient output stage with low impedance [7] to drive a subminiature loudspeaker (receiver).

The output modulated pulses are typically either width modulated [pulsewidth modulation (PWM)] or density modulated [pulse-density modulation (PDM)]. The simplest PWM scheme, the uniform sampling method, simply involves generation of the modulated pulses from a digital counter clocked at a rate of  $f_{\text{fast clock}} = 2^N \times f_c$  to resolve  $2^N$  distinct pulsewidths per input sampling period, where N is the output resolution and  $f_c$ is the input sampling rate or the switching frequency. This simplistic method has two major drawbacks. First, the  $f_{\text{fast clock}}$  can be very high and is impractical; for example, in a system where N = 16 and  $f_c = 48$  kHz, the required  $f_{\text{fast clock}}$  will be ~3 GHz. Second, the THD can be excessive; for example, the THD is -30 dB (~ 3%) at modulation index (M) = 0.9full scale (FS),  $f_c = 48$  kHz,  $f_{\text{in}}$  (input modulating signal frequency) = 997 Hz, and bandwidth (BW) = 100 Hz–8 kHz.

The PDM scheme is a special case of the delta–sigma ( $\Delta\Sigma$ ) modulation—specifically, the PDM is a 1-bit  $\Delta\Sigma$  modulation. The large in-band quantization noise arising from the quantization of the N-bit (N is typically 16) input to 1 bit is usually mitigated by employing either a sampling frequency with a high oversampling ratio or a high-order  $\Delta\Sigma$  noise shaper. These usual techniques are incongruous with the power- and area-critical demands of the hearing instrument. This is because a high oversampling requires several multistage interpolation filters, and the high sampling frequency reduces the power efficiency of the output stage [7], [8] and raises the need for a higher rate modulator computational circuit (loop filter). Furthermore, a high-order  $\Delta \Sigma$  noise shaper tends to be more prone to instability [9] which may undesirably limit the maximum input signal allowed, hence compromising the dynamic range. The well-established method to circumvent the limitations of the 1-bit  $\Delta\Sigma$ modulation (PDM) is the multibit  $\Delta\Sigma$  modulation that quantizes the N-bit input to multibit (less than N) output. The ensuing difficulty is that the multibit output cannot be driven by the (single-bit) CDA output stage. Instead, the usual approach involves conversion of the multibit output into PWM-type pulses (for the CDA output stage to be used)-effectively, the output is modulated using the uniform sampling method. Hence, as expected, the PWM-type output suffers from similar unacceptable harmonic distortion as in the uniform sampling method.

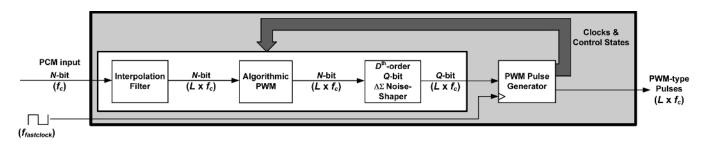

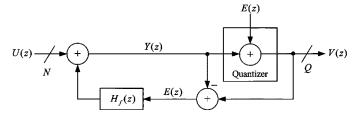

The well-adopted scheme, shown in Fig. 2, that collectively addresses the shortcomings of the uniform sampling method (PWM scheme) and 1-bit  $\Delta\Sigma$  modulation (PDM scheme) is the hybrid/combination of an algorithmic PWM and the multibit  $\Delta\Sigma$  modulation methods. The algorithmic PWM is an algorithm

Manuscript received December 17, 2007; revised April 14, 2008. First published July 22, 2008; current version published February 11, 2009. The work of V. Adrian was supported by the Singapore Millennium Foundation through a scholarship. This paper was presented in part at the IEEE International Symposium on Circuits and Systems, Vancouver, BC, Canada, May 23–26, 2004. This paper was recommended by Associate Editor P. K. T. Mok.

Fig. 1. Typical digital CDA with load.

Fig. 2. Block diagram of the components in a digital modulator employing the algorithmic PWM–multibit  $\Delta\Sigma$  modulation method.

that outputs pulsewidth data from the PCM input and mitigates the harmonic distortion of the uniform sampling method, e.g., the cross-point deriver algorithms [4] (see Section II-A-I later). The multibit  $\Delta\Sigma$  modulation, on the other hand, quantizes down the pulsewidth data into lesser number of bits so that the required  $f_{\text{fast clock}}$  can be reduced. The quantized data are subsequently converted into the final PWM-type pulses for the CDA output stage. This hybrid method was first described in [12], and its realizations have been reported elsewhere in [4] and [13].

In this paper, we present the analyses, design, and implementation of a novel digital modulator (for a CDA) based on the hybrid method for area- and power-critical 8-kHz-voice-bandwidth digital hearing instruments and with relatively low nonlinearity (near high-fidelity standards). This design is for advanced hearing instruments that demand higher fidelity without the usual IC area and power dissipation overheads. Specifically, the nonlinearity specification for a 16-bit PCM input is THD+N < -70 dB (0.03%) which far exceeds that specified for typical current hearing instruments whose typical THD + N of the complete path is -40 dB or 1% [14]. The other nonlinearities are below the noise floor-specifically, the intermodulation distortion (IMD) between the input and carrier signals, IMD  $\ll -80$  dB; this IMD is sometimes referred to as foldback distortion. In this paper, to benchmark the proposed modulator against reported modulators, we propose a new figure of merit (FOM) which is a modification of that originally used for analog-to-digital converters (ADCs). This FOM takes into consideration the bandwidth, THD + N, and power dissipation (normalized to  $V_{DD}^2$ , hence independent of  $V_{DD}$ ). On the basis of this proposed FOM, the proposed digital modulator's performance ranks among the very best and is the lowest power among the reported digital modulators.

The hybrid method embodied in the proposed modulator is the proposed algorithmic PWM, which is denoted as the "combined first- and second-order Lagrange interpolation algorithm" (LAGI) [1], and is an improvement on our earlier linear interpolation (equivalent to the first-order Lagrange interpolation). The objective of the proposed algorithm is to further suppress the harmonic distortion, thereby improving the THD + N of the uniform sampling method with small hardware and power penalties (see Section IV later).

In this paper, by means of double-Fourier-series analysis, we further investigate the harmonic distortion of the proposed LAGI to determine the mechanisms thereof, thereby providing insight into the parameters that influence the distortion. This insight is particularly useful to designers because it delineates the available parameters to vary or tradeoff to meet a given specification. Furthermore, we derive an expression to analytically determine the THD, and this expression is useful to predict the THD without resorting to time-consuming simulations or measurements (as an afterthought). We verify our analyses and proposed CDA modulator design on the basis of simulations and on measurements on a fabricated prototype IC. The design features an overall THD + N of -74dB (0.02%) at M = 0.9 FS over an 8-kHz voice bandwidth and dissipates a very modest  $31-\mu W$  average power at 1.1 V, which is thus highly applicable to an area- and power-critical advanced hearing instrument with low nonlinearities. On the basis of simulations, this design features a 12-dB THD improvement and yet dissipates only  $\sim$ 50% power of an earlier design [4].

This paper is organized as follows. Section II details designs of the building blocks of the proposed digital modulator. Section III describes the proposed FOM. Section IV presents the simulation and IC measurement results of the proposed modulator and compares the FOM values of recently reported digital modulators in the literature. Finally, conclusions are drawn in Section V.

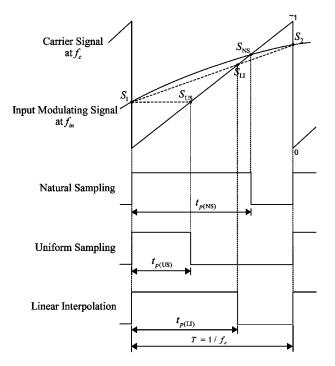

Fig. 3. Natural sampling, uniform sampling, and linear interpolation.

#### II. DIGITAL MODULATOR DESIGN

The functional blocks of a typical CDA and of the digital modulator based on the hybrid method were earlier shown in Figs. 1 and 2, respectively. As a preamble to the proposed LAGI, we will succinctly review one of the rudimentary algorithmic PWM methods, a type of cross-point deriver known as linear interpolation. The proposed LAGI is the combined first- and second-order Lagrange interpolation algorithm (LAGI), which is also an algorithmic PWM of the cross-point deriver type. The double-Fourier-series analysis will thereafter be applied to determine the mechanisms of the harmonic nonlinearities and used for deriving an expression to analytically determine THD.

#### A. Algorithmic PWM

1) Cross-Point Deriver Review: Fig. 3 shows the uniform sampling method along with its analog modulator counterpart (for analog input signal or digital with infinite sampling) known as the natural sampling method, both using single-sided trailing-edge modulation. As shown in the figure, natural sampling is ideal, as an exact cross point,  $S_{\rm NS}$ , between the modulating input signal and the carrier signal is obtained. This exact cross point translates to an exact pulsewidth,  $t_{p(\rm NS)}$ , and hence has an ideal zero THD (in the baseband of output pulses) [15]. Uniform sampling, on the other hand, results in  $S_{\rm US}$  and  $t_{p(\rm US)}$  that may differ significantly from  $S_{\rm NS}$  and  $t_{p(\rm NS)}$ , respectively. The resulting nonlinear output has significantly higher THD in its baseband, e.g., 3% as discussed earlier.

The cross-point deriver algorithmic PWM, such as linear interpolation shown in Fig. 3, improves the linearity of uniform sampling by finding a closer estimation to the ideal intersection point  $S_{\rm NS}$ . For completeness, note that there exists [4] a plethora of reported cross-point derivers and other pertinent algorithmic PWM algorithms.

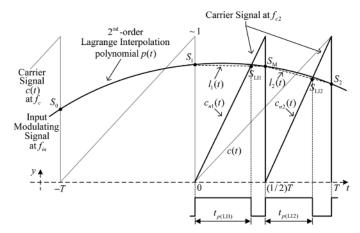

Fig. 4. Combined first- and second-order Lagrange interpolation algorithm.

2) Combined First- and Second-Order Lagrange Interpolation Algorithm (LAGI): The proposed LAGI algorithm is shown in Fig. 4, where  $S_2$  is the current sampled datum at time t = T, and  $S_1$  and  $S_0$  are the previous sampled data at time t = 0 and t = -T, respectively. This method initiates by first approximating the modulating signal arc with a second-order Lagrange interpolation [16] polynomial p(t) that passes through the three sampled points ( $S_0$ ,  $S_1$ , and  $S_2$ ). Mathematically, the general Rth-order Lagrange interpolation polynomial is of the form

$$p(t) = \sum_{k=0}^{R} I_k(t) y_k \tag{1}$$

$$I_{j}(t) = \prod_{\substack{k=0\\k\neq j}}^{R} \frac{(t-t_{k})}{(t_{j}-t_{k})}.$$

(2)

Note that for R = 1, (1) will result in linear interpolation. The polynomial p(t) for R = 2 can be obtained as follows:

$$p(t) = \frac{t^2(S_0 - 2S_1 + S_2) + t(-S_0 + S_2)T + 2S_1T^2}{2T^2} \quad (3)$$

for  $-T \leq t \leq T$ .

To obtain the pulsewidth, the intersection point of (3) and the carrier ramp (c(t) = (1/T)t) for  $0 \le t \le T$  can be solved, but this would involve a square-root computation, which is a complex process. We instead propose to simply substitute t = (1/2)T into (3) to interpolate a middle point denoted as  $S_M$  between  $S_1$  and  $S_2$ , and subsequently employ the cross-point deriver linear interpolation to obtain  $S_{L11}$  and  $S_{L12}$ .

The middle point  $S_M$  can hence be simply determined as

$$S_M = \frac{-S_0 + 6S_1 + 3S_2}{8}$$

=  $\frac{1}{8} (-S_0 + 4S_1 + 2S_1 + 2S_2 + S_2).$  (4)

In a hearing instrument where  $f_c$  is typically 48 kHz, the introduction of  $S_M$  effectively increases the input sampling rate and the computational frequency of the algorithmic PWM and the  $\Delta\Sigma$  noise shaper to  $f_{c2} = L \times f_c = 2 \times 48$  kHz = 96 kHz, where L is the number of interpolations (two in this case). For completeness, note that if a different reference 0 for the time axis is used in Fig. 4, a different expression for (3) may be obtained, but (4) would remain unaffected.

Authorized licensed use limited to: Nanyang Technological University. Downloaded on February 26,2010 at 00:23:32 EST from IEEE Xplore. Restrictions apply.

The effective oversampling arising from the interpolation of  $S_M$  reduces the nonlinearities of the output of the algorithmic PWM (and the same effect to the quantization noise at the output of the noise shaper); see the next section for the double-Fourier-series analysis of the LAGI. Physically, the interpolation process renders the distance between successive samples to become smaller, thereby providing samples that have finer quantization in time for the algorithmic PWM. Further improvements to the performance can be obtained by interpolating more data in-between  $S_1$  and  $S_2$ , but at the expense of increasing (hardware) complexity and higher switching frequency, both of which are incongruous with the desired attributes of a hearing instrument.

The doubling of the input sampling rate  $f_c$  to  $f_{c2}$  also correspondingly increases the carrier frequency to  $f_{c2}$ . This is shown in Fig. 4 where the single ramp of the carrier signal c(t) is now replaced by two ramps  $[c_{n1}(t) \text{ and } c_{n2}(t)]$  in one T period. These two ramps intersect with the linear interpolation lines  $l_1(t)$  and  $l_2(t)$  to obtain the two crossover points  $S_{LI1}$  and  $S_{LI2}$ . The corresponding pulsewidths of  $S_{LI1}$  and  $S_{LI2}$  can be obtained as follows:

$$t_{p(\text{LI1})} = T' \frac{S_1}{1 + S_1 - S_M} \tag{5}$$

$$t_{p(\text{LI2})} = T' \frac{S_M}{1 + S_M - S_2} \tag{6}$$

where  $T' = 1/2T = 1/f_{c2}$ .

The divider for the aforementioned two division operations can be implemented using the (simplified) parallel divider [17] described in [4], which is a small hardware with modest power requirements.

In a practical implementation, (5) and (6) are used for computing the  $S_1/(1 + S_1 - S_M)$  and  $S_M/(1 + S_M - S_2)$  values which will be converted to the pulsewidths  $t_{pL11}$  and  $t_{pL12}$  at the PWM pulse generator stage (after quantization at the  $\Delta\Sigma$  noise shaper; refer to Fig. 2). The switching frequency of the resulting PWM-type pulses will be that of the new carrier frequency  $f_{c2}$ .

Note that as with any other interpolation process, the interpolated output  $(S_M)$  has some errors. These errors cause spectral-image by-products (in the frequency domain) that are beyond the audio band, and in view of their wasted power dissipation, these by-products should be kept small. To determine the lowest image attenuation (the image closest to the bandwidth of interest), a tone signal at the extreme of the upper band edge,  $f_{BW,U}$ , is input to determine the power of its image component located at  $f_{image} = f_{c2}/L - f_{BW,U}$ . The resulting image gain (G) (negative of image attenuation) is

$$G = 10 \log \left[ \frac{\text{Power at } f_{\text{image}}}{\text{Power at } f_{\text{BW},U}} \right].$$

(7)

In the hearing instrument whose bandwidth is 8 kHz, the test tone signal at  $f_{BW,U} = 8$  kHz with M = 1.0 FS has a corresponding image at  $f_{image} = 40$  kHz with G = -29 dB. As the image is located well above the upper voice-band band edge, it will be attenuated by the analog low-pass filter after the output stage (Fig. 1). At  $f_{image} = 40$  kHz, the attenuation of a second-order Butterworth low-pass filter with 8-kHz cutoff is 41 dB, yielding a total image attenuation of 70 dB. Put simply, as the image is substantially attenuated, the power dissipation due to the image by-products is negligible. As a matter of interest, the usual interpolation method of zero insertion (zero stuffing) followed by low-pass filtering using the popular *sinc* interpolation filter would require a fifth-order *sinc* filter at twice interpolation to obtain the same G = -29 dB (see (8)–(10), shown at the bottom of the next page). Physically, a direct implementation of this *sinc*<sup>5</sup> filter would require four adders at  $f_{c2} = 96$  kHz (equivalent to eight adders at  $f_c = 48$  kHz) which is relatively expensive compared to the simpler implementation of  $S_M$  in (4) that requires only four adders.

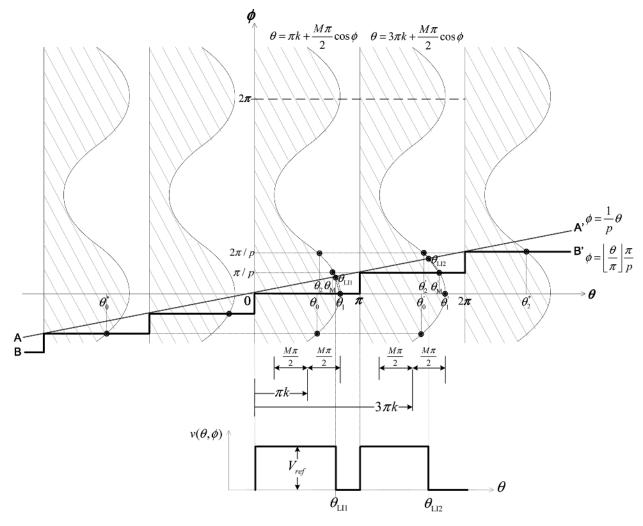

3) Double-Fourier-Series Analysis of the LAGI Pulses: In view of the deviation of the  $S_{L11}$  and  $S_{L12}$  from the exact natural sampling cross points, it is instructive to analyze and determine the harmonic nonlinearities in the LAGI pulses (quantization noise is not considered at this juncture and will be discussed separately in the next section). This analysis is performed by applying the double-Fourier-series analysis method [15] to the LAGI pulses. At the outset, note that, in [1], the double Fourier series of the LAGI pulses was inadvertently approximated to the double Fourier series of the linear interpolation pulses at twice the input sampling rate. In other words,  $S_M$  was assumed to be a true datum (not interpolated) and sampled using the new sampling rate (twice the original). A more precise analytical approach that is adopted here is to allow  $S_M$  to be a function of the other sampled data  $(S_0, S_1, \text{ and } S_2)$  at the original  $f_c$ frequency given in (4). To cater for the two PWM-type pulses with frequency  $f_{c2}$ , the entire LAGI process is treated as having a period of  $T = 1/f_c$ , but in each period, two PWM pulses are generated. The derivation using this approach is delineated in the Appendix.

The corresponding double Fourier series for the PWM-type pulses generated by the single-sided trailing-edge LAGI of a sinusoidal input modulating signal can be obtained as follows:

$$\int_{0}^{2\pi} e^{-j\pi\Phi} d\Phi = \begin{cases} 0, & n \neq 0\\ 2\pi, & n = 0 \end{cases}$$

(11)

$$K_{0n} = K_{mn}|_{m=0} \tag{12}$$

$$K_{m0} = K_{mn}|_{n=0}.$$

(13)

k is the duty cycle ratio of the PWM-type pulses for a zero input modulating signal (ideally k = 0.5), and  $V_{\text{ref}}$  is the reference value, e.g., the supply voltage, which determines the amplitude of the PWM-type pulses and can be normalized to unity for convenience of analysis.

Equation (8) is interpreted as follows. The first term  $K_{00}$  is the inconsequential dc component of the pulses. The second term corresponds to the output modulating signal and its harmonics. The third term represents the carrier signal and its harmonics. The fourth term corresponds to the IMD components that arise from the input modulating signal and its harmonics intermodulated with the carrier and the carrier's harmonics.

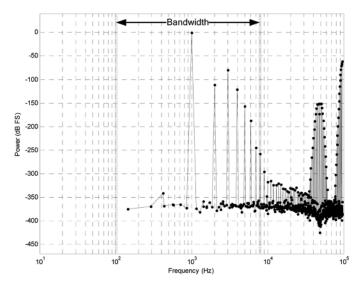

Fig. 5 shows the (single-sided) power spectrum of the LAGI pulses from the double Fourier series in (8) for  $f_{\rm in} = 997$  Hz, M = 0.9 FS, with the infinite terms approximated by limiting them to 200, and the spectra filtered by a second-order Butterworth low-pass filter with 8-kHz cutoff frequency (hearing

Fig. 5. Power spectrum of the LAGI pulses from the double-Fourier-series analysis at  $f_{\rm in}$  = 997 Hz, M = 0.9 FS after low-pass filtering.

instrument bandwidth). Note that the carrier and its harmonics in the third term are out of the band of interest. They are also of little consequence, since they are attenuated by the low-pass filter, as shown by the < -150 dB and < -50 dB spectra at 48 and 96 kHz, respectively. The foldback distortions, i.e., the in-band distortions produced by the IMD components in the fourth term, are also negligible, as shown by the in-band spectra below -350 dB.

It is of interest to note that the source of distortions is dominated by the second term in (8), i.e., the harmonics of the input modulating signal. As a case in point, the THD over the *BW* in Fig. 5 is  $-79 \text{ dB} (\sim 0.01\%)$ —commensurable with that for a high-fidelity hearing instrument. From a practical perspective, this is much lower than the typical THD (-40 dB or 1%) of hearing instruments.

In Section IV, the THD obtained from power spectral density simulations and measurements of the complete modulator design (including the  $\Delta\Sigma$  noise shaper) will be compared against the THD result obtained analytically from the second term in (8). For completeness, note that the other terms (third and fourth terms) in (8) are difficult to be verified from simulations because these terms are masked by the quantization noise floor. Another verification, albeit somewhat crude, is a visual comparison between the waveform obtained from the conversion of the double-Fourier-series expression to the time domain against the PWM-type waveform at the expected frequency  $f_{c2}$ .

#### B. $\Delta \Sigma$ Noise Shaper

The  $\Delta\Sigma$  noise shaper is implemented using the error feedback structure [18], [20] whose z-domain linear model is shown in Fig. 6. This structure is chosen for its simplicity, including the following.

- 1) The quantizer is a simple truncation of the least significant bits of Y(z), and hence, the quantization noise E(z) can be easily obtained.

- 2) From Fig. 6, the feedback filter  $H_f(z)$  is a simple (low-complexity) finite-impulse-response filter expressed as NTF(z) 1, where the noise transfer function  $NTF(z) = (1 z^{-1})^D$ [10] and D is the order of the  $\Delta\Sigma$

$$v_{\text{LAG-I}}(t) = K_{00} + \sum_{n=\pm 1}^{\pm \infty} \left( K_{0n} e^{j(n\omega_{\text{in}}t)} \right) + \sum_{m=\pm 1}^{\pm \infty} \left( K_{m0} e^{j(m\omega_c t)} \right) + \sum_{m=\pm 1}^{\pm \infty} \sum_{n=\pm 1}^{\pm \infty} \left( K_{mn} e^{j(m\omega_c t+n\omega_{\text{in}}t)} \right)$$

(8)

where

$$\omega_{\rm in} = \text{input modulating signal angular frequency} = 2\pi f_{\rm in},$$

$$\omega_c = \text{carrier angular frequency} = 2\pi f_c,$$

$$K_{00} = \frac{V_{\rm ref}}{4\pi^2} \left( \left( \int_{\Phi=0}^{\Phi=2\pi} \frac{8\pi \left(2k + M\cos(\Phi)\right)}{16 + M\cos\left(\Phi - \frac{2\pi}{p}\right) + 2M\cos(\Phi) - 3M\cos\left(\Phi + \frac{2\pi}{p}\right)} \right) + \frac{\pi \left(48k - 2M\cos\left(\Phi - \frac{2\pi}{p}\right) + 12M\cos(\Phi) - 2M\cos\left(\Phi + \frac{2\pi}{p}\right)\right)}{16 - M\cos\left(\Phi - \frac{2\pi}{p}\right) + 6M\cos(\Phi) - 5M\cos\left(\Phi + \frac{2\pi}{p}\right)} d\Phi \right) - 2\pi^2 \right) \qquad (9)$$

$$K_{mn} = \frac{jV_{\rm ref}}{4\left(m + \frac{n}{p}\right)\pi^2} \left( \int_{\Phi=0}^{\Phi=2\pi} e^{-jn\phi} \left( e^{-j\left(m + \frac{n}{p}\right)\left(\frac{8\pi(2k + M\cos(\Phi))}{16 + M\cos\left(\Phi - \frac{2\pi}{p}\right) + 2M\cos(\Phi) - 3M\cos\left(\Phi + \frac{2\pi}{p}\right)}\right)} + e^{-j\left(m + \frac{n}{p}\right)\left(\frac{\pi \left(48k - 2M\cos\left(\Phi - \frac{2\pi}{p}\right) + 12M\cos(\Phi) - 2M\cos\left(\Phi + \frac{2\pi}{p}\right)\right)}{16 - M\cos\left(\Phi - \frac{2\pi}{p}\right) + 6M\cos(\Phi) - 5M\cos\left(\Phi - \frac{2\pi}{p}\right)}\right)} - e^{-j\left(m + \frac{n}{p}\right)} d\Phi - \int_{\Phi=0}^{\Phi=2\pi} e^{-jn\Phi} d\Phi \right) \qquad \forall m, n \in \mathbb{Z} \qquad (10)$$

Fig. 6. Error feedback structure of the DS Noise Shaper.

noise shaper. The coefficients for  $H_f(z)$  can simply be obtained as powers of two or additions of powers of two. For this structure, it can be shown that the output signal-to-

quantization-noise ratio (SQNR) for an N-bit (N > Q) sinusoidal input signal (with the same assumptions assumed in [11]) is given by

SQNR (dB)

$$\approx 6.02Q + 1.76 + 20 \log(M)$$

+10 log  $\left(\frac{2D+1}{\pi^{2D}}\right) + (2D+1)10 \log\left(\frac{f_s}{2f_{\text{BW},U}}\right)$

(14)

where Q is the number of output bits and  $f_s$  is the sampling frequency of the  $\Delta\Sigma$  noise shaper; in our case,  $f_s = f_{c2} = 96$  kHz.

In the proposed design, Q is set to eight (see also Section II-C hereinafter), and D is set to three. Thus, at M = 0.9 FS, the approximate SQNR using (14) is 82 dB. By combining this SQNR value with the analytical THD value obtained from the previous section, the overall analytical THD + N of the hybrid modulator system is -77 dB which more than satisfies the desired maximum target THD + N of -70 dB. On the basis of dc-input time-domain simulations, the  $\Delta\Sigma$  noise-shaper implementation is stable up to 0.98 FS.

#### C. PWM Pulse Generator

The PWM pulse generator converts the Q-bit digital value from the  $\Delta\Sigma$  noise shaper into PWM-type pulses by means of a Q-bit digital counter. This counter is clocked at a rate of  $f_{\text{fast clock}} = 2^Q \times L \times f_c$ , where it counts up per  $1/f_{\text{fast clock}}$  period and sets the pulsewidth when the counter reaches the Q-bit value. The output PWM-type pulses have a switching frequency of  $f_{c2} = L \times f_c$ , where  $f_{c2} = 96$  kHz here.

An important consideration in the design of the PWM pulse generator is its power dissipation in relation to its number of bits (Q), its  $f_{\text{fast clock}}$  frequency, and the SQNR of the  $\Delta\Sigma$  noise shaper. On the basis of simulations, Table I tabulates the SQNR and average power dissipation of the PWM pulse generator for several Q-bit configurations using a 0.35- $\mu$ m CMOS process at 1.1-V supply and M = 0.9 FS. As shown in Table I and as expected, the power dissipation approximately doubles for every 1-bit increment of Q or, equivalently, for every doubling in the  $f_{\text{fast clock}}$ . As a compromise in the proposed design, Q is selected to be 8 bits, where the average power dissipation of the PWM pulse generator is a modest 5.8  $\mu$ W and the required  $f_{\text{fast clock}}$  is  $2^8 \times 96$  kHz  $\approx 24.6$  MHz. By adopting our frequency doubler [4], the  $f_{\text{fast clock}}$  is halved to 12.3 MHz—this is a modest and practical clock frequency compared to the

TABLE I SQNRs and Average Power Dissipation Simulation Results of the PWM Pulse Generator

| Q<br>(bit) | SQNR<br>(dB) | f <sub>fastclock</sub><br>(MHZ) | Average Power Dissipation <sup>1</sup><br>(µW) |

|------------|--------------|---------------------------------|------------------------------------------------|

| 7          | 76           | 6.1                             | 2.9                                            |

| 8          | 82           | 12.3                            | 5.8                                            |

| 9          | 88           | 24.6                            | 12.0                                           |

| 10         | 94           | 49.2                            | 26.0                                           |

<sup>1</sup> Simulated using a 0.35  $\mu$ m CMOS process at 1.1 V supply and M = 0.9 FS.

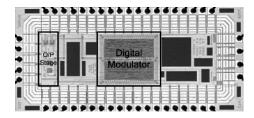

Fig. 7. IC microphotograph of the proposed digital modulator and an output stage.

TABLE II NUMBER OF TRANSISTORS REQUIRED TO REALIZE THE PROPOSED DIGITAL MODULATOR BASED ON A 0.35-MM CMOS PROCESS

| Component                                       | Number of Transistors (%) |  |  |  |

|-------------------------------------------------|---------------------------|--|--|--|

| Algorithmic PWM and $\Delta\Sigma$ Noise-Shaper | 24910 (97 %)              |  |  |  |

| PWM Pulse Generator                             | 812 (3 %)                 |  |  |  |

$f_{\text{fast clock}}$  requirement of ~6 GHz for the uniform sampling PWM method.

For hardware efficiency, the counter in the PWM pulse generator also operates as a frequency divider by dual functioning its outputs as clock and control states for the finite-state machine of the computational circuits.

#### III. FOM

From a technological perspective, it is usually of interest to benchmark new designs against reported designs. Nevertheless, comparing different designs, including CDA modulators, is often contentious because of the interdependent parameters such as the invariably diverse bandwidths, supply voltages, etc., thereof.

The FOM [21] (and its decibel-scaled form [19]) that is often used for comparing the performance of various ADCs is

$$FOM_{ADC} = DR_{dB} + 10\log\left(\frac{BW}{P}\right)$$

(15)

where DR is the dynamic range defined as  $M(DR_{dB} = -M_{dB})$  for which THD + N = 0 dB, and P is the power dissipation of the ADC.

We propose a modified FOM of (15) given hereinafter in (16) for comparing CDA modulators to account for the following.

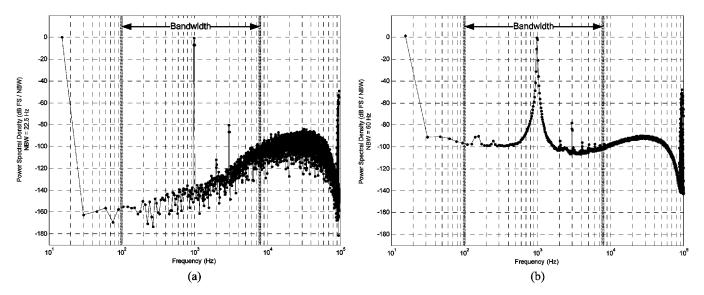

Fig. 8. Power spectral density of the output of the proposed digital modulator at  $f_{in} = 997$  Hz and M = 0.9 FS after low-pass filtering. (a) Simulation results. (b) Measurement results.

First, instead of DR that is typically given in ADC specifications, the modified FOM uses (the negative of) THD + N that is typically given for CDA modulators and accounts for the applied input M when measuring the THD + N. Note that  $[-(THD+N_{dB})-M_{dB}]$  is equivalent to  $DR_{dB}$  if THD+Nis proportional to M. For example, in a 16-bit Nyquist rate ADC, its DR is ideally 98 dB (at M = -98-dB FS, the THD + N =0 dB). Conversely, at M = 0-dB FS, the THD + N is ideally -98 dB. Second, to accommodate different supply voltages that would otherwise skew the FOM, we propose to normalize the power parameter P by dividing it by the squared voltage of the supply  $(V_{DD}^2)$

$$FOM_{CDAmod} = \left[ -\left(THD + N_{dB}\right) - M_{dB} \right] + 10 \log \left(\frac{BW}{\left(\frac{P}{V_{DD}^2}\right)}\right). \quad (16)$$

This  $FOM_{CDAmod}$  will be used as the FOM to compare reported and the proposed CDA modulators in the following.

#### IV. SIMULATION AND MEASUREMENT RESULTS

Fig. 7 shows the microphotograph of a prototype IC embodying the proposed digital modulator and an output stage, using a 0.35- $\mu$ m CMOS process. The IC area of the modulator is a relatively small area of 0.46 mm<sup>2</sup>. Table II tabulates the number of transistors and the respective relative IC areas of the combined algorithmic PWM and the  $\Delta\Sigma$  noise shaper and of the PWM pulse generator in the proposed digital modulator design.

The input datum to the modulator is a pregenerated 16-bit unsigned digital sinusoidal waveform of frequency  $f_{\rm in} = 997$  Hz (AES standards [22]) and sampled at  $f_c = 48$  kHz. The SQNR of this pregenerated digital sinewave is 102 dB for M = 0.9 FS and  $f_{\rm BW,U} = 8$  kHz and is sufficiently lower than the analytical THD + N (THD and SQNR) of the proposed modulator. The THD + N measurements are performed using the Brüel & Kjær PULSE Analyzer (Frame Type 3560C and Input/Output

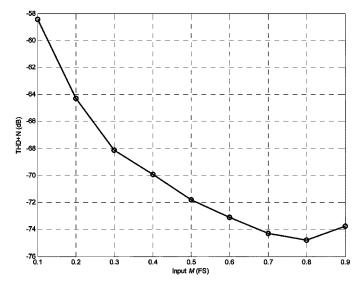

Fig. 9. THD + N measurement results versus M at  $f_{in} = 997$  Hz.

TABLE III AVERAGE POWER DISSIPATION OBTAINED FROM SIMULATIONS AND FROM MEASUREMENTS OF THE PROPOSED DIGITAL MODULATOR (1.1 V)

| Input                | Simulation<br>(µW) | Measurement<br>(µW) |  |  |

|----------------------|--------------------|---------------------|--|--|

| <i>M</i> = 0.9 FS    | 27                 | 31                  |  |  |

| M = 0 FS (quiescent) | 18                 | 20                  |  |  |

Measurement Module Type 3110) in conjunction with the power spectral density analysis using the PULSE Labshop software.

Fig. 8(a) and (b) shows the power spectral density of the proposed digital modulator obtained from simulations and from measurements on the prototype IC, respectively. Both are obtained with the same test conditions, i.e.,  $f_{in} = 997$  Hz, M = 0.9 FS, and low-pass filtered. The simulated THD is -79 dB and is consistent with the analytical THD of the LAGI obtained in Section II-A-III, thereby verifying the earlier derivations. The

| Design                      | Modulation<br>Scheme | Process<br>(µm) | Bandwidth<br>(Hz)           | THD+N<br>(dB)    | Supply Voltage<br>(V) | Power (W)                          | FOM <sub>CDAmod</sub> |

|-----------------------------|----------------------|-----------------|-----------------------------|------------------|-----------------------|------------------------------------|-----------------------|

| Pascual, et al., 2003 [13]  | Digital PWM          | -               | 20 <b>x</b> 10 <sup>3</sup> | -73 <sup>a</sup> | 43.0                  | 11.3 <sup>e, f</sup>               | 139                   |

| Gwee, et al., 2005 [4]      | Digital PWM          | 0.35            | 4 <b>x</b> 10 <sup>3</sup>  | -66 <sup>b</sup> | 1.1                   | 60 x 10 <sup>-6 g</sup>            | 145                   |

| Fujimoto, et al., 2005 [23] | Digital PDM          | 0.35            | 22 x 10 <sup>3</sup>        | −96 °            | 5.0                   | 150 <b>x</b> 10 <sup>-3 h, i</sup> | 162                   |

| Proposed modulator          | Digital PWM          | 0.35            | 8 x 10 <sup>3</sup>         | -74 <sup>d</sup> | 1.1                   | 31 x 10 <sup>-6</sup>              | 159                   |

TABLE IV FOM (  $FOM_{CDAmod}$ ) Comparison

<sup>a</sup> Measured THD+N at a low-pass filtered load at M = -1 dB FS (~0.9 FS) and  $f_{in} = 1$  kHz.

<sup>b</sup> Simulated THD+N at an LC low-pass filter at M = -0.9 dB FS (0.9 FS) and  $f_{in} = 997$  Hz.

<sup>c</sup> Measured THD+N at an *LC* low-pass filter at M = -1 dB FS (~0.9 FS) and  $f_{in} = 997$  Hz.

<sup>d</sup> Measured THD+N at an *LC* low-pass filter at M = -0.9 dB FS (0.9 FS) and  $f_{in} = 997$  Hz.

<sup>e</sup> Calculated from the stated output power ( $P_{OUT}$ ) and efficiency ( $\eta$ ):  $P = ((100-\eta)/\eta) \times P_{OUT}$ .

<sup>f</sup> This design is implemented in a DSP.

<sup>g</sup> Simulated power dissipation.

<sup>h</sup> Power dissipation for 1 channel (1 modulator).

<sup>i</sup> This design does not include any circuits for the digital interpolation process.

simulated SQNR, on the other hand, is 84 dB and largely agrees with the SQNR obtained from the analytical expression in (14) at 82 dB, and the small difference is attributed to the approximations used in the derivations of (14).

The simulated THD+N obtained by summing the harmonic power with the quantization noise power is -78 dB, and on the basis of simulations in Fig. 8(a), this is a 12-dB improvement compared to the first-order Lagrange interpolation design in [4]. The measured THD+N in Fig. 8(b), on the other hand, is -74 dB (0.02%). The 4-dB difference between the simulations and measurements is largely due to the supply noise in the low-frequency region (< 1 kHz). In the perspective of the specifications for an advanced hearing instrument, the measured THD+N still satisfies the maximum target THD+N of -70dB; note that it is expected that the low-frequency noise is further mitigated in practical battery cell operation in hearing instruments. For completeness, note that the component (the first point) with about 0-dB power spectral density in both figures is an inconsequential dc component.

Fig. 9 shows the THD + N measurement results versus M at  $f_{in} = 997$  Hz. The average measured THD + N for the range of M = 0.1-0.9 FS is -70 dB (0.03%). It is worth noting that at high modulation indexes (M > 0.8 FS), the harmonic distortions (THDs) dominate the THD+N. This is because the distance between samples is larger, and consequently, the errors in the interpolation and algorithmic PWM processes increase. On the other hand, as the modulation index decreases, the signal magnitude decreases while the noise floor remains unchanged (throughout all of the modulation indices), hence the THD+N increases.

Table III tabulates the average power dissipation obtained from simulations and from measurements of the digital modulator IC for two modulation indexes at 1.1-V supply. The simulated and measured power dissipation results agree well.

Table IV tabulates a comparison on the basis of the proposed  $FOM_{CDAmod}$  of recently reported digital modulator designs

with various bandwidths and supply voltages. The comparison depicts that the proposed modulator design is very competitive. Note that although the FOM of the reported design [23] appears to be slightly better, the computation of its FOM does not include any digital interpolation circuits which may otherwise increase the power dissipation, hence negatively skewing its FOM slightly. A further worthy attribute of the proposed design is its lowest power dissipation attribute in the comparison, commensurable for a practical advanced digital hearing instrument.

#### V. CONCLUSION

We have presented a digital modulator design embodying a proposed LAGI algorithm for low-voltage micropower operation such as power-critical hearing instruments. We have also derived the double-Fourier-series expression of the LAGI algorithm to analytically determine the harmonic nonlinearities therein. The modulator design and the derived analytical double-Fourier-series expression were verified by means of simulations and measurements on a prototype IC. The modulator featured low nonlinearity with low computational/output frequency requirements and micropower dissipation at 1.1 V. We have also presented a proposed FOM to compare various modulators, and the proposed modulator was shown to be very competitive and features the lowest power dissipation.

#### APPENDIX

#### DOUBLE FOURIER SERIES ANALYSIS OF THE COMBINED FIRST-AND SECOND-ORDER LAGRANGE INTERPOLATION PWM PULSES

Three-Dimensional Geometrical Configuration: The double-Fourier-series analysis method [15] is applied to the PWM pulses generated by the single-sided trailing-edge LAGI of a sinusoidal input modulating waveform. This method reconstructs the PWM-type pulses using the 3-D geometrical configuration in [24] and is shown in Fig. 10 for the LAGI pulses. In this illustration, the shaded areas represent walls

Fig. 10. Three-dimensional geometrical configuration of the LAGI pulses.

that are parallel and have identical shapes to each other. The walls are flat on one side, while their other sides are shaped according to the input modulating signal. The height of the walls represents  $V_{\rm ref}.$

The  $\phi$  axis in Fig. 10 represents the phase shift of the input modulating signal

$$\phi = 2\pi f_{\rm in} t = \omega_{\rm in} t. \tag{A1}$$

On the other hand, the  $\theta$  axis represents the phase shift of the original carrier signal  $(f_c)$  instead of the new carrier signal  $(f_{c2} = 2f_c)$ , i.e.,

$$\theta = 2\pi f_c t = \omega_c t. \tag{A2}$$

This is because  $S_M$  is not a true datum sampled at  $f_{c2}$  frequency but a function of the other sampled datum at  $f_c$  given in (4). This  $\theta$  axis would impose difficulty in representing the output PWM-type pulses which are at  $f_{c2}$ . To circumvent this problem, the whole process of LAGI can be treated as having a period of  $T = 1/f_c$  whereby, in each period, two PWM pulses are generated (at  $f_{c2}$ ).

In the time domain, the LAGI employs two linear interpolations which result in two PWM-type pulses for every T period. In the corresponding  $(\theta, \phi)$  domain, these two linear interpolations occur every  $2\pi$  length of  $\theta$ . Since each of them needs to take place on an input modulating signal wall, two identical walls are erected per  $2\pi$  of  $\theta$ . Fig. 10 shows the two linear interpolations that occur in  $0 \le \theta < \pi$  and  $\pi \le \theta < 2\pi$ .

For the first wall that is erected on  $0 \le \theta < \pi$ , the shape of its sinusoidal side can be defined as

$$\theta = \pi k + \frac{M\pi}{2}\cos(\phi), \quad \text{for } 0 \le \theta < \pi$$

(A3)

while for the second wall on  $\pi \le \theta < 2\pi$ , the shape of its sinusoidal side can be defined as

$$\theta = 3\pi k + \frac{M\pi}{2}\cos(\phi), \quad \text{for } \pi \le \theta < 2\pi$$

(A4)

where k is the duty cycle ratio of the PWM-type pulses for a zero input modulating signal (ideally, k = 0.5).

The line AA' in Fig. 10 corresponds to the new carrier signal in Fig. 4. The portion of the line within  $0 \le \theta < \pi$  corresponds to the ramp of  $c_{n1}(t)$  in Fig. 4, while the portion within  $\pi \le \theta <$

Fig. 11. Finding  $\theta_{LT1}$  and  $\theta_{LT2}$ .

$2\pi$  corresponds to the ramp of  $c_{n2}(t)$ . The line AA' is expressed as

$$\phi = \frac{1}{p}\theta \tag{A5}$$

where

$$\frac{\omega_{\rm in}}{\omega_c} = \frac{2}{p}.\tag{A6}$$

The line BB' in Fig. 10 corresponds to the contour of uniform sampling that samples the input signal periodically in the time domain. Correspondingly, the line BB' also periodically samples the input signal which is now represented by the walls in the  $(\theta, \phi)$  domain. The line BB' samples two points  $(\theta_1 \text{ and } \theta'_M)$  from the two signal walls in every  $2\pi$  period of  $\theta$  and can be expressed as

$$\phi = \left\lfloor \frac{\theta}{\pi} \right\rfloor \frac{\pi}{p} \tag{A7}$$

where  $\lfloor \theta/\pi \rfloor$  denotes the nearest integer that is less than or equal to  $\theta/\pi$ .

In Fig. 10, the points  $\theta_0$ ,  $\theta_1$ , and  $\theta_2$ , which are located within  $0 \le \theta < \pi$ , correspond to the sampled data  $S_0$ ,  $S_1$ , and  $S_2$  in Fig. 4, respectively. These points can be obtained by substituting (A7) into (A3). Similarly, their counterparts located within  $\pi \le \theta < 2\pi$ , i.e.,  $\theta'_0$ ,  $\theta'_1$ , and  $\theta'_2$ , can be obtained by substituting (A7) into (A4).

The point  $\theta_M$  in Fig. 10, which is located within  $0 \le \theta < \pi$ , corresponds to  $S_M$  in Fig. 4 and can be represented by replacing  $S_0$ ,  $S_1$ , and  $S_2$  in (4) with  $\theta_0$ ,  $\theta_1$ , and  $\theta_2$ , respectively, as

$$\theta_M = \frac{-\theta_0 + 6\theta_1 + 3\theta_2}{8}.\tag{A8}$$

Likewise, its counterpart,  $\theta'_M$ , which is located within  $\pi \leq \theta < 2\pi$ , can be represented as

$$\theta'_M = \frac{-\theta'_0 + 6\theta'_1 + 3\theta'_2}{8}.$$

(A9)

The PWM-type pulses, shown at the bottom of Fig. 10, can be defined using the pulse amplitude function  $v(\theta, \phi)$  as

$$v(\theta, \phi) = \begin{cases} V_{\text{ref}}, & 0 \le (\theta - |\theta|_{\pi}) \le \theta_{\text{LI1}} \\ V_{\text{ref}}, & \pi \le (\theta - |\theta|_{2\pi}) \le \theta_{\text{LI2}} \\ 0, & \text{otherwise} \end{cases}$$

(A10)

where  $|\theta|\pi$  denotes the nearest multiple of  $\pi \leq \theta$ ,  $|\theta|_2\pi$  denotes the nearest multiple of  $2\pi \leq \theta$ ,  $V_{\text{ref}}$  is the reference value, e.g., supply voltage, which will determine the amplitude of the PWM pulses and can be normalized to unity for convenience, and  $\theta_{\text{LI1}}$ and  $\theta_{\text{LI2}}$  are the pulsewidth functions—determined by the input signal and the linear interpolation algorithm.

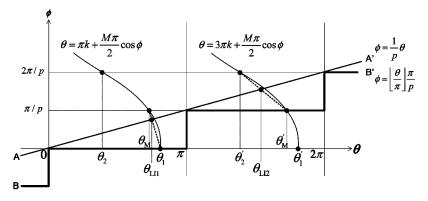

1) Pulsewidth Functions: The pulsewidth functions  $\theta_{LI1}$  and  $\theta_{LI2}$  are required to solve for  $v(\theta, \phi)$ . These two functions locate the cross points (in the  $(\theta, \phi)$  domain) that correspond to the cross points  $S_{LI1}$  and  $S_{LI2}$ , respectively (in the time domain). Fig. 11 shows a detailed illustration of finding  $\theta_{LI1}$  and  $\theta_{LI2}$ .

The linear interpolation line between  $(\theta_1, 0)$  and  $(\theta_M, \pi/p)$  in Fig. 11 can be obtained as follows:

$$\phi = \frac{\pi}{p} \left( \frac{\theta - \theta_1}{\theta_M - \theta_1} \right). \tag{A11}$$

The cross point  $\theta_{LI1}$  can be obtained when  $\phi$  of (A11) equals  $\phi$  of line AA' (A5), i.e.,

$$\frac{1}{p}\theta_{L11} = \frac{\pi}{p} \left( \frac{\theta_{L11} - \theta_1}{\theta_M - \theta_1} \right)$$

$$\therefore \ \theta_{L11} = \frac{\pi \theta_1}{\pi - \theta_M + \theta_1}.$$

(A12)

Using similar steps,  $\theta_{L12}$  can be obtained as

$$\theta_{\rm LI2} = \frac{\pi (2\theta'_M - \theta'_2)}{\pi - \theta'_2 + \theta'_M}.$$

(A13)

By substituting  $\theta_M(A8)$  into (A12) and  $\theta'_M(A9)$  into (A13),  $\theta_{L11}$  and  $\theta_{L12}$  can be written in terms of the sampled points as follows:

$$\theta_{\rm LI1} = \frac{8\pi\theta_1}{8\pi + \theta_0 + 2\theta_1 - 3\theta_2} \tag{A14}$$

$$\theta_{\rm LI2} = \frac{\pi \left(-2\theta'_0 + 12\theta'_1 - 2\theta'_2\right)}{8\pi - \theta'_0 + 6\theta'_1 - 5\theta'_2}.$$

(A15)

The sampled point terms in (A14) and (A15) can be substituted by the input modulating signal wall expressions in (A3) and (A4). However, the cross points or, equivalently, the pulsewidth functions  $\theta_{L11}$  and  $\theta_{L12}$  still depend on the  $\phi$  values that are sampled by the line BB' in (A7). Since this line is discontinuous in the  $(\theta, \phi)$  domain, due to the discrete term  $\lfloor \theta/\pi \rfloor$ , the double Fourier series in the  $(\theta, \phi)$  domain cannot be

Authorized licensed use limited to: Nanyang Technological University. Downloaded on February 26,2010 at 00:23:32 EST from IEEE Xplore. Restrictions apply.

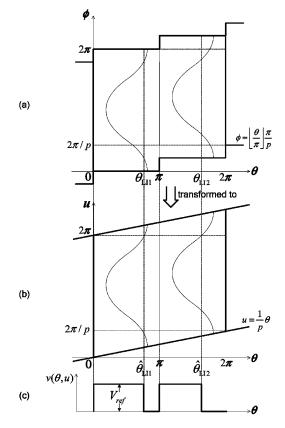

Fig. 12. Transforming  $(\theta, \phi)$  to  $(\theta, u)$  domain.

obtained directly. To circumvent this, (A7) is transformed into a continuous straight line using the following transform:

$$u = \phi - \left\lfloor \frac{\theta}{\pi} \right\rfloor \frac{\pi}{p} + \frac{\theta}{p}.$$

(A16)

The transformation process is shown from Fig. 12(a) and (b). Note that even after the transformation, the PWM-type pulses, as shown in Fig. 12(c), remain the same. As shown in Fig. 12(b), the line BB' is now a continuous straight line in the  $(\theta, u)$  domain. This line is given by

$$u = \phi - \left\lfloor \frac{\theta}{\pi} \right\rfloor \frac{\pi}{p} + \frac{\theta}{p} = \left\lfloor \frac{\theta}{\pi} \right\rfloor \frac{\pi}{p} - \left\lfloor \frac{\theta}{\pi} \right\rfloor \frac{\pi}{p} + \frac{\theta}{p} = \frac{\theta}{p}.$$

(A17)

By substituting (A3) into (A14) and (A4) into (A15), followed by transforming the  $\phi$  terms into the  $(\theta, u)$  domain, the pulsewidth functions can finally be obtained as (A18) and (A19), shown at the bottom of the page.

2) Double Fourier Series: Consider the parallelogram bounded by  $\theta = 0$ ,  $\theta = 2\pi$ ,  $u = (\theta/p)$ , and  $u = 2\pi + (\theta/p)$ in Fig. 12(b). The PWM-type pulses (the pulse amplitude function) in (A10), which can now be written as  $v(\theta, u)$ , are given by the wall configurations inside this parallelogram. Since the wall configurations are periodic in both  $\theta$  and u directions,  $v(\theta, u)$  can be expressed by means of a double Fourier series as (its complex form is used here)

$$v(\theta, u) = \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} K_{mn} e^{j(m\theta + nu)}$$

(A20)

where  $K_{mn}$  is the complex Fourier coefficient given by

$$K_{mn} = \frac{1}{4\pi^2} \int_{u} \int_{\theta} F(\theta, u) e^{-j(m\theta + nu)} d\theta du \qquad \forall m, n \in \mathbb{Z}.$$

(A21)

The limits of the aforesaid integrals are the edges of the aforementioned parallelogram.

In Fig. 12(b), the height of the walls is equal to the constant  $V_{\text{ref}}$  for all values of  $\theta$  between 0 and  $\hat{\theta}_{\text{LI1}}$ , and between  $\pi$  and  $\hat{\theta}_{\text{LI2}}$ . It is zero for other values of  $\theta$  up to  $2\pi$ . Consequently, (A21) takes the following form when applied to this particular configuration:

$$K_{mn} = \frac{1}{4\pi^2} \int_{u=(\theta/p)}^{u=2\pi+(\theta/p)} \left( \int_{\theta=0}^{\theta_{1,11}} V_{\text{ref}} e^{-j(m\theta+nu)} d\theta + \int_{\theta=\pi}^{\theta=\hat{\theta}_{1,12}} V_{\text{ref}} e^{-j(m\theta+nu)} d\theta \right) du,$$

$$\forall m, n \in \mathbb{Z}.$$

(A22)

This integration is difficult to compute because of the term  $(u - \theta/p)$  in  $\hat{\theta}_{L11}$  (A18) and  $\hat{\theta}_{L12}$  (A19). To simplify the integration, the following substitution can be performed:

$$\Phi = u - \frac{\theta}{p}, \qquad 0 \le \theta < 2\pi, \quad 0 \le u < 2\pi.$$

(A23)

$$\hat{\theta}_{\text{LI1}} = \frac{8\pi \left(2k + M\cos\left(u - \frac{\theta}{p}\right)\right)}{16 + M\cos\left(u - \frac{\theta}{p} - \frac{2\pi}{p}\right) + 2M\cos\left(u - \frac{\theta}{p}\right) - 3M\cos\left(u - \frac{\theta}{p} + \frac{2\pi}{p}\right)}, \quad \text{for } 0 \le \theta < \pi$$

(A18)

$$\hat{\theta}_{\text{LI2}} = \frac{\pi \left(48k - 2M\cos\left(u - \frac{\theta}{p} - \frac{2\pi}{p}\right) + 12M\cos\left(u - \frac{\theta}{p}\right) - 2M\cos\left(u - \frac{\theta}{p} + \frac{2\pi}{p}\right)\right)}{16 - M\cos\left(u - \frac{\theta}{p} - \frac{2\pi}{p}\right) + 6M\cos\left(u - \frac{\theta}{p}\right) - 5M\cos\left(u - \frac{\theta}{p} + \frac{2\pi}{p}\right)}, \quad \text{for } \pi \le \theta < 2\pi$$

(A19)

Hence

$$u = \Phi + \frac{\theta}{p}$$

to yield  $\frac{\mathrm{d}u}{\mathrm{d}\Phi} = 1.$  (A24)

The substitution renders the parallelogram to undergo a linear shearing transform into a square bounded by  $\theta = 0$ ,  $\theta = 2\pi$ ,  $\phi = 0$ , and  $\phi = 2\pi$ . The preceding integration now takes the form of (A25), shown at the bottom of the page. If  $m + (n/p) \neq 0$ , (A26), shown at the bottom of the page, is derived, where

$$\int_{0}^{2\pi} e^{-jn\Phi} d\Phi = \begin{cases} 0, & n \neq 0\\ 2\pi, & n = 0 \end{cases}.$$

(A27)

The evaluation of the integration can be considered for several cases, depending on the integer values of m and n. These cases will be discussed in the following.

Case 1: m = 0 and n = 0. Since  $m\theta = m\omega_c t = 0$  and  $n\phi = n\omega_m t = 0$ , i.e., dc, this case therefore corresponds to  $K_{00}$  of the dc component.  $K_{00}$  can be derived from (A25) as (A28), shown at the bottom of the page.

Case 2:  $m + (n/p) \neq 0$ , m = 0, and  $n \neq 0$ . This case corresponds to  $K_{0n}$  of the input modulating signal and its harmonics. From (A26)

$$K_{0n} = K_{mn}|_{m=0}.$$

(A29)

Case 3:  $m \neq 0$  and n = 0. This case corresponds to  $K_{m0}$  of the carrier signal and its harmonics. From (A26)

$$K_{m0} = K_{mn}|_{n=0}$$

. (A30)

Case 4:  $m + (n/p) \neq 0$ ,  $m \neq 0$ , and  $n \neq 0$ . This case corresponds to  $K_{mn}$  of the intermodulation components arising from the input modulating signal and carrier signal harmonics.  $K_{mn}$  is given by (A26).

To obtain the double-Fourier-series expression for the PWMtype pulses in the time domain,  $\theta$  and u have to be related to time. From (A2),  $\theta = \omega_c t$ , and from (A17) and (A6)

$$u = \frac{\theta}{p} = \omega_{\rm in} t. \tag{A31}$$

$$K_{mn} = \frac{1}{4\pi^2} \int_{\Phi=0}^{\Phi=2\pi} \left( \int_{\theta=0}^{\theta=8\pi(2k+M\cos(\Phi))/16+M\cos(\Phi-\{2\pi/p\})+2M\cos(\Phi)-3M\cos(\Phi+\{2\pi/p\})} \times V_{\text{ref}} e^{-j(m\theta+n(\theta+\theta/p))} d\theta + \int_{\theta=\pi}^{\theta=\pi(48k-2M\cos(\Phi-2\pi/p)+12M\cos(\Phi)-2M\cos(\Phi+2\pi/p))/16-M\cos(\Phi-2\pi/p)+6M\cos(\Phi)-5M\cos(\Phi+2\pi/p)} \times V_{\text{ref}} e^{-j(m\theta+n(\Phi+\theta/p))} d\theta \right) d\Phi \quad \forall \, m, n \in \mathbb{Z}$$

(A25)

$$K_{mn} = \frac{jV_{\text{ref}}}{4\left(m + \frac{n}{p}\right)\pi^{2}} \times \left(\int_{\Phi=0}^{\Phi=2\pi} e^{-jn\Phi} \times \left(e^{-j(m+n/p)(8\pi(2k+M\cos(\Phi))/16+M\cos(\Phi-2\pi/p)+2M\cos(\Phi)-3M\cos(\Phi+2\pi/p))} + e^{j(m+n/p)(\pi(48k-2M\cos(\Phi-2\pi/p)+12M\cos(\Phi)-2M\cos(\Phi+2\pi/p))/16-M\cos(\Phi-2\pi/p)+6M\cos(\Phi)-5M\cos(\Phi+2\pi/p))} - e^{-j(m+n/p\pi)\pi}\right) d\Phi - \int_{\Phi=0}^{\Phi=2\pi} e^{-jn\Phi} d\Phi \qquad \forall m, n \in \mathbb{Z}$$

(A26)

$$K_{00} = \frac{V_{\text{ref}}}{4\pi^2} \left( \left( \int_{\Phi=0}^{\Phi=2\pi} \frac{8\pi \left(2k + M\cos(\phi)\right)}{16 + M\cos\left(\Phi - \frac{2\pi}{p}\right) + 2M\cos(\phi) - 3M\cos\left(\Phi + \frac{2\pi}{p}\right)} + \frac{\pi \left(48k - 2M\cos\left(\Phi - \frac{2\pi}{p}\right) + 12M\cos(\phi) - 2M\cos\left(\Phi + \frac{2\pi}{p}\right)\right)}{16 - M\cos\left(\Phi - \frac{2\pi}{p}\right) + 6M\cos(\phi) - 5M\cos\left(\Phi + \frac{2\pi}{p}\right)} d\Phi \right) - 2\pi^2 \right)$$

(A28)

Authorized licensed use limited to: Nanyang Technological University. Downloaded on February 26,2010 at 00:23:32 EST from IEEE Xplore. Restrictions apply.

Hence, by substituting (A2) and (A31) into (A20)

$$v(\theta, u) = v(\omega_c t, \omega_{\rm in} t) = v(t). \tag{A32}$$

The coefficients in (A26), (A28), (A29), and (A30) are inserted to the series in (A20), and thereafter, following the substitutions shown in (A32), the double Fourier series for the PWMtype pulses generated by the single-sided trailing-edge LAGI of a sinusoidal input modulating waveform can finally be obtained as

$$v_{\text{LAGI}}(t) = K_{00} + \sum_{n=\pm 1}^{\pm \infty} \left( K_{0n} e^{j(n\omega_{\text{in}}t)} \right)$$

$$+ \sum_{m=\pm 1}^{\pm \infty} \left( K_{m0} e^{j(m\omega_{c}t)} \right)$$

$$+ \sum_{m=\pm 1}^{\pm \infty} \sum_{n=\pm 1}^{\pm \infty} \left( K_{mn} e^{j(m\omega_{c}t+n\omega_{\text{in}}t)} \right). \quad (A33)$$

#### REFERENCES

- V. Adrian, B.-H. Gwee, and J. S. Chang, "A novel combined first and second order Lagrange interpolation sampling process for a digital class D amplifier," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2004, vol. 3, pp. 233–236.

- [2] J. S. Chang and Y. C. Tong, "A micropower-compatible time-multiplexed SC speech spectrum analyzer design," *IEEE J. Solid-State Circuits*, vol. 28, no. 1, pp. 40–48, Jan. 1993.

- [3] K. S. Chong, B.-H. Gwee, and J. S. Chang, "Energy-efficient synchronous-logic and asynchronous-logic FFT/IFFT processors," *IEEE J. Solid State Circuits*, vol. 42, no. 9, pp. 2034–2045, Sep. 2007.

- [4] B.-H. Gwee, J. S. Chang, and V. Adrian, "A micropower low-distortion digital class-D amplifier based on an algorithmic pulsewidth modulator," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 10, pp. 2007–2022, Oct. 2005.

- [5] B.-H. Gwee, J. S. Chang, and H. Li, "A micropower low-distortion digital pulsewidth modulator for a digital class D amplifier," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 49, no. 4, pp. 245–256, Apr. 2002.

- [6] T. Ge and J. S. Chang, "Bang-bang control class-D amplifiers: Power supply noise," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 8, pp. 723–727, Aug. 2008, to be published.

- [7] J. S. Chang, M. T. Tan, Z. H. Cheng, and Y. C. Tong, "Analysis and design of power efficient class D amplifier output stages," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 6, pp. 897–902, Jun. 2000.

- [8] W. Shu and J. S. Chang, "THD of closed-loop analog PWM class-D amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 6, pp. 1769–1777, Jul. 2008, to be published.

- [9] S. R. Norsworthy, R. Schreier, and G. C. Temes, *Delta-Sigma Data Converters: Theory, Design, and Simulation*. New York: IEEE Press, 1996, pp. 166–167.

- [10] S. R. Norsworthy, R. Schreier, and G. C. Temes, *Delta-Sigma Data Converters: Theory, Design, and Simulation*. New York: IEEE Press, 1996, p. 172.

- [11] S. R. Norsworthy, R. Schreier, and G. C. Temes, *Delta-Sigma Data Converters: Theory, Design, and Simulation*. New York: IEEE Press, 1996, pp. 4–5.

- [12] M. Sandler, J. Goldberg, R. Hiorns, R. Bowman, M. Watson, and P. Ziman, "Ultra low distortion digital power amplification," presented at the 91st Audio Engineering Society Conv., New York, Oct. 1991, preprint no. 3115.

- [13] C. Pascual, Z. Song, P. T. Krein, D. V. Sarwate, P. Midya, and W. J. Roeckner, "High-fidelity PWM inverter for digital audio amplification: Spectral analysis, real-time DSP implementation, and results," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 473–485, Jan. 2003.

- [14] F. Serra-Graells, L. Gómez, and J. L. Huertas, "A true-1-V 300-µW CMOS-subthreshold log-domain hearing-aid-on-chip," *IEEE J. Solid-State Circuits*, vol. 39, no. 8, pp. 1271–1281, Aug. 2004.

- [15] H. S. Black, *Modulation Theory*. Princeton, NJ: Van Nostrand, 1953, pp. 263–281.

- [16] E. Kreyszig, Advanced Engineering Mathematics, 8th ed., Singapore: Wiley, 1999, pp. 848–852.

- [17] R. F. Tinder, *Engineering Digital Design*, 2nd ed. San Diego, CA: Academic, 2000, pp. 353–357.

- [18] R. Schreier and G. C. Temes, *Understanding Delta–Sigma Data Converters*. New York: IEEE Press, 2004, pp. 224–225.

- [19] R. Schreier and G. C. Temes, Understanding Delta–Sigma Data Converters. New York: IEEE Press, 2004, p. 357.

- [20] C. C. Cutler, "Transmission systems employing quantization," U.S. Patent 2 927 962, Mar. 8, 1960.

- [21] S. Rabii and B. A. Wooley, "A 1.8-V digital-audio sigma–delta modulator in 0.8-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 32, no. 6, pp. 783–796, Jun. 1997.

- [22] AES Standard Method for Digital Audio Engineering—Measurement of Digital Audio Equipment, AES17–1998 (r2004), pp. 17.

- [23] Y. Fujimoto, P. L. Ré, and M. Miyamoto, "A delta-sigma modulator for a 1-bit digital switching amplifier," *IEEE J. Solid-State Circuits*, vol. 40, no. 9, pp. 1865–1871, Sep. 2005.

- [24] W. R. Bennett, "New results in the calculation of modulation products," *Bell Syst. Tech. J.*, no. 12, pp. 228–243, 1933.

Victor Adrian received the B.Eng. degree in electrical and electronic engineering and the M.Phil. degree from Nanyang Technological University (NTU), Singapore, in 2003 and 2004, respectively, where he is currently working toward the Ph.D. degree in the School of Electrical and Electronic Engineering.

He was a Project Officer with NTU from 2004 to 2005. His research interests include digital class-D amplifiers, real-time implementation of digital signal processing systems, and acoustic noise reduction.

Mr. Adrian was awarded a Singapore Millennium Foundation Ph.D. Scholarship in 2005.

**Joseph Chang** received the B.Eng. degree from Monash University, Melbourne, Australia, and the Ph.D. degree from the Department of Otolaryngology, University of Melbourne, Melbourne.

He was the Associate Dean of Research and Graduate Studies of the College of Engineering, Nanyang Technological University, Singapore, where he is currently with the School of Electrical and Electronic Engineering. He is also an Adjunct Professor with Texas A&M University, College Station. His research pertains to multidisciplinary

biomedical and electronics including auditory prosthesis and devices. He has published over 100 peer-reviewed papers and conference proceedings and is the holder of seven patents.

Dr. Chang is an Associate Editor for the IEEE TCAS-I and TCAS-II, a Coeditor of the CAS Magazine "Open Column," and an Associate Editor for a Special Issue of the IEEE Proceedings. He has chaired several international conferences, including the recent IEEE–NIH Life Science Systems and Applications Workshop, USA. He received the Best Paper Award in the Microelectronics Conference.

**Bah-Hwee Gwee** (S'93–M'97–SM'03) received the B.Eng. degree in electrical and electronic engineering from the University of Aberdeen, Aberdeen, U.K., in 1990 and the M.Eng. and Ph.D. degrees from Nanyang Technological University (NTU), Singapore, in 1992 and 1998, respectively.

He is currently an Associate Professor with the School of Electrical and Electronic Engineering, NTU. His research interests include low-power asynchronous microprocessor designs, class-D amplifiers, and soft computing.

Dr. Gwee was the Chairman of the IEEE Circuits and Systems—Singapore Chapter in 2005 and 2006. He has served as the Technical Program Chair for ISIC 2007 and served in the Steering Committee for the IEEE APCCAS. He has been an Associate Editor for the journal of *Circuits, Systems, and Signal Processing* since 2007.