# A Magnetic-Less DC–DC Converter for Dual-Voltage Automotive Systems

Fang Zheng Peng, Senior Member, IEEE, Fan Zhang, and Zhaoming Qian, Senior Member, IEEE

Abstract—The automotive industry is moving toward 42 V to meet more electrical needs. Several dual-voltage (42 and 14 V) architectures have been proposed for the transition and accommodation of 14-V loads. A dc–dc converter that connects the 42 and 14 V is one key device in any dual-voltage architecture. This paper presents a compact, efficient, magnetic-less bidirectional dc–dc converter for dual-voltage (42/14 V) automotive systems. The dc–dc converter is based on the generalized multilevel converter topology having the ability to balance battery voltages, emit zero or low electromagnetic interference, and have low cost by using low-voltage MOSFETs. The main circuit of the dc–dc converter is analyzed and its control scheme is presented in the paper. A self-powered gate drive circuit is developed for the dc–dc converter to reduce costs, signal connections, and circuit complexity. A prototype has been built and experimental results are presented.

*Index Terms*—DC–DC converter, dual-voltage automotive system, multilevel converter, 42-V automotive system.

## I. INTRODUCTION

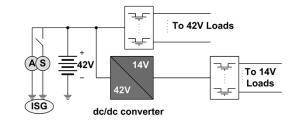

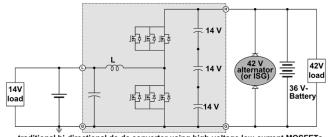

**I** N ORDER TO meet more electrical needs, the automotive industry is moving toward 42 V. Several dual-voltage (42 and 14 V) architectures have been considered for the transition and accommodation of 14-V loads. Figs. 1 and 2 show the two most popular architectures: dual- and single-battery 42/14-V systems. A dc–dc converter that connects the 42 and 14 V is indispensable in either dual-voltage architecture. An integrated starter generator (ISG), or integrated starter alternator (ISA) is used to generate 42 V.

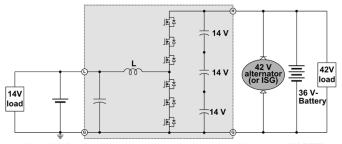

Fig. 3 shows a traditional bidirectional dc–dc converter using relatively high-voltage and low-current MOSFETs, where each MOSFET has to sustain 42 V continuously. For this configuration, MOSFETs with a voltage rating of at least 150 V should be used considering load dump transients. For reference, a 14-V alternator's voltage can be as high as 50 V at load dump transients. Therefore, one may have to parallel several MOSFETs to reach current ratings required. Fig. 4 shows a traditional bidirectional dc–dc converter using

Paper IPCSD 02–082, presented at the 2002 Industry Applications Society Annual Meeting, Pittsburgh, PA, October 13–18, and approved for publication in the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS by the Industrial Power Converter Committee of the IEEE Industry Applications Society. Manuscript submitted for review June 1, 2002 and released for publication December 17, 2002.

F. Z. Peng is with the Department of Electrical and Computer Engineering, Michigan State University, East Lansing, MI 48824-1226 USA, and also with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: fzpeng@egr.msu.edu).

F. Zhang is with the Department of Electrical and Computer Engineering, Michigan State University, East Lansing, MI 48824-1226 USA.

Z. Qian is with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: qian@cee.zju.edu.cn).

Digital Object Identifier 10.1109/TIA.2003.808945

AS = 42V 42V

Fig. 1. Dual-battery 42/14-V system architecture.

Fig. 2. Single-battery 42/14-V system architecture.

traditional bi-directional dc-dc converter using high-voltage low-current MOSFETs

Fig. 3. Traditional bidirectional dc-dc converter using high-voltage low-current MOSFETs, where each MOSFET has to sustain 42 V.

traditional bi-directional dc-dc converter using low-voltage high-current MOSFETs

Fig. 4. Traditional bidirectional dc–dc converter using low-voltage high-current MOSFETs, where each MOSFET has to sustain only 14 V.

relatively low-voltage and high-current MOSFETs, where each MOSFET has to sustain only 14 V continuous. In this case,

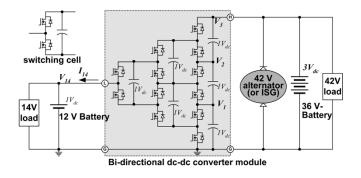

Fig. 5. Proposed four-level bidirectional dc-dc converter using low-voltage MOSFETs, where each MOSFET only sustains 14 V.

three low-voltage MOSFETs are put in series to reach the high voltage of 42 V. In either configuration, an LC filter is needed on the low voltage side. The inductor is the most lossy and bulkiest component in the converter. The magnetic component also has been the stumbling block to converters' circuit integration. In order to reduce the size and weight of the inductor, the MOSFET devices have to be switched at a very high frequency, typically tens to hundreds of kilohertz. However, this increases switching power loss and thermal management. Semiconductor heat dissipation also limits the switching frequency of the converter, and a low switching frequency results in increased size and weight of the magnetic components, further increasing converter size and weight. Therefore, it is sought to develop a simple cost-effective topology to reduce dc-dc converter size and weight and improve efficiency. This paper presents a novel dc-dc converter to achieve these goals.

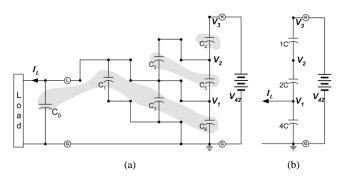

# II. MAIN CIRCUIT AND OPERATING PRINCIPLE

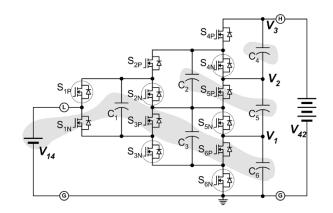

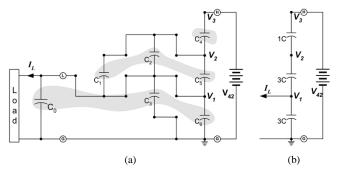

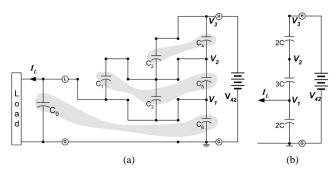

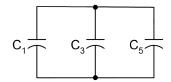

Fig. 5 shows the proposed four-level bidirectional dc–dc converter using relatively low-voltage high-current MOSFETs, where each MOSFET only sustains 14 V. The converter is composed of six switching cells forming three switching poles. The converter does not use any magnetic components and operate at a fixed duty ratio and frequency with no pulsewidth modulation (PWM). The four-level dc–dc converter operates like a voltage multiplier. Each capacitor's voltage is kept close to 1 V<sub>dc</sub>, which is one third of the high-side voltage. The converter has three switching states that generate an output voltage of 1 V<sub>dc</sub> on the low-voltage side.

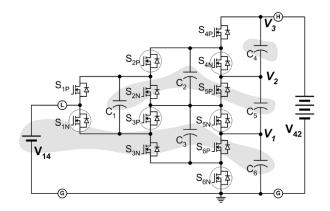

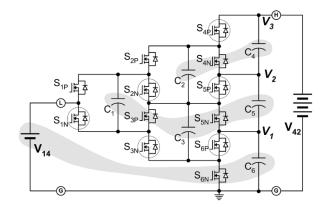

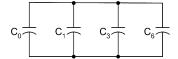

Figs. 6–8 show the three respective switching states, where the circled devices are gated on. These three redundant switching states keep all voltages balanced. In Fig. 6, capacitors C1, C3, and C6 are charge-equalized and connected to the 12-V battery (or 14-V loads), thus, we have  $V_{14} = V_{C1} = V_{C3} = V_{C6}$  and  $V_{C2} = V_{C5}$ . Similarly, we have  $V_{14} = V_{C3} = V_{C6}$  and  $V_{C1} = V_{C2} = V_{C5}$  in Fig. 7 and  $V_{14} = V_{C6}$ ,  $V_{C1} = V_{C3} = V_{C5}$ , and  $V_{C2} = V_{C4}$  in Fig. 8. After one cycle of these three states, all capacitors and output voltage on the 12-V battery side are kept balanced and charged to the one-third of the 36-V battery. Any adjacent two switches of each switch pole are complementary to each other. Therefore, if any switch's state is determined or known then

Fig. 6. Switching state I:  $(S_{1P}, S_{2P}, S_{4P}) = (1, 0, 0)$  to produce 1 V<sub>dc</sub>.

Fig. 7. Switching state II:  $(S_{1P}, S_{2P}, S_{4P}) = (0, 1, 0)$  to produce 1  $V_{dc}$ .

Fig. 8. Switching state III:  $(S_{1P}, S_{2P}, S_{4P}) = (0, 0, 1)$  to produce 1 V<sub>dc</sub>.

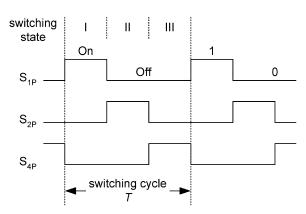

the rest switches of the pole are automatically determined. In Fig. 6–8, only the top switch of each pole  $(S_{1P}, S_{2P}, S_{4P})$  is used to describe switching states. Fig. 9 shows the gating sequence.

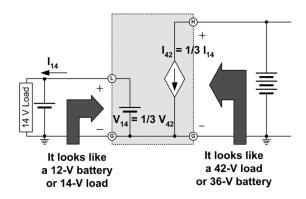

The dc–dc converter behaves like an ideal voltage multiplier or voltage divider interfacing the 14-V and 42-V buses as shown in Fig. 10. That is, the bidirectional converter module steps down the 36-V battery (or 42-V load) into an equivalent 12-V battery (or 14-V load) when viewed from the low-voltage side

$$V_{14} = \frac{1}{3}V_{42} \tag{1}$$

Fig. 9. Switching sequence of the converter.

Fig. 10. Equivalent circuits as seen from either side.

and steps up the 14-V load (or 12-V battery) into an equivalent 42-V load (or 36-V battery) when viewed from the high-voltage side

$$V_{42} = 3V_{14}.$$

(2)

In other words, for a single 36-V battery system, the converter behaves like a 12-V battery to the 14-V load or a 42-V load to the 36-V battery. Equations (1) and (2) indicate that the voltage ratio of the low- and high-voltage sides is locked to a factor of 3. This integer multiplication/division relationship between the 14- and 42-V sides is desirable in most cases because the battery status is passed onto the other side and it is consistent with the traditional 14-V load requirements.

For noninteger multiplication/division or independent voltage regulation, switching frequency control or a PWM operation with minimal inductor can be used.

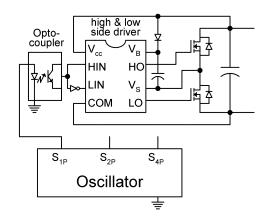

## III. SELF-POWERED GATE DRIVE AND CONTROL CIRCUIT

As described above, the four-level dc–dc converter has six switching cells. Each cell only sustains 14 V, which makes it easy to implement a simple gate drive and control circuit. The dc–dc converter developed is a self-contained module, where each switching cell is driven by a self-powered gate drive circuit. An oscillator circuit is used to generate gate sequence signals. Fig. 11 shows a brief sketch of the circuit, where a high- and low-side gate driver based on charge pump is used to drive each switching cell. The oscillator circuit is based on the converter

Fig. 11. Self-powered gate drive and control.

ground and each cell is level-shifted or opto-isolated through an optocoupler. The power is directly from each cell's dc capacitor voltage, which is 14 V. The circuit is designed operable for a voltage range of 8–16 V covering the traditional 12-V battery operating range. This self-powered gate drive reduces circuit complexity and cost tremendously. For the subject power (1 kW) and voltage (42 V) levels, gate drive circuits (about U.S.  $2\sim3$  per switching cell) and their power supply with isolation (U.S. 3-6 per switching cell) cost much more than the main MOSFET device itself (about U.S.  $2\sim3$  per 30 V/2.8 m $\Omega$ MOSFET). This four-level dc–dc converter structure makes the self-powered gate drive possible and, thus, reduces cost greatly.

## IV. ANALYSIS OF POWER LOSS AND EFFICIENCY

The traditional dc-dc converter's power loss can be divided into four major parts: switching loss, conduction loss, gate drive loss, and magnetic component (or inductor) loss. Since the new converter has no magnetic parts, magnetic component loss does not exist. Switching and gate drive losses are very small, compared with those of the traditional converter because the switching frequency (1-10 kHz) used is one to two orders lower. However, capacitor loss exists in the new converter. As discussed above, the capacitors' charge/voltage is balanced through rotating the three redundant switching states and connecting capacitors to parallel. Therefore, energy loss occurs at each switching-over instant when different capacitors with different voltages are connected together in parallel for charge balancing. This capacitor loss is analyzed in the Appendix. The total capacitor loss and voltages in the worst case are expressed as follows:

$$P_{\text{Cap-loss}} = 0.218 \frac{I_L^2}{C \cdot f} \tag{3}$$

$$V_{C4} = V_3 - V_2 = V_0 + 0.147\Delta \tag{4}$$

$$V_{C5} = V_2 - V_1 = V_0 + 0.076\Delta \tag{5}$$

$$V_{14} = V_{C6} = V_1 = V_0 - 0.223\Delta \tag{6}$$

$$\Delta = \frac{I_L}{C \cdot f} \tag{7}$$

where  $I_L$  is the load current, C is the capacitance, f is the switching frequency, and  $V_0 = V_{42}/3$ . The power loss and voltage unbalance  $\Delta$  are inversely proportional to the capacitance and switching frequency. By increasing capacitance and

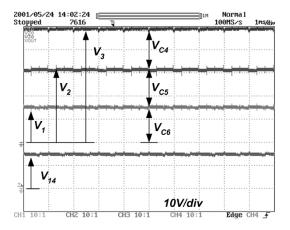

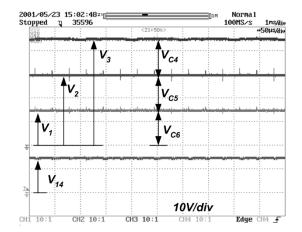

Fig. 12. Voltage waveforms ( $V_{\rm batt} = \sim 110\%$  and  $f_{\rm sw} = 1$  kHz).  $V_{C4} = 17$  V,  $V_{C5} = 15.45$  V, and  $V_{C6} = 14.5$  V.

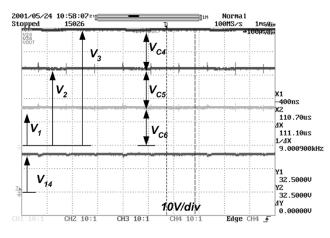

Fig. 13. Voltage waveforms ( $V_{\rm batt} = \sim 110\%$  and  $f_{\rm sw} = 3$  kHz).  $V_{C4} = 16$  V,  $V_{C5} = 15.7$  V, and  $V_{C6} = 15.45$  V.

switching frequency, efficiency and voltage balance can be improved. For example, considering that the load current  $I_L = 50$  A, the capacitance  $C = 4700 \ \mu\text{F}$ , switching frequency f = 10 kHz, and the input voltage  $V_{42} = 42$  V, we have

$$P_{\text{Cap-loss}} = 0.218 \frac{I_L^2}{C \cdot f} = 11.596 \text{ W},$$

which is about 1.66% of the output power,  $(14 \text{ V}) \cdot (50 \text{ A}) = 700 \text{ W}$ , and the capacitor voltages are

$$\Delta = \frac{I_L}{C \cdot f} = 1.064 \text{ V},$$

$$V_{C4} = V_3 - V_2 = V_0 + 0.147\Delta = 14.156 \text{ V},$$

$$V_{C5} = V_2 - V_1 = V_0 + 0.076\Delta = 14.081 \text{V}$$

$$V_{C6} = V_1 = V_0 - 0.223\Delta = 13.763 \text{ V}.$$

As can be seen from the above calculation, with enough capacitance and switching frequency, the capacitor loss and voltage unbalance are relatively small even in the worst case. In real applications, the capacitor loss and voltage unbalance will be smaller for single battery systems because of larger output capacitance and even much smaller for dual battery systems. The detailed analysis is given in Appendix.

In addition, it should be noted that independent voltage control /regulation can be implemented by controlling switching

Fig. 14. Voltage waveforms ( $V_{\rm batt} = \sim 100\%$  and  $f_{\rm sw} = 10$  kHz).  $V_{C4} = 14.8$  V,  $V_{C5} = 14.5$  V, and  $V_{C6} = 14.3$  V.

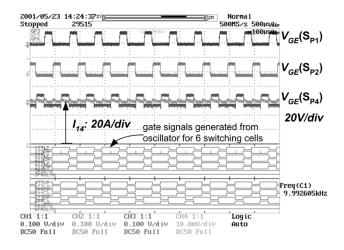

Fig. 15. Gate voltage and signals ( $V_{\text{batt}} = 48\%$  and  $f_{\text{sw}} = 10$  kHz).

frequency, because the output voltage  $V_{14}$  is related to the switching frequency as indicated in (6).

## V. EXPERIMENTAL RESULTS

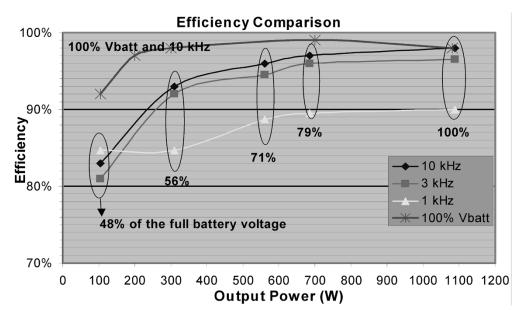

Figs. 12-16 show experimental results with capacitance  $C = 4,700 \ \mu\text{F}$  and power flow from the 42-V to 14-V side. Figs. 12-14 show voltage waveforms at three different switching frequencies: 1, 3, and 10 kHz. With 1-kHz switching, Fig. 12 shows that the voltage unbalance is appreciable:  $V_{C6} < V_{C5} < V_{C4}$ , which is consistant with the analytical conclusions expressed in (4)-(6). While increasing the switching frequency to 10 kHz, the voltage unbalance becomes insignificant. Fig. 15 shows gate voltages and signals that were generated by the self-powered gate drive and control circuit. Fig. 16 shows high efficiency over a wide load range at full (100%) battery voltage. The efficiency was measured by a Yokogawa power meter with power flow from the high voltage to low voltage at difference battery voltage levels. Since both the input and output voltage and current are dc, the measurement error should be less than 0.3% according to the power meter specifications. The experimental results clearly demonstrated voltage balance, voltage ripple reduction,

Fig. 16. Measured efficiency. A 12-V battery is considered fully charged at 14.2 V (or 100%) and empty at 8 V (56%), while a 36-V battery is full at 42.6 V (or 100%) and empty at 24 V (or 56%). The operating range is  $8 \sim 16$  V for 14-V loads and  $24 \sim 48$  V for 42-V loads. The efficiency measurement was performed further down to 7 V (~48%) and 21 (~48%) V for 14- and 42-V loads, respectively.

and efficiency improvement when the switching frequency is increased, which is consistant with the analysis.

## VI. CONCLUSIONS

This paper has presented a compact, efficient, magnetic-less bidirectional dc–dc converter for dual voltage (42/14 V) automotive systems. The dc–dc converter is based on the generalized multilevel converter topology having ability to balance battery voltages, emit zero or low electromagnetic interference (EMI), and have low cost by using low-voltage MOSFETs.

The multilevel configuration makes it possible to utilize low voltage MOSFETs, which have extremely low on-resistance and are low cost because of large production volume for switching power supplies used in communication and computer industries. A self-powered gate drive and control circuit has been developed. Advantages of the dc–dc converter include: 1) no magnetic components; 2) compact size and light weight; 3) easy manufacturing (possible to build a whole converter system on package, or IC power module); 4) high efficiency (>98%); and 5) low EMI emission. A prototype using six cell modules was built and tested. Experimental results demonstrated that the new dc–dc converter has high efficiency, good voltage regulation, and low EMI.

In addition, it has been analyzed that independent voltage control/regulation can be implemented by changing switching frequency. This technique can be used when the fixed input–output relation (i.e., the output voltage is always 1/3 of the input voltage) is not desirable (e.g., one battery is overdrained or overcharged) and voltage regulation is needed.

#### APPENDIX

## ANALYSIS OF CAPACITOR LOSS AND VOLTAGE UNBALANCE

According to the control scheme used, the capacitors' charge /or voltage is balanced through rotating the three redundant

Fig. 17. Equivalent circuit of Fig. 6 (i.e., State I).

switching states every T/3 as shown in Fig. 9 and connecting capacitors to parallel. Power loss occurs when capacitors with different voltage are connected together to parallel. To determine the power loss and voltage unbalance of the capacitors, we need to consider each of the three redundant states and their transitions.

# A. Switching State I: Fig. 6, $(S_{1P}, S_{2P}, S_{4P}) = (1, 0, 0)$

At the beginning of State I, assume that

$$V_{C4} = V_3 - V_2 = V_0 + \Delta_3 \tag{8}$$

$$V_{C2} = V_{C5} = V_2 - V_1 = V_0 + \Delta_2 \tag{9}$$

$$V_{C0} = V_{C1} = V_{C3} = V_{C6} = V_1 = V_0 + \Delta_1$$

(10)

where

$$V_0 = \frac{1}{3}V_{42} \tag{11}$$

$$\Delta_1 + \Delta_2 + \Delta_3 = 0. \tag{12}$$

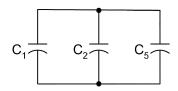

The equivalent circuit of State I is shown in Fig. 17(a), which can be further reduced to Fig. 17(b). Note that the on-resistance of MOSFETs has no effect on the capacitor balancing and power loss rather than the initial charge /discharge current [1], thus using short circuit to represent conducting MOSFETs in Fig. 17. For simplicity, assume all capacitors including the output capacitor  $C_0$  in the converter have the same capacitance C. This is the

Fig. 18. Equivalent circuit of Fig. 7 (i.e., State II).

worst case for power loss and voltage unbalance of the converter. For a dual-battery system,  $C_0$  is the 12-V battery that has equivalently large capacitance. For a single-battery system, 14-V loads normally have input capacitors that augment the total output capacitance  $C_0$ . The load current  $I_L$  charges the upper capacitors and discharges the lower capacitors as shown in Fig. 17(b). This state lasts T/3 as shown in Fig. 9. At the end of State I (after T/3), the voltages become

$$V_{C4} = V_3 - V_2 = V_0 + \Delta_3 + \frac{1}{21}\Delta$$

(13)

$$V_{C2} = V_{C5} = V_2 - V_1 = V_0 + \Delta_2 + \frac{1}{42}\Delta$$

(14)

$$V_{C0} = V_{C1} = V_{C3} = V_{C6} = V_1 = V_0 + \Delta_1 - \frac{1}{14}\Delta$$

(15)

where

$$\Delta = \frac{I_L \cdot T}{C}.$$

(16)

## B. At the Transition From State I to State II

Now consider the transition from State I to State II. Fig. 18 shows the equivalent circuits of State II (Fig. 7).

Before State II (i.e., at the end of State I), the capacitors' voltages are expressed in (13)–(15), which are the initial values before the switching over transition. After switching over to State II, the capacitors settle down to the following voltages, which can be calculated from (13)–(15) and Fig. 18:

$$V_{C4} = V_3 - V_2$$

=  $V_0 - \frac{1}{5}\Delta_1 + \frac{1}{5}\Delta_2 + \Delta_3 + \frac{1}{15}\Delta$  (17)

$$V_{C1} = V_{C2} = V_{C5} = V_2 - V_1$$

=  $V_0 + \frac{4}{\Delta_1} + \frac{11}{\Delta_2} + \frac{1}{\Delta} \Delta$  (18)

$$V_{C0} = V_{C3} = V_{C6} = V_1$$

$$=V_0 + \frac{14}{15}\Delta_1 + \frac{1}{15}\Delta_2 - \frac{41}{630}\Delta.$$

(19)

# C. At the End of State II

At the beginning of State II, the voltages are expressed in (17)–(19). Using the similar analysis described in State I, the voltages at the end of State II become

$$V_{C4} = V_3 - V_2$$

=  $V_0 - 0.2\Delta_1 + 0.2\Delta_2 + \Delta_3 + 0.1333\Delta$  (20)

$V_{C1} = V_{C2} = V_{C5} = V_2 - V_1$

$$= V_0 + 0.2666\Delta_1 + 0.7333\Delta_2 + 0.0206\Delta \qquad (21)$$

Fig. 19. Equivalent circuit of Fig. 8 (i.e., State III).

$$V_{C0} = V_{C3} = V_{C6} = V_1$$

=  $V_0 + 0.9333\Delta_1 + 0.0667\Delta_2 - 0.1539\Delta.$  (22)

## D. At the Transition From State II to State III

Now consider the transition from State II to State III. Fig. 19 shows the equivalent circuits of State III (Fig. 8). Before State III (i.e., at the end of State II), the capacitors' voltages are expressed in (20)–(22), which are the initial values before this switching over transition. After switching over to State III, the capacitors settle down to the following new voltages:

$$V_{C2} = V_{C4} = V_3 - V_2$$

=  $V_0 - 0.1376\Delta_1 + 0.45\Delta_2 + 0.6875\Delta_3 + 0.12\Delta$  (23)

$V_{C1} = V_{C3} = V_{C5} = V_2 - V_1$

=  $V_0 + 0.3751\Delta_1 + 0.5\Delta_2 + 0.125\Delta_3 - 0.009\Delta$  (24)

$$V_{C0} = V_{C6} = V_1$$

=  $V_0 + 0.7624\Delta_1 + 0.05\Delta_2 + 0.1875\Delta_3 - 0.111\Delta.(25)$

# E. At the End of State III

At the beginning of State III, the voltages are expressed in (23)–(25). Similarly, after T/3 at the end of State III the voltages become

$$V_{C2} = V_{C4} = V_3 - V_2$$

=  $V_0 - 0.1376\Delta_1 + 0.45\Delta_2 + 0.6875\Delta_3 + 0.1825\Delta$

(26)

$$V_{C1} = V_{C3} = V_{C5} = V_2 - V_1$$

=  $V_0 + 0.3751\Delta_1 + 0.5\Delta_2 + 0.125\Delta_3 - 0.0327\Delta$  (27)

$V_{C0} = V_{C6} = V_1$

=  $V_0 + 0.7624\Delta_1 + 0.05\Delta_2 + 0.1875\Delta_3 - 0.2152\Delta.$

(28)

## F. At the Transition From State III to State I

Now consider the transition from State III back to State I. The equivalent circuits of State I have been shown in Fig. 17. Before State I (i.e., at the end of State III), the capacitors' voltages are expressed in (26)–(28), which are the initial values before the switching over transition. After switching over to State I, the capacitors settle down to new voltages as follows:

$$V_{C4} = V_3 - V_2$$

=  $V_0 - 0.12\Delta_1 + 0.3357\Delta_2 + 0.5446\Delta_3$

+  $0.0682\Delta$  (29)

Fig. 20. Parallel connection resulting from State I to II switchover.

$$V_{C0} = V_{C2} = V_{C5} = V_2 - V_1$$

=  $V_0 + 0.2474\Delta_1 + 0.4178\Delta_2 + 0.3348\Delta_3$

+  $0.05\Delta$  (30)

$$V_{C0} = V_{C1} = V_{C3} = V_{C6} = V_1$$

=  $V_0 + 0.6331\Delta_1 + 0.2464\Delta_2 + 0.12055\Delta_3$

-  $0.12\Delta$ . (31)

#### G. Solution of the Voltages

After one cycle, the voltages come back to the beginning of State I. Therefore, (29)–(31) should equal (8)–(10), respectively. From (8)–(12) and (29)–(31), we get the following equations:

$$V_0 + \Delta_3 = V_0 + 0.12\Delta_1 + 0.3357\Delta_2 + 0.5446\Delta_3 + 0.0682\Delta$$

(32)

$$V_0 + \Delta_2 = V_0 + 0.2474\Delta_1 + 0.4178\Delta_2$$

$$+0.3348\Delta_3 + 0.05\Delta$$

(33)

$$\Delta_1 + \Delta_2 + \Delta_3 = 0. \tag{34}$$

Solving the above three equations, we have

$$\Delta_1 = -0.223\Delta,\tag{35}$$

$$\Delta_2 = 0.076\Delta \tag{36}$$

$$\Delta_3 = 0.147\Delta. \tag{37}$$

Therefore, the voltages are

$$V_3 - V_2 = V_0 + 0.147\Delta, \tag{38}$$

$$V_2 - V_1 = V_0 + 0.076\Delta, \tag{39}$$

$$V_1 = V_0 - 0.223\Delta.$$

(40)

# H. Power Loss Calculation

When connecting together capacitors with different voltages power loss always occurs. There are the following five instances per switching cycle.

1) C1–C2–C5 Connection From State I to State II (Fig. 20): Before the switching-over transition of State I to State II, capacitors C1, C2, and C5's voltages are expressed in (14) and (15). After the switching over, they settle down to a new voltage and become (18). In this case, C1 has a different voltage from C2 and C5 before the connection. The energy loss at this connection is  $(1/3) C\delta_i^2$ , where  $\delta_i$  is the voltage difference between the two initial voltages. The voltage difference between (14) and (15) is

$$\delta_i = 0.394\Delta. \tag{41}$$

Therefore, the energy loss at this switching-over transition is

$$E_i = \frac{1}{3}C\delta_i^2 = 0.052C\Delta^2.$$

(42)

Fig. 21. Parallel connection resulting from State II to III switchover.

Fig. 22. Another parallel connection resulting from State II to III switchover.

Fig. 23. Parallel connection resulting from State III to I switchover.

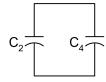

2) C2–C4 Connection From State II to State III (Fig. 21): Before this switching-over transition, capacitors C2 and C4's voltages are expressed in (20) and (21). After the switching over, they become (23). The energy loss in this case—two capacitors with two different voltages connected together is  $(1/4) C\delta_{ii}^2$ , where  $\delta_{ii}$  is the voltage difference between the two initial voltages. The voltage difference between (20) and (21) is

$$\delta_{ii} = 0.3233\Delta. \tag{43}$$

Therefore, the energy loss is

$$E_{ii} = \frac{1}{4}C\delta_{ii}^2 = 0.026C\Delta^2.$$

(44)

3) C1–C3–C5 Connection From State II to State III (Fig. 22): Before the switching-over transition, capacitors C1, C3, and C5's voltages are expressed in (21) and (22). After the switching over, their voltages become (24). Similarly, the voltage difference between (21) and (22) is

$$\delta_{iii} = 0.3734\Delta. \tag{45}$$

Therefore, the energy loss is

$$E_{iii} = \frac{1}{3}C\delta_{iii}^2 = 0.047C\Delta^2.$$

(46)

4) C2-C5 Connection From State III to State I (Fig. 23): Before the switching-over transition, capacitors C2 and C5's voltages are expressed in (26) and (27). After the switching over, they become (30). The voltage difference between (26) and (27) is

$$\delta_{iv} = 0.343\Delta. \tag{47}$$

Therefore, the energy loss is

$$E_{iv} = \frac{1}{4}C\delta_{iv}^2 = 0.029C\Delta^2.$$

(48)

5) C0–C1–C3–C6 Connection From State III to State I (Fig. 24): Before the switching-over transition, capacitors C0, C1, C3, and C6's voltages are expressed in (27) and (28). After

Fig. 24. Another parallel connection resulting from State III to I switchover.

the switching over, they become (31). The voltage difference between (27) and (28) is

$$\delta_v = 0.359\Delta. \tag{49}$$

Therefore, the energy loss is

$$E_v = \frac{1}{2}C\delta_v^2 = 0.064C\Delta^2.$$

(50)

The total loss over one cycle is

$$E = \sum_{j=i}^{v} E_j = 0.218C\Delta^2 \tag{51}$$

and the power loss for a switching frequency of f is

$$P_{\text{Cap-loss}} = E \cdot f = 0.218 \frac{I_L^2}{C \cdot f}.$$

(52)

## REFERENCES

- F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Trans. Ind. Applicat.*, vol. 37, pp. 611–618, Mar./Apr. 2001.

- [2] X. Yuan, I. Barbi, and H. Stemmler, "A new diode clamping multilevel inverter," in *Proc. IEEE APEC'99*, 1999, pp. 494–501.

- [3] J. S. Lai and F. Z. Peng, "Multilevel converters—a new breed of power converters," *IEEE Trans. Ind. Applicat.*, vol. 32, pp. 509–517, May/June 1996.

- [4] F. Z. Peng and J. S. Lai, "A static var generator using a staircase waveform multilevel voltage source converter," in *Proc. Seventh Int. Power Quality Conf.*, Dallas/Ft. Worth, TX, Sept. 17–22, 1994, pp. 58–66.

- [5] C. Hochgraf, R. Lasseter, D. Divan, and T. A. Lipo, "Comparison of multilevel inverters for static var compensation," in *Conf. Rec. IEEE-IAS Annu. Meeting*, 1994, pp. 921–928.

- [6] F. Z. Peng, J. S. Lai, J. McKeever, and J. Vancoevering, "A multilevel voltage-source converter system with balanced DC voltages," in *Proc. IEEE PESC'95*, Atlanta, GA, 1995, pp. 1144–1150.

- [7] J. Menzies, P. Steimer, and J. K. Steike, "Five level GTO inverters for large induction motor drives," in *Conf. Rec. IEEE-IAS Annu. Meeting*, 1993, pp. 595–601.

- [8] X. Yuan, H. Stemmler, and I. Barbi, "Investigation of the clamping voltage self-balancing of the three-level capacitor clamping inverter," in *Proc. IEEE PESC'99*, 1999, pp. 1059–1064.

- [9] J. S. Brugler, "Theoretical performance of voltage multiplier circuits," *IEEE J. Solid-State Circuits*, vol. 6, pp. 132–135, June 1971.

- [10] P. M. Lin and L. O. Chua, "Topological generation and analysis of voltage multiplier circuits," *IEEE Trans. Circuits Syst.*, vol. CAS-24, pp. 517–530, Oct. 1977.

- [11] L. Malesani and R. Piovan, "Theoretical performance of capacitor-diode voltage multiplier fed by a current source," *IEEE Trans. Power Electron.*, vol. 8, pp. 147–155, Apr. 1993.

- [12] A. Lamantia, P. G. Maranesi, and L. Radrizzani, "Small-signal model of the Cockcroft-Walton voltage multiplier," *IEEE Trans. Power Electron.*, vol. 9, pp. 18–25, Jan. 1994.

- [13] K. D. T. Ngo and R. Webster, "Steady-state analysis and design of a switched-capacitor DC-DC converter," in *Proc. IEEE PESC'92*, 1992, pp. 378–385.

- [14] J. G. Kassakian, "Automotive electrical systems—The power electronics market of the future," in *Proc. IEEE APEC*, 2000, pp. 3–9.

- [15] J. M. Miller and A. R. Gale, "Hybrid electric vehicle success will depend on low cost, efficient power electronics systems," *Power Conversion Intell. Motion*, vol. 23, no. 11, pp. 22–38, Nov. 1997.

Fang Zheng Peng (M'92–SM'96) received the B.S. degree from Wuhan University, Wuhan, China, in 1983, and the M.S. and Ph.D. degrees from Nagaoka University of Technology, Nagaoka, Japan, in 1987 and 1990, respectively, all in electrical engineering.

From 1990 to 1992, he was a Research Scientist with Toyo Electric Manufacturing Company, Ltd., engaged in research and development of active power filters, flexible ac transmission systems (FACTS) applications, and motor drives. From 1992 to 1994, he was a Research Assistant Professor with

Tokyo Institute of Technology, where he initiated a multilevel inverter program for FACTS applications and a speed-sensorless vector control project. From 1994 to 2000, he was with Oak Ridge National Laboratory (ORNL) and, from 1994 to 1997, he was a Research Assistant Professor at the University of Tennessee, Knoxville. He was a Staff Member and Lead (Principal) Scientist of the Power Electronics and Electric Machinery Research Center at ORNL from 1997 to 2000. In 2000, he joined Michigan State University, East Lansing, as an Associate Professor in the Department of Electrical and Computer Engineering. He is also currently a specially invited Adjunct Professor at Zhejiang University, Hangzhou, China. He is the holder of ten patents.

Dr. Peng has received numerous awards, including the 1996 First Prize Paper Award and the 1995 Second Prize Paper Award from the Industrial Power Converter Committee at the IEEE Industry Applications Society Annual Meeting; the 1996 Advanced Technology Award of the Inventors Clubs of America, Inc., the International Hall of Fame; the 1991 First Prize Paper Award from the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS; the 1990 Best Paper Award from the *Transactions of the Institute of Electrical Engineers of Japan*; and the Promotion Award of the Electrical Academy. He has been an Associate Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS since 1997 and Chair of the Technical Committee for Rectifiers and Inverters of the IEEE Power Electronics Society.

**Fan Zhang** was born in Haining, China, in 1976. He received the B.S. degree in electrical engineering in 1999 and the M.S. degree from Zhejiang University, Hangzhou, China, where he is currently working toward the Ph.D. degree in electrical engineering.

Since January 2002, he has been a Visiting Scholar at Michigan State University, East Lansing. His research interests include soft-switching, dc–dc converters, and inverters.

**Zhaoming Qian** (SM'92) graduated in radio engineering from the Electrical Engineering Department, Zhejiang University, Hangzhou, China, in 1961, and received the Ph.D. degree in applied science from the Catholic University of Leuven, Leuven, Belgium, and the Interuniversity Microelectronics Center (IMEC), Leuven, Belgium, in 1989.

Since 1961, he has been teaching and conducting research on electronics, electronic measurements, photovoltaic, and power electronics at Zhejiang University, where he became a Professor in the Elec-

trical Engineering Department in 1992. He was also the Director of the Power Electronics Research Institute until 2000. He is currently the Deputy Director of the National Engineering Research Center for Applied Power Electronics and the Deputy Director of the Scientific Committee of the National Key Laboratory of Power Electronics at Zhejiang University. His main professional interests include power electronics and industrial applications, as well as EMC in power electronic systems. He has authored one book on EMC design and more than 200 papers.

Dr. Qian received Excellent Education Awards from the China Education Commission and from Zhejiang University in 1993, 1997, and 1999, the Science and Technology Development Award from the China Education Commission in 1999, and several Excellent Paper Awards. He has served as a Vice-Chairman of the IEEE Power Electronics Society Beijing Chapter since 1995.