Open access • Journal Article • DOI:10.1007/BF01189337

### A methodology for designing, modifying, and implementing Fourier transform algorithms on various architectures — Source link

Jeremy Johnson, R. W. Johnson, D. Rodriquez, R. Tolimieri

Institutions: Ohio State University, City University of New York, City College of New York

Published on: 01 Oct 1990 - Circuits Systems and Signal Processing (Birkhauser Boston Inc.)

Topics: Fourier transform, Tensor (intrinsic definition), Cooley-Tukey FFT algorithm, Fast Fourier transform and Tensor product

#### Related papers:

- An algorithm for the machine calculation of complex Fourier series

- SPIRAL: Code Generation for DSP Transforms

- The Design and Implementation of FFTW3

- · An Adaptation of the Fast Fourier Transform for Parallel Processing

- · SPL: a language and compiler for DSP algorithms

### A Methodology for Designing, Modifying, and Implementing Fourier Transform Algorithms on Various Architectures

J. Johnson

Department of Computer Science, The Ohio State University

R. W. Johnson Department of Computer Science, CUNY Graduate Center

D. Rodriguez

Department of Electrical Engineering, The City College of New York

$$\rm R.~Tolimieri$  Department of Electrical Engineering, The City College of New York

This work was performed at the Center for Large Scale Computation\* 25 West 43rd Street Suite 400 New York, NY 10036

8 September 1989

<sup>\*</sup>Supported by a grant from DARPA/ACMP

#### Contents

| 1 | Introduction                                                                                                                                                                                                                                                                                                      | 1                    |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2 | Tensor Products                                                                                                                                                                                                                                                                                                   | 3                    |

| 3 | Commuting Tensor Products and Stride Permutations                                                                                                                                                                                                                                                                 | 7                    |

| 4 | Implementing Tensor Products         4.1       Factorization of Tensor Products and Implications for Various Architectures         4.2       Programming Tensor Product Factorizations         4.3       Modifying the Implementation to Parallel Architectures         4.4       The Cray X-MP: A Design Example | 13<br>15<br>21<br>25 |

| 5 | What is the Finite Fourier Transform?  5.1 An Algorithm for Computing the Fourier Transform  5.2 Variations on Cooley-Tukey: Parallelized and Vectorized FT Algorithms                                                                                                                                            | <b>35</b> 36 41      |

| 6 | Some Notes on Code Generation and a Special Purpose Compiler                                                                                                                                                                                                                                                      | 43                   |

| 7 | Summary                                                                                                                                                                                                                                                                                                           | 46                   |

| A | Appendix: A Loop Implementation of the FT on the AT&T DSP32                                                                                                                                                                                                                                                       | 49                   |

#### 1 Introduction

Shortly after Cooley and Tukey (C-T) introduced their algorithm for computing the Fourier transform (FT) [6], a large number of variations were created and this work was summarized by Cochran et al. in [5]. In this paper a method of obtaining variations of the C-T algorithm was presented, and it was conjectured this produced all of the "C-T type" algorithms. Within a year Pease [13] introduced an algorithm not based on this method. In the introduction to Pease's paper he suggested strongly that the tensor product formulation was a valuable tool in the study of C-T type algorithms. This was not taken up at this time due to the great success of the "butterfly" as a teaching and programming device.

With the advent of parallel and vector processors, there began another flurry of C-T algorithmic and programming effort. In much of this effort no use of the tensor product was made. However, in their comparison of several vector algorithms [11], Korn and Lambiotte make a slight use of tensor products as a tool. The most successful programming of the FT on vector computers like

the CRAY X-MP and Cyber 205 is due to C. Temperton [18, 19, 20]. In his expository paper [21] he places the tensor product at center stage. This paper was written for numerical physicists and is not familiar to the Electrical Engineering and Computer Science communities. In our paper we again place the tensor product at center stage, but we extend Temperton's work by presenting a detailed study of the permutations associated with tensor products – stride permutations – and their relation to the addressing requirements in the C-T type algorithms. We also make explicit the relationship of tensor products and stride permutations to the programming of these algorithms on various architectures.

Tensor products offer a natural language for expressing C-T type algorithms. In the first section, we introduce tensor products from a point of view best suited to our algorithmic and programming needs. We emphasize a decomposition which leads to an efficient evaluation of a tensor product on a vector. We also give several isomorphisms which make explicit the connections between various viewpoints of the C-T algorithms. These isomorphisms are later used to construct the indexing needed to program these algorithms.

Closely associated with tensor products are a class of permutations, containing stride permutations and tensor products of stride permutations, which govern the addressing between the stages of a tensor product decomposition. These permutations arise as a permutation of a tensor product basis. From a programming point of view these permutations interchange the order of the nested loops used to program a tensor product factorization. Some previous discussion of these permutations from a different point of view was given by Swartztrauber in his expository papers [16] and [17]. It is these permutations that are the basis of all variations of the C-T algorithm.

After introducing tensor products and the associated permutations, we give a direct method for programming tensor product factorizations. Once the programming of tensor products is made explicit, we can systematically study various ways of optimizing an implementation and modifying it to a specific architecture. The basic idea is to obtain a natural loop implementation based on tensor product identities and then to unroll some of the loops to match specific instruction sets. Furthermore, various factorizations of the permutations that arise can be used to adapt the algorithm to the specific addressing capabilities of a given architecture. In particular, in section 4.4 we give a detailed study of the implementation of tensor products on the CRAY X-MP [2]. Using tensor product and permutation identities, we obtain a vectorized segmented algorithm that uses addressing that can be efficiently implemented on this machine. Finally, using the programming techniques discussed earlier we obtain a program that implements this algorithm. In [7] Granata and Rofheart use some of these ideas to obtain an efficient implementation of a 1K FT on the AT&T DSP32 [3]. By performing various compile time optimizations that we will discuss in section 4.2 they were able to save the cost of run time permutations. This savings helped them to achieve a program that was twice as fast as the distributed FFT.

In the remaining sections, we show how tensor products can be used in the design and implementation of FT algorithms. The derivation of the standard variations of the C-T algorithm using the tensor product and permutation language discussed in this paper was presented by Rodriguez in his thesis [14].

At the end of the paper, we give some ideas on automating the techniques presented. Essentially, the algebraic properties of tensor products and stride permutations need to be incorporated into a special purpose compiler which can automatically generate code to implement various C-T algorithms. Ideally, heuristics could be added to derive an algorithm suited to a given architecture. With such a compiler, an environment would be created for easily implementing and modifying FT algorithms on various architectures.

#### 2 Tensor Products

In this section we introduce some of the basic properties of tensor products which will play a major role in the design and implementation of FT algorithms. The formalism of tensor product notation can be used to keep track of the complex index calculation needed in FT algorithms. This property of the formalism can be used to aid in program design and verification. If the mapping between tensor product notation and machine instructions is automated, mathematical properties of tensor products can be used to guarantee the correctness of the implementation. Furthermore, tensor product identities can be used to directly transform the corresponding programs.

We begin with some definitions and some identifications which will allow us to look at tensor products from several perspectives. Let  $C^n$  denote the n-dimensional vector space of n-tuples of complex numbers. The collection of vectors with a one in the i-th position and zeros elsewhere form the standard basis for this vector space. We use  $e^n_i$  to denote such a vector. The superscript n indicates the size of the vector. Furthermore we let i range from 0 to n-1. We will also use  $x^n$  to denote an arbitrary n-dimensional vector.

We can form the tensor product  $C^m \otimes C^n$  of the vector spaces  $C^m$  and  $C^n$  to get an mn-dimensional vector space with basis  $\{e_i^m \otimes e_j^n | 0 \le i < m-1, 0 \le j < n-1\}$ . We can associate this vector space with  $C^{mn}$  by ordering the basis lexicographically. This gives the following map

$$e_i^m \otimes e_j^n \longleftrightarrow e_{in+j}^{mn},$$

(1)

which relates tensor products to mixed-radix indices. Let

$$x^m = \begin{pmatrix} x_0 \\ \vdots \\ x_{m-1} \end{pmatrix} = \sum_{0 \le i < m} x_i e_i^m,$$

and

$$y^{n} = \begin{pmatrix} y_{0} \\ \vdots \\ y_{n-1} \end{pmatrix} = \sum_{0 \le j < n} y_{j} e_{j}^{n}.$$

Then using the bilinearity of the tensor product and this map we have

$$x^m \otimes y^n = \sum_{0 \le i < m} x_i y_j (e_i^m \otimes e_j^n) = \sum x_i y_j e_{in+j}^{mn} = \begin{pmatrix} x_0 y^n \\ \vdots \\ x_{m-1} y^n \end{pmatrix}.$$

This mn-dimensional vector can be mapped to an  $m \times n$  matrix by placing the segments  $x_i y$  of n elements in consecutive rows. For example,

$$x^m \otimes y^n \to \begin{pmatrix} x_0 y_0 & \cdots & x_0 y_{n-1} \\ \vdots & \ddots & \vdots \\ x_{m-1} y_0 & \cdots & x_{m-1} y_{n-1} \end{pmatrix}.$$

This operation identifies the vector space  $C^m \otimes C^n$  with the vector space  $C^{m,n}$  of  $m \times n$  matrices. The standard basis for  $C^{m,n}$  is  $\{E^{m,n}_{i,j} | 0 \le i < m, \ 0 \le j < n\}$ , where  $E^{m,n}_{i,j}$  is the  $m \times n$  matrix with a one in the (i,j)-th position and zeros elsewhere. Using these basis elements, the preceding operation can be written as

$$e_i^m \otimes e_j^n \longleftrightarrow E_{i,j}^{m,n}.$$

(2)

We can extend this map to act on an arbitrary mn-dimensional vector by placing consecutive segments of n elements in m consecutive rows. This identifies the vector space  $C^{mn}$  with  $C^{m,n}$  by associating the basis vectors with the map

$$e_{in+j}^{mn} \longleftrightarrow E_{i,j}^{m,n}.$$

(3)

The inverse map which takes an  $m \times n$  matrix to an mn-dimensional vector by placing consecutive rows after each other is the same map that is used to store a two-dimensional array in linear memory. Clearly this entire discussion could have been carried out based on anti-lexicographic ordering, which would have given the column method of storing arrays that is used in FORTRAN, instead of the row major ordering used in languages like Pascal. In the next section we will study an important permutation which allows one to go back and forth between these two representations.

We can extend the definition of the tensor product of vectors to a tensor product of linear transformations by the following definition.

**Definition 1**

$$(A \otimes B)(x \otimes y) = Ax \otimes By$$

,

where A and B are linear transformations on the appropriate dimensional vector spaces. If A and B are represented by matrices with respect to the standard

basis and are of dimensions m and n respectively, we have the following matrix picture

$$A \otimes B = \begin{pmatrix} a_{0,0}B & \cdots & a_{0,m-1}B \\ \vdots & \ddots & \vdots \\ a_{m-1,0}B & \cdots & a_{m-1,m-1}B \end{pmatrix}.$$

This block structured matrix, which replaces each element of the first matrix A by that element times the second matrix B is called the tensor product of two matrices (sometimes it is called the Kronecker product).

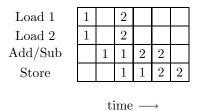

The action of the matrix  $A \otimes B$  on an arbitrary mn-dimensional vector can be performed efficiently with the aid of the following decomposition

$$A \otimes B = (A \otimes I_n)(I_m \otimes B) = (I_m \otimes B)(A \otimes I_n), \tag{4}$$

where  $I_n$  and  $I_m$  are n and m dimensional identity matrices. This decomposition is a corollary of the multiplication rule for tensor products.

**Theorem 1 (Multiplication Rule For Tensor Products)**  $(A \otimes B)(C \otimes D) = AC \otimes BD$ , where A and C are  $m \times m$  matrices and B and D are  $n \times n$  matrices.

This follows immediately from the definition since

$$(A \otimes B)(C \otimes D)(e_i^m \otimes e_j^n)$$

$$= (A \otimes B)(Ce_i^m \otimes De_j^n)$$

$$= (AC)e_i^m \otimes (BD)e_i^n.$$

Applying this identity to  $A \otimes B = AI_m \otimes I_n B = I_m A \otimes BI_n$  gives the decompositions in equation (4). This multiplication rule and its implications are the most important tools in the design of efficient algorithms for computing with tensor products.

In order to better understand the computation of  $(A \otimes B)x$  we need to examine the factors  $I_m \otimes B$  and  $A \otimes I_n$  that arise in decomposition (4).  $I_m \otimes B$  is the direct sum of m copies of B

$$I_m \otimes B = \left( \begin{array}{ccc} B & & \\ & \ddots & \\ & & B \end{array} \right),$$

and its action on x is performed by computing the action of B on the m consecutive segments of size n. Clearly this direct sum can be computed in parallel on separate segments of the vector x, hence we will call it a parallel tensor product term.

An alternative view of this computation can be obtained if we map x to the matrix X using equation (3). In this case B acts on the rows of the matrix.

$$X = \begin{pmatrix} x_0 & \cdots & x_{n-1} \\ x_n & \cdots & x_{2n-1} \\ \vdots & \ddots & \vdots \\ x_{(m-1)n} & \cdots & x_{mn-1} \end{pmatrix}.$$

Since matrices usually act on column vectors, we must first transpose X, let B act on the columns and then transpose the result to return to our row representation. Thus the computation is given by the following matrix multiplication  $(BX^t)^t = XB^t$ , which can be mapped back to a vector using the inverse of the previous map.

The factor  $A \otimes I_n$  can be interpreted as a vector operation on vectors of length n.

$$A \otimes I_n = \begin{pmatrix} a_{0,0}I_n & \cdots & a_{0,m-1}I_n \\ \vdots & \ddots & \vdots \\ a_{m-1,0}I_n & \cdots & a_{m-1,m-1}I_n \end{pmatrix}.$$

The action of  $A \otimes I_n$  can be interpreted as a vector operation if we segment the input vector x into m consecutive segments of length n. If we let  $X_i$  denote the i-th such segment, then  $(A \otimes I_n)x$  is the following vector operation

$$\begin{pmatrix} a_{0,0}X_0 + \dots + a_{0,m-1}X_{m-1} \\ \vdots \\ a_{m-1,0}X_0 + \dots + a_{m-1,m-1}X_{m-1} \end{pmatrix},$$

where  $a_{i,j}X_j$  denotes a scalar-vector multiply and + denotes a vector addition. This computation is just the evaluation of A on vector segments of length n.

An alternative interpretation of this computation results from the matrix point of view. In this case, A naturally acts on the columns of the matrix X giving the computation AX. The two factors  $I_m \otimes B$  and  $A \otimes I_n$  are related by changing from a row representation of X to a column representation of X.

Thus the computation of  $(A \otimes B)x$  can be thought of as a parallel operation followed by a vector operation, or more conventionally as the matrix operation  $Y = A(XB^t)$ , where the result is obtained from the rows of the matrix Y. Clearly the order of these two operations could be interchanged, as indicated by the two forms of the decomposition in equation (4), or by the associativity of matrix multiplication. Furthermore, the computation of the two types of factors  $A \otimes I_n$  and  $I_m \otimes B$  are identical up to a change of representation given by the transpose of the matrix X.

In terms of the vector x, this change of representation is obtained by a permutation, called a stride permutation, that skips over the segments representing the rows or columns. This permutation governs the addressing needed in the

implementation of the factors  $A \otimes I$  and  $I \otimes B$ . Further discussion of these permutations and their implementation will be given in the next section.

Before discussing stride permutations, we need to show how to extend tensor products to arbitrarily many factors, and thus give a natural setting for multidimensional problems. The way to proceed is by induction from the two-dimensional case. For example,

$$(A_1 \otimes A_2 \otimes A_3)(x \otimes y \otimes z) = (A_1 \otimes A_2)(x \otimes y) \otimes A_3z = A_1x \otimes A_2y \otimes A_3z,$$

where  $A_1$ ,  $A_2$ , and  $A_3$  are  $m \times m$ ,  $n \times n$ , and  $p \times p$  matrices and x, y, and z are m, n, and p dimensional vectors respectively. In order for this to make sense, it is essential that the tensor product be associative. From our point of view this reduces to an index computation that is related to the induction used to store multidimensional arrays. Namely, to show that  $A_1 \otimes A_2 \otimes A_3$  is associative we use the associativity of  $x \otimes y \otimes z$ , and to show that  $x \otimes y \otimes z$  is associative we compute

$$\begin{split} (e_i^m \otimes e_j^n) \otimes e_k^p &= e_{in+j}^{mn} \otimes e_k^p = e_{(in+j)p+k}^{mnp} \\ &= e_i^m \otimes (e_j^n \otimes e_k^p) = e_i^m \otimes e_{jp+k}^{np} = e_{inp+jp+k}^{mnp}. \end{split}$$

Using associativity we can uniquely define the tensor product of n terms by induction. This recursive definition makes it easy to inductively derive and program factorizations of tensor products, which can be used to compute multiple tensor products. In section 4.1 we will examine several important factorizations and their programming implications.

# 3 Commuting Tensor Products and Stride Permutations

In this section the permutations that arise from commuting tensor products will be studied. The ability to commute tensor products is essential to modifying tensor product factorizations and hence modifying algorithms for computing with tensor products. As pointed out previously, stride permutations can be used to convert the parallel operation  $I \otimes A$  to the vector operation  $A \otimes I$ . Alternatively these permutations can be thought of as converting a row representation of a matrix to a column representation, or in other words transposing a matrix.

A stride permutation P(mn, n) is defined by

#### Definition 2 (Stride Permutation)

$$P(mn,n)e_i^m \otimes e_i^n = e_i^n \otimes e_i^m$$

To get an  $mn \times mn$  matrix representation of this permutation, observe that  $P(mn, n): e_{in+j}^{mn} \longrightarrow e_{jm+i}^{mn}$ . For example,

$$P(6,2)(x_0e_0+x_1e_1+x_2e_2+x_3e_3+x_4e_4+x_5e_5) = x_0e_0+x_1e_3+x_2e_1+x_3e_4+x_4e_2+x_5e_5.$$

As a matrix computation, this can be written as:

$$P(6,2)x = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \end{pmatrix} = \begin{pmatrix} x_0 \\ x_2 \\ x_4 \\ x_1 \\ x_3 \\ x_5 \end{pmatrix}.$$

Thus we see that the elements of x are collected at stride two into two consecutive segments containing three elements each. The first segment begins with  $x_0$ , and the second segment begins with  $x_1$ . In general, P(mn, n) reorders the coordinates at stride n into n consecutive segments of m elements; the i-th segment beginning with  $x_{i-1}$ . This reordering of the coordinates corresponds to the inverse of the permutation of the basis elements. A physical interpretation of such a reordering can be observed when a deck of mn cards are dealt into n piles.

On some machines the action of a stride permutation might be implemented as elements of the input vector are loaded from main memory into registers. For example, each segment might be loaded at the appropriate stride into a separate register beginning at the appropriate offset. For architectures where this is the case, considerable savings can be obtained by performing these permutations when loading the input vector into the registers. If it is necessary to load the input vector to perform some arithmetic operation, and the permutation is performed during this load, then a separate computation of the permutation can be avoided. In section 4.4, we will see an architecture where these savings can be obtained. There will also be a discussion of the implementation of stride permutations on that machine.

Because of this interpretation, we use  $L_n^{mn}$  to denote the stride permutation P(mn,n). This notation indicates that a vector of size mn is reordered by loading into n segments at stride n. Shortly, we will see that the inverse of the stride permutation P(mn,n) is the stride permutation P(mn,m). Along the lines of the load interpretation of P(mn,n), there is an interpretation of  $P(mn,n)^{-1}$  as a store operation. In this case, n consecutive segments, residing in n registers, are stored back to memory at stride n with the i-th segment beginning i positions from the first segment. It is clear that a load operation followed by the inverse store operation leaves the input vector fixed. Similarly to the L notation used for the load operation, we use  $S_n^{mn}$  to denote the inverse store operation. Even though  $(L_n^{mn})^{-1} = L_m^{mn} = S_n^{mn}$  all denote the same permutation, the notational distinction will be important when we are concerned

with implementation. Even when we are not concerned with the implementation of these permutations, we will use the L and S notation to help keep track of the indices. For example, the definition of P(mn,n) can be conveniently remembered with

$$L_n^{mn}(x^m \otimes x^n) = x^n \otimes x^m. \tag{5}$$

An alternative view of these permutations as a change of representation arises from the matrix representation of  $e_i^m \otimes e_j^n$ . In this case,  $L_n^{mn} E_{i,j}^{m,n} = E_{j,i}^{n,m} = (E_{i,j}^{m,n})^t$ . Thus we see that a stride permutation effects a transposition. In other words, it collects terms by striding over the segments storing the rows of a matrix. For example, if we map a vector x containing 6 elements to the matrix

$$X = \left(\begin{array}{cc} x_0 & x_1 \\ x_2 & x_3 \\ x_4 & x_5 \end{array}\right),$$

then

$$X^t = \left(\begin{array}{ccc} x_0 & x_2 & x_4 \\ x_1 & x_3 & x_5 \end{array}\right)$$

gets mapped to the vector  $L_2^6x$ .

The most important property of stride permutations is that they commute the factors in the tensor product of matrices. Using this property we will be able to show, as indicated in the last section, that

$$A \otimes B = L_m^{mn}(I_n \otimes A)L_n^{mn}(I_m \otimes B). \tag{6}$$

so that both factors in the decomposition can be performed as a loop, which is indicated by the direct sum interpretation of  $I \otimes A$ . In order to do this it is necessary to perform a change of basis by a stride permutation, which corresponds to changing from row representation to column representation. This change of basis is given in the following commutation theorem.

**Theorem 2 (Commutation Theorem)**  $L_n^{mn}(A \otimes B) = (B \otimes A)L_n^{mn}$  where A is an  $m \times m$  matrix and B is an  $n \times n$  matrix. In other words  $B \otimes A = L_n^{mn}(A \otimes B)(L_n^{mn})^{-1}$ .

The proof is nothing more than a simple computation based on the definition.

$$L_n^{mn}(A \otimes B)(e_i^m \otimes e_j^n) = L_n^{mn}(Ae_i^m \otimes Be_j^n) = Be_j^n \otimes Ae_i^m$$

Similarly

$$(B\otimes A)L_n^{mn}(e_i^m\otimes e_j^n)=(B\otimes A)(e_j^n\otimes e_i^m)=Be_j^n\otimes Ae_i^m.$$

As an application of the commutation theorem observe that  $A \otimes I_n = (L_n^{mn})^{-1}(I_n \otimes A)L_n^{mn} = S_n^{mn}(I_n \otimes A)L_n^{mn}$ . The readdressing denoted by  $L_n^{mn}$  on input and  $S_n^{mn}$  on output turns the vector expression  $A \otimes I_n$  into the parallel

expression  $I_n \otimes A$ . In the same way,  $I_m \otimes B = (L_n^{mn})^{-1}(B \otimes I_m)L_n^{mn}$ , which turns the parallel expression  $I_m \otimes B$  into the vector expression  $B \otimes I_m$ . As promised, we can now write  $A \otimes B$  as

$$(A \otimes I_n)(L_n^{mn})^{-1}(B \otimes I_m)L_n^{mn} \tag{7}$$

or

$$(L_n^{mn})^{-1}(I_n \otimes A)L_n^{mn}(I_m \otimes B). \tag{8}$$

Using the fact that  $(L_n^{mn})^{-1} = L_m^{mn}$ , we can write these factorizations as

$$(A \otimes I_n) L_m^{mn} (B \otimes I_m) L_n^{mn}, \tag{9}$$

and

$$L_m^{mn}(I_n \otimes A)L_n^{mn}(I_m \otimes B). \tag{10}$$

These factorizations decompose  $A\otimes B$  into a sequence of vector operations and parallel operations respectively. The intervening stride permutations provide a mathematical language for describing the readdressing between the stages of the computation. In the next two sections we will show how knowledge of these permutations can be used to implement the addressing of a tensor product factorization on a variety of architectures. Furthermore, the direct interpretations of  $A\otimes I$  as a vector operation and  $I\otimes B$  as a parallel operation along with the commutation theorem will allow us to automatically derive parallel and vector algorithms.

Before examining the implementation of stride permutations and the use of the commutation theorem in deriving various tensor product factorizations, we need to obtain a better understanding of these permutations. The algebra of stride permutations is especially rich and will serve as an important tool in algorithm design. We begin with a multiplication rule, which can be expressed formally with our notation as:

**Theorem 3** If

$$N = rst$$

then  $L_{st}^N = L_s^N L_t^N$

Proof: First observe that  $L_{st}^N(x^r \otimes x^s \otimes x^t) = x^s \otimes x^t \otimes x^r$ . Since also  $L_s^N L_t^N(x^r \otimes x^s \otimes x^t) = L_s^N(x^t \otimes x^r \otimes x^s) = x^s \otimes x^t \otimes x^r$ , the theorem is proved. In particular, since  $L_N^N = I_N$ , we have  $L_n^N L_{N/n}^N = I_N$ , so that  $(L_n^N)^{-1} = X_n^N L_{N/n}^N = I_N$ .

In particular, since  $L_N^N = I_N$ , we have  $L_N^N L_{N/n}^N = I_N$ , so that  $(L_N^N)^{-1} = L_{N/n}^N$ . Since in general the inverse of a permutation matrix is the transpose we have that  $L_{N/n}^N = (L_n^N)^t$ . For example,

$$(L_2^6)^{-1} = (L_2^6)^t = L_3^6 = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix}.$$

As a simple application of theorem 3 we get

Corollary 1 If  $N = p^k$ , the set of stride permutations corresponding to the divisors of N,

$\{L_{n^j}^N: 0 \le j < k\},\$

form a cyclic group of order k generated by  $L_p^N$ .

The second type of theorem of importance in the algebra of stride permutations is a tensor product decomposition of stride permutations. In general, the permutations that arise from commuting terms in a multidimensional tensor product are built up from products of terms of the form  $I \otimes L \otimes I$ . A permutation of the form  $I \otimes L \otimes I$  will commute a tensor product and fix the remaining terms to the left and right. For example,

$$(A_{n_1} \otimes \cdots A_{n_i} \otimes A_{n_{i+1}} \otimes \cdots \otimes A_{n_t})$$

$$= (I_{n_1 \cdots n_{i-1}} \otimes L_{n_i}^{n_i n_{i+1}} \otimes I_{n_{i+2} \cdots n_t})$$

$$(A_{n_1} \otimes \cdots \otimes A_{n_{i+1}} \otimes A_{n_i} \otimes \cdots \otimes A_{n_t})$$

$$(I_{n_1 \cdots n_{i-1}} \otimes L_{n_{i+1}}^{n_i n_{i+1}} \otimes I_{n_{i+2} \cdots n_t}),$$

where  $A_{n_i}$  is a  $n_i \times n_i$  matrix. To see this, use the multiplicative rule for tensor products and the commutation theorem. An alternative interpretation of this permutation is obtained by its action on a basis vector of the form  $x^{n_1} \otimes \cdots \otimes x^{n_t}$ . The collection of basis elements of this form is called a tensor product basis and the general permutations associated with tensor products result from permutations of the component positions of these basis elements. In terms of the tensor basis, this permutation exchanges the *i*-th component with the i+1-st, and can be represented as a permutation of t objects by the transposition (i,i+1) written in cycle notation. Thus we have the following map which reduces stride permutations and tensor products of stride permutations to permutations of an appropriate tensor basis.

$$I_{n_1\cdots n_{i-1}} \otimes L_{n_{i+1}}^{n_i n_{i+1}} \otimes I_{n_{i+2}\cdots n_t} \longleftrightarrow (i, i+1)$$

$$\tag{11}$$

All permutations arising from repeated applications of the commutation theorem can thus be thought of as a permutation of the terms in the tensor basis, and can be written as a product of permutations of the form  $I \otimes L \otimes I$ . As such we have a convenient notation for dealing with such permutations.

Two special cases of these types of permutations are especially important for some architectures. These are the permutations  $I_r \otimes L_t^{st}$  and  $L_t^{st} \otimes I_r$ . The first permutes the elements within the segments of the input vector and the second permutes the segments themselves. The permutation  $I_r \otimes L_t^{st}$  permutes the elements in each of the r segments of size st by  $L_t^{st}$ , and the  $L_t^{st} \otimes I_r$  permutes the st segments of size r by  $L_t^{st}$ .  $I_r \otimes L_t^{st}$  can be implemented as a loop of r stride permutations  $L_t^{st}$ , where the same permutation is performed, but the initial offset is incremented by st each iteration.  $L_t^{st} \otimes I_r$  can be implemented by loading blocks of r consecutive elements, beginning at offsets given by the

permutation  $L_t^{st}$ . A combination of these two types of permutations can by implemented efficiently on an architecture that can load at a given stride and can stride the offsets.

With these types of permutations in mind we shall derive a tensor product decomposition of stride permutations. This decomposition will be of importance on certain architectures, where the size of the registers must be taken into account. A detailed example using the CRAY X-MP architecture will be given in section 4.4. The stride permutation  $L_t^N$ , where N = rst can be thought of as a rotation of the tensor basis  $x^r \otimes x^s \otimes x^t$ . As such it can be decomposed into two transpositions. Formally, the permutation (r, s, t) can be written as (r, s)(s, t), where the permutations are composed from right to left. This observation leads to the following decomposition theorem.

**Theorem 4** If N = rst then  $L_t^N = (L_t^{rt} \otimes I_s)(I_r \otimes L_t^{st})$ .

Proof: Since  $L_t^N(x^r \otimes x^s \otimes x^t) = x^t \otimes x^r \otimes x^s$ , and  $(L_t^{rt} \otimes I_s)(I_r \otimes L_t^{st})(x^r \otimes x^s \otimes x^t) = (L_t^{rt} \otimes I_s)(x^r \otimes x^t \otimes x^s) = (x^t \otimes x^r \otimes x^s)$ , the theorem is proved.

Other decompositions of the permutations that arise in tensor product factorizations can be obtained in the same way. The important point is that these permutations are really only permutations of the tensor product basis rather than arbitrary permutations of the full vector. In many cases special features of the architecture can be used to implement these permutations without resorting to a general purpose implementation of an arbitrary permutation. For many algorithms dealing with tensor products, including the FT, this observation can lead to a substantial efficiency gain.

### 4 Implementing Tensor Products

We can now use the commutation theorem and other tensor product identities to obtain some important factorization theorems for multidimensional tensor products. These factorization theorems will have important implications for FT algorithms on various parallel and vector architectures. Using these factorizations and the addressing information given by the permutations, we will show how to obtain a direct implementation of the factorization on a serial machine.

Tensor product identities can be used to modify a factorization so that the addressing permutations are more suitable to a given architecture. First we will show how to obtain a general vector or parallel algorithm. These algorithms will contain features such as maximum vector length and constant data flow. However, when designing an algorithm for a specific machine, these idealized algorithms may not be appropriate. For example, a vector machine might have a maximum vector length, or a parallel machine might have a fixed number of processors or a specific communication network. In these cases, we need to fine tune an algorithm to conform to or take advantage of the features of the

machine. We will end this section with an example of how to use properties of tensor products in this tuning process.

## 4.1 Factorization of Tensor Products and Implications for Various Architectures

Before deriving the factorizations, we need to introduce some notation. This notation will be used throughout this section. Let  $n_i$  be a positive integer, and  $N(i) = n_1 \cdots n_i$ . We will use the convention that N(0) = 1. Finally, we will represent an  $n_i \times n_i$  matrix by  $A_{n_i}$ . When we have an arbitrary number of matrices in a tensor product, we will use t to denote the number of factors. In this special case, we will let N = N(t). With this notation, we begin with the fundamental tensor product factorization.

#### Theorem 5 (Fundamental Tensor Product Factorization)

$$A_{n_1} \otimes \cdots \otimes A_{n_t} = \prod_{i=1}^t (I_{N(i-1)} \otimes A_{n_i} \otimes I_{N/N(i)}).$$

Furthermore, the factorization is true for any permutation of the factors  $(I_{N(i-1)} \otimes A_{n_i} \otimes I_{N/N(i)})$ .

The proof is by induction on t. For t=2 the theorem is just the factorization  $A_{n_1} \otimes A_{n_2} = (A_{n_1} \otimes I_{n_2})(I_{n_1} \otimes A_{n_2})$  given in equation (4). For the general case we have:

$$A_{n_1} \otimes A_{n_2} \otimes \cdots \otimes A_{n_t} = (A_{n_1} \otimes I_{N/n_1})(I_{n_1} \otimes A_{n_2} \otimes \cdots \otimes A_{n_t}),$$

which by induction is equal to

$$(A_{n_1} \otimes I_{N/n_1}) \left( I_{n_1} \otimes \prod_{i=2}^t (I_{N(i-1)/n_1} \otimes A_{n_i} \otimes I_{N/N(i)}) \right).$$

Using the tensor product identities

$$(I \otimes BC) = (I \otimes B)(I \otimes C) \tag{12}$$

$$I_m \otimes I_n = I_{mn} \tag{13}$$

obtained from the multiplicative rule, in theorem 1, and the definition, we get

$$(A_{n_1} \otimes I_{N/n_1}) \prod_{i=2}^t (I_{N(i-1)} \otimes A_{n_i} \otimes I_{N/N(i)})$$

which gives the desired result. Since any two terms commute, the theorem is true independent of the order of the factors.

Each term in this factorization  $(I_m \otimes A \otimes I_n)$  involves m copies of the vector operation  $A \otimes I_n$ . In order to understand the implementation and modification of this factorization, we must study a general tensor product term of this form. We begin by showing two ways to convert this term into the parallel form  $I_{mn} \otimes A$ . Besides the benefit for a parallel machine, this form has a natural interpretation as a loop, hence it can be directly implemented on a serial machine using a loop construct. In order to program  $I_n \otimes A \otimes I_m$  as the loop  $I_{mn} \otimes A$ , we must keep track of the indexing given by the necessary stride permutations. Two possible indexing schemes are given by the following equations.

$$I_{m} \otimes A_{n_{i}} \otimes I_{n} = I_{m} \otimes L_{n_{i}}^{n_{i}n} (I_{n} \otimes A_{n_{i}}) L_{n}^{nn_{i}}$$

$$= (I_{m} \otimes L_{n_{i}}^{n_{i}n}) (I_{mn} \otimes A_{n_{i}}) (I_{m} \otimes L_{n}^{nn_{i}})$$

$$I_{m} \otimes A_{n_{i}} \otimes I_{n} = (I_{m} \otimes A_{n_{i}}) \otimes I_{n} = L_{mn_{i}}^{mn_{i}n} (I_{mn} \otimes A_{n_{i}}) L_{n}^{mn_{i}n}.$$

$$(14)$$

$$I_m \otimes A_{n_i} \otimes I_n = (I_m \otimes A_{n_i}) \otimes I_n = L_{mn_i}^{mn_i n} (I_{mn} \otimes A_{n_i}) L_n^{mn_i n}.$$

(15)

The first equation can be implemented with a pair of nested loops with the innermost loop indexing given by the stride permutations  $L_n^{nn_i}$  and  $L_{n_i}^{nn_i}$  or as a single loop with the input indexing given by  $I_m \otimes L_n^{nn_i}$  and the output indexing given by its inverse. The second equation can be implemented with a single loop with its indexing given by  $L_n^{mn_in}$  and its inverse. A detailed translation between these equations and their implementations will be given in section 4.2.

These two modifications can be applied to the fundamental tensor product factorization to obtain alternative factorizations which give direct implementations using loops.

The first indexing scheme gives the following two alternative factorizations.

#### Theorem 6

$$A_{n_{1}} \otimes \cdots \otimes A_{n_{t}} = \prod_{i=1}^{t} I_{N(i-1)} \otimes \left( L_{n_{i}}^{N/N(i-1)} (I_{N/N(i)} \otimes A_{n_{i}}) L_{N/N(i)}^{N/N(i-1)} \right)$$

$$= \prod_{i=1}^{t} \left( I_{N(i-1)} \otimes L_{n_{i}}^{N/N(i-1)} \right) (I_{N/n_{i}} \otimes A_{n_{i}}) \left( I_{N(i-1)} \otimes L_{N/N(i)}^{N/N(i-1)} \right).$$

The last factorization can be simplified if we combine adjacent permutations, and thereby eliminate some permutations. We carry out this simplification to familiarize the reader with the permutation manipulations that arise in modifying tensor product factorizations. The form of the factorization that would be used on a particular machine depends on the types of permutations that can be efficiently implemented. This simplification can easily be obtained using equation (11), and the permutation identity  $(i, \ldots, t)(i-1, i, \ldots, t)^{-1} = (i-1, i)$ . If we map this equation to stride permutations, we get the tensor product identity,

$$\left(I_{N(i-2)} \otimes L_{N/N(i-1)}^{N/N(i-2)}\right) \left(I_{N(i-1)} \otimes L_{n_i}^{N/N(i-1)}\right) = I_{N(i-2)} \otimes L_{n_i}^{n_{i-1}n_i} \otimes I_{N/N(i)},$$

which leads to the following factorization

$$A_{n_1} \otimes \cdots \otimes A_{n_t} = \prod_{i=1}^t (I_{N(i-2)} \otimes L_{n_i}^{n_{i-1}n_i} \otimes I_{N/N(i)}) (I_{N/n_i} \otimes A_{n_i}).$$

(16)

The second indexing scheme gives rise to

#### Theorem 7 (Parallel Tensor Product Factorization)

$$A_{n_1} \otimes \cdots \otimes A_{n_t} = \prod_{i=1}^t L_{N(i)}^N(I_{N/n_i} \otimes A_{n_i}) L_{N/N(i)}^N = \prod_{i=1}^t L_{n_i}^N(I_{N/n_i} \otimes A_{n_i}).$$

The second equation is obtained by using the multiplication rule for stride permutations, given in theorem 3, to simplify adjacent stride permutations.

All of the modified factorizations that we have presented so far are completely parallelized in the sense that all tensor product terms are of the form  $I \otimes A$ . We can easily use the commutation theorem to convert the parallel terms to vector terms to get factorizations that are completely vectorized. By complete vectorization, we mean that each tensor product  $A \otimes I$  acts on vectors of the maximum length. For example, we commute the last factorization to get

#### Theorem 8 (Vectorized Tensor Product Factorization)

$$\prod_{i=1}^t (A_{n_i} \otimes I_{N/n_i}) L_{n_i}^N.$$

In many practical cases, complete vectorization is not desired because of machine limitations such as the size of the vector registers. In these cases we would like a factorization that is only partially vectorized. For example, if the maximum size of vector operations was 64, then we would like tensor product terms of the form  $I_m \otimes A \otimes I_{64}$ . This would correspond to a loop of m vector operations on vectors of the maximum size possible on the machine in question. We can interpret this as segmenting a large vector operation into vector operations that fit on a given machine. Using the mathematical tools presented so far, it is easy to obtain a variety of factorizations that meet the addressing and architectural features of a given machine. In section 4.4, we will give an example of how to modify tensor product operations to the CRAY X-MP.

#### 4.2 Programming Tensor Product Factorizations

In this section we show how to program tensor product factorizations. In general, we will start with a set of base macros and combine them by performing operations corresponding to tensor products, stride permutations, and compositions. Thus macros will be algebraically combined to form new macros.

Furthermore, a macro can be optimized by applying algebraic transformations to it. Several examples of these operations will be presented in this section.

We begin by showing how  $I_m \otimes A$  corresponds to a loop. For this example and the rest of the examples throughout this section, we let

$$A = F_2 = \left(\begin{array}{cc} 1 & 1 \\ 1 & -1 \end{array}\right).$$

To produce the code for  $y = (I_m \otimes F_2)x$ , we must start with code for  $F_2$ .

$$F_2 \equiv F2(y,x)$$

$\equiv y(0) = x(0) + x(1)$

$y(1) = x(0) - x(1)$

F2 is a macro with two parameters corresponding to the base addresses of the input x and the output y. The tensor product of this code,  $(I_m \otimes F_2)$  is constructed by looping over  $F_2$ .

$$I_m \otimes F_2 \equiv ITF2(m, y, x)$$

$\equiv \text{ for } i = 0, \dots, m-1$

$F2(y(2i), x(2i))$

$\equiv \text{ for } i = 0, \dots, m-1$

$y(2i) = x(2i) + x(2i+1)$

$y(2i+1) = x(2i) - x(2i+1)$

Using this construction, any tensor product term of the form  $I \otimes A$  naturally gets mapped to code that computes its action on a vector.

Two such code sequences can be concatenated to create a program that computes the product of matrices of that form. This is done by creating a temporary vector which serves as the output of the first code sequence and the input to the next. For example,  $y = (I_m \otimes F_2)(I_m \otimes F_2)x$  is computed with

$$ITF2(m, t, x)$$

$ITF2(m, y, t)$

where t is a temporary.

In general tensor product factorizations, not all tensor product terms are of the form we desire to construct loop implementations. For example, in the fundamental factorization, the generic tensor product term is of the form  $I_m \otimes F_2 \otimes I_n$ . This has a natural interpretation as a loop of m vector operations on vectors of length n.

for

$$i = 0, \dots, m - 1$$

$$\begin{pmatrix} Y_{2ni} \\ Y_{2n(i+1)} \end{pmatrix} = \begin{pmatrix} I_n & I_n \\ I_n & -I_n \end{pmatrix} \begin{pmatrix} X_{2ni} \\ X_{2n(i+1)} \end{pmatrix}$$

On a machine that does not offer vector instructions,  $F_2 \otimes I_n$  must be computed as a loop. In order to obtain a direct loop interpretation, we must apply the commutation theorem. If we do this, we will introduce stride permutations,  $F_2 \otimes I_n = L_2^{2n}(I_n \otimes F_2)L_n^{2n}$ , that must either be performed as actual permutations or incorporated into the code for computing  $I_n \otimes F_2$  as readdressing.

First we show how to use the mathematical definition of a stride permutation to write code to implement it. Recall that the stride permutation  $L_n^{mn}$  permutes the basis elements  $e_{in+j}^{mn} \longrightarrow e_{jm+i}^{mn}$ . If we write an arbitrary vector in terms of this basis, we have

$$L_n^{mn}\left(\sum_{i=0}^{m-1}\sum_{j=0}^{n-1}x_{in+j}e_{in+j}^{mn}\right) = \sum_{j=0}^{n-1}\sum_{i=0}^{m-1}x_{in+j}e_{jm+i}^{mn}.$$

Thus if  $y = L_n^{mn}x$ , we have that y(jm+i) = x(in+j), where the index into the arrays is given by the basis elements. To get a program that computes this permutation, we need to loop over all possible values of i and j.

$$L_n^{mn} \equiv L(m, n, y, x)$$

for  $i = 0, \dots, m - 1$

for  $j = 0, \dots, n - 1$

$y(jm + i) = x(in + j)$

The order of these loops does not matter; however, it is essential that the dimensions are associated with the proper indices.

Using these stride macros, we can program  $w = (F_2 \otimes I_n)x$  as  $w = L_2^{2n}(I_n \otimes F_2)L_n^{2n}x$  with the following code sequence.

$$L(2, n, y, x)$$

$$ITF2(n, z, y)$$

$$L(n, 2, w, z)$$

We can optimize this code sequence by incorporating the permutations  $L_n^{2n}$  and  $L_2^{2n}$  into the code for  $I_n \otimes F_2$  as readdressing.

To see how this readdressing is carried out, we expand these code sequences.

for

$$j = 0, ..., 1$$

for  $i = 0, ..., n - 1$

$y(i2 + j) = x(jn + i)$

for  $i = 0, ..., n - 1$

$z(2i) = y(2i) + y(2i + 1)$

z(2i+1) = y(2i) - y(2i+1)

for

$$i = 0, \dots, n-1$$

for  $j = 0, \dots, 1$

$w(jn+i) = z(i2+j)$

In this expansion we have taken the liberty to consistently associate i with n and j with 2. This makes it easier to see the substitutions that are needed to combine the code sequences to obtain the correct readdressing. The first stride permutation  $L_n^{2n}$  combines with the code for  $I_n \otimes F_2$  by substituting the input expression of ITF2(n, z, y) with the output expression of L(2, n, y, x). To get a direct match, we must further expand L(2, n, y, x) by setting j = 0 and j = 1:  $(e_{2i}^{2n} \longrightarrow e_{i+1}^{2n})$  and  $e_{2i+1}^{2n} \longrightarrow e_{i+n}^{2n})$ .

for

$$i = 0, ..., n - 1$$

$y(2i) = x(i)$

$y(2i + 1) = x(i + n)$

After this expansion, we can combine the two code sequences.

for

$$i = 0, ..., n - 1$$

$z(2i) = x(i) + x(i+n)$

$z(2i+1) = x(i) - x(i+n)$

The composition with the output permutation  $L_2^{2n} = S_n^{2n}$  is carried out in the same way. However, in this case the substitution is carried out with the output variable. We can use the notation  $S_n^{2n}$  instead of  $L_2^{2n}$  to make this distinction.

After both of these compositions are carried out, we arrive at the transformed (conjugated) code sequence which computes  $w = (F_2 \otimes I_n)x$ .

for

$$i = 0, ..., n - 1$$

$w(i) = x(i) + x(i+n)$

$w(i+n) = x(i) - x(i+n)$

This code transformation eliminates the runtime permutations L(2, n, y, x) and L(n, 2, w, z) by changing the indexing of ITF2(n, z, y) at compile time, thereby saving runtime memory accesses.

An alternative approach to this problem of transforming code sequences would be to augment the parameters of ITF2 to include stride information. For example, we could redefine ITF2 with the stride parameters a, s, b, and t. In the definition of ITF2 we have included the macro for F2 with the additional stride parameters s and t.

$$ITF2(m, y, b, t, x, a, s) \equiv \text{for } i = 0, \dots, m-1$$

$$F2(y(bi), t, x(ai), s)$$

$$\equiv \text{ for } i = 0, \dots, m - 1$$

$$y(bi) = x(ai) + x(ai + s)$$

$$y(bi + t) = x(ai) - x(ai + s)$$

This being the case, we have  $S_m^{2m}ITF2(m,z,2,1,y,2,1)L_m^{2m}=ITF2(m,z,1,m,y,1,m)$ . We can now use these techniques to program  $I_m\otimes F_2\otimes I_n$ . If we rewrite this as  $I_m\otimes S_n^{2n}(I_n\otimes F_2)L_n^{2n}$ , it can be programmed by looping over ITF2(n,y,x).

for

$$i = 0, ..., m - 1$$

$ITF2(n, y(2ni), x(2ni))$

We then expand this code sequence.

for

$$i = 0, ..., m - 1$$

for  $k = 0, ..., n - 1$

$$y(2ni + k) = x(2ni + k) + x(2ni + k + n)$$

$$y(2ni + k + n) = x(2ni + k) - x(2ni + k + n)$$

This code sequence could also have been constructed from the tensor product expression  $(I_m \otimes S_n^{2n})(I_m \otimes I_n \otimes F_2)(I_m \otimes L_n^{2n})$ . The simplest way to implement this would be to separately construct  $I_m \otimes S_n^{2n}$ ,  $I_m \otimes (I_n \otimes F_2)$ , and  $I_m \otimes L_n^{2n}$  using the looping techniques discussed previously, and then compose the code sequences together with the appropriate introduction of temporaries. If we then optimize by combining the permutations with  $I_m \otimes I_n \otimes F_2$ , we arrive at the same code sequence produced from  $I_m \otimes (S_n^{2n}(I_n \otimes F_2)L_n^{2n})$ . To see this observe that  $(I_m \otimes L_n^{2n})e_i^m \otimes e_j^2 \otimes e_k^n = e_i^m \otimes e_k^n \otimes e_j^2$  which implies that  $e_{(2i+j)n+k}^{m2n} \longrightarrow e_{(in+k)2+j}^{m2n}$ . Before applying this substitution, we list the code for  $I_m \otimes I_n \otimes F_2$ .

$$I_m \otimes I_n \otimes F_2 \equiv IITF2(m, n, x, y)$$

$\equiv \text{ for } i = 0, \dots, m - 1$

$\text{ for } k = 0, \dots, n - 1$

$y(2in + 2k) = x(2in + 2k) + x(2in + 2k + 1)$

$y(2in + 2k + 1) = x(2in + 2k) - x(2in + 2k + 1)$

If we make the substitution corresponding to the permutation  $I_m \otimes L_n^{2n}$  and  $I_m \otimes S_n^{2n}$ , we obtain the same code for  $I_m \otimes F_2 \otimes I_n$  that we derived previously.

So far we have only been able to program  $I_m \otimes F_2 \otimes I_n$  using two nested loops. Yet one would like to be able to rewrite this as  $I_{mn} \otimes F_2$  and only use one loop of mn interations. The reason that we have not been able to do this is

that the addressing given by the permutations  $I_m \otimes L_n^{2n}$  and  $I_m \otimes S_n^{2n}$  requires two indices. Instead of using the transformation that led to these permutations, we might try the second transformation  $I_m \otimes F_2 \otimes I_n = S_n^{m2n} (I_{mn} \otimes F_2) L_n^{m2n}$ . However a careful inspection shows that if the permutations are composed with  $I_{mn} \otimes F_2$ , the same problem occurs. There is no way to combine the permutation  $e_{in+j}^{m2n} \longrightarrow e_{jm+i}^{m2n}$  with the loop for  $I_{mn} \otimes F_2$  listed below.

for

$$i = 0, ..., mn - 1$$

$$y(2i) = x(2i) + x(2i + 1)$$

$$y(2i + 1) = x(2i) - x(2i + 1)$$

The only way to combine the permutation with the code would be to rewrite  $I_{mn} \otimes F_2$  as  $I_m \otimes I_n \otimes F_2$  as before and look at  $L_n^{m2n}$  as a permutation on  $e_i^m \otimes e_j^2 \otimes e_k^n$ . In this way we see that  $L_n^{m2n}(e_i^m \otimes e_j^2 \otimes e_k^n) = e_k^n \otimes e_i^m \otimes e_j^2$  and  $e_{(2i+j)n+k}^{m2n} \longrightarrow e_{(km+i)2+j}^{m2n}$ , and this substitution leads to the same code as before

The only way to get a single loop is to look at the complete tensor product factorization. Using theorem 7, we have that

$$F_2\otimes\cdots\otimes F_2=\prod_{k=1}^tL_2^{2^t}(I_{2^{t-1}}\otimes F_2).$$

In this factorization we have terms of the form  $L_2^{2mn}(I_{mn} \otimes F_2) = S_{mn}^{2mn}(I_{mn} \otimes F_2)$ , which can be programmed with a single loop.

$$ITF2(mn, y, 1, mn, x, 2, 1) \equiv$$

$$for i = 0, ..., mn - 1$$

$$F2(y(i), mn, x(2i), 1)$$

$$\equiv for i = 0, ..., mn - 1$$

$$y(i) = x(2i) + x(2i + 1)$$

$$y(i + mn) = x(2i) - x(2i + 1)$$

In this factorization, adjacent stride permutations combine to produce a stride permutation with appropriate stride so that it can be combined with  $F_2$  in a single loop. However, the input and output permutations are no longer the same. This makes programming the algorithm in place impossible. Nonetheless, with the introduction of temporaries, t copies of this code can be used to compute  $F_2 \otimes \cdots \otimes F_2$ .

## 4.3 Modifying the Implementation to Parallel Architectures

In this section we show how tensor product factorizations lead to parallel and vector implementations. Tensor product terms of the form  $I_m \otimes A$  can be implemented as m copies of A, which can be done in parallel. Instead of implementing  $y = (I_m \otimes F_2)x$  as a loop, each  $F_2$  can be computed in parallel on m separate processors. If each processor has access to a shared memory containing the input vector x and the output vector y, then the code sequence  $F_2(y(2i), x(2i))$  can be computed by the i-th processor. In the same fashion,  $F_2 \otimes I_m$  can be computed as  $S_m^{2m}(I_m \otimes F_2)L_m^{2m}$ , where each processor computes  $F_2(y(i), m, x(i), m)$  an  $F_2$  at stride m. Here we are using the  $F_2$  macro which includes stride parameters.

In general,  $I_m \otimes F_2 \otimes I_n$  can be computed by mn processors labeled by the pair of integers (i,j)  $0 \le i < m$ ,  $0 \le j < n$ , each computing F2(y(2ni+j),n,x(2ni+j),n). Alternatively,  $I_m \otimes (I_n \otimes F_2)$  can be thought of as m parallel computations of  $I_n \otimes F_2$ . In this case, each processor would compute the following code sequence.

for

$$j = 0, ..., n - 1$$

$$y(2ni + 2j) = x(2ni + 2j) + x(2ni + 2j + 1)$$

$$y(2ni + 2j + 1) = x(2ni + 2j) - x(2ni + 2j + 1)$$

Using  $I_m \otimes (I_n \otimes F_2)$  instead of  $I_{mn} \otimes F_2$ , is a natural way of controlling the granularity of the parallel computation. This is especially useful if there is a fixed number of processors. Returning to the general term,  $I_m \otimes F_2 \otimes I_n = I_m \otimes (S_m^{2m}(I_n \otimes F_2)L_m^{2m})$  can be computed with m processors each computing the following loop.

for

$$j = 0, ..., n - 1$$

$$y(2ni + j) = x(2ni + j) + x(2ni + j + n)$$

$$y(2ni + j + n) = x(2ni + j) - x(2ni + j + n)$$

We can now use the fundamental factorization and these ideas to compute  $F_2 \otimes \cdots \otimes F_2$  in parallel. However, there is some added difficulty. First of all, between each stage  $I_{2^{i-1}} \otimes F_2 \otimes I_{2^{t-i}}$ , a barrier synchronization is needed to guarantee that the input to the next stage is correct. Furthermore, the natural interpretation of each stage leads to a different degree of parallelism at each stage. Different addressing and hence different programming at each stage is required to get a consistent degree of parallelism. This problem can be fixed if we use the parallel factorization instead. In this case, the addressing is the same at each stage and the natural interpretation has the maximum possible degree of parallelism at each stage. The only problem with this factorization is that we may desire a larger granularity and not the maximum degree of parallelism.

If we wish to adapt to a parallel processor with a fixed number of processors, we can modify this factorization accordingly. For example, if we have 8

processors and wish to compute  $F_2 \otimes \cdots \otimes F_2 = F_{2,10}$ , the tensor product of 10 factors of  $F_2$ , we could rewrite the factorization as

$$\prod_{i=1}^{10} S_{512}^{1024}(I_{512} \otimes F_2) = \prod_{i=1}^{10} S_{512}^{1024}(I_8 \otimes I_{64} \otimes F_2).$$

In this case each processor would compute the following code sequence.

for

$$j = 0, ..., 63$$

$$F2(y(2^{7}i + j), 2^{9}, x(2^{7}i + 2j), 1)$$

$$\equiv$$

for  $j = 0, ..., 63$

$$y(2^{7}i + j) = x(2^{7}i + j) + x(2^{7}i + 2j + 1)$$

$$y(2^{7}i + j + 2^{9}) = x(2^{7}i + j) - x(2^{7}i + 2j + 1)$$

There are two potential problems with this parallel implementation. These difficulties stem from locality and granularity considerations. After each computation of  $F_2$ , the results are stored back to main (shared) memory. It might be advantageous to do more local computation before doing the memory operation. Even for serial computers this might be the case. In fact any implementation on a machine with an hierarchical memory structure should be concerned with doing the proper amount of local computation. Furthermore, depending on the memory organization, it might be beneficial to load and store more than one operand or result at a time. These objectives can be satisfied by further modifying the factorization.

More local computation can be obtained if the decomposition is based on a larger unit of computation than  $F_2$ . For example, we may have enough local memory to compute  $F_2 \otimes F_2$  instead of just  $F_2$ . In this case we can use the modified parallel factorization

$$\prod_{i=1}^{5} \left( S_{256}^{1024} \left( I_8 \otimes I_{32} \otimes (F_2 \otimes F_2) \right) \right).$$

In this factorization there are only 5 factors instead of 10. Therefore, the number of required synchronizations has been decreased and the granularity has been increased.

In this example, we have chosen the number of  $F_2$ 's in each stage (2) to divide the total number of factors (10). If we had chosen a decomposition that was not compatible in this sense, the only difficulty that would arise would be an odd sized factor somewhere in the computation. Such a decision might be necessitated by the limitations of the given architecture. Returning to our example, suppose we could compute  $F_2 \otimes F_2 \otimes F_2 = F_{2,3}$  instead of just  $F_2 \otimes$

$F_2$ . If we chose to have the odd-sized factor in front, there are two natural factorizations that we could use.

$$F_{2} \otimes F_{2,9} = F_{2} \otimes \prod_{i=1}^{3} \left( S_{64}^{512} (I_{64} \otimes F_{2,3}) \right)$$

$$= (F_{2} \otimes I_{512}) \prod \left( (I_{2} \otimes S_{64}^{512}) (I_{2} \otimes I_{64} \otimes F_{2,3}) \right)$$

$$= S_{512}^{1024} (I_{512} \otimes F_{2}) L_{512}^{1024} \prod \left( (I_{2} \otimes S_{64}^{512}) (I_{2} \otimes I_{64} \otimes F_{2,3}) \right).$$

$$(17)$$

$$F_{2,10} = S_{512}^{1024}(I_{512} \otimes F_2) \prod_{i=1}^{3} \left( S_{128}^{1024}(I_{128} \otimes F_{2,3}) \right). \tag{18}$$

The first factorization is obtained by a tensor product construction of the decomposition of  $F_{2,9}$  which is compatible with  $F_{2,3}$ . The difficulty with this construction is that the addressing given by the permutations is not compatible with  $I_{128} \otimes F_{2,3}$ , but instead is compatible with  $I_2 \otimes I_{64} \otimes F_{2,3}$ . This combined with the extra permutation given by the commutation of  $F_2 \otimes I_{512}$  leads to a complicated program that can not easily be programmed in our 8 processor machine. However, the second factorization, which follows immediately from the mixed radix parallel factorization (theorem 7) starting from  $F_2 \otimes F_{2,3} \otimes F_{2,3} \otimes F_{2,3}$ , can easily be programmed in the same manner as the compatible example based on  $F_{2,2}$ .

The second possible problem with the computation given by the parallel factorization is that each memory operation must be done separately. We would like to be able to do permutations within local memories of the separate processors, and then store large blocks of results back to shared memory. This type of data flow can be obtained by decomposing the intervening permutations into a collection of local permutations followed by a global block permutation. This is given by the tensor product decomposition of stride permutations (theorem 4). For our example, where we need to compute  $S_{512}^{1024}(I_8 \otimes I_{64} \otimes F_2)$  this allows us to write

$$S_{512}^{1024} = (S_8^{16} \otimes I_{64})(I_8 \otimes S_{64}^{128}).$$

$I_8 \otimes S_{64}^{128}$  is carried out by permuting elements in local memory for each of the 8 processors by  $S_{64}^{128}$ . After that local permutation, the results are sent back to main memory in segments of length 64. These segments are permuted by  $S_8^{16}$ .

The regularity of the factorization  $\prod S_{N/2}^N(I_{N/2}\otimes F_2)$  implies that the computation could be carried out on an array processor or in VLSI. For each stage of the computation, the same instructions  $(F_2)$  are computed on each segment of the input vector. Furthermore, the same permutation of the output is performed after each stage, so that the same routing instructions could be used to transmit the data after each stage. Thus it is quite conceivable to program tensor product factorizations on an array processor, a single instruction multiple

data architecture, with various interconnection networks for data transmission. Factorizations of stride permutations can be used to adapt algorithms to a given interconnection network.

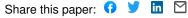

As a simple example, we look at an array of four processors with a perfect shuffle interconnection network called the omega network [12]. This network has been designed for problems involving stride permutations [15]. The permutation  $L_{2^{n-1}}^{2^n}$  has been called the perfect shuffle since its action on a deck of cards is obtained by shuffling two equal piles of cards so that the cards are interleaved one from each pile. Since the permutation  $L_4^8$  is hardwired into this processor, a single pass through the network performs this permutation. If each processor can add and subtract, a single pass through this network can be used to compute  $(I_4 \otimes F_2)L_4^8$  (see figure 1). In the factorizations we have considered so far, terms

Figure 1: Omega network computing  $(I_4 \otimes F_2)L_4^8$

of this form have not arisen. We have only seen  $S_4^8(I_4 \otimes F_2)$ . However, if we rederive the parallel factorization for  $F_{2,3}$  in the opposite order, the appropriate terms are obtained.

$$F_{2,3} = (I_4 \otimes F_2)(I_2 \otimes F_2 \otimes I_2)(F_2 \otimes I_4)$$

=  $(I_4 \otimes F_2)L_4^8(I_4 \otimes F_2)L_4^8(I_4 \otimes F_2)L_4^8.$  (19)

Using this factorization,  $F_{2,3}$  can be computed in three passes through the network.

In general, if we had an N/2  $(N=2^n)$  processor omega network, we could compute  $F_{2,n}$  in  $n = \log N$  passes. However, if we have a fixed number of processors, we can use the omega network as a module to help in larger computations. Such programs are constructed from tensor products.

$$F_{2,n} = \prod \left( S_{N/8}^N \left( I_{N/8} \otimes I_4 \otimes F_{2,3} \right) \right).$$

$$F_{2,n} = \prod \left( S_{N/2}^N \left( I_{N/8} \otimes I_4 \otimes F_2 \right) \right)$$

$$= \prod \left( \left( S_{N/8}^{N/4} \otimes I_4 \right) \left( I_{N/8} \otimes S_4^8 \right) \left( I_{N/8} \otimes I_4 \otimes F_2 \right) \right).$$

$$(20)$$

In this section we have presented a variety of techniques for implementing tensor products on a variety of parallel architectures. We have shown how to use tensor product identities to modify algorithms to situations with a fixed number of processors, fixed granularity, shared memory, and special interconnection networks. While this should give a general overview of using tensor product formulations to modify algorithms and obtain parallel implementations, none of the techniques can be fully appreciated without a specific example. In the next section we deal with questions of vectorization using the CRAY X-MP as a specific example. While we have not specifically discussed vectorization in this section, the techniques needed are similar to the ones presented for the parallel architectures discussed.

#### 4.4 The Cray X-MP: A Design Example

In this section, we use the mathematical techniques developed in the previous sections to design algorithms for a specific architecture. In particular, we will study how to efficiently implement tensor product operations and the corresponding stride permutations on the CRAY X-MP. The X-MP is a sample architecture from a class of machines called vector processors. In order to obtain an efficient implementation on this machine, it is essential that the algorithm be programmed to take advantage of its architectural features. For a vector processor like the X-MP, the two key programming concerns are vectorization and segmentation. These issues will become clearer as we present some examples.

The reason we have singled out a particular machine is not due to the limitations of our techniques, but rather that our techniques can be used to tune an algorithm to a specific architecture, and the X-MP serves as a nice example. Before studying the implementation of tensor products on the X-MP, we will briefly review the X-MP's architecture and highlight some of the key parameters, which are needed for tuning our algorithms to the machine. More information on the X-MP can be found in the hardware reference and CAL

assembly manuals [1, 2]. A discussion of algorithm design and modification for the X-MP can be found in [9, 8].

The X-MP is a pipelined vector processor. Built into the X-MP's instruction set are instructions for performing vector operations. For example, the X-MP has an instruction for adding all of the components of two vectors of floating point numbers. Vector instructions are implemented, in hardware, by pipelining the elements of the vectors through a functional unit that performs the corresponding operation. In our example of floating point addition, the functional unit that performs the addition is a six stage pipeline. Therefore, the result obtained from adding the first two elements is produced in 6 CPs (clock periods), and the remaining results are produced one every clock period after that. So two vectors containing 64 elements each can be added in 6 + 63 = 69 CPs. If the vector addition were performed with a loop of scalar additions, it would take  $64 \cdot 6 = 384$  CPs. It is this speed-up that gives vector processing its power.

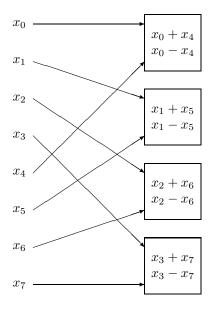

Thus the first concern in obtaining an efficient algorithm for the X-MP, is maximizing the use of vector instructions. Some important vector instructions for our purposes are vector addition and subtraction and scalar-vector multiplication.

It is important to realize that the vector instructions available on the X-MP are carried out on vectors located in vector registers. For example, the instruction

#### • V0 V1 + FV2 Floating point vector add

adds the vectors contained in registers V1 and V2 and produces the result in register V0. Since the vector registers can contain a maximum of only 64 elements, this limits the size of vectors that can be used in vector instructions. However, several vector instructions can be combined to perform operations on larger vectors, which we call supervectors. Splitting a supervector into appropriate segments on which vector instructions can be used, is the second major concern in designing an algorithm for the X-MP. In this case, the size of the vector registers is a key design parameter.

Before giving an example of a supervector instruction, we need to examine how vectors are loaded into and stored from the vector registers. Also, studying these memory operations is essential to efficiently implementing the loadstride permutations that arise from tensor product operations. A vector of elements in memory beginning at X and separated at stride s can be loaded into a vector register with the following instruction.

#### • Vi X, s Load a vector beginning at X into Vi at stride s

The number of elements that are loaded is determined by the contents of a special register called the vector length register VL. Similarly, a vector register can be stored to memory at any given stride.

#### $\bullet$ , Y, s, Vk Store Vk to Y at stride s

Both of these instructions are performed in the same pipelined fashion that other vector instructions are. Ignoring potential memory conflicts, a vector of 64 elements can be loaded in 17+63=80CPs, the time to load the first element plus one CP each for the remaining elements. If memory operations were not done with vector instructions, then performance degradation would be disasterous. By properly segmenting an algorithm its performance can be improved dramatically.

Now that we know how to load segments of vectors into the vector registers, we can see how to perform a supervector instruction like supervector addition. To do this we need a loop that loads a segment of each vector, adds them, and stores the resulting segment. Since the functional units on the X-MP are independent and there are three independent memory ports, these operations can be performed concurrently. The overlap obtained from this concurrency can be thought of as another level of pipelining. In the example of supervector addition, we have a three stage pipeline so that while two segments are being loaded, another two can be added, and the previous result can be stored. Here we see another important benefit of proper segmentation, namely the overlap of the operations on the segments.

We now begin our study of the implementation of tensor product operations on the X-MP. Tensor product terms of the form  $A \otimes I_n$ , for  $n \leq 64$ , can be implemented directly with vector instructions. For example,

$$(F_2 \otimes I_3)x = \begin{pmatrix} 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 \\ 1 & 0 & 0 & -1 & 0 & 0 \\ 0 & 1 & 0 & 0 & -1 & 0 \\ 0 & 0 & 1 & 0 & 0 & -1 \end{pmatrix} \begin{pmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \end{pmatrix} = \begin{pmatrix} x_0 + x_3 \\ x_1 + x_4 \\ x_2 + x_5 \\ x_0 - x_3 \\ x_1 - x_4 \\ x_2 - x_5 \end{pmatrix}.$$

If we let V0 contain the vector  $(x_0, x_1, x_2)$  and V1 contain  $(x_3, x_4, x_5)$ , the tensor product operation can be performed with the following vector instructions.

- V2 V0 + FV1

- V3 V0 − FV1

The result is obtained by storing V2 followed by V3 back to memory. If Y is the location of the output vector, this is done with the following instructions.

- $\bullet$ , Y, 1 V2 Store first segment at stride 1

- ,Y+3,1 V3 Store second segment at stride 1

In this case the stride is 1 for the individual stores, but the offset must be incremented by the size of the vector segments.

Next we will see how to implement stride permutations using load and store operations. As in the previous example, we let x be a vector with six elements.

First we would like to perform the load operation  $y = L_2^6 x$ , which corresponds to the permutation

$$\begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \end{pmatrix} = \begin{pmatrix} x_0 \\ x_2 \\ x_4 \\ x_1 \\ x_3 \\ x_5 \end{pmatrix}.$$

The following load instructions can be used to perform this operation.

- V0 , X, 2 Load first segment at stride 2

- $\bullet$  V1 , X + 1, 2 Load second segment at stride 2

After these loads are performed,

$$V0 = \begin{pmatrix} x_0 \\ x_2 \\ x_4 \end{pmatrix} , V1 = \begin{pmatrix} x_1 \\ x_3 \\ x_5 \end{pmatrix}.$$

To obtain the permuted vector Y, we must store these registers back to memory.

- $\bullet$  , Y, 1 V0 Store first segment at stride 1

- ,Y+3,1 V1 Store second segment at stride 1

The same permutation could be carried out with the storestride operation  $S_3^6$ . In this case we load the registers V0, V1, and V2 with consecutive elements, and store the registers back at stride 3.

- V0 , X, 1 Load first segment at stride 1

- V1, X+2,1 Load second segment at stride 1

- V2, X+4,1 Load third segment at stride 1

After these loads, we have

$$V0 = \begin{pmatrix} x_0 \\ x_1 \end{pmatrix}$$

,  $V1 = \begin{pmatrix} x_2 \\ x_3 \end{pmatrix}$  ,  $V2 = \begin{pmatrix} x_4 \\ x_5 \end{pmatrix}$ .

These registers are then stored back to main memory.

- ullet , Y,3 V0 Store first segment at stride 3

- ,Y+1,3 V1 Store second segment at stride 3

- Y + 2, 3 V2 Store third segment at stride 3

After the first store operation  $y=(x_0, , x_1, , )$ , after the second store  $y=(x_0,x_2, ,x_1,x_3, )$ , and after the third store y contains the appropriately permuted vector.

To see how loadstride and storestride permutations can be implemented in conjunction with tensor product operations, we show how terms like  $(A \otimes I)L$  and  $S(A \otimes I)$  are implemented. We begin by looking at  $(F_2 \otimes I_3)L_2^6x$ . As in the previous example, we load x into two vector registers at stride 2. However, before storing the vectors back to memory, we perform the vector operation  $F_2 \otimes I_3$  as in the first example, obtaining:

$$V2 = \begin{pmatrix} x_0 + x_1 \\ x_2 + x_3 \\ x_4 + x_5 \end{pmatrix}, V3 = \begin{pmatrix} x_0 - x_1 \\ x_2 - x_3 \\ x_4 - x_5 \end{pmatrix}.$$

Finally, these registers are stored back giving the desired output vector. It is imperative that the loadstride operation be compatible with the tensor product operation. In this case, we must have two registers with 3 elements each in order to be able to perform  $F_2 \otimes I_3$ .

The operation  $S_2^6(F_2 \otimes I_3)$  can be implemented in a similar fashion. In this case, after performing the vector operation  $F_2 \otimes I_3$ , we have two registers each containing 3 elements, which can be stored at stride 2. An important feature of both of these examples, is that in order to perform  $F_2 \otimes I_3$  we must load the input vectors and store the result even if there were no permutation. By performing the permutation during the loading or storing phases we are essentially obtaining the permutation for free. In effect we are saving the extra memory operations that would be needed if the permutation was carried out separately.

To see how tensor product terms with preceding load stride permutations can arise, let A be a  $2\times 2$  matrix and B be a  $3\times 3$  matrix and consider the factorization given by the commutation theorem. In this case we need to implement the factorization

$$z = (A \otimes B)x = (A \otimes I_3)(I_2 \otimes B)x \tag{22}$$

$$= (A \otimes I_3) L_2^6 (B \otimes I_2) L_3^6 x. \tag{23}$$

We would perform  $y = (B \otimes I_2)L_3^6x$  followed by  $z = (A \otimes I_3)L_2^6y$ . This factorization allows  $A \otimes B$  to be performed using only vector instructions. Also the factorization forces the tensor product operations to be compatible with the loadstride operations.

Up until now, by assuming vectors fit inside the vector registers, we have ignored the problem of segmentation. Since the size of the vector registers is 64, we would like to perform vector instructions on vectors with 64 elements. In terms of tensor product operations, we would like factors of the form  $I_m \otimes A \otimes I_{64}$ . Such a factor corresponds to performing a loop of m tensor product operations on vectors of length 64. Factors of this form are not always present in tensor

product factorizations; however, it is possible to use tensor product identities to manipulate the factorization so that appropriate terms can be obtained.

For example, suppose we need to evaluate  $F_2 \otimes I_{128}$ . Here the size of the vector operation is 128, so that the vector appears not to fit in the vector registers. We would like to rewrite this as  $I_2 \otimes F_2 \otimes I_{64}$ , in order to get the correct vector length. It is clear that the commutation theorem can be used to do this; however, if we do this in the obvious way, we run into some difficulty. To see this observe

$$F_2 \otimes I_{128} = (F_2 \otimes I_{64}) \otimes I_2 \tag{24}$$

$$= L_{128}^{256}(I_2 \otimes (F_2 \otimes I_{64}))L_2^{256}. \tag{25}$$

In order to perform the vector operation  $F_2 \otimes I_{64}$ , we need vectors of length 64, but  $L_2^{256}$  gives two vectors of length 128:

$$\begin{pmatrix} x_0 \\ x_2 \\ x_4 \\ \vdots \\ x_{254} \end{pmatrix} \text{ and } \begin{pmatrix} x_1 \\ x_3 \\ x_5 \\ \vdots \\ x_{255} \end{pmatrix}.$$

In order to solve this difficulty, we need to use the loadstride factorization

$$L_2^{256} = (L_2^4 \otimes I_{64})(I_2 \otimes L_2^{128})$$

given by theorem 4. This factorization can easily be remembered if the terms in  $F_2 \otimes I_{64} \otimes I_2$  are commuted in stages. The first factor  $I_2 \otimes L_2^{128}$  corresponds to a permutation within segments, and the second factor  $L_2^4 \otimes I_{64}$  can be thought of as a permutation of segments.  $I_2 \otimes L_2^{128}$  creates four segments of size 64:

$$V0 = \begin{pmatrix} x_0 \\ x_2 \\ \vdots \\ x_{126} \end{pmatrix}, V1 = \begin{pmatrix} x_1 \\ x_3 \\ \vdots \\ x_{127} \end{pmatrix}, V2 = \begin{pmatrix} x_{128} \\ x_{130} \\ \vdots \\ x_{254} \end{pmatrix}, V3 = \begin{pmatrix} x_{129} \\ x_{131} \\ \vdots \\ x_{255} \end{pmatrix}.$$