# A Multilevel Bottom-up Optimization Methodology for the Automated Synthesis of RF Systems

Fábio Passos, *Member, IEEE*, Elisenda Roca, Javier Sieiro, Rafaella Fiorelli, *Member, IEEE*, Rafael Castro-López, *Member, IEEE*, José Maria López-Villegas, *Senior Member, IEEE*, Francisco V. Fernández, *Member, IEEE*

Abstract— In recent years there has been a growing interest in electronic design automation methodologies for the optimizationbased design of radiofrequency circuits and systems. While for simple circuits several successful methodologies have been proposed, these very same methodologies exhibit significant deficiencies when the complexity of the circuit is increased. The majority of the published methodologies that can tackle radiofrequency systems are either based on high-level system specification tools or use models to estimate the system performances. Hence, such approaches do not usually provide the desired accuracy for RF systems. In this work, a methodology based on hierarchical multilevel bottom-up design approaches is presented, where multi-objective optimization algorithms are used to design an entire radiofrequency system from the passive component level up to the system level. Furthermore, each level of the hierarchy is simulated with the highest accuracy possible: electromagnetic simulation accuracy at device-level and electrical simulations at circuit/system-level.

Index Terms— bottom-up design methodology; radiofrequency; automated design; multi-objective optimization; surrogate modeling

# I. INTRODUCTION

RADIO FREQUENCY (RF) circuits are considered to be a bottleneck in automated system synthesis [1]. In RF, circuit/system design is highly intuitive, rather than systematic and structured as in e.g., digital circuits. Also, RF design relies heavily upon the designer know-how. Furthermore, RF circuits

Manuscript submitted in July 25, 2018. Revised December, 4, 2018. Accepted December, 28, 2018. This work was supported in part by the P12-TIC-1481 Project (funded by Junta de Andalucía) and in part by the TEC2013-45638-C3-3-R and TEC2016-75151-C3-3-R Project (funded by the Spanish Ministry of Science, Innovation and Universities and ERDF). F. Passos acknowledges the same ministry for supporting his research activity through the grant BES-2014-068216.

Fábio Passos, Elisenda Roca, Rafaela Fiorelli, Rafael Castro-López and Francisco V. Fernández are with Instituto de Microelectrónica de Sevilla, CSIC and Universidad de Sevilla, 41092 Sevilla, Spain (e-mails: moreira; eli; fiorelli; castro; pacov@imse-cnm.csic.es).

Javier Sieiro and Jose Maria Lopez-Villegas are with the Radiofrequency Group of the University of Barcelona, Barcelona, Spain. (e-mails: jsieiro@el.ub.es, m.lopez\_villegas@ub.edu).

usually need very time-consuming simulations, such as electromagnetic (EM) simulations, in order to accurately model passive devices such as inductors and transformers, which are key elements in RF design.

Since the world is evolving towards 5G wireless communications and the Internet of Things (IoT) becomes a trending topic in todays' electronics, RF systems are becoming more complex, with higher integration needs and harder-to-obtain specifications. Todays' setback is that designers' productivity rate is insufficient to cope with the advances in integrated circuit specifications, therefore leading to a design gap. In order to overcome this design gap, new design methodologies have to be developed that can help the designer improve his/her productivity.

During the past fifteen years, several optimization-based methodologies have been reported for the automatic design of RF circuits [2]-[19]. Most of them address the synthesis of basic building blocks, e.g., power amplifiers or low noise amplifiers [2]-[14], in some cases considering parasitic effects and process variations. Moreover, and because of the high cost of EM simulations, passive devices, like inductors and transformers, are, instead, usually evaluated with analytical (i.e., fast) but inaccurate models, something that could lead to a fatal impact in how accurately circuit performances end up being evaluated [11]. Other works do address RF system-level synthesis but, however, relying on high-level description tools or approximated models for performance evaluation and, therefore, lack sufficient accuracy [15]-[19].

In consequence, in order to tackle complex RF circuits and solve the accuracy issues mentioned above, this work presents a design methodology that follows a divide-and-conquer strategy, which is based on hierarchical circuit partitioning and bottom-up (BU) composition of lower-level blocks. Furthermore, each level of the hierarchy is simulated with the highest accuracy possible: EM accuracy at the device level (using an efficient state-of-the-art machine learning technique [20]), and electrical simulations at the circuit/system level, using smart simulation techniques that do not degrade the efficiency of the entire synthesis. In [12], this BU design methodology was successfully applied between the passive and

the circuit level to design a low noise amplifier. However, to the best of the authors' knowledge, the work presented here is the first automated BU methodology to reach a system level design (e.g., RF front-end receiver) with highly accurate performance evaluation from the device up to the system level.

A second contribution of this paper is that it demonstrates the reusability of inductor and circuit information by using the same performance models for different system level specifications. Finally, a last contribution is the detailed comparison with other partitioning strategies for the same specifications, simulation tools and optimization techniques.

The rest of this paper is organized as follows. Section II details previous efforts made on RF system synthesis, i.e., circuits with higher complexity than the building blocks in [2]-[14]. Section III presents the proposed methodology. Section IV provides the experimental results coming from the application of the proposed methodology to the design of a typical RF system. The proposed methodology is further validated in Section V, by comparing it against other partitioning strategies. Finally, in Section VI, conclusions are drawn.

# II. PREVIOUS WORKS ON RF SYSTEM SYNTHESIS

From the early 2000's up to the last few years, most efforts aimed at RF system-level design were focused on high-level system specification tools, architecture comparison tools and RF budget analyzers [15]-[17]. Such tools were commonly used to select the desired system architecture based on the needed system performances. Afterwards, the performances were distributed among the circuits constituting the system, using either optimization processes based on behavioral models [15],[16] or analytical equations [17]. As power consumption minimization is essential for optimal system design, in some cases a power consumption estimation model was used [15],[17]. The main disadvantage of such tools is their inability to consider all circuit nonlinearities. Since they are based on simple behavioral models or equations, it may be difficult to guarantee that the specifications imposed by the tools will be eventually achieved at the device level. Therefore, when designing lower-level circuits, the designer may face some difficulties reaching the desired performances, and, thus, redesign cycles are unavoidable. Eventually, since the high-level specifications do not entirely match the device-level simulations, the designer can choose to over-design the RF system in order to reduce the re-design cycles. However, this would ultimately lead to sub-optimal designs (e.g., circuits with higher power consumption than strictly required).

Some other approaches have tried to reach the lower circuit sizing level. In [18], the circuit specifications provided by the tool in [16] are used to size a low-noise amplifier (LNA) and a mixer. The circuit performances are estimated using first-order analytical equations, that do not take into account all non-idealities. Furthermore, ideal models are used for the passive components. Therefore, these components have to be synthesized after the circuit design, and there is no guarantee that the value required for the passive is achievable in the adopted technology. As reported in [18], some components had

to be iteratively tuned by more than 50% from its initial value in order to meet the circuit specifications.

Another attractive approach starts from a manual coarse design [19]; then, models linking LNA and mixer performances (estimated using electrical simulation) to the circuit variables are generated using sparse regression techniques. An optimization algorithm is then used to generate Pareto fronts of the optimal performance trade-offs of each circuit block and a polynomial fitting is used to obtain equations relating the performances of the Pareto front. Optimization at the system level is performed using the Pareto front equations of the blocks to constrain the search space. However, the developed models are local, only covering 20% of the design space around the initial coarse design and, therefore, the circuit optimization is not expected to yield globally optimal results, being instead more focused on local optimization around the initial design. Furthermore, as in [5], the performance models are built using ideal passive components (with the designer having to ultimately synthesize these components) and only NF, gain and IIP<sub>3</sub> are considered for the performance of the blocks, leaving out important performances such as power consumption.

In some other cases, optimized RF blocks were connected together to obtain an RF frontend but no real system optimization was performed [9],[10]. What is more, in most cases the models for the passive components are of the analytical nature whose typical inherent inaccuracies can make the synthesis process unsuccessful [11] thus calling for new redesign iterations.

Therefore, it is possible to conclude that:

- There is a lack of tools and methods to estimate system performances with the utmost accuracy at all levels, from the device level up to the system level, and to overcome the accuracy problems of performance/behavioral models, analytical equations, etc., reducing or avoiding in this way re-design iterations.

- There is a lack of tools and methods to perform device/circuit/system optimization in order to find globally optimal designs, therefore enabling the minimization of performances such as power consumption and area.

- There is a lack of tools and methods to fully synthesize RF systems and provide the sizing of all components.

Thus, to address these deficiencies, this paper describes an accurate and efficient methodology to design RF systems.

# III. PROPOSED MULTILEVEL BOTTOM-UP DESIGN METHODOLOGY FOR SYSTEM SYNTHESIS

The proposed methodology avoids re-design iteration issues by using BU design approaches (subsections A and B) and uses accurate models for passive components, in order to attain the utmost accuracy at each level of the system design (subsection C).

#### A. Multilevel BU Circuit Design

The design of an RF circuit can be considered as an optimization problem, mathematically formulated as:

minimize

$$f(x)$$

;  $f(x) \in R^m$

subject to  $g(x) \le 0$ ;  $g(x) \in R^k$

$x \in \Omega$  (1)

where f(x) is a vector with m objective functions, g(x) is a vector with k constraints and x is a vector with n design variables on the search space  $\Omega$ . When designing a circuit, where only one performance is minimized or maximized (m=1) the problem can be solved with a single-objective optimization algorithm. When trade-offs between two or more objectives are to be explored (m>1), then a multi-objective optimization algorithm can be used.

In the multi-objective case, a solution a is said to constraindominate solution b if and only if a has a smaller constraint violation than b, or, if all constraints are met,  $f_i(a) \le f_i(b)$ , for every  $i \in \{1,...,m\}$  and  $f_j(a) < f_j(b)$  for at least an index  $j \in \{1,...,m\}$ . A point  $y \in \Omega$  is Pareto-optimal if it is not dominated by any other point in  $\Omega$ . The set of all Pareto-optimal points in the search space is known as the Pareto set and the corresponding points in the objective space is the Pareto-optimal front (POF).

In BU design methodologies, the complete system is decomposed into two or more hierarchical levels; then, the design starts at the lowest level and composes the results up the hierarchy until reaching the system level. In this type of design methodologies, multi-objective optimization algorithms are commonly used so the information passed to the upper level is not a single design solution but rather a POF representing the best trade-offs available for a given circuit topology (e.g., phase noise vs. power consumption in a voltage-controlled oscillator (VCO)). This approach ensures that the designs considered at all levels are feasible and that no re-design cycles are required.

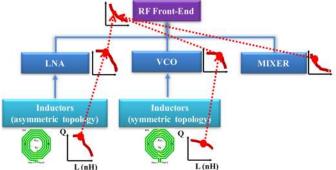

This type of BU methodology has been successfully applied in two-level hierarchical design, as in [21]. More recently, these BU methodologies have been exploited in RF circuit design by splitting the design of the circuit and the device levels [12]. In this work, a BU methodology is developed for the entire system-circuit-device hierarchy, as shown in Fig. 1, for the design of an RF front-end.

Since we are interested in obtaining POFs in order to compose a system up the hierarchy, the Non-dominated Sorting Genetic Algorithm (NSGA-II) is used [22]. NSGA-II is a multiobjective optimization algorithm based on the evolution of a set

Fig. 1. BU design methodology for the specific case of an RF front-end

of solutions (i.e., individuals) along a certain number of iterations (i.e., generations). The combination of Pareto dominance with the maximization of the minimal crowding distances aims at promoting convergence and diversity of the solutions. The RF circuit design methodologies considered in this paper do not exploit any particular characteristic of NSGA-II and, therefore, this algorithm could be substituted by any other multi-objective optimization algorithm.

Apart from avoiding re-design cycles, there are several other motivations for using BU design methodologies:

# 1) Optimal Circuit Trade-Offs

In BU design methodologies, each low-level device/circuit design space is reduced to only optimal solutions, representing the best trade-offs for the selected objectives and the device/circuit topology (i.e., the POF). This means that when designing a given higher-level block that contains a low-level device/circuit, the optimization algorithm is only performing a design space exploration in an already optimized design space (the device/circuit POFs previously obtained). This fact improves, considerably, the efficiency of the entire optimization as well as the convergence of the optimizations, because the algorithm no longer has to search in unusable/sub-optimal design areas.

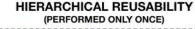

#### 2) Hierarchical Reusability of Lower-Level Blocks

Another motivation for using BU design methodologies is that it facilitates the hierarchical reusability of lower-level blocks. Since in BU design methodologies the lower-level blocks are designed first, the obtained POFs can be stored and used afterwards in the composition of any other system or the same system with different specifications. For example, this means that for the front-end depicted in Fig. 1, the inductor topologies and each individual circuit (LNA, VCO and mixer), have to be optimized only once. Afterwards, the front-end can be optimized for another communication standard without having to perform any additional low-level optimization. Again, this highly improves the efficiency of the methodology.

# 3) Low-Level Topology Selection

It is also possible to consider several device and circuit topologies for each optimization. Thus, all levels of the BU hierarchy can be implemented with different topologies and, therefore, while performing the system synthesis, the optimization algorithm can combine not only different circuit designs but also different circuit topologies (all selected from pre-generated POFs) [21].

The above-mentioned features provide the basis for an efficient and highly dynamic optimization-based multilevel BU methodology which can tackle highly complex systems.

#### B. Composing the System up the Hierarchy

While composing the system up the hierarchy, the lower-level POFs have to be explored because they represent part of the search space in the higher-level optimizations. Therefore, an important issue in BU design methodologies is how to search through these low-level POFs when optimizing higher-level blocks. This issue is important because searching these low-level POFs poses a problem to the optimization algorithms.

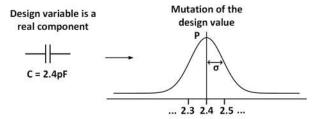

Evolutionary algorithms use mutation operators for local

Fig. 2. Illustrating the mutation operation for regular design variables.

Fig. 3. Illustrating the mutation operation for indexed variables.

search in the design space, where a slight movement in the design space represents a small change in component parameter e.g., transistor width, capacitance value, resistance value, etc. A small component variation (e.g., capacitor value changes from 2.4pF to e.g., 2.5pF, as illustrated in Fig. 2), is usually associated to a small variation in the objective and constraint values of the circuit these components are part of.

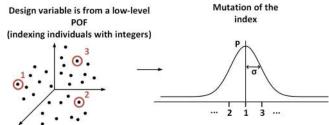

When considering low-level POFs in a high-level optimization, and in order to allow the optimization algorithm to search the low-level POFs, the simplest solution is to assign an integer value to each individual of the low-level POF and use this integer (so-called index value) as a design variable during the optimization. The range of this new design variable, the index variable, would be the number of individuals in the lowlevel POF. The problem, however, is that this index variable does not have any information on the performances of the lowlevel individual, and therefore, individuals with index 1, 2 or 3, may be in completely different areas of the design space (see Fig. 3). Hence, while performing mutation around individual 1, the algorithm can jump to individual 3, which is in a completely different area of the design space and may cause a large variation in the objectives and/or constraints of the system this low-level circuit is part of. As a consequence, the mutation operation is transformed into a completely random variation, that can hamper the convergence of the optimization.

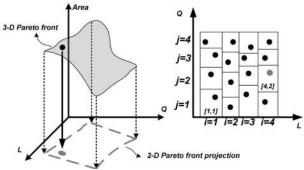

In order to solve this problem, and realizing that a POF generated for N design objectives is a hypersurface of dimension N-1, a set of N-1 coordinates can be used to represent the POF. Therefore, instead of assigning only one index to the individuals in low-level POFs, the individuals of each POF can be sorted by their performances and mapped into a matrix with N-1 dimensions. This operation can be seen in Fig. 4, where a set of 2 coordinates is given to each individual of a 3-D POF. By doing so, each individual of a low-level POF can be represented by a set of coordinates instead of a single index variable. Thus, the designs in each POF are organized by

Fig. 4. Illustrating the mapping of each inductor into a two-coordinate matrix

its performances in such a way that the mutation operator can be efficiently used. The matrix coordinates are then used as design variables in the upper level optimization [23].

# C. Accurate Inductor Modeling

One of the most important subjects in the design of RF circuits/systems is how accurate the device models are. While for transistors, resistors and capacitances, the foundry usually provides sufficiently accurate models, inductors are still a bottleneck due to their distributed effects and parasitics. Traditionally, designers use EM simulations in order to estimate inductor performances, as in [7]. However, including EM simulations in optimization-based approaches, where thousands of EM simulations have to be performed, leads to impractical optimization times. Some approaches, on the other hand, use analytical models, as in [3]. Still, although efficient, these models tend to be highly inaccurate and therefore cause huge shifts in the circuit performances as shown in [11]. Therefore, new modeling strategies, based on machine learning and surrogate models, have been developed in the last few years that are both extremely accurate and efficient, and therefore more suited to be used with optimization-based approaches [24]. Surrogate modeling is an engineering method used when the performances of interest of a complex system cannot be easily measured or, as in this case, when the alternatives are too time consuming (e.g., EM simulations) or too inaccurate (e.g., analytical models). Surrogate models are able to acquire the behavior of a system from a limited number of smartly chosen data points. After learning the system behavior, the model is able to predict how the system will respond to any given input, and predict its output. Surrogate models have been used in the literature, for instance, to model circuit performances [25] or device variability [26]. The work presented here uses an extremely accurate surrogate model that has less than 1% error when compared with EM simulations [20]. Furthermore, the model can describe the inductors through its S-parameters for an accurate frequency behavior description, which can be used in any commercial electrical simulator (e.g., SpectreRF, EldoRF, HspiceRF). In this work, this model is used in order to accurately and efficiently design and optimize inductors.

# IV. EXPERIMENTAL RESULTS

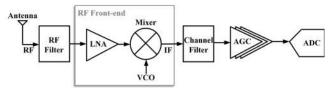

The methodology presented in Section III can be applied to any RF system, technology process and communication standard. In this Section, experimental results are shown for a low-IF RF front-end receiver in a 0.35-µm CMOS technology for the ISM band. The selection of the technology process in these experiments was motivated by the availability of foundry data for EM simulation. In Fig. 5, an RF receiver is depicted. For the experimental results in this paper, the RF front-end composed of an LNA, a VCO and a mixer is considered.

Fig. 5. Complete RF receiver signal chain with focus on the RF front-end (LNA, VCO and Mixer).

As shown in Fig. 1, the methodology is based on hierarchical partitioning and composition, from the device level up to the system level. By ensuring that each low-level device/circuit design performs well for the entire 2.4-2.5GHz ISM band we ensure that any receiver working in this band can be designed (e.g., Bluetooth, Bluetooth Low Energy, ZigBee, Wi-Fi/WLAN, etc.).

#### A. Device-Level Synthesis

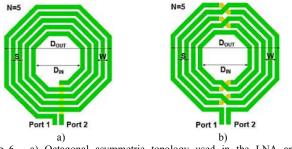

The first step of the methodology is to optimize the devices that correspond to the lowest hierarchical level of the system. In this work, the two inductor topologies illustrated in Fig. 6 are considered: an octagonal asymmetric topology and an octagonal symmetric topology. The search space for the inductors is presented in Table I (for both topologies, where N is the number of turns of the inductor,  $D_{in}$  is the inner diameter and W is the turn width.). The minimum inner diameter and turn width, as well as the grid size, are imposed by the design rules of the technology process. Upper limits are reasonably high values, well beyond what is commonly found and is of interest for cost reasons. The same occurs for the number of turns: higher numbers are never used, especially for relatively high frequencies. These inductors are designed by using surrogate models that present less than 1% error when compared to EM

Fig. 6. a) Octagonal asymmetric topology used in the LNA and b) octagonal symmetric topology used in the VCO.

TABLE I

DESIGN VARIABLES FOR THE INDUCTORS.

| N   |     |      | D <sub>in</sub> (μm) |     |      | W (µm) |     |      |

|-----|-----|------|----------------------|-----|------|--------|-----|------|

| Min | Max | Grid | Min                  | Max | Grid | Min    | Max | Grid |

| 1   | 8   | 1    | 10                   | 300 | 0.05 | 5      | 25  | 0.05 |

simulations, which is an extremely accurate estimation that will introduce an also extremely negligible deviation when simulating the circuit performances.

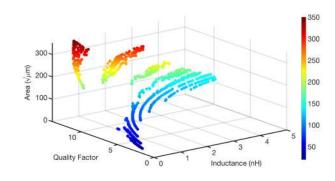

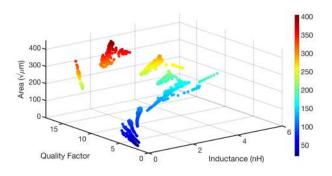

Two optimizations, one for each topology, were carried out with three design objectives: maximization of the quality factor, Q, maximization of inductance, L, and minimization of the area. Both optimizations were performed with 1000 individuals and 80 generations and several constraints were imposed to guarantee the proper behavior of inductors at the entire frequency band. These constraints are:

$$\begin{cases} area < 400 \mu m \times 400 \mu m \\ \frac{L_{@WF} - L_{@WF} + 0.05GHz}{L_{@WF}} | < 0.01 \\ \frac{L_{@WF} - L_{@WF} - 0.05GHz}{L_{@WF}} | < 0.01 \\ \frac{L_{@WF} - L_{at \ 0.1GHz}}{L_{@WF}} | < 0.05 \\ Q_{@WF} + 0.05GHz - Q_{@WF} > 0 \end{cases}$$

(2)

where  $L_{@WF}$  and  $Q_{@WF}$  are the inductance and quality factor at the working frequency (WF), which, in this case, is the center of the ISM band (2.45GHz) [20]. The inductance and quality factor at any frequency can be easily obtained from the S-parameters [27]. The second and third constraint in (2) guarantee that the inductance is very flat around the WF. In addition, the fourth constraint guarantees that the inductance is sufficiently flat from low frequencies up to the WF (preventing in this way a significant inductance valley that typically appears in integrated inductors). The last constraint in (2) guarantees that the maximum of the quality factor is beyond the working frequency and, therefore, that the inductor self-resonance frequency (SRF) will still be at higher frequencies. The obtained POFs are shown in Fig. 7 and Fig. 8.

The individuals of these POFs represent fully-sized inductors

Fig. 7. POF of the inductor octagonal asymmetric topology. The color bar represents the area objective.

| Table II                                              |  |

|-------------------------------------------------------|--|

| SPECIFICATIONS FOR THE LNA, VCO, MIXER OPTIMIZATIONS. |  |

| LNA Performance                       | LNA Specifications         | VCO Performance  | VCO Specifications          | Mixer Performance         | Mixer Specifications              |

|---------------------------------------|----------------------------|------------------|-----------------------------|---------------------------|-----------------------------------|

| S <sub>11</sub> @ 2.45; 2.5; 2.55 GHz | < -12 dB                   | $f_{ m osc}$     | > 2.45 GHz                  | CG @ 10 MHz               | > 5 dB                            |

| S <sub>22</sub> @ 2.45; 2.5; 2.55 GHz | < -12 dB                   | $f_{\rm osc}$    | < 2.55 GHz                  | CG @ 40 MHz               | > 5 dB                            |

| S <sub>21</sub> @ 2.45; 2.5; 2.55 GHz | Maximize                   | PN @ 1MHz        | Minimize                    | P <sub>DC</sub>           | Minimize                          |

| 521 (6) 2. 13, 2.3, 2.33 (31)2        | (>7 dB)*                   | offset           | $(< -110 \text{ dBc/Hz})^*$ | T DC                      | $(< 20 \text{ mW})^*$             |

| k                                     | > 1                        | $P_{DC}$         | Minimize<br>(< 20 mW)*      | NF @ 10 MHz               | < 20 dB                           |

| NF @ 2.45; 2.5; 2.55 GHz              | Minimize                   | P <sub>OUT</sub> | <b>Maximize</b> (> -2 dBm)* | NF @ 40 MHz               | $     Minimize      (< 20 dB)^* $ |

| $P_{ m DC}$                           | <b>Minimize</b> (< 20 mW)* |                  |                             | IIP <sub>3</sub>          | <b>Maximize</b> (> -15 dBm)*      |

| IIP <sub>3</sub>                      | > -15 dBm                  |                  |                             | Port-to-Port<br>Isolation | >30 dB                            |

| Area (μm²)                            | Minimize                   | Area (μm²)       | Minimize                    | Area (μm²)                | Minimize                          |

<sup>\*</sup>Although this performance is given as an objective a constraint is also imposed.

Fig. 8. POF of the inductor octagonal symmetric topology. The color bar represents the area objective.

whose performances (L, Q and Area) correspond to the best trade-offs for the selected technology and working frequency. This means that, for a given L value, inductors with the smallest possible area and highest Q values in this technology will be available in the POF. After the inductor optimization is performed, the inductor POFs are mapped into matrices, as described in Section III.B, and used as inductor search space in the following circuit optimizations.

# B. Circuit-Level Synthesis

The second step in the methodology is to optimize the circuitlevel blocks that compose the system. Therefore, in this subsection, the optimization of the three individual circuits (LNA, VCO and mixer) used in the RF front-end are illustrated. In our methodology, all circuits are simulated using SpectreRF (although the methodology is completely independent from the

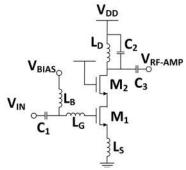

Fig. 9. Schematic of the LNA.

TABLE III

DESIGN VARIABLES FOR THE LNA OPTIMIZATION.

| Variables        | Min                         | Max             | Step  |  |  |  |  |

|------------------|-----------------------------|-----------------|-------|--|--|--|--|

| $W_{1,2}(\mu m)$ | 30                          | 600             | 10    |  |  |  |  |

| 11,2             |                             | Fixed @ 0.35 μm |       |  |  |  |  |

| $V_{bias}(V)$    | 0.001                       | 1.5             | 0.001 |  |  |  |  |

| Inductors        | Selected from POF in Fig. 7 |                 |       |  |  |  |  |

| $C_{1,2,3}$ (pF) | 0.4                         | 4               | 0.4   |  |  |  |  |

electrical simulator), providing therefore the utmost accuracy at each level of the hierarchy. As power and area will be optimization objectives at the receiver level, it is essential that they are also optimized at the circuit level for all RF blocks.

Regarding the LNA design, the circuit is intended to operate at any frequency of the ISM band (2.4-2.5GHz), with a supply voltage of  $V_{DD}$ =2.5V. The LNA topology considered is a source-degenerated LNA shown in Fig. 9. The LNA has several important performance parameters that need to be considered during the design process: noise figure NF, gain  $S_{21}$ , power consumption  $P_{DC}$ , third-order intercept point IIP<sub>3</sub>, input matching coefficient  $S_{11}$ , output matching coefficient  $S_{22}$ , Rollet stability factor k (if smaller than 1, the LNA is potentially unstable) and the area occupation (extremely important as it is directly related to the manufacturing cost in IC technologies).

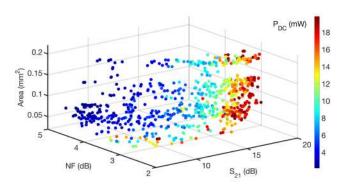

According to Friis's equations [28], for the design of an RF cascaded system, the NF of the LNA is the main contributor to the NF of the receiver; therefore, it should be minimized. In most of the reported optimization-based approaches, the calculation of the IIP<sub>3</sub> is usually avoided due to the needed power sweep, which is time consuming and degrades the efficiency of the optimization. In this work, a highly efficient technique is used in order to calculate the IIP3, where no power sweep is needed [12]. The LNA optimization was performed with 800 individuals, 300 generations and had four objectives: maximization of  $S_{21}$  and minimization of area, NF and  $P_{DC}$ . The specifications are shown in Table II. Notice that in some cases, constraints have also been imposed on optimization objectives (e.g., lower constraint for gain or upper constraint for power). Although this is not strictly necessary, it helps the optimizer to avoid exploring search regions we are clearly not interested in. The search space is defined in Table III and the result of the optimization is shown in Fig. 10. Notice that, for this graphical representation, the 3-D plot is used for three objectives (S<sub>21</sub>, NF

Fig. 10. Obtained LNA POF. The color bar represents the power consumption, the fourth objective in the optimization.

and area), while a color bar is used for the fourth objective  $(P_{DC})$ .

With this LNA POF, the designer is in possession of the best trade-offs available for the selected performances, which means that for a given value of  $S_{21}$ , the LNA with lowest NF,  $P_{DC}$  and area is available in the POF. After the circuit optimization, the POF has to be mapped into a matrix for higher level optimizations. Since this POF has 4 objectives, it has to be mapped into a matrix using three indexes.

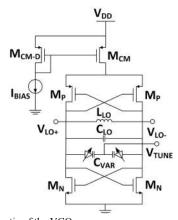

The next circuit considered for optimization is the VCO. This circuit is intended to oscillate at a frequency of 2.5GHz with a supply voltage of  $V_{DD}$ =2.5V. From the several VCO topologies available, in this work, a cross-coupled double-differential VCO, depicted in Fig. 11, has been considered. The most important VCO performances are: oscillation frequency ( $f_{osc}$ ), phase noise (PN), power consumption ( $P_{DC}$ ), output swing ( $P_{OUT}$ ), which is an important performance parameter especially when the VCO is connected to a mixer, and, finally, the area occupation.

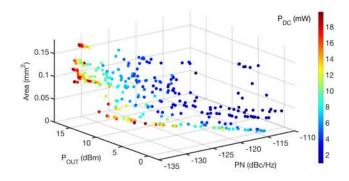

The VCO optimization was carried out with 300 individuals, 100 generations and four objectives: maximization of  $P_{OUT}$  and minimization of PN,  $P_{DC}$  and area. The specifications are shown in Table II, the design variables are listed in Table IV and the optimization results are plotted in Fig. 12. As in the previous example, the resulting POF has the best trade-offs for the chosen performances, which means that, for a given value of  $P_{DC}$ , the VCO with lowest PN, area and highest  $P_{OUT}$  is available

Fig. 11. Schematic of the VCO.

DESIGN VARIABLES FOR THE VCO OPTIMIZATION.

Variables

Min

Max

Step

$w_n$  (μm)

10

200

10

$p_{\text{CM-D,CM}}$  (μm)

10

150

10

TABLE IV

| $w_{\rm n}(\mu m)$                                      | 10              | 200              | 10          |  |  |  |

|---------------------------------------------------------|-----------------|------------------|-------------|--|--|--|

| $w_{\rm p,CM-D,CM}$ ( $\mu m$ )                         | 10              | 150              | 10          |  |  |  |

| $l_{\rm n,p,CM-D,CM}$                                   |                 | Fixed @ 0.35     | μm          |  |  |  |

| $I_{bp}(mA)$                                            | 0.1             | 5                | 0.1         |  |  |  |

| $w_{\text{Cvar}}(\mu \text{m})$                         |                 | Fixed @ 6.6 μm   |             |  |  |  |

| $l_{\mathrm{Cvar}}(\mu\mathrm{m})$                      | Fixed @ 0.65 μm |                  |             |  |  |  |

| Inductors                                               | Sele            | cted from the PO | F in Fig. 8 |  |  |  |

| Row <sub>Cvar</sub> ,Col <sub>Cvar</sub> <sup>(1)</sup> | 4               | 12               | 1           |  |  |  |

| C (pF)                                                  | 0.4             | 4                | 0.4         |  |  |  |

<sup>(1)</sup> Row<sub>Cvar</sub> is the number of fingers per row and Col<sub>Cvar</sub> is the multiplicity of the varactors.

in the POF. Since four objectives were considered, the VCO POF is also mapped using three indexes.

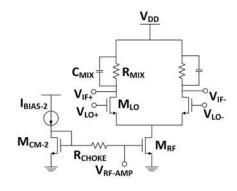

The last circuit block considered for optimization is the down-conversion mixer, which converts the RF frequency (coming from the LNA) into a lower intermediate frequency (IF). The Gilbert cell mixer topology shown in Fig. 13 has been used. The mixer optimization is performed setting an ideal RF signal at 2.46GHz and an ideal local oscillator (LO) signal at 2.5GHz. The mixer operates with a supply voltage V<sub>DD</sub>=2.5V. The most important performance parameters for the mixer are: conversion gain (CG), P<sub>DC</sub>, IIP<sub>3</sub>, which is extremely important in mixers because it usually dominates the IIP<sub>3</sub> of the entire cascaded RF system [28], Port-to-Port isolation, which is a measure of how well the ports (RF, LO and IF) are separated

Fig. 12. Obtained VCO POF. The color bar represents the power consumption, the fourth objective in the optimization.

Fig. 13. Schematic of the mixer.

$\label{eq:table_variables} Table~V \\ Design variables for the Mixer optimization.$

| Variables                | Min             | Max    | Step |  |  |  |

|--------------------------|-----------------|--------|------|--|--|--|

| $W_{LO,RF,CM-2}(\mu m)$  | 10              | 200    | 10   |  |  |  |

| $L_{LO,RF,CM-2}$         | Fixed @ 0.35 μm |        |      |  |  |  |

| I <sub>BIAS-2</sub> (mA) | 0.1             | 1.5    | 0.1  |  |  |  |

| $R_{CHOKE}(\Omega)$      | 10              | 24,000 | 10   |  |  |  |

| $R_{MIX}(\Omega)$        | 10              | 18,000 | 10   |  |  |  |

| C <sub>MIX</sub> (pF)    | 0.3             | 3      | 0.3  |  |  |  |

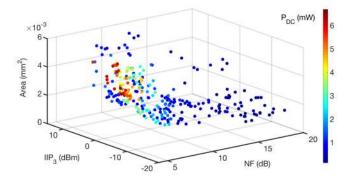

Fig. 14. Obtained POF of the Gilbert cell mixer. The color bar represents the power consumption, the fourth objective in the optimization.

from each other in terms of unwanted signal coupling (typically, an isolation of 30dB is in most cases considered "high isolation"), NF, which is not a very critical performance in mixers because in cascaded systems it is divided by the LNA gain [28], and, finally, the area occupation.

The mixer optimization was performed with 300 individuals, 100 generations and four objectives: maximization of IIP<sub>3</sub> and minimization of P<sub>DC</sub>, NF and area. The desired specifications are shown in Table II, the design variables are listed in Table V and the results of the optimization are depicted in Fig. 14. In the mixer, CG and NF constraints in Table II were imposed at two different IF frequencies in order to guarantee that the constraints are met for an IF band from 10 to 40MHz. Since four objectives were considered, the mixer POF is also mapped using three indexes.

#### C. Receiver Front-end Synthesis

After obtaining the POF for each individual circuit (LNA, VCO and mixer), the next optimization is performed at the third hierarchical level in order to compose the individual blocks that together empower the best front-ends for a given communication standard. Due to the hierarchical POF reusability that the methodology enables, the previous optimizations (passives and circuits) only have to be performed once for a given frequency band. Afterwards, the POFs can be stored and reused for any given communication standard that operates in the same frequency band. In the following, the receiver synthesis is illustrated for two different standards: Bluetooth and Wi-Fi.

#### 1) Bluetooth Receiver Synthesis

It was shown in [29] that the specifications for the Bluetooth standard (IEEE 802.15.1) yield NF<8.79dB and

$TABLE\ VI$  Desired Specifications for the receiver front-end optimizations.

| Front-end Performance | Bluetooth standard | Wi-Fi standard |  |  |

|-----------------------|--------------------|----------------|--|--|

| CG @ down-frequency   | > 12 dB            | > 12 dB        |  |  |

| CG @ up-frequency     | > 12 dB            | > 12 dB        |  |  |

| $P_{DC}$              | Minimize           | Minimize       |  |  |

| r <sub>DC</sub>       | < 40 mW            | < 40 mW        |  |  |

| NF @ down-frequency   | < 8.79 dB          | < 5.64 dB      |  |  |

| NF @ up-frequency     | < 8.79 dB          | < 5.64 dB      |  |  |

| IIP <sub>3</sub>      | > -10.35 dBm       | > -20.3 dBm    |  |  |

| Area (μm²)            | Minimize           | Minimize       |  |  |

|                       |                    |                |  |  |

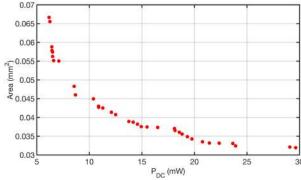

$IIP_3$ >-10.35dBm. Furthermore, assuming that the receiver is designed for an IoT application, the receiver area and  $P_{DC}$  need to be kept at a minimum. The constraints and objectives for the receiver synthesis are shown in Table VI. The optimization was performed with 160 individuals and 60 generations.

Similar to the mixer optimization, the receiver CG and NF constraints were ensured at two different IF frequencies in order to guarantee that the constraints are met for the IF band. However, while for the mixer optimization an ideal LO of 2.50GHz was used, now, for the receiver, a real VCO is used, which may oscillate between 2.45-2.55GHz (as imposed in the VCO constraints). Therefore, the up- and down-frequency will vary depending on which VCO is used in the receiver (the desired IF is then selected by tuning the VCO using V<sub>TUNE</sub> shown in Fig. 11). The result of the optimization can be seen in Fig. 15. Each red dot in Fig. 15 represents a fully-sized RF receiver front-end, compliant with the Bluetooth standard with its performances obtained with accurate EM simulation of the inductors and electrical simulation accuracy at higher levels.

Fig. 15. POF of the front-ends compliant with the Bluetooth standard.

Fig. 16. POF of the front-ends compliant with the Wi-Fi standard

| TABLE VII                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------|

| CONSTRAINTS FOR THE DIFFERENT OPTIMIZATION STRATEGIES. ILLUSTRATING THE NUMBER OF DESIGN VARIABLES AND CONSTRAINTS. |

| Performance                      | В              | U        | CIR       |                 | IND              |          |

|----------------------------------|----------------|----------|-----------|-----------------|------------------|----------|

| reriormance                      | Bluetooth      | Wi-Fi    | Bluetooth | Wi-Fi           | Bluetooth        | Wi-Fi    |

| S <sub>11</sub> (dB)             | x <sup>a</sup> | X        | <-12      | <-12            | <-12             | <-12     |

| CG (dB)                          | >12            | >12      | >12       | >12             | >12              | >12      |

| NF (dB)                          | <8.79          | < 5.64   | <8.79     | < 5.64          | <8.79            | < 5.64   |

| IIP <sub>3</sub> (dBm)           | >-10.35        | >-20.30  | >-10.35   | >-20.30         | >-10.35          | >-20.30  |

| $f_{\rm osc}$ (VCO) (GHz)        | X              | X        | >2.45     | >2.45           | >2.45            | >2.45    |

| $f_{\rm osc}$ (VCO) (GHz)        | X              | X        | <2.55     | < 2.55          | <2.55            | < 2.55   |

| Port-to-port isolation (dB)      | X              | X        | >30dB     | >30dB           | >30dB            | >30dB    |

| Inductor Constraints             | X              | X        | X         | X               | yes <sup>b</sup> | yes      |

| $P_{DC}(mW)$                     | <40            | <40      | <40       | <40             | <40              | <40      |

| $P_{DC}$                         | Minimize       | Minimize | Minimize  | Minimize        | Minimize         | Minimize |

| Area                             | Minimize       | Minimize | Minimize  | Minimize        | Minimize         | Minimize |

| Optimization settings            |                |          |           |                 |                  |          |

| Total number of design variables | 9°             | 9        | 33        | 33 <sup>d</sup> | 38 <sup>e</sup>  | 38       |

| Total number of constraints      | 6              | 6        | 15        | 15              | 40               | 40       |

<sup>&</sup>lt;sup>a</sup>The constraints marked with an x were already imposed at device/circuit level and do not need to be imposed at the circuit/system level.

<sup>&</sup>lt;sup>e</sup>All the design variables of the LNA, VCO and mixer, plus the geometrical parameters of inductors are considered.

Fig. 17. Timeline of the entire proposed design methodology for the design of RF systems.

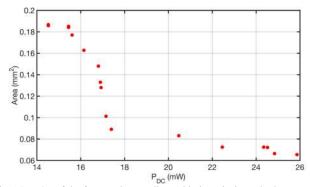

# 2) Wi-Fi Receiver Synthesis

It was shown in [29] that the required performances for the Wi-Fi standard (IEEE 802.11b) are NF<5.64dB and IIP<sub>3</sub>>-20.3dBm. The constraints and objectives of the receiver synthesis are shown in Table VI and the result from an optimization process with 160 individuals and 60 generations is presented in Fig. 16.

By comparing Fig. 15 and Fig. 16, it is possible to observe that the Bluetooth POF achieves designs with lower area and power consumption, which is due to the more relaxed NF specification of the Bluetooth standard.

The total design time for the entire methodology can be seen in Fig. 17. As mentioned before, one of the very important advantages of the proposed approach is its hierarchical reusability. This feature allows the designers to reuse, over and over, the lower level POFs in order to optimize the front-end for different standards. Therefore, if a POF for another standard is desired, the designer only needs to perform the system-level optimization without the need for re-optimizing each individual circuit. After that, in a few hours, several fully-sized RF front-ends (or any other system, since the methodology can be applied to other blocks) are ready for its physical implementation.

# V. COMPARISON TO OTHER PARTITIONING STRATEGIES

In order to assess the advantages of the proposed methodology, this section reports several comparisons to other alternative partitioning strategies.

# A. Device-Level Hierarchical Optimization

In this sub-section, a device-level optimization methodology is applied. This optimization is considered at the device-level, without any type of hierarchical partitioning. Therefore, all circuits and passives are sized during the optimization. This optimization, denoted as IND, is the most straightforward. Thus, the search space includes all the design variables shown in Table I for the inductors, and in Tables III to V for the circuits. During the optimization, surrogate models of the Sparameters are used to evaluate the performances of both the asymmetric and symmetric inductors considered during the sizing process [11]. Accurate performances of the complete front-end are simulated with an electrical simulator.

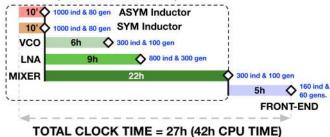

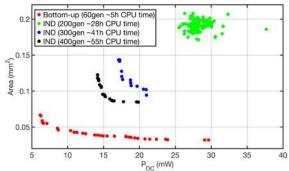

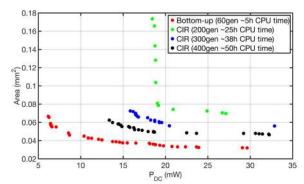

Several factors can be considered for comparison of the different methodologies: accuracy, quality of the results and efficiency. In this work, all methodologies use the same evaluation techniques and therefore the accuracy is the same. Therefore, the comparison will be centered around efficiency and quality of the final results. Since the BU strategy presented in Section III and the IND strategy have different number of design variables and design constraints, as shown in Table VII, a CPU criterion will be used in order to compare both strategies. It was shown in Fig. 17 that the BU strategy needed around 42 hours of CPU time to get the 2D POF of the front-end, including the time needed to optimize all the passives, circuits and system. Therefore, for the IND strategy, the optimization was allowed to run with the same number of individuals of the system-level optimization of the BU approach and for a large number of generations. The POF obtained at several generations and corresponding CPU times is compared to the BU approach in Fig. 18 for the Bluetooth standard and in Fig.

<sup>&</sup>lt;sup>b</sup>The inductor constraints are the ones imposed in order to ensure that the inductors are in the flat-BW zone, as explained in Section IV.A.

<sup>&</sup>lt;sup>c</sup>The design variables of the BU strategy are the indexes of the matrix mapping for each circuit.

<sup>&</sup>lt;sup>d</sup>All design variables of the LNA, VCO and mixer are considered. The inductors are passed as indexes from the matrix mapping.

Fig. 18. Comparison between the POFs obtained with the BU and IND strategies for the Bluetooth standard.

Fig. 19. Comparison between the POFs obtained with the BU and IND strategies for the Wi-Fi standard.

#### 19 for the Wi-Fi standard.

The CPU time for the entire BU strategy is 42 hours. However, due to the low-level hierarchical reusability, the optimization of the passives and circuits only has to be performed once. Therefore, the actual system synthesis takes only 5 hours of CPU time. In both Fig. 18 and Fig. 19, the BU POF is represented with red dots, while the green dots, represent the population of solutions of the IND approach at generation 200, where the consumed CPU time was around 28 hours. At this generation, a cloud of points, rather than an actual POF (for both Bluetooth and Wi-Fi) is obtained. Therefore, the optimization was allowed to evolve further for 400 generations (black dots in Fig. 18 and Fig. 19), extending to a total CPU time of 55 hours. Despite this high CPU time figure, the IND strategy cannot achieve the same results as the BU strategy since the POFs obtained for both standards are completely dominated by the POFs obtained using the BU strategy. Therefore, this comparison clearly endorses the usage of BU strategies over IND strategies for RF circuit design.

From the optimization times shown in Fig. 18 and Fig. 19 it may be perceived that there is a lack of proportionality between the BU and IND CPU optimization times. The BU strategy performs 9,600 electrical simulations of the front-end (160 individuals along 60 generations), and the IND strategy performs 64,000 simulations (160 individuals along 400 generations). In the IND strategy, roughly 7 times the number of simulations are performed but the optimization time is more than 7 times that of the BU strategy. This is due to several reasons:

- In the IND strategy, the inductors are designed during the optimization. Since surrogate models are being used, the S-parameter files have to be created at each generation, whereas in the BU strategy, these files are created a priori only for the inductors of the POF.

- The IND strategy has to perform more simulations at each generation in order to comply with all front-end constraints. In order to evaluate the front-end input matching, an S-parameter analysis must be performed, and, in order to consider the port-to-port isolation, a periodic transfer function analysis must be performed too. In the BU strategy, these analyses are performed during the simulation of the LNA and the mixer, relieving, therefore, the front-end optimizations from these simulations.

- The time needed for the periodic steady-state analysis highly depends on the individual design being simulated, because the analysis needs to converge to a steady-state. Whereas in the BU strategy every single LNA, VCO and mixer designs are fully functional, in the IND strategy, especially during the initial stages of the optimization, there may be many designs that take longer to converge.

From the obtained Bluetooth and Wi-Fi POFs, and the previous given drawbacks of the IND strategy, it may be concluded that the BU strategy is more efficient and achieves much better results than the IND strategy.

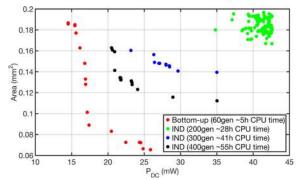

# B. Circuit-Level Hierarchical Optimization

The IND strategy has the drawback of having to design the inductors in an online style (i.e., during the optimization), thus considerably increasing the number of design variables and constraints imposed. Therefore, it may be possible that the optimization algorithm struggles to converge to optimal solutions. In order to study the effect of such online inductor design in the entire front-end optimization, a circuit-level hierarchical optimization, denoted as CIR, is performed, where the circuits composing the front-end (LNA, VCO and mixer) are sized at the same optimization. However, the inductors are designed previously and passed as a POF.

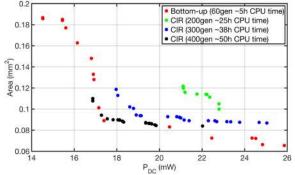

Again, since a fair comparison between BU and CIR strategies is difficult, the optimization was run with the same number of individuals but for a longer CPU time in order to inspect the convergence of the optimization. The results of the optimization can be seen in Fig. 20 for the Bluetooth standard and in Fig. 21 for the Wi-Fi standard.

The front-end POF obtained with the BU strategy is illustrated with red dots in both Fig. 20 and Fig. 21. Green dots are used to depict the CIR POF at generation 200, reached after 25 hours of CPU time. It can be seen that the obtained POF is still far away from the one obtained with the BU strategy. The optimization was run up to 50 hours of CPU time, where the obtained POF is shown with black dots in Fig. 20 and Fig. 21. It is possible to observe that by just using the inductor POF, the obtained results are widely improved (e.g., see green dots in Fig. 18 and Fig. 20).

By comparing the BU and the CIR results for the Bluetooth standard it is reasonable to conclude that, despite the longer CPU time of the CIR approach (50 hours), the obtained POF is completely dominated by the POF obtained with the BU

Fig. 20. Comparison between the POFs obtained with the BU and CIR strategies for the Bluetooth standard.

Fig. 21. Comparison between the POFs obtained with the BU and CIR strategies for the Wi-Fi standard.

strategy. For the Wi-Fi standard, shown in Fig. 21, the CIR optimization with 400 generations slightly overlaps the BU POF; however, the BU POF is much wider and achieves lower power consumptions and lower areas.

#### VI. CONCLUSIONS

In this work, a multilevel BU circuit design methodology was described and applied to the design of an RF system composed of an LNA, a VCO and a mixer. By using such multilevel BU strategy, different circuits can be assembled to design an RF system. Furthermore, each level of the hierarchy is simulated with the utmost accuracy possible: EM accuracy at device-level and electrical simulations at circuit/system-level. Also, the methodology developed in this work, promotes the hierarchical reusability of low-level POFs. Moreover, the methodology proved to be highly efficient and presented superior results when compared to other alternative partitioning and synthesis strategies. To the best of the authors' knowledge, the design of an RF system, using a multilevel BU approach, has been demonstrated for the first time in this work.

#### REFERENCES

- R.A. Rutenbar, G.E. Gielen and J. Roychowdhury, "Hierarchical modeling, optimization, and synthesis for system-level analog and RF designs," in Proc. IEEE, vol. 95, no. 3, pp. 640-669, 2007.

- [2] B. Liu, G. Gielen and F.V. Fernandez, Automated design of analog and high-frequency circuits, Springer, 2014.

- [3] G. Tulunay and S. Balkir, "A synthesis tool for CMOS RF low-noise amplifiers," in IEEE Trans. Comp.-Aided Design Integr. Cir. Sys., vol. 27, no. 5, pp. 977–982, May 2008.

- [4] R. Gupta, B. Ballweber and D. Allstot, "Design and optimization of CMOS RF power amplifiers," in IEEE J. Solid-State Cir., vol. 36, no. 2, pp. 166-175, Feb. 2001.

- [5] G. Zhang, A. Dengi, and L. R. Carley, "Automatic synthesis of a 2.1 GHz SiGe low noise amplifier," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), pp. 125–128, 2002.

- [6] Y. Xu, K.-L. Hsiung, X. Li, L. T. Pileggi, and S. P. Boyd, "Regular analog/RF integrated circuits design using optimization with recourse including ellipsoidal uncertainty," in IEEE Trans. Comp.-Aided Design Integr. Cir. Sys., vol. 28, no. 5, pp. 623–637, May 2009.

- [7] C. Ranter, et. al., "CYCLONE: automated design and layout of RF LC-oscillators," in IEEE Trans. Comp.-Aided Design of Integr. Cir. Sys., vol. 21, no. 10, pp. 1161-1170, Oct. 2002.

- [8] G. Alpaydin, S. Balkir and G. Dundar, "An evolutionary approach to automatic synthesis of high-performance analog integrated circuits," IEEE Trans. Evol. Comp., vol.7, pp. 240-252, June 2003.

- [9] R. Povoa, I. Bastos, N. Lourenço, N. Horta, Automatic synthesis of RF front-end blocks using multi-objective evolutionary techniques, *Integration, the VLSI Journal*, vol. 52, pp. 243-252, 2016.

- [10] M. Chu and D. J. Allstot, "Elitist nondominated sorting genetic algorithm based RF IC optimizer," in *IEEE Trans. Cir. and Sys. I*, vol. 52, pp. 535-545, 2005.

- [11] F. Passos, R. Gonzalez-Echevarria, E. Roca, R. Castro-Lopez and F. V. Fernandez, "A two-step surrogate modeling strategy for single-objective and multi-objective optimization of radiofrequency circuits", in Soft Computing, 2018, doi: 10.1007/s00500-018-3150-9.

- [12] R. Gonzalez-Echevarria, et al., "An automated design methodology of RF circuits by using Pareto-optimal fronts of EM-simulated inductors," in *IEEE Trans. Comp.-Aided Design of Integr. Cir. Sys.*, vol. 36, no. 1, pp. 15-26, Jan. 2017.

- [13] D. Ghai, S. P. Mohanty and E. Kougianos, "Design of parasitic and process-variation aware nano-CMOS RF circuits: a VCO case study," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 17, no. 9, pp. 1339-1342, Sept. 2009.

- [14] S. P. Mohanty and E. Kougianos, "Incorporating manufacturing process variation awareness in fast design optimization of nanoscale CMOS VCOs," in *IEEE Transactions on Semiconductor Manufacturing*, vol. 27, no. 1, pp. 22-31, Feb. 2014.

- [15] G. Gielen, "Modeling and analysis techniques for system-level architectural design of telecom front-ends," in IEEE Trans. Microwave Theory and Techniques, vol. 50, no. 1, pp. 360-368, 2002.

- [16] D. Rodriguez de Llera Gonzalez, A. Rusu, and M. Ismail, "Receiver design for multi-standard wireless communications," in Radio Design in Nanometer Technologies, D. Rodríguez de Llera González and M. Ismail, Eds. New York: Springer, 2006.

- [17] W. Sheng, A. Emira, and E. Sanchez-Sinencio, "CMOS RF receiver system design: A systematic approach," in *IEEE Trans. Cir. and Sys. I*, vol. 53, pp. 1023-1034, May 2006.

- [18] S. Rodriguez, J. Atallah, A. Rusu, L. Zheng and M. Ismail, "ARCHER: an automated RF-IC Rx front-end circuit design tool," in Analog Integrated Circuits and Signal Processing, vol. 58, no. 3, pp. 255-270, 2009.

- [19] Zhijian Pan, Chuan Qin, Zuochang Ye and Y. Wang, "Automatic design for analog/RF front-end system in 802.11ac receiver," *The 20th Asia and South Pacific Design Automation Conference*, Chiba, 2015, pp. 454-459.

- [20] F. Passos, E. Roca, R. Castro-Lopez, F.V. Fernandez, "Radio-frequency inductor synthesis using evolutionary computation and Gaussian-process surrogate modeling", in *Applied Soft Computing*, vol. 60, pp. 495-507, 2017.

- [21] T. Eeckelaert, R. Schoofs, G. Gielen, M. Steyaert, and W. Sansen, "An efficient methodology for hierarchical synthesis of mixed-signal systems with fully integrated building block topology selection," in Proc. Conf. Design, Automation and Test in Europe, 2007, pp. 81–86.

- [22] K. Deb, A. Pratap, S. Agarwal, T. Meyarivan, "A fast and elitist multiobjective genetic algorithm: NSGA-II", *IEEE Trans. Evol. Comp.*, vol. 6, no. 2, pp. 182-197, 2002.

- [23] M. Velasco-Jimenez, R. Castro-Lopez, E. Roca and F. V. Fernandez, "Implementation issues in the hierarchical composition of performance models of analog circuits," in Proc. Conf. Design, Automation and Test in Europe, 2014, pp. 1-6.

- [24] A. I. J. Forrester, A. Sobester, and A. J. Keane, Engineering design via surrogate modelling - A Practical Guide. Wiley, 2008.

- [25] O. Okobiah, S. Mohanty and E. Kougianos, "Fast design optimization through simple kriging metamodeling: a sense amplifier case study," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 22, no. 4, pp. 932-937, April 2014.

- [26] M. B. Yelten, P. D. Franzon and M. B. Steer, "Surrogate-model-based analysis of analog circuits—part I: variability analysis," in *IEEE Transactions on Device and Materials Reliability*, vol. 11, no. 3, pp. 458-465, Sept. 2011.

- [27] K. Okada and K. Masu, "Modeling of spiral inductors," Advanced Microwave Circuits and Systems, InTech, 2010.

- [28] H. T. Friis, "Noise figures of radio receivers", Proc. IRE, vol. 32, pp.419-422, 1944

- [29] A. Emira, Bluetooth/WLAN receiver design methodology and IC implementations. PhD thesis, Texas A&M University. Texas A&M University, 2003.

**Fábio Passos** received the M.Sc. degree from Universidade Nova de Lisboa, Lisbon, Portugal, in 2013 and the Ph.D. degree from Universidad de Sevilla, Seville, Spain, in 2018.

He is working as a Post-Doctoral Researcher at the Institute of Microelectronics of Seville (IMSE), CNM-CSIC, Seville, Spain. In 2018 he worked at Analog Devices, Valencia, Spain, for 3 months (as part of a

technology transfer collaboration between IMSE and Analog Devices) developing automated design methodologies for mm-Wave systems. His research interests include the modeling of passive RF devices, automated design methodologies for analog, RF and mm-Wave circuits and reliability issues in analog/RF ICs. Dr. Passos, was the recipient of the Outstanding Paper Award in MIXDES 2013 and the Best Paper Award in SMACD 2018. He was also the SMACD 2016 EDA competition winner.

Elisenda Roca received the Ph.D. degree in Physics from the University of Barcelona, Spain, in 1995. From November 1990 to April 1995, she worked at IMEC, Leuven, Belgium, in the field of infrared detection aiming to obtain large arrays of CMOS compatible silicide Schottky diodes. Since 1995, she has been with the Institute of Microelectronics of Seville, (IMSE-CNM-CSIC), Spain, where she holds the position of Tenured Scientist. Her research interests lie in the field of modeling and design

methodologies for analog, mixed-signal and RF integrated circuits. She has been involved in several research projects with different institutions: Commission of the EU, ESA, ONR-NICOP, etc. She has also co-authored more than 100 papers in international journals, books, and conference proceedings

Javier Sieiro received the Ph.D. degree in physics from the University of Barcelona, Barcelona, Spain, in 2001. From 2002 to 2003, he was a member of the ECTM Group, Delft University of Technology, Delft, The Netherlands, where he was involved in the modeling of passive components and in the design of RFIC circuits. Since 2003, he has been with the Department of Electronics, University of Barcelona, where he is currently an Associate Professor. His current research interests include modeling of passive components and RF circuits.

Rafaella Fiorelli (S'05–M'13) received the B.Sc. and M.Sc. degrees in electrical engineering from the Universidad de la República, Montevideo, Uruguay, in 2002 and 2005, respectively, and the M.Sc. and Ph.D. degrees from the Universidad de Sevilla, Seville, Spain, in 2009 and 2012, respectively. From 2003 to 2009, she joined the Electrical Engineering Institute, Universidad de la República. Since 2009, she is with the Instituto de Microelectrónica de Sevilla (IMSE-CNM), CSIC and the Universidad de Sevilla. Her current research

includes the development of methodologies for low-power RF blocks, and the design of implantable low-power medical devices for neural stimulation and recording.

Rafael Castro-López received the "Licenciado en Física Electrónica" degree (M.S. degree on Electronic Physics) and the "Doctor en Ciencias Físicas" (Ph.D. degree) from the University of Seville, Spain, in 1998 and 2005, respectively. Since 1998, he has been working at the Institute of Microelectronics of Seville (CSIC-IMSE-CNM) of the Spanish Microelectronics Center, where he now holds the position of Tenured Scientist. His research interests lie in the field of integrated circuits, especially design and computer-

aided design for analog and mixed-signal circuits. He has participated in several national and international R&D projects and co-authored more than 100 international scientific publications, including journals, conference papers, book chapters and the book Reuse-based Methodologies and tools in the Design of Analog and Mixed-Signal Integrated Circuits (Springer, 2006).

José María López-Villegas received the Ph.D. degree in physics from the University of Barcelona, Barcelona, Spain, in 1990. He is currently the Director of the Group of Excellence for Radio Frequency Components and Systems, University of Barcelona, where he is also a Full Professor with the Electronic Department. His current research interests include design optimization and test of RF systems and circuits performed using silicon and multilayered technologies, such as multichip modules and low

temperature co-fired ceramics, modeling, and optimization of integrated inductors and transformers for RF-integrated circuit applications, particularly in the development of new homodyne transceiver architectures based on injection-locked oscillators, the use of 3-D simulators for electromagnetic (EM) analysis of RF devices, components, and systems, as well as the analysis of EM compatibility/EM interference problems, particularly the interaction of EM energy with biological tissues.

Francisco V. Fernández got the Physics-Electronics degree from the University of Seville, Spain, in 1988 and his Ph. D. degree in 1992. In 1993, he worked as a postdoctoral research fellow at Katholieke Universiteit Leuven (Belgium). From 1995 to 2009, he was an Associate Professor at the Dept. of Electronics and Electromagnetism of University of Seville, where he was promoted to full professor in 2009. He is also a researcher at IMSE-CNM (University of Seville and CSIC). Dr. Fernández was the Editor-in-Chief of Integration, the VLSI Journal (Elsevier) from 2005 to

2015. His research interests lie in the design and design methodologies of analog, mixed-signal and radiofrequency circuits. Dr. Fernández has authored or edited five books and has co-authored more than 200 papers in international journals and conferences. He has served as General Chair of three international conferences and regularly serves at the Program Committee of several international conferences. He has also participated as researcher or main researcher in numerous national and international R&D projects.