Received 29 November 2019; revised 21 January 2020; accepted 3 February 2020. Date of publication 7 February 2020; date of current version 21 February 2020.

The review of this paper was arranged by Editor M. Liu.

Digital Object Identifier 10.1109/JEDS.2020.2972319

# A New 8T Hybrid Nonvolatile SRAM With Ferroelectric FET

WEI-XIANG YOU<sup>®</sup> 1, PIN SU<sup>®</sup> 1 (Member, IEEE), AND CHENMING HU<sup>®</sup> 2,3 (Life Fellow, IEEE)

1 Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan 2 Department of Electrical Engineering and Computer Science, University of California at Berkeley, Berkeley, CA 94720, USA 3 International College of Semiconductor Technology, National Chiao Tung University, Hsinchu 30010, Taiwan

CORRESPONDING AUTHOR: P. SU (e-mail: pinsu@faculty.nctu.edu.tw)

This work was supported in part by the "Center for Semiconductor Technology Research" from the Featured Areas Research Center Program within the Framework of the Higher Education Sprout Project by the Ministry of Education in Taiwan, and in part by the Ministry of Science and Technology,

Taiwan, under Contract MOST-108-3017-F-009-003 and Contract MOST-107-2221-E-009-090-MY2.

**ABSTRACT** This paper proposes a new 8T nonvolatile SRAM (nvSRAM) cell employing ULP FinFETs and ferroelectric FinFETs to enable energy-efficient and low-latency store/recall operations. Different from other types of nvSRAM requiring additional circuitry or nonvolatile memories connected to a standard 6T SRAM cell to achieve nonvolatility, the proposed hybrid nvSRAM cell reduces the area penalty by embedding the nonvolatile ferroelectric FinFETs in a 6T SRAM cell without sacrificing the cell stability, read/write performance and power consumption.

**INDEX TERMS** Ferroelectric field-effect transistor FET, negative-capacitance FET (NCFET), FinFET, nonvolatile SRAM (nvSRAM), nonvolatile memory.

### I. INTRODUCTION

In order to realize the ultra-low power computing near memory system, a compact and fast embedded nonvolatile memory is expected to be important [1], [2]. Several nonvolatile SRAM (nvSRAM) solutions with additional circuitry or nonvolatile memories (e.g., RRAM, MTJ, etc.) connected to a 6T SRAM cell have been proposed [3]–[10]. Nevertheless, the added cost of integrating the nonvolatile memory with advanced logic technology and the large offon energy ( $E_{S\&R}$ ) due to store and recall operations are unsatisfactory [5].

To overcome these limitations, a 6T2C nvSRAM cell with two ferroelectric capacitors connected to a conventional 6T SRAM cell has been proposed recently [10]. However, the additional two ferroelectric capacitors enabling the non-volatility lead to a large area penalty compared with using transistors.

Thanks to the recent discovery of ferroelectricity in doped hafnium-oxide [11], the ferroelectric FET with CMOS compatibility and scalability has garnered substantial interest.

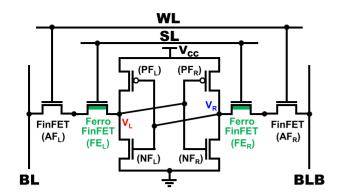

In this work, we propose a new 8T hybrid nvSRAM cell (as shown in Fig. 1) employing FinFETs and ferroelectric FinFETs to achieve energy-efficient data storage with

reduced area overheads. The read/write static noise margins and performance of 8T hybrid nvSRAM are also addressed.

This paper is organized as follows. In Section II, we describe the device design and simulation methodology. In Section III, the voltage conditions and operating principles for the 8T hybrid nvSRAM during the store/recall period are illustrated. The read/write operation, cell stability, performance and power consumption are examined in Section IV. Finally, the conclusion is drawn in Section V.

#### II. DEVICE DESIGN AND SIMULATION METHODOLOGY

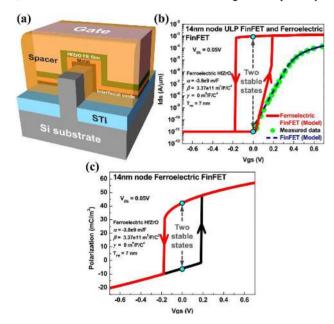

Different from the hysteresis-free negative-capacitance FETs (NCFETs) that are promising for performing low-power Boolean logic operations in processing units, the ferroelectric FinFETs (see Fig. 2(a)) in the hybrid nvSRAM cell is designed to have two nonvolatile stable states in the hysteresis loop around  $V_{gs} = 0$ V in Figs. 2(b) and 2(c). One state can switch to the other by applying a sufficiently positive or negative  $V_{gs}$  pulse that exceeds the coercive voltage ( $\sim$ 0.2V in this work) [13]. Even though the device is powered-off, the two polarization states in ferroelectric FET can still be maintained [14], [15]. This hysteresis characteristic can be achieved by capacitance engineering where the

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see http://creativecommons.org/licenses/by/4.0/

VOLUME 8, 2020 171

FIGURE 1. Schematic of proposed 8T hybrid nonvolatile SRAM cell. WL, BL/BLB, and SL are the word line, bit line, and storage line, respectively.

FIGURE 2. (a) Schematic of a ferroelectric FinFET structure. (b)  $I_{ds}$ - $V_{gs}$  characteristics of the ferroelectric FinFET and the 14nm-node Ultra-Low-Power (ULP) FinFET [12]. Note that the hysteretic  $I_{ds}$ - $V_{gs}$  and (c) polarization P- $V_{gs}$  characteristics with two stable nonvolatile states in ferroelectric FinFET straddle  $V_{gs}=0$ V by design.

value of ferroelectric capacitance  $|C_{FE}|$  is made smaller than that of internal FinFET (metal) gate capacitance  $C_{mos}$  [16].

In this work, the ferroelectric FinFET is modeled by coupling the surface-potential-based BSIM-CMG model [17] with the time-dependent Landau-Khalatnikov equation [18] which has been adopted by [14], [19], [20]. (The floating metal gate between the interfacial oxide and the FE film in Fig. 2(a) is needed to implement this modeling approach. It may not be a necessary part of the ferroelectric FinFET design.) The short-channel gate charge model of the underlying FinFET,  $Q_{mos}$ , (i.e., the polarization charge seen by the ferroelectric) is derived based on an analytical short-channel surface potential equation of FinFETs [21], [22]. The model is self-consistently solved in the SPICE circuit simulator. We first calibrate the model of the underlying baseline FinFET with the reported data of a 14nm-node Ultra-Low-Power (ULP) FinFET

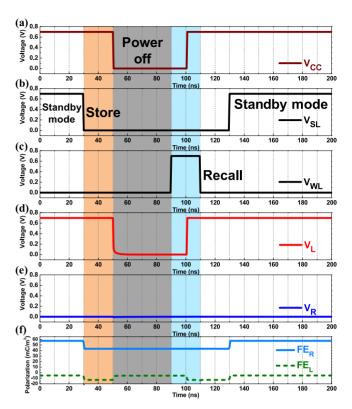

FIGURE 3. The transient waveforms of the proposed 8T hybrid nvSRAM during data storage and recall operations.

technology [12] shown in Fig. 2(b). The parasitic capacitance is estimated ( $\sim$ 0.14fF/ $\mu$ m) with 3D TCAD simulation [23] for the calibrated FinFET. The ferroelectric parameters of HfZrO used in this work are:  $\alpha = -3.8 \times 10^9$  m/F,  $\beta = 3.37 \times 10^{11}$  m<sup>5</sup>/F/C<sup>2</sup> and  $\gamma = 0$  m<sup>9</sup>/F/C<sup>4</sup>. These values were obtained based on the remnant polarization ( $P_r$ ) and coercive field ( $E_c$ ) data of HfZrO in [24]. The value of damping constant  $\rho = 0.25$   $\Omega$ m has been adopted as in [14]. In our circuit evaluation, the front-end-of-line (FEOL) and back-end-of-line (BEOL) capacitive load is estimated based on the 14nm technology node [25].

## III. OPERATION PRINCIPLE OF PROPOSED 8T HYBRID NVSRAM

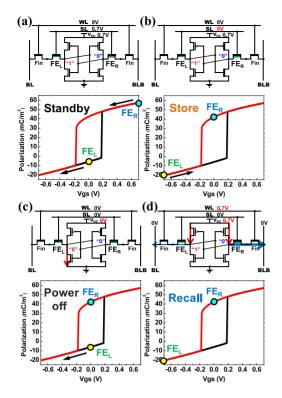

Before the power failure, the data in cell storage nodes  $V_L$  and  $V_R$  should be stored in the ferroelectric FinFETs (FE<sub>L</sub> and FE<sub>R</sub> in Fig. 1). To demonstrate the nonvolatile characteristic in the proposed hybrid nvSRAM, the transient waveforms and their corresponding operation points in P- $V_{gs}$  at each operation stage are shown in Fig. 3 and Fig. 4, respectively. The state of the nvSRAM is assumed to be "1" at  $V_L$  and "0" at  $V_R$ .

Normally, the SL is set to  $V_{DD}$  as shown at t=0 in Fig. 3(b). The polarization in FE<sub>L</sub> is at the low polarization state (i.e., at the subthreshold regime in Fig. 2(b)) while the polarization in FE<sub>R</sub> is at the high polarization state (i.e., at the strong inversion regime in Fig. 2(b)) as shown in Fig. 4(a). The polarization states in FE<sub>L</sub> and FE<sub>R</sub> are determined by the state stored in  $V_L$  and  $V_R$ , respectively. The  $V_{gs}$  of FE<sub>L</sub>

172 VOLUME 8, 2020

FIGURE 4. Schematics of hybrid nvSRAM voltage bias conditions and the corresponding operation points in  $P-V_{gs}$  at each operation stage. The directions of arrows represent the movements of polarization states from the current stage to the next stage.

is zero due to the logical "1" at  $V_L$ , while the  $V_{gs}$  of  $FE_R$  is  $V_{DD}$  due to the logical "0" at  $V_R$ . Before power-off, to ensure the polarization in  $FE_L$  keeping at a low polarization state (i.e., prevent from the logical "1" at  $V_L$  discharging to logical "0" before the SL power-off), the SL is pulled down to GND. Note that, at this step, the polarization state in  $FE_R$  remains stable as shown in Fig. 3(f). After the data storage operation, the power supply ( $V_{CC}$ ) can be turned-off. Even after  $V_L$  is discharged to GND, the polarization states in  $FE_L$  and  $FE_R$  are still maintained (see Fig. 3(f)).

In Fig. 3(c), during the recall period, WL is pulled up to  $V_{DD}$  before the nvSRAM wakes up and provides a low resistance path from  $V_R$  to ground, and contrarily, a high resistance path from  $V_L$  to ground. After that,  $V_{CC}$  is pulled up to  $V_{DD}$  and charges both cell storage nodes  $V_L$  and  $V_R$  by the P-type FinFETs (see Fig. 4(d)). Because of different strength to pull down  $V_L$  and  $V_R$  by the bit line capacitances (see Fig. 4(d)), the node voltages are restored to the previous states before power-off. After  $V_L$  and  $V_R$  settle down, the SL is pulled up to  $V_{DD}$ , and the nvSRAM is ready to resume operation as a regular SRAM. Note that, the polarization states in FE<sub>L</sub> and FE<sub>R</sub> are not changed during the recall operation.

# IV. READ/WRITE SNMS AND PERFORMANCE EVALUATION

Although there are several other nvSRAM architectures [3]–[10], they introduce nonvolatile memories

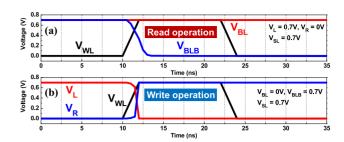

FIGURE 5. Transient waveforms of proposed 8T hybrid nvSRAM cell during (a) read and (b) write operations.

outside the 6T SRAM cell without changing the read/write operations, cell stability and performance of basic 6T SRAM cell. However, with ferroelectric FinFETs directly embedded in the proposed hybrid nvSRAM cell, its read/write operations, cell stability and performance should be further investigated.

Fig. 5 shows the transient waveforms of read and write operations. During the read operation (see Fig. 5(a)), the BL and BLB are precharged to  $V_{DD}$ . The SL is raised to  $V_{DD}$  to provide low resistance paths from cell storage nodes to the access pass-gate transistors (AF<sub>L</sub> and AF<sub>R</sub> in Fig. 1), so the read operation is still initiated by enabling the WL. Other voltage conditions are also similar to a conventional 6T SRAM during the read period. The BL and BLB capacitance of 16.8 fF is estimated for 64 cells per bit line [26] and adopted in all our simulations. Fig. 5(b) demonstrates the capability of bit writing in the hybrid nvSRAM cell. During the write operation, the SL is raised to  $V_{DD}$ . Once the WL is enabled, the bit lines can successfully flip the state of the cell. Then, the write process is completed.

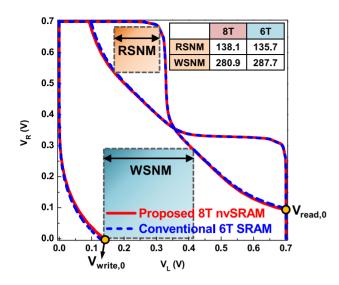

Fig. 6 shows the comparison of read and write static noise margins (RSNM and WSNM) between the proposed 8T hybrid nvSRAM and conventional 6T SRAM. It can be seen that, in addition to the RSNM and WSNM, the read/write disturb voltages ( $V_{read,0}$  and  $V_{write,0}$ ) of the proposed 8T hybrid nvSRAM cell are comparable with that of the conventional 6T SRAM cell. Although there exists an embedded ferroelectric FinFET connecting the cell storage node and access pass-gate transistor in the hybrid nvSRAM cell, the voltage divider effect is negligible due to the relatively high ON-state current of ferroelectric FinFET (compared with the FinFET) shown in Fig. 2(b). Therefore, the read and write stabilities are still determined by the strength ratios of the pull-down transistor to the access pass-gate transistor and access passgate transistor to the pull-down transistor using FinFETs, respectively, which is similar to the design of a conventional 6T SRAM. This characteristic substantially reduces the complexity of the hybrid nvSRAM design.

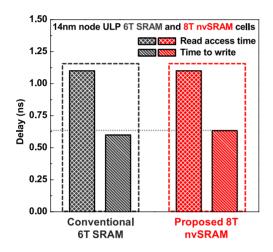

Fig. 7 shows the comparison of cell performance between the proposed 8T hybrid nvSRAM and conventional 6T SRAM cells. Because the ferroelectric FinFET with a relatively higher ON-state current lessens the voltage divider effect between the cell storage node and the access pass-gate transistor, the read current is only determined by the access pass-gate transistor and pull-down

VOLUME 8, 2020 173

FIGURE 6. The RSNM and WSNM of proposed 8T hybrid nvSRAM cell are comparable to that of conventional 6T SRAM cell.

FIGURE 7. Comparable read/write performance of proposed 8T hybrid nvSRAM and conventional 6T SRAM cells. A slight increase in time-to-write of proposed 8T hybrid nvSRAM cell results from the enhanced gate capacitance in ferroelectric FinFET.

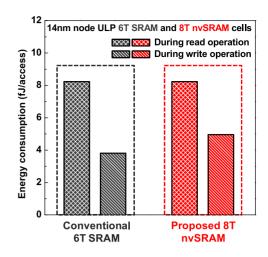

transistor using FinFETs. Thus, the read access time of the 8T hybrid nvSRAM is nearly identical to that of the conventional 6T SRAM. Based on the same reason, the timeto-write of 8T hybrid nvSRAM is comparable with the conventional 6T SRAM. A slight increase in time-to-write of a 8T hybrid nvSRAM cell results from the enhanced gate capacitance in the ferroelectric FinFET, especially for the ferroelectric FinFET with a thicker ferroelectric thickness  $(T_{FE})$  [27], [28]. Nevertheless, the impact of enhanced gate capacitance of a ferroelectric FinFET on the read access time can be negligible due to the existence of the bit line capacitance which dominates the overall capacitance for the nvSRAM during the read operation. This can also explain the comparable energy consumption during the read and write operations between the proposed 8T hybrid nvSRAM and conventional 6T SRAM cells shown in Fig. 8.

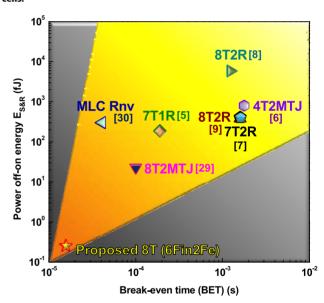

The power off-on energy  $(E_{S\&R})$  and break-even-time (BET) are critical energy-performance

FIGURE 8. Comparable energy consumption during the read and write operations of proposed 8T hybrid nvSRAM and conventional 6T SRAM cells.

FIGURE 9. Comparison of power off-on energy ( $E_{S\&R}$ ) and break-even time (BET) for various nvSRAMs. The  $E_{S\&R}$  of the proposed 8T nvSRAM with ferroelectric FETs is simulated and extracted with  $1\mu s$  power supply ramp-up time.

indices of nonvolatile logic circuits for power gating applications [3]. Fig. 9 shows the  $E_{S\&R}$  and BET data for RRAM and MTJ based nvSRAMs [5]–[9], [29], [30]. In general, the nvSRAM based on MTJ devices (particularly the advanced SHE/SOT driven MTJs [31], [32]) can achieve superior energy efficiency than the RRAM based counterparts. It can be revealed from Fig. 9 that, compared with the simulated MTJ (8T2MTJ [29]) based nvSRAM, the proposed 8T nvSRAM with ferroelectric FETs can achieve better energy-efficiency and energy savings during the power gating which is favorable for the frequent data access. Note that the ferroelectric FinFET thoroughly gets shot of the large static current in RRAM and MTJ based nvSRAMs during store and recall operations.

174 VOLUME 8, 2020

#### **V. CONCLUSION**

To realize the ultra-low power computing system, we propose a new 8T hybrid nvSRAM cell employing FinFETs and ferroelectric FinFETs. The proposed hybrid nvSRAM cell demonstrates the nonvolatility with superior energy-efficiency during store and recall operations. Therefore, compared with the existing 6T2C nvSRAM with additional ferroelectric capacitors to achieve nonvolatility, the proposed 8T hybrid nvSRAM reduces the area penalty without sacrificing the cell stability, read/write performance and energy consumption.

### **ACKNOWLEDGMENT**

The authors would like to thank anonymous referees for critical reading of the manuscript and valuable feedback.

### **REFERENCES**

- [1] W.-H. Chen et al., "A 65nm 1Mb nonvolatile computing-in-memory ReRAM macro with sub-16ns multiply-and accumulate for binary DNN AI edge processors," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), Feb. 2018, pp. 494–496, doi: 10.1109/ISSCC.2018.8310400.

- [2] X. Sun, P. Wang, K. Ni, S. Datta, and S. Yu, "Exploiting hybrid precision for training and inference: A 2T-1FeFET based analog synaptic weight cell," in *IEEE Int. Electron Devices Meeting Tech. Dig. (IEDM)*, Dec. 2018, pp. 3.1.1–3.1.4, doi: 10.1109/IEDM.2018.8614611.

- [3] Y. Shuto, S. Yamamoto, and S. Sugahara, "Nonvolatile static random access memory based on spin-transistor architecture," *J. Appl. Phys.*, vol. 105, no. 7, pp. 1–3, Apr. 2009, doi: 10.1063/1.3076895.

- [4] W. Wang et al., "Nonvolatile SRAM cell," in Int. Electron Devices Meeting Tech. Dig. (IEDM), Dec. 2006, pp. 1–4, doi: 10.1109/IEDM.2006.346730.

- [5] A. Lee et al., "RRAM-based 7T1R nonvolatile SRAM with 2x reduction in store energy and 94x reduction in restore energy for frequent-off instant-on applications," in Proc. Symp. VLSI Circuits (VLSI Circuits), Jun. 2015, pp. C76–C77, doi: 10.1109/VLSIC.2015.7231368.

- [6] T. Ohsawa et al., "A 1 Mb nonvolatile embedded memory using 4T2MTJ cell with 32 b fine-grained power gating scheme," *IEEE J. Solid-State Circuits*, vol. 48, no. 6, pp. 1511–1520, Jun. 2013, doi: 10.1109/JSSC.2013.2253412.

- [7] S.-S. Sheu et al., "A ReRAM integrated 7T2R non-volatile SRAM for normally-off computing application," in Proc. IEEE Solid-State Circuits Conf., Nov. 2013, pp. 245–248, doi: 10.1109/ASSCC.2013.6691028.

- [8] S. Yamamoto, Y. Shuto, and S. Sugahara, "Nonvolatile SRAM (NV-SRAM) using functional MOSFET merged with resistive switching devices," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2009, pp. 531–534, doi: 10.1109/CICC.2009.5280761.

- [9] P.-F. Chiu et al., "A low store energy, low VDDmin, nonvolatile 8T2R SRAM with 3D stacked RRAM devices for low power mobile applications," in Proc. Symp. VLSI Circuits, Jun. 2010, pp. C229–C230, doi: 10.1109/VLSIC.2010.5560286.

- [10] M. Kobayashi, N. Ueyama, and T. Hiramoto, "A nonvolatile SRAM integrated with ferroelectric HfO<sub>2</sub> capacitor for normally-off and ultralow power IoT application," in *Proc. Symp. VLSI Technol.*, Jun. 2017, pp. T156–T157, doi: 10.23919/VLSIT.2017.7998161.

- [11] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, "Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors," in *Int. Electron Devices Meeting Tech. Dig. (IEDM)*, Dec. 2011, pp. 24.5.1–24.5.4, doi: 10.1109/IEDM.2011.6131606.

- [12] C.-H. Jan et al., "A 14 nm SoC platform technology featuring 2<sup>nd</sup> generation tri-gate transistors, 70 nm gate pitch, 52 nm metal pitch, and 0.0499 um<sup>2</sup> SRAM cells, optimized for low power, high performance and high density SoC products," in Symp. VLSI Circuits Tech. Dig. (VLSI Circuits), Jun. 2015, pp. T12–T13, doi: 10.1109/VLSIC.2015.7231380.

- [13] A. I. Khan et al., "Negative capacitance in short-channel FinFETs externally connected to an epitaxial ferroelectric capacitor," *IEEE Electron Device Lett.*, vol. 37, no. 1, pp. 111–114, Jan. 2016, doi: 10.1109/LED.2015.2501319.

- [14] X. Li et al., "Enabling energy-efficient nonvolatile computing with negative capacitance FET," IEEE Trans. Electron Devices, vol. 64, no. 8, pp. 3452–3458, Aug. 2017, doi: 10.1109/TED.2017.2716338.

- [15] Z. Wang, S. Khandelwal, and A. I. Khan, "Ferroelectric oscillators and their coupled networks," *IEEE Electron Device Lett.*, vol. 38, no. 11, pp. 1614–1617, Nov. 2017, doi: 10.1109/LED.2017.2754138.

- [16] W.-X. You and P. Su, "Design space exploration considering back-gate biasing effects for 2D negative-capacitance field-effect transistors," *IEEE Trans. Electron Devices*, vol. 64, no. 8, pp. 3476–3481, Aug. 2017, doi: 10.1109/TED.2017.2714687.

- [17] (2016). BSIM-CMG Technical Manual. [Online]. Available: http://bsim.berkeley.edu/models/bsimcmg/

- [18] L. D. Landau and I. M. Khalatnikov, "On the anomalous absorption of sound near a second order phase transition point," *Doklady Akademii Nauk SSSR*, vol. 96, pp. 469–472, Jun. 1954.

- [19] X. Li et al., "Lowering area overheads for FeFET-based energy-efficient nonvolatile flip-flops," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 2670–2674, Jun. 2018, doi: 10.1109/TED.2018.2829348.

- [20] S. George et al., "Nonvolatile memory design based on ferroelectric FETs," in Proc. 53rd ACM/EDAC/IEEE Design Autom. Conf. (DAC), Jun. 2016, p. 118, doi: 10.1145/2897937.2898050.

- [21] W.-X. You, P. Su, and C. Hu, "Evaluation of NC-FinFET based subsystem-level logic circuits," *IEEE Trans. Electron Devices*, vol. 66, no. 4, pp. 2004–2009, Apr. 2019, doi: 10.1109/TED.2019.2898445.

- [22] W.-X. You, C.-P. Tsai, and P. Su, "Short-channel effects in 2D negative-capacitance field-effect transistors," *IEEE Trans. Electron Devices*, vol. 65, no. 4, pp. 1604–1610, Apr. 2018, doi: 10.1109/TED.2018.2805716.

- [23] Sentaurus TCAD, G2012–06-SP2 Manual, Mountain View, CA, USA, Synopsys, 2012.

- [24] M. Kobayashi and T. Hiramoto, "Device design guideline for steep slope ferroelectric FET using negative capacitance in sub-0.2 V operation: Operation speed, material requirement and energy efficiency," in *Symp. VLSI Technol. Tech. Dig. (VLSI Technol.)*, Jun. 2015, pp. T212–T213, doi: 10.1109/VLSIT.2015.7223678.

- [25] A. N. Bhoj, R. V. Joshi, and N. K. Jha, "3-D-TCAD-based parasitic capacitance extraction for emerging multigate devices and circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 21, no. 11, pp. 2094–2104, Nov. 2013, doi: 10.1109/TVLSI.2012.2227848.

- [26] K.-Y. Tseng, W.-X. You, and P. Su, "Evaluation of 2D negative-capacitance FETs for low-voltage SRAM applications," in *Proc. Proc. Int. Symp. VLSI Technol. Syst. Appl. (VLSI-TSA)*, Apr. 2019, pp. 1–2.

- [27] W.-X. You and P. Su, "Intrinsic difference between 2-D negative-capacitance FETs with semiconductor-on-insulator and double-gate structures," *IEEE Trans. Electron Devices*, vol. 65, no. 10, pp. 4196–4201, Oct. 2018, doi: 10.1109/TED.2018.2866125.

- [28] T. Dutta, G. Pahwa, A. R. Trivedi, S. Sinha, A. Agarwal, and Y. S. Chauhan, "Performance evaluation of 7-nm node negative capacitance FinFET-based SRAM," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1161–1164, Aug. 2017, doi: 10.1109/LED.2017.2712365.

- [29] D. Kitagata, S. Yamamoto, and S. Sugahara, "Design and energy-efficient architectures for nonvolatile static random access memory using magnetic tunnel junctions," *Jpn. J. Appl. Phys.*, vol. 58, Mar. 2019, Art. no. SBBB12, doi: 10.7567/1347-4065/ab00f5.

- [30] Y. Sun et al., "Energy-efficient nonvolatile SRAM design based on resistive switching multi-level cells," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 5, pp. 753–757, May 2019, doi: 10.1109/TCSII.2019.2908243.

- [31] W. Kang, W. Lv, Y. Zhang, and W. Zhao, "Low store power high-speed high-density nonvolatile SRAM design with spin hall effect-driven magnetic tunnel junctions," *IEEE Trans. Nanotechnol.*, vol. 16, no. 1, pp. 148–154, Jan. 2017, doi: 10.1109/TNANO.2016.2640338.

- [32] K. Jabeur, G. D. Pendina, F. Bernard-Granger, and G. Prenat, "Spin orbit torque non-volatile flip-flop for high speed and low energy applications," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 408–410, Mar. 2014, doi: 10.1109/LED.2013.2297397.

VOLUME 8, 2020 175