# A New DC-DC Converter for Photovoltaic Systems: Coupled-Inductors Combined Cuk-SEPIC Converter

Kumaran Nathan, Saikat Ghosh, Student Member, IEEE, Yam Siwakoti, Member, IEEE, and Teng Long, Member, IEEE

Abstract—An enhanced DC-DC converter is proposed in this paper, based on the combination of the Cuk and SEPIC converters, which is well-suited for solar photovoltaic (PV) applications. The converter uses only one switch (which is ground-referenced, so simple gate drive circuitry may be used), yet provides dual outputs in the form of a bipolar DC bus. The bipolar output from the DC-DC converter is able to send power to the grid via any inverter with a unipolar or bipolar DC input, and leakage currents can be eliminated if the latter type is used without using lossy DC capacitors in the load current loop. The proposed converter uses integrated magnetics cores to couple the input and output inductors, which significantly reduces the input current ripple and hence greatly improves the power extracted from the solar PV system. The design methodology along with simulation, experimental waveforms, and efficiency measurements of a 4 kW DC-DC converter are presented to prove the concept of the proposed converter. Further, a 1 kW inverter is also developed to demonstrate the converter's grid-connection potential.

Index Terms—DC-DC power conversion, grounding, DC-AC power conversion, MPPT, bipolar DC output, solar power generation.

## I. INTRODUCTION

## A. DC-DC Converters for Photovoltaic Applications

OLAR photovoltaic (PV) systems, including both string and distributed architectures, typically employ DC-DC converters to control the power generation in order to harness the maximum solar power at varying climatic and panel conditions [1, 2]. In addition to high efficiency and low cost, the DC-DC converter is required to provide a wide range of output/input voltage change ratios, and fast current and voltage control to facilitate maximum power point tracking (MPPT). A summarized comparison of the most popular non-isolated DC-DC converters is provided in Table I, in addition to the converter proposed in this paper. Boost converters are commonly used for the DC-DC conversion in PV applications, but only step-up voltage ratios are possible. The standard buck-boost converter is capable of both step-up and step-down voltage conversion, however its discontinuous input current limits its ability to perform optimal MPPT without large decoupling capacitors. Cuk and SEPIC converters have continuous input currents, and are also capable of both voltage step-up and step-down, however their large input current ripples still limit

Manuscript submitted April 9, 2018.

MPPT performance as the PV system will vary widely around its maximum power point (MPP) [3-6]. The unipolar DC output of these converters also limits their inverter pairing options, typically leading to leakage currents as explained in Section I-B. The component ratings for the converters are largely similar, so the primary factor influencing the cost of these converters is their component count, shown in Table I. The primary losses in DC-DC converters are switching losses, copper losses (inductor windings), diode conduction losses, MOSFET conduction losses, and inductor core losses (eddy current and hysteresis). The converters in Table I all have an equal switch count so the switching losses will be similar. The inductor losses are lower for the proposed converter because the reduced input current ripple decreases the peak inductor current, however the converter has more inductors. For this PV application, it is also important to distinguish between the DC-DC converter's efficiency and the overall system efficiency. The low input current ripple in the proposed converter will keep the PV system closer to its MPP, further improving the overall power extracted.

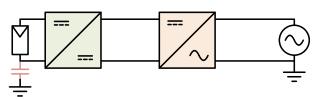

### B. Photovoltaic System Configurations

Domestic PV systems are usually connected to single-phase, earthed AC grids. Thus, in addition to voltage change ratios and input current waveforms, another important factor to consider is the impact of leakage currents [7–9]. These stem from the high frequency common mode voltages introduced at the DC side of many inverter topologies (e.g. H-bridge), which cause leakage currents to flow through the significant panel-toground parasitic capacitances inherent in PV systems [10, 11], as shown in Fig. 1a. A simple method of mitigating this issue is to introduce a line frequency transformer between the inverter and grid which allows the PV system to be grounded, as shown in Fig. 1b. The major drawback of this method is that these transformers are bulky, heavy, and costly [12, 13]. If this line frequency transformer is replaced by a high frequency transformer within an isolated DC-DC converter, as shown in Fig. 1c, then the common mode voltages can be eliminated with a higher power density and lower cost. The downside of using an isolated DC-DC converter is that they have an increased number of switches and diodes [14], and they still rely on transformers which negatively impact the overall efficiency of the PV system. The leakge current decoupling method has been investigated in recent years to reduce the leakage currents in converters such as the HERIC, H5, and H6, however additional switching devices must be employed

K. Nathan, S. Ghosh, and T. Long are with the Department of Engineering, University of Cambridge, Cambridge, United Kingdom. E-mail: ksn26@cam.ac.uk, ssg39@cam.ac.uk, tl322@cam.ac.uk.

Y. Siwakoti is with the Faculty of Engineering and IT, University of Technology Sydney, Australia. E-mail: Yam.Siwakoti@uts.edu.au.

| Converter  | Voltage output | Input current | Voltage output/input ratio | # switches | # diodes | # inductors | # capacitors |

|------------|----------------|---------------|----------------------------|------------|----------|-------------|--------------|

| Buck       | Unipolar       | Discontinuous | D                          | 1          | 1        | 1           | 1            |

| Boost      | Unipolar       | Continuous    | 1/(1-D)                    | 1          | 1        | 1           | 1            |

| Buck-boost | Unipolar       | Discontinuous | D/(1-D)                    | 1          | 1        | 1           | 1            |

| Cuk        | Unipolar       | Continuous    | -D/(1-D)                   | 1          | 1        | 2           | 2            |

| SEPIC      | Unipolar       | Continuous    | D/(1-D)                    | 1          | 1        | 2           | 2            |

| CI-CCS     | Bipolar        | Continuous    | 2D/(1-D)                   | 1          | 2        | 3           | 4            |

TABLE I DC-DC CONVERTERS COMMONLY USED IN SOLAR APPLICATIONS.

(a) Unipolar DC output without transformer causing leakage currents.

(b) Unipolar DC with line frequency transformer.

(c) Isolated DC-DC converter with unipolar output.

(d) Unipolar DC output with grounded bipolar input inverter.

(e) Bipolar DC output with grounded bipolar input inverter.

Fig. 1. Grounding options for single-phase PV systems.

[15, 16], which increases the losses, cost and complexity of the system.

An alternative to transformers and these DC decoupling methods is to eliminate these common mode voltages by using an inverter with a grounded bipolar DC input (e.g. half-bridge inverter, T-type inverter, diode/neutral-point-clamped inverter, flying capacitor/capacitor-clamped inverter), which is driven by a bipolar, ground-referenced DC bus [17]. These inverters operate without introducing switching frequency common mode voltages on the DC bus. It is theoretically possible to use a standard unipolar output DC-DC converter to create the required bipolar DC bus by providing a ground connection at the midpoint of the DC link capacitors, as shown in Fig. 1d,

however the entire grid current will flow through the DC link capacitors creating substantial losses, and the PV input will be referenced to the negative DC bus voltage, leaving the 100 Hz common mode voltage on the PV array.

The solution explored in this paper uses a DC-DC converter that produces a bipolar output from a unipolar input, as shown in Fig. 1e. This method fundamentally addresses the leakage current issue without the use of transformers or high current-carrying capacitors, whilst also providing grounding for both the PV system and DC-DC converter (which eases their isolation and gate driver requirements), and serendipitously solving the 'potential induced degradation' problem associated with PV cells [18].

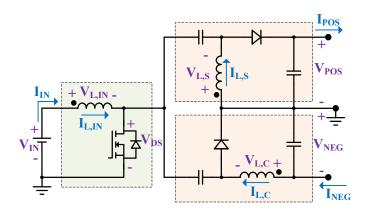

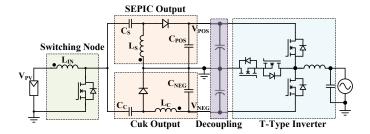

## C. The Combined Cuk-SEPIC (CCS) Converter

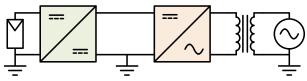

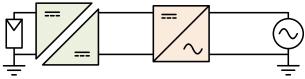

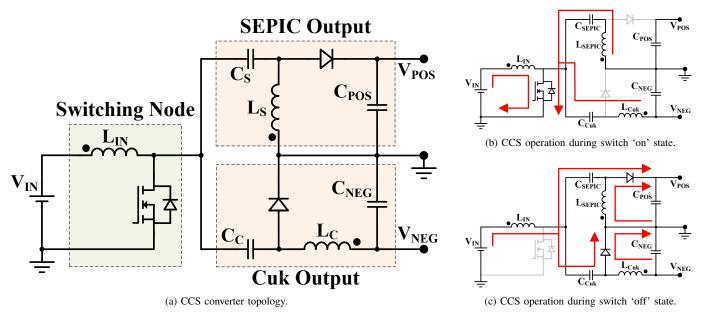

The Combined Cuk-SEPIC (CCS) converter, shown in Fig. 2a, is an emerging DC-DC converter topology that is well-suited for this application and has hence been investigated recently [19–23]. It uses a single switching node, which is common to both Cuk and SEPIC energy transfer stages, to provide matching ground-referenced positive and negative outputs. During the switch 'on' state (Fig. 2b), all inductors are charging and the capacitors are discharging. When the switch turns off (Fig. 2c), the inductor currents redirect into the two diodes and the capacitors charge while the inductors discharge. In continuous conduction mode (CCM) operation considered in this paper, the switch turns on again prior to the complete discharge of any inductor.

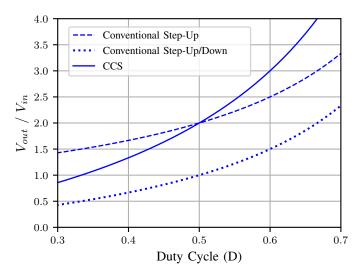

The CCS converter can provide large step-up, as well as step-down voltage conversion ratios. The converter has an output/input ratio of D/(1-D) for each of the positive and negative DC output terminals, providing step-up conversion for duty ratios greater than 1/2, and operating in step-down mode for duty ratios below 1/2. The converter's overall gain (i.e. considering the output voltage as the positive-to-negative voltage) is 2D/(1-D). This distinct output/input voltage ratio allows regulation of larger input voltage variations with the same duty cycle range, or alternatively allows the converter to handle the same input voltage variation with a narrower duty cycle range, allowing for smaller inductors to be used. Fig. 3 shows the gain provided by different converter types for a range of duty cycles.

# D. Inductor Magnetic Coupling

The benefits of inductor coupling in Cuk converters and SEPIC converters has been described in the literature [23, 24]. Despite recent interest in the CCS converter however, research

Fig. 2. Combined Cuk-SEPIC (CCS) converter.

Fig. 3. Voltage gain ratios for various converter types.

is yet to be conducted into the effects of coupling its input and output inductors and the benefits this has for PV systems. This paper examines the impact of coupling between  $L_{IN},\,L_S$ , and  $L_C$ , as shown in Fig. 2a. This converter is henceforth referred to as the Coupled Inductors Combined Cuk-SEPIC (CI-CCS) converter. A multi-variable optimization has been conducted to determine the optimum coupling levels in Section II, which also includes simulation and experimental results. The results demonstrate that this coupling can significantly reduce the input current ripple, which allows the overall inductance – and hence volume and weight – to be reduced. Section III presents a discussion of the benefits this reduced current ripple has on solar PV performance – specifically addressing MPPT and a high bandwidth current controller – along with an examination of the wider grid integration of this converter.

#### II. CONVERTER DESIGN AND MAGNETICS OPTIMIZATION

# A. Converter Rating Analysis

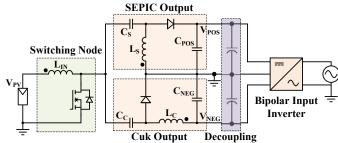

The peak power ratings of both the DC-DC converter and inverter for single-phase grid-connected PV systems are important considerations. Fig. 4 shows the CI-CCS converter feeding a bipolar input inverter, with some energy storage present on the DC bus to decouple the 100 Hz power fluctuations caused by the single-phase system. For a 1 kW average AC output power, the peak instantaneous power will be 2 kW, since the instantaneous power is given by  $P_{ac}(t) = \sqrt{2}V_{rms}\sin{(\omega t)}\sqrt{2}I_{rms}\sin{(\omega t)} = 2V_{rms}I_{rms}\sin^2{(\omega t)}$ .

Fig. 4. CI-CCS converter feeding a bipolar input inverter.

If there is no storage present on the DC bus, then the CI-CCS converter needs to be capable of supplying this 2 kW peak power on both of its positive and negative outputs (since this peak occurs in both the positive and negative cycles of the grid voltage). If there is no cyclical power de-rating of the CI-CCS converter (i.e. its continuous rating is conservatively set to the temporary peak power requirements) and if we pessimistically ensure that it can supply this peak power on both outputs simultaneously, then the converter must be rated to a total of 4 kW (i.e. 2 kW for each output). In this case, the power supplied to the DC input of the CI-CCS converter

will not be constant, but rather follow the same shape as the instantaneous AC output power. Thus, in this worst case scenario the power rating ratio of the CI-CCS to inverter will be 4:1.

In reality, enough capacitance should be included in between the CI-CCS converter and the inverter to decouple the 100 Hz ripple from the PV array, allowing it to produce a constant power output and maintain operation at its MPP. In this scenario, with the same 1 kW average AC output power, the input to the CI-CCS converter will be a continuous 1 kW. This is supplied alternatively to the positive and negative outputs in each grid half cycle. Again, without cyclical power de-rating and ensuring the converter can supply 1 kW on both outputs simultaneously, the converter should be rated to a total of 2 kW (i.e. 1 kW for each output). Thus, in this scenario the power rating ratio of the CI-CCS to inverter will be 2:1.

If the converter's rating is adjusted to account for the cyclical nature of the power supplied, then the power rating ratio of the CI-CCS to inverter will be 1:1, since the average power supplied by the CI-CCS converter is 1 kW, despite this coming alternately from each output.

Thus, the CI-CCS converter's rating must be between 1x and 4x the inverter's average output power, depending on the storage present between the converters, and the level of de-rating applied. In this paper, the converter prototype is conservatively designed for the worst case scenario (i.e. 4 kW peak power), but tested at 2 kW since sufficient capacitance is provided to ensure 100 Hz decoupling between the PV array and the grid. A more detailed investigation into the impacts of these decoupling DC link capacitors and inverter topology selection is left for other papers, focusing in the grid-integration aspect of the proposed DC-DC converter.

## B. Coupling Factor Optimization

The CCS converter was initially designed with no magnetic coupling between any of the inductors to meet the specifications given in Table II (the input voltage range corresponds to a duty cycle of  $0.5 \pm 10\%$ ). It should be noted that the input current ripple (given as a percentage of average input current) specification was deliberately set high to allow the benefits of inductor coupling to be highlighted.

The design process involved analyzing the converter in the 'on' state (though the 'off' state could also be used to produce the same results) to obtain equations that describe the voltages across, and the currents through, the various components. Using equations from either of these states in combination with the inductor and capacitor equations ( $V=L\frac{di}{dt}$  and  $I=C\frac{dv}{dt}$ ) produces expressions for inductances and capacitances as a function of other known parameters. As there are seven of these components, these equations would be of a prohibitively high order (up to seven), so small ripple approximations are applied to simplify the derivations. This process produces the

following equations:

$$L_{in_{min}} = \frac{V_{in}^2 V_{out} T_s}{\left(V_{in} + V_{out}\right) P_{out} \left(\Delta i_{L_{in_{max}}} \%\right)} \tag{1}$$

4

$$L_{S_{min}} = \frac{2V_{in}V_{out}^2 T_s}{(V_{in} + V_{out}) P_{out} \left(\Delta i_{L_{S_{max}}}\%\right)}$$

(2)

$$L_{C_{min}} = \frac{2V_{in}V_{out}^2T_s}{(V_{in} + V_{out})P_{out}\left(\Delta i_{L_{C_{max}}}\%\right)}$$

(3)

$$C_{POS_{min}} = \frac{P_{out}T_s}{2\left(V_{in} + V_{out}\right)V_{out}\left(\Delta v_{C_{POS_{max}}}\%\right)} \tag{4}$$

$$C_{NEG_{min}} = \frac{P_{out}T_s \left(\Delta i_{L_{C_{max}}}\%\right)}{16V_{out}^2 \left(\Delta v_{C_{NEG_{max}}}\%\right)}$$

(5)

$$C_{S_{min}} = \frac{P_{out}T_s}{2V_{in}\left(V_{in} + V_{out}\right)\left(\Delta v_{C_{S_{max}}}\%\right)}$$

(6)

$$C_{C_{min}} = \frac{P_{out}T_s}{2\left(V_{in} + V_{out}\right)^2 \left(\Delta v_{C_c} \%\right)} \tag{7}$$

In these equations,  $T_s$  refers to the switching period, and the  $(\Delta x\%)$  terms refer to the peak-to-peak ripples (expressed as a percentage of their average values). Two important observations can be made from these equations:

- 1) As the converter is designed to operate with a range of input voltages, the worst case value of  $V_{in}$  should be used for each component. This means the maximum input voltage for inductors, and the minimum input voltage for capacitors.

- 2) Similarly, it should also be noted that  $P_{out}$  appears in the denominator for the inductor equations but in the numerator for the capacitor equations. This means that the inductances required will be largest at the *minimum* output power, and the capacitances required will be largest at the *maximum* (rated) output power. Here, we will consider performance at rated power, rather than over a defined output power range.

With the specifications given in Table II, the passive sizing equations produce the component sizes listed in Table III (which also shows the commercially-available capacitor values selected).

TABLE II CONVERTER DESIGN SPECIFICATIONS.

| Nominal input voltage     | 360 V                          |

|---------------------------|--------------------------------|

| Input voltage range       | 294 V to 440 V                 |

| Target output voltage     | ± 360 V                        |

| Rated output power        | 4 kW                           |

| Switching frequency       | 100 kHz                        |

| Input current ripple      | 40% peak-peak (at rated power) |

| Transfer capacitor ripple | 10% peak-peak (at rated power) |

| Output voltage ripple     | 2% peak-peak (at rated power)  |

TABLE III

CONVERTER COMPONENT VALUES.

| I | $C_S$            | 1.04 μF (1.5 μF selected)  |

|---|------------------|----------------------------|

| I | $C_{C}$          | 0.47 μF (0.47 μF selected) |

| I | $C_{POS}$        | 4.25 μF (5 μF selected)    |

|   | C <sub>NEG</sub> | 0.39 μF (0.33 μF selected) |

| L <sub>IN</sub> | 545 µH |

|-----------------|--------|

| L <sub>S</sub>  | 891 μH |

| L <sub>C</sub>  | 891 μH |

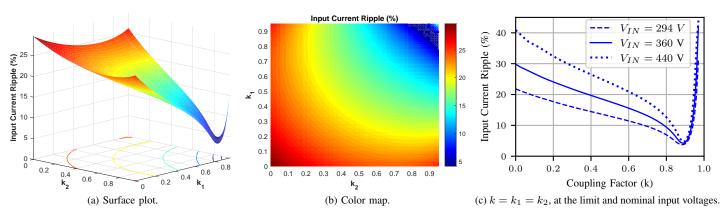

Fig. 5. Input current ripple at rated output power as a function of coupling factors,  $k_1$  and  $k_2$ .

A multi-variable optimization was conducted to identify the correlation between inductor coupling and input current ripple by modeling the ripple current at different coupling factors. The variables being tested were:

- Coupling factor between  $L_{IN}$  and  $L_{S}$   $(k_{1})$

- Coupling factor between  $L_{IN}$  and  $L_{C}$   $(k_{2})$

- Coupling factor between  $L_S$  and  $L_C$   $(k_3)$

The optimization process revealed that a positive value of  $k_3$ had a detrimental impact on performance, but a negative value of  $k_3$  improved performance. This improved performance comes at the cost of a complex inductor design, so the process is continued with uncoupled output inductors (i.e.  $k_3 = 0$ ) to maximize prototype flexibility. Next, the input inductance was split equally into two inductors ( $L_{in1}$  in series with  $L_{in2}$ ), to achieve coupling between  $L_{IN}$  and  $L_{S}$ , and  $L_{IN}$  and  $L_{C}$ , without having any coupling between  $L_S$  and  $L_C$ . Fig. 5a is a surface plot showing the impact of varying  $k_1$  and  $k_2$  on the input ripple current, and Fig. 5b presents the same data viewed from above as a color map. This graph shows almost perfect symmetry along the  $k_1 = k_2$  line, demonstrating that there are no advantages to distinct values of  $k_1$  and  $k_2$ . Thus, it was sensible to apply the constraints given in (8), (9), and (10) to simplify the optimization.

$$L_{in1} = L_{in2} = 0.5 \times L_{in} \tag{8}$$

$$k_1 = k_2 = k \tag{9}$$

$$k_3 = 0 \tag{10}$$

The results of this simplified optimization can be seen in Fig. 5c, which shows the sensitivity of the input current ripple against the coupling factor, k,  $(L_{in1} \text{ and } L_C \text{ and } L_{in2} \text{ and } L_S)$  at rated power. A variable step size was used to ensure that the curve had many data points around the turning point, while the coupling factor was swept from k=0 to k=0.99. The three lines show the input current ripple (as a percentage of average input current) at the nominal input voltage (360 V), as well as at the limits of the input voltage range (294 V and 440 V). It is observed that the minimum ripple occurs at the same coupling factor (k0.89), independent of input voltage and voltage conversion ratio. This result shows a significant decrease in input current ripple of more than 80% compared

to uncoupled inductors for all three input voltages tested, and forms the basis of the simulations and experimental work.

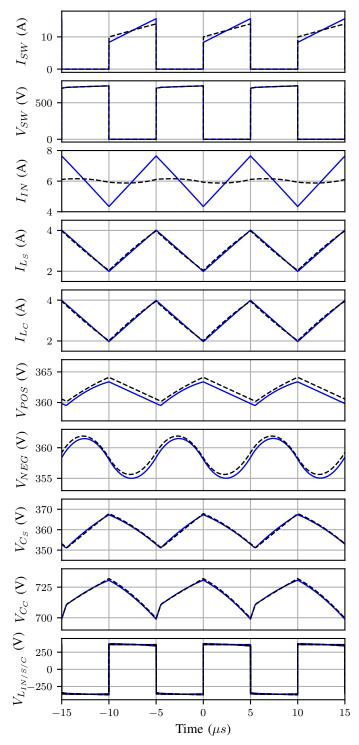

#### C. Simulation Results

The CCS converter has been simulated successfully using the Saber simulation package, in two key scenarios:

- Reference scenario: no coupling between input, Cuk, and SEPIC inductors.

- Optimal scenario for input current ripple reduction: coupling factor of 0.89 between  $L_{IN}$  and  $L_C$ , and  $L_{IN}$  and  $L_S$ , and no coupling between  $L_S$  and  $L_C$ .

For both of these scenarios, the converter was simulated at nominal input voltage (360 V) as well as the minimum and maximum rated input voltages (294 V and 440 V) by adjusting the duty cycle accordingly. The most relevant waveforms of these simulations, corresponding to the nominal input voltage condition, are shown is shown in Fig. 6. The key observation is the significant decrease in the input current ripple in the coupled inductors scenario. The switch current at turn-off is the peak input current, so the reduced input current translates to a reduced peak switch current, as shown in the simulation waveforms. The waveforms also show the SEPIC and Cuk capacitor voltages in addition to the three inductor voltages (plotted together as they overlap). These results show that there are no waveforms negatively impacted as a result of the inductor coupling. The peak-to-peak output voltage ripple is calculated to be 1.8% for the positive DC output and 2% for the negative DC output, fulfilling the design requirements. These values remain largely constant over variations in both input voltage and coupling factor.

The average input current remains the same regardless of coupling factor, however the ripple component is significantly reduced when a 0.89 coupling factor between input and output inductors is used. The input current ripple (peak-to-peak) as a percentage of average input current at rated power is shown in Table IV. These results demonstrate that a 0.89 coupling factor reduces input current ripple by 82% to 88% compared with the no coupling scenario.

#### D. Experimental Design

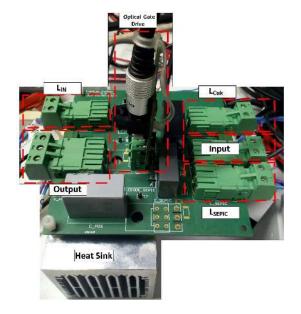

An experimental prototype was built to validate the results obtained through the simulation studies and optimizations. In

Fig. 6. Switch current, switch voltage,  $I_{IN}$ ,  $I_{L_S}$ ,  $I_{L_C}$ ,  $V_{POS}$ ,  $V_{NEG}$ ,  $V_{C_S}$ ,  $V_{C_C}$ ,  $V_{L_{IN/S/C}}$  (with  $V_{IN}=360$  V; no coupling - blue solid line, optimal coupling - black dotted line).

the literature, IGBTs have been used as the CCS converter's switching device [20]. This limits the switching frequency, and hence power density, for high frequency power converter designs. Considering these aspects in designing a compact converter, a silicon carbide (SiC) MOSFET was implemented to operate at 100 kHz for higher volumetric and gravimetric power density and efficiency. Fiber optic transmitter and

TABLE IV

INPUT CURRENT RIPPLE AT VARIOUS COUPLING FACTORS AND INPUT

VOLTAGES.

| Coupling             | Input current ripple (percentage of average) |                          |                          |  |

|----------------------|----------------------------------------------|--------------------------|--------------------------|--|

| Coupling             | $V_{in} = 294 \text{ V}$                     | $V_{in} = 360 \text{ V}$ | $V_{in} = 440 \text{ V}$ |  |

| None $(k = 0)$       | 21.8%                                        | 29.7%                    | 40.0%                    |  |

| Optimal $(k = 0.89)$ | 3.8%                                         | 4.2%                     | 4.7%                     |  |

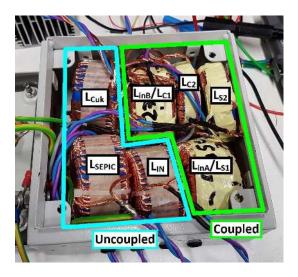

receiver boards have also been built to connect the microcontroller to the gate drive circuitry. Film capacitors were chosen over electrolytic capacitors due to their higher voltage rating, higher rms and peak current handling capabilities, as well as their better reliability. A photo of the developed prototype is shown in Fig. 7.

Fig. 7. 4 kW developed laboratory prototype.

Custom-made inductors are used to provide the coupling required to reduce the input current ripple. The choice of magnetic material for the inductor core is extremely important due to the high switching frequency and DC bias. Some important factors to consider when selecting the core material are the saturation point, permeability, and core losses.

Though ferrite cores have typically been used in DC line reactor applications [25], nanocrystalline powder cores have an advantage due to their homogeneous low permeability [26]. Nanocrystalline powder cores are formed with distributed and controllable micro air gaps to achieve low permeability (normally from 60 to 120) in order to avoid saturation of flux density caused by the large DC currents, thus one single piece of magnetic core can be used for the inductor. Due to ferrite's naturally high permeability (normally several thousand) and low saturation point, additional air gaps must be inserted between ferrite core pieces when making the inductor to avoid saturation. This can lead to complex and difficult designs and inconsistent performance. Additionally, the saturation point of nanocrystalline-based materials is more than twice that of ferrite, which further supports the use of nanocrystalline powder cores in DC line reactors [27].

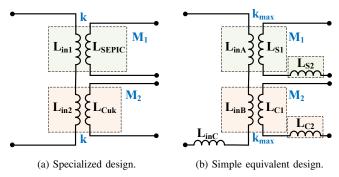

Fig. 8. Specialized vs. simple equivalent coupled inductors.

For the purpose of demonstrating the CI-CCS concept whilst maintaining the flexibility to adjust coupling factors, different coupling factors can be realized by connecting tightly coupled inductors ( $k = k_{max} \approx 1$ ) in series with separate uncoupled inductors, as shown in Fig. 8.

The self and mutual inductances of the coupled inductors in Fig. 8a are:

$$L_{IN} = L_{in1} + L_{in2} (11)$$

$$L_S = L_{SEPIC} \tag{12}$$

$$L_C = L_{Cuk} (13)$$

$$M_1 = k\sqrt{L_{in1} \times L_{SEPIC}} \tag{14}$$

$$M_2 = k\sqrt{L_{in2} \times L_{Cuk}} \tag{15}$$

Similarly, the self and mutual inductances of the tightly coupled inductors in Fig. 8b are:

$$L_{in} = L_{inA} + L_{inB} + L_{inC} \tag{16}$$

$$L_S = L_{S1} + L_{S2} (17)$$

$$L_C = L_{C1} + L_{C2} (18)$$

$$M_1 = k_{max} \sqrt{L_{inA} \times L_{S1}} \tag{19}$$

$$M_2 = k_{max} \sqrt{L_{inB} \times L_{C1}} \tag{20}$$

To eliminate the need for  $L_{inC}$ , let  $L_{inA} = L_{inB} = 0.5 \times$  $L_{in}$ . If two coils tightly wound on the same toroidal core have a coupling factor of  $k_{max} \approx 1$ , then  $L_{S1}$  and  $L_{C1}$  can be calculated as shown in (21) and (22), where  $M_1$  and  $M_2$ are obtained from the desired values given in (14) and (15).

$$L_{S1} = \frac{\left(\frac{M_1}{k_{max}}\right)^2}{0.5 \times L_{IN}}$$

$$L_{C1} = \frac{\left(\frac{M_2}{k_{max}}\right)^2}{0.5 \times L_{IN}}$$

(21)

$$L_{C1} = \frac{\left(\frac{M_2}{k_{max}}\right)^2}{0.5 \times L_{IN}} \tag{22}$$

It is then easy to calculate the separate series-connected inductances required,  $L_{S2}$  and  $L_{C2}$  by using (23) and (24).

$$L_{S2} = L_{SEPIC} - L_{S1} \tag{23}$$

$$L_{C2} = L_{Cuk} - L_{C1} (24)$$

This means that the overall mutual and self inductance (and hence performance) are identical to what would be obtained with a specialized inductor design. Both the uncoupled and coupled inductors used in the experimental testbed are shown in Fig. 9.

Fig. 9. Coupled and uncoupled inductors

## E. Experimental Results

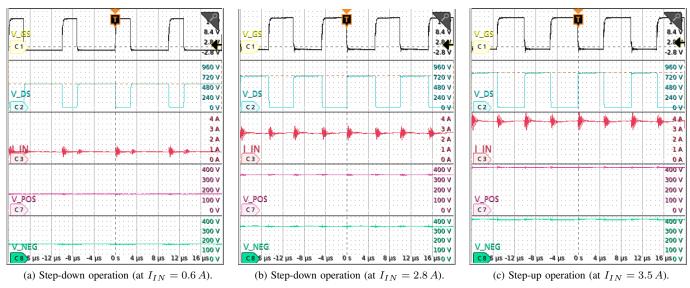

Experimental results are presented in Fig. 10, demonstrating the operation and performance of the converter using both uncoupled and coupled inductors, and clearly showing the large reduction in input ripple current. The experimental results have high frequency ringing present due to parasitics present (primarily the inter-turn capacitance of the inductor windings, but also stray inductance in the current paths for the MOSFET, diodes, and capacitors). This ringing could be substantially reduced with improved inductor and PCB design, however that is not the primary focus of this paper.

When all inductors are left uncoupled, the peak-to-peak 100 kHz input current ripple is 30.4%. When the integrated magnetics are introduced, the peak-to-peak current ripple drops to just 2.1%, representing a reduction of more than 93%. It can also be seen that there is a minor imbalance  $(\pm 0.5\%)$ between the positive and negative output voltages due to component non-idealities impacting each converter differently. The peak-to-peak output voltage ripple is calculated to be 1.2% for the positive DC output and 2.3% for the negative DC output. These values remain largely constant over variations in both input voltage and coupling factor, and agree closely with the simulation results presented in Fig. 6.

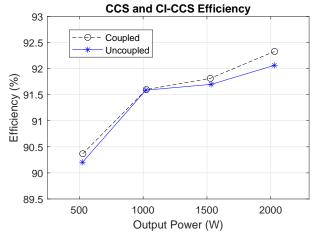

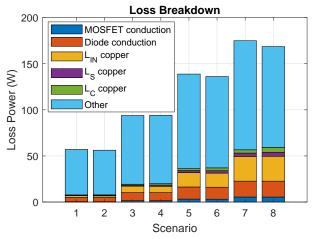

The converter's efficiency and loss sources (e.g. switching losses, conduction losses, core losses, copper losses) are each dependent on a number of parameters, including switching frequency and output power. The converter's efficiency has been measured at the designed switching frequency (100 kHz) over a range of output power.

Fig. 12a shows the measured efficiency for both the CCS and CI-CCS converters at rated input voltage (360 V). The efficiency remains largely constant over the range of powers tested, and is very similar between the CCS and CI-CCS converters, with the CI-CCS converter's efficiency being slightly higher. It is expected these loss reductions stem from smaller

Fig. 10. MOSFET voltage  $(V_{DS})$ ,  $I_{IN}$ ,  $I_{LS}$ ,  $I_{LC}$ ,  $V_{POS}$ ,  $V_{NEG}$  (with  $V_{IN} = V_{POS} = V_{NEG} = 360$  V, i.e. D = 0.5).

Fig. 11. CI-CCS topology showing the waveforms measured for efficiency calculations.

copper  $I^2R$  losses, switching losses, capacitor ESR losses, and hysteresis losses.

Fig. 11 shows the waveforms measured in the converter during the efficiency tests. These waveforms, in combination with datasheet information, have been used to determine the contribution of some loss sources. These breakdowns are shown in Fig. 12b, where the eight stacked graphs correspond to the efficiency measurements in Fig. 12a (scenarios 1 and 2 correspond to the 500 W output, both uncoupled and coupled; scenarios 3 and 4 correspond to the 1000 W output, uncoupled and coupled; scenarios 5 and 6 correspond to the

1.5 kW output, uncoupled and coupled; and scenarios 7 and 8 correspond to the 2 kW output, uncoupled and coupled). The height of these bars are equal to the total loss in each scenario, and the 'other' segments comprise mostly of the MOSFET switching (turn-on and turn-off) losses, though also include the inductor core losses and capacitor ESR losses.

In addition to these results which show a unity voltage gain for each individual output (360 V input and 360 V on each output), three additional sets of results are presented to demonstrate the wide voltage conversion ratios possible with this converter. These three tests are conducted with the same input voltage (400 V) and different duty cycles. Fig. 13a shows a step-down in both individual output voltages, as well as the overall positive-to-negative voltage bus. Fig. 13b shows a step-down for each individual output voltage (from 400 V in to 360 V out), but an overall step-up of the positive-to-negative voltage bus (from 400 V in to 720 V out). Fig. 13c shows a step-up in both individual output voltages, as well as the overall positive-to-negative voltage bus. It can also be observed that the input current ripple remains small in these scenarios.

# III. SOLAR PHOTOVOLTAICS INTEGRATION

## A. Maximum Power Point Tracking and Current Controller

Typical P-V and I-V curves for PV modules demonstrate the importance of the converter's input current as this determines the PV system's output current, and hence power. As discussed

(a) CCS and CI-CCS efficiency measurements.

(b) Loss breakdown for the CCS and CI-CCS converters at various output powers.

Fig. 12. Efficiency measurements for the CCS and CI-CCS over a range of output powers at the nominal input voltage condition  $(V_{in}=360\,V)$ .

in Section I-A, the CI-CCS converter is particularly well-suited for this application due to its continuous input current with low ripple, and grounded bipolar output.

An MPPT controller is designed based on an adaptive "hill climbing" method to operate at the highest point on the P-V curve and hence maximize the energy generated and reduce the power oscillations [28]. This works by varying the voltage reference,  $V_{ref}$ , by an adaptive amount,  $\Delta V_{adp}$ , which decreases as the output power nears the MPP.

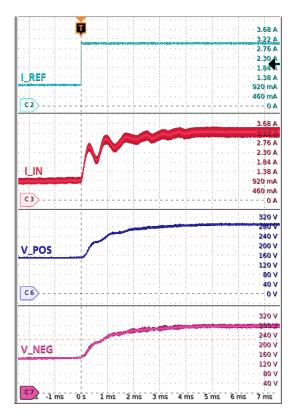

A PI-based current controller is designed which receives a continuously updated reference value from the MPPT controller. The reference generated by the MPPT would typically vary smoothly, however to demonstrate the performance of the current controller, a step change in the reference current is demanded. Fig. 14 shows the converter's response to this step change from 1 A to 3 A with an input voltage of 200 V. These results demonstrate that the converter is capable of tracking a 400 W step change in under 4 ms, meaning that its bandwidth is easily sufficient for optimal MPPT performance. It can also be seen that the output voltages also increase, resulting from the required change in duty cycle to obtain the higher input current at the same input voltage. When

considering the performance of the CI-CCS converter's current controller, it should be noted that the small signal model will differ depending on whether the converter's inductors are coupled or uncoupled. The MPPT controller's bandwidth requirement is very low compared with the converter's current controller bandwidth, so any differences are negligible for this PV application.

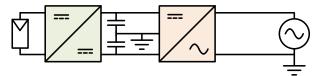

#### B. Grid Integration via Bipolar Input Inverter

In most PV applications it is desired to export generated solar power to an AC grid. The CI-CCS converter can be paired with with any inverter with a unipolar or bipolar DC input. If the former is used (e.g. H-bridge), then CI-CCS output is taken between the positive and negative DC terminals (with the midpoint left unconnected), however this system configuration does not provide the advantage of leakage current elimination. The grounded bipolar DC output structure of the CI-CCS converter therefore makes it better-suited for inverters with a grounded bipolar DC input (e.g. half-bridge inverter, T-type inverter, diode/neutral-point-clamped inverter, flying capacitor/capacitor-clamped inverter) as the lack of common mode voltage eliminates leakage currents, and the grounding of both the PV system and CI-CCS converter increases the system safety, and prolongs the lifetime of the PV panels.

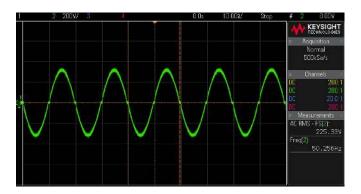

A 1 kW T-type single-phase inverter has been designed and constructed to be used in combination with the CI-CCS converter to demonstrate the complete power flow from the PV system to the grid. The complete topology for this system is given in Fig. 15, showing the input PV array, the proposed CI-CCS converter, the 100  $\mu$ F DC capacitance per output used to decoupled the 100 Hz ripple from the PV array, and the T-type inverter. The designed prototype also uses SiC MOSFETs and an LC output filter with a 330  $\mu$ H inductor and 1  $\mu$ F capacitor.

Full analysis and discussion of this T-type converter and the decoupling capacitor selection is left for another paper, however the fundamental result of the converter's AC output voltage is shown in Fig. 16, demonstrating a 50 Hz, 230 V output waveform (though a 60 Hz, 110 V output waveform is also possible with minor control changes). Some zero crossing distortion can be observed resulting from conservative duty cycle limits imposed, though this will be remedied in future work.

The CI-CCS converter is controlled to perform MPPT and the inverter is controlled to regulate the DC bus voltage, which in turn means varying the rms AC output current in order to export all generated solar power.

#### IV. CONCLUSION

Combining the input stages of the Cuk and SEPIC converters allows a bipolar DC output to be generated from a unipolar input, using only a single switch. This emerging converter topology shows many advantages for PV applications as its bipolar output structure allows the both the PV system and grid to be grounded without an isolation transformer.

In this paper, the benefits that can be derived by magnetically coupling the converter's input and output inductors are investigated. SiC power devices and nanocrystalline powder

Fig. 13. Switch signal ( $V_{GS}$ ), MOSFET voltage ( $V_{DS}$ ),  $I_{IN}$ ,  $I_{L_S}$ ,  $I_{L_C}$ ,  $V_{POS}$ ,  $V_{NEG}$  (with  $V_{IN} = 400$  V, at different output voltages).

Fig. 14. Reference current,  $I_{IN}$ ,  $V_{POS}$ ,  $V_{NEG}$  (with  $V_{IN} = 200$  V; k = 0.89).

cores are used in place of IGBTs and ferrite cores, enabling much higher switching frequencies. Together with the coupled inductors, minimal input current ripple has been realized, which enables high levels of PV utilization as the system can remain close to the power curve's peak. In addition to the lower input current ripple, a CCS converter with coupled inductors is smaller, lighter, and more efficient than its uncoupled equivalent. An inner-loop current controller has been designed to facilitate MPPT. A SiC-based T-type converter has

Fig. 15. Full system topology: PV, CI-CCS converter, decoupling capacitors, and T-type inverter.

Fig. 16. AC output voltage of the T-type converter connected directly to the CI-CCS converter's  $\pm 360$  V DC bus.

been used to export the PV power from the CI-CCS converter to the AC grid.

Results have been obtained, both in simulations and experimentally, which show that input current ripple reductions of 80-93% are possible, in addition to demonstrating the converter's step-up and step-down capabilities. The current controller's performance demonstrates its ability to track rapid changes in the MPPT current reference. The T-type converter has also been shown to successfully generate an AC voltage compatible with all major power systems.

#### ACKNOWLEDGMENTS

The authors would like to express their appreciation for the following funding sources: The General Sir John Monash Foundation, the Cambridge Trust (in partnership with Cambridge Australia Scholarships), and the Isaac Newton Trust.

#### REFERENCES

- [1] J. M. Carrasco, L. G. Franquelo, J. T. Bialasiewicz, E. Galvan, R. C. PortilloGuisado, M. A. M. Prats, J. I. Leon, and N. Moreno-Alfonso, "Power-electronic systems for the grid integration of renewable energy sources: A survey," *IEEE Transactions on Industrial Electronics*, vol. 53, no. 4, pp. 1002–1016, June 2006.

- [2] W. Xiao, N. Ozog, and W. G. Dunford, "Topology study of photovoltaic interface for maximum power point tracking," *IEEE Transactions on Industrial Electronics*, vol. 54, no. 3, pp. 1696–1704, June 2007.

- [3] G. R. Walker and P. C. Sernia, "Cascaded dc-dc converter connection of photovoltaic modules," *IEEE Transactions on Power Electronics*, vol. 19, no. 4, pp. 1130–1139, July 2004.

- [4] D. Meneses, F. Blaabjerg, . GarcÃa, and J. A. Cobos, "Review and comparison of step-up transformerless topologies for photovoltaic acmodule application," *IEEE Transactions on Power Electronics*, vol. 28, no. 6, pp. 2649–2663, June 2013.

- [5] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg, and B. Lehman, "Step-up dc-dc converters: A comprehensive review of voltage-boosting techniques, topologies, and applications," *IEEE Transactions on Power Electronics*, vol. 32, no. 12, pp. 9143–9178, Dec 2017.

- [6] M. Forouzesh, Y. Shen, K. Yari, Y. P. Siwakoti, and F. Blaabjerg, "High-efficiency high step-up dc-dc converter with dual coupled inductors for grid-connected photovoltaic systems," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 5967–5982, July 2018.

- [7] S. V. Araujo, P. Zacharias, and R. Mallwitz, "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 9, pp. 3118–3128, Sept 2010.

- [8] J. M. Shen, H. L. Jou, and J. C. Wu, "Novel transformerless grid-connected power converter with negative grounding for photovoltaic generation system," *IEEE Transactions on Power Electronics*, vol. 27, no. 4, pp. 1818–1829, April 2012.

- [9] Y. P. Siwakoti and F. Blaabjerg, "Common-ground-type transformerless inverters for single-phase solar photovoltaic systems," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 3, pp. 2100–2111, March 2018.

- [10] H. Xiao and S. Xie, "Leakage current analytical model and application in single-phase transformerless photovoltaic grid-connected inverter," *IEEE Transactions on Electromagnetic Compatibility*, vol. 52, no. 4, pp. 902–913, Nov 2010.

- [11] V. Sonti, S. Jain, and S. Bhattacharya, "Analysis of the modulation strategy for the minimization of the leakage current in the pv gridconnected cascaded multilevel inverter," *IEEE Transactions on Power Electronics*, vol. 32, no. 2, pp. 1156–1169, Feb 2017.

- [12] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Transactions* on *Industry Applications*, vol. 41, no. 5, pp. 1292–1306, Sept 2005.

- [13] S. Saridakis, E. Koutroulis, and F. Blaabjerg, "Optimal design of modern transformerless pv inverter topologies," *IEEE Transactions on Energy Conversion*, vol. 28, no. 2, pp. 394–404, June 2013.

- [14] Q. Li and P. Wolfs, "A review of the single phase photovoltaic module integrated converter topologies with three different dc link configurations," *IEEE Transactions on Power Electronics*, vol. 23, no. 3, pp. 1320–1333, May 2008.

- [15] W. Li, Y. Gu, H. Luo, W. Cui, X. He, and C. Xia, "Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression," *IEEE Transactions on Indus*trial Electronics, vol. 62, no. 7, pp. 4537–4551, July 2015.

- [16] X. Guo and X. Jia, "Hardware-based cascaded topology and modulation strategy with leakage current reduction for transformerless pv systems," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 12, pp. 7823–7832. Dec 2016.

- [17] E. Gubia, P. Sanchis, A. Ursua, J. Lopez, and L. Marroyo, "Ground currents in single-phase transformerless photovoltaic systems," *Progress* in *Photovoltaics: Research and Applications*, vol. 15, no. 7, pp. 629– 650, 2007.

- [18] S. Pingel, O. Frank, M. Winkler, S. Daryan, T. Geipel, H. Hoehne, and J. Berghold, "Potential induced degradation of solar cells and panels," in 2010 35th IEEE Photovoltaic Specialists Conference, June 2010, pp. 002 817–002 822.

- [19] A. Anand and B. Singh, "Power Factor Correction in Cuk-SEPIC Based Dual Output Converter fed SRM Drive," *IEEE Transactions on Industrial Electronics*, pp. 1–1, 2017.

- [20] M. B. Ferrera, S. P. Litran, E. Duran Aranda, and J. M. Andujar Marquez, "A Converter for Bipolar DC Link Based on SEPIC-Cuk Combination," *IEEE Transactions on Power Electronics*, vol. 30, no. 12, pp. 6483–6487, dec 2015.

- [21] M. B. Ferrera, S. P. Litran, E. Duran, and J. M. Andujar, "A SEPIC-Cuk converter combination for bipolar DC microgrid applications," in 2015 IEEE International Conference on Industrial Technology (ICIT). IEEE, mar 2015, pp. 884–889.

- [22] B.-R. Lin, K.-L. Shih, J.-J. Chen, and H.-K. Chiang, "Implementation of a zero voltage switching Sepic-Cuk converter," in 2008 3rd IEEE Conference on Industrial Electronics and Applications. IEEE, jun 2008, pp. 394–399.

- [23] N. Jayaram and D. Maksimovic, "Power factor correctors based on coupled-inductor Sepic and Cuk converters with nonlinear-carrier control," in APEC '98 Thirteenth Annual Applied Power Electronics Conference and Exposition, vol. 1. IEEE, 1998, pp. 468–474.

- [24] L. Mohammadian and E. Babaei, "Investigating the effect of inductor coupling on intrinsic stability of Cuk converter," in *IECON Proceedings* (*Industrial Electronics Conference*). IEEE, oct 2016, pp. 1359–1364.

- [25] M. S. Rylko, B. J. Lyons, J. G. Hayes, and M. G. Egan, "Revised magnetics performance factors and experimental comparison of highflux materials for high-current dc-dc inductors," *IEEE Transactions on Power Electronics*, vol. 26, no. 8, pp. 2112–2126, Aug 2011.

- [26] X. Wang, Z. Lu, C. Lu, and D. Li, "Fe-based nanocrystalline powder cores with ultra-low core loss," *Journal of Magnetism and Magnetic Materials*, vol. 347, pp. 1–3, dec 2013.

- [27] G. T. Nikolov and V. C. Valchev, "Nanocrystalline magnetic materials versus ferrites in power electronics," *Procedia Earth and Planetary Science*, vol. 1, no. 1, pp. 1357–1361, sep 2009.

- [28] W. Xiao and W. G. Dunford, "A modified adaptive hill climbing mppt method for photovoltaic power systems," in 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), vol. 3, June 2004, pp. 1957–1963 Vol.3.

Kumaran Nathan was born in Sydney, Australia, in 1990. He received the Bachelor of Engineering (Electrical) from the University of Newcastle, Australia, in 2012. He worked as an electrical engineer at Ausgrid, a large Australian transmission & distribution electrical power utility. He is currently working toward the Ph.D. degree in Engineering at the University of Cambridge, UK. His research is focused on power electronic converters for renewable energy systems.

Saikat Ghosh (SM'18) received the Bachelor of Engineering from Indian Institute of Engineering Science and Technology, Shibpur, India in 2011, and the Master of Engineering in 2013 from the Indian Institute of Science, India. After a two-year career as a manager, at Engineering Research Centre of Tata Motors Limited, he joined the University of Cambridge, Engineering Department in 2015. He is currently working toward the Ph.D. degree and his research interests include electrical drives (particularly for automotive applications), power electronic

converters, and high-frequency converters using wide bandgap devices..

Yam Siwakoti (S'10–M'14) received the B.Tech. degree in electrical engineering from the National Institute of Technology, Hamirpur, India, in 2005, the M.E. degree in electrical power engineering from the Norwegian University of Science and Technology, Trondheim, Norway, and Kathmandu University, Dhulikhel, Nepal, in 2010, and the Ph.D. degree from Macquarie University, Sydney, Australia, in 2014. He was a postdoctoral fellow at the Department of Energy Technology, Aalborg University, Denmark (2014-2016). He was a visiting scientist

at the Fraunhofer Institute for Solar Energy Systems, Freiburg, Germany (2017/2018). He also served as a Guest Associate Editor of the IEEE transaction on Power Electronics (2015/2016). He is also a recipient of the prestigious Green Talent Award from the Federal Ministry of Education and Research, Germany in 2016. Currently he is a Lecturer in the Faculty of Engineering and Information Technology, University of Technology Sydney, Australia. He serves as an Associate Editor of the IEEE Transactions on Industrial Electronics, and the IET Power Electronics; and also a peer review college member of Engineering and Physical Science Research Council (EPSRC), UK.

Teng Long (M'13) received the B.Eng. degree from the Huazhong University of Science and Technology, China, the first class B.Eng. (Hons.) degree from the University of Birmingham, UK in 2009, and the Ph.D. degree from the University of Cambridge, UK in 2013. Until 2016, he was a Power Electronics Engineer with the General Electric (GE) Power Conversion business in Rugby, UK. He is currently a Lecturer with the University of Cambridge. His research interests include power electronics, electrical machines, and machine drives. Dr Long is a

Chartered Engineer (CEng) registered with the Engineering Council in the UK.