# A New Low-Frequency State Model of a Three-Phase Three-Switch Three-Level Fixed-Frequency PWM Rectifier

H. Kanaan, K. Al-Haddad, R. Chaffai\*, L. Duguay\* and F. Fnaiech\*\*

École de Technologie Supérieure 1100 Rue Notre-Dame Ouest, Montreal, Quebec, H3C 1K3, Canada Tel: (514) 396-8874, Fax: (514) 396-8684 E-mail: kamal@ele.etsmtl.ca , hkanaan@ele.etsmtl.ca

\* ASTEC Advanced Power System 2280 Boul. Alfred Nobel, Saint-Laurent, Quebec, H4S 2A4, Canada

\*\* ESSTT – University of Tunis 5 Av. Taha Hussein 1008 Tunis TUNISIA Farhat.Fnaiech@esstt.rnu.tn

#### **ABSTRACT**

This paper presents a new dynamic model of a three-phase, three-switch, three-level, fixed-frequency Pulse-Width-Modulated (PWM) rectifier. The modeling approach uses the state-space averaging technique in continuous current mode. The averaging process is applied on two time intervals: the switching period for average current evaluation, and the mains period for average voltage computation. A basic mathematical model of the converter is first established. A simplified time-invariant model is then deduced using rotating Park transformation. The steady-state regime is analyzed on the basis of the obtained model, and converter design criteria are consequently discussed. Numerical simulations are carried out in order to demonstrate the effectiveness of the proposed modeling approach.

#### I – INTRODUCTION

AC-to-DC three-phase converters are increasingly required to provide high input power factor, low line current distortion, fixed output voltage and robustness to load and utility voltage unbalances. Several topologies that satisfy these requirements have been proposed recently [1]. Among these structures, the three-switch, three-level AC-to-DC converter, known as the Vienna rectifier, is characterized by a low number of high-frequency switches, high efficiency, low design costs and low voltage stresses, which make it suitable for high or medium power applications [2]. Besides its topological advantages, this converter is also known for its low control complexity and its low sensing effort regarding the control system design and implementation [3].

In this paper, a new mathematical model of a three-phase, three-switch, three-level, fixed-frequency Pulse-Width-modulated (PWM) rectifier, operating in continuous current mode, is developed from a control design perspective. The

model is elaborated using the state-space averaging technique commonly used in PWM DC-DC converters modeling problems [4]. This modeling approach is so far valid as long as the input and state variables of the converter vary slowly in time. Other modeling techniques have already been proposed in the literature, such that the averaging technique that is based on equivalent circuit manipulation [4], and the Fourier analysis based modeling approach [5]. Although their differences, they all yields at the same low-frequency representation of the converter.

The basic model firstly obtained for the converter is a nonlinear fifth-order time-varying system, and the elaboration and implementation of a corresponding suitable control law seem highly difficult. Thus, in order to simplify the eventual control design procedure, a fourth-order time-invariant model is elaborated by applying to the former one two transformations: a three-axis/two-axis frame transformation [5], known as Park transformation, and an input vector nonlinear transformation. The effectiveness of the proposed modeling approach is highlighted through numerical simulation using the Power System Blockset tool of Matlab/Simulink.

This paper is divided into five sections. In section II, a brief description of the converter topology and operation is presented. In section III, the reduced nonlinear time-invariant low-frequency model of the converter is elaborated. All the corresponding theoretical developments are indicated, including the three-axis/two-axis frame transformation and the proposed input vector nonlinear transformation. Based on the obtained model, the steady-state operating mode of the converter is analyzed in section IV. Design criteria allowing a suitable choice of the converter parameters, namely the reactive elements, are then enumerated in the section V. Finally, the numerical results showing the effectiveness of the proposed modeling approach are presented in section VI.

# II – CONVERTER TOPOLOGY AND OPERATING MODE

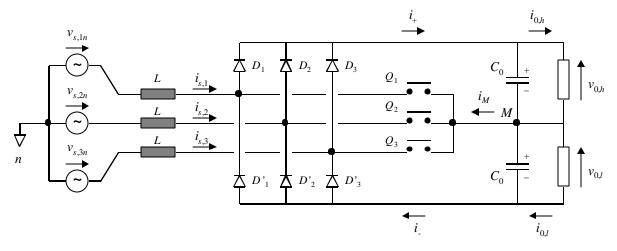

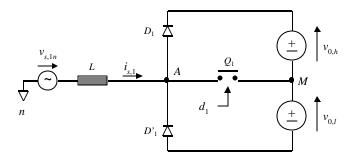

The converter topology is presented in Fig. 1. It consists of three single-switch legs associated to each phase.  $Q_1$ ,  $Q_2$  and  $Q_3$  are four-quadrants switches. They are controlled in order to ensure line current shaping at the input, DC voltage regulation and middle point stabilization at the output. From an operational view, the converter can be seen as an association of three identical bi-directional boost converters, as the one presented in Fig. 2 for phase 1. Referring to this figure, we may write the following equation for phase 1:

$$v_{s,1n} = L \frac{di_{s,1}}{dt} + v_{M,n} + v_{AM}$$

(1)

where  $v_{s,1n}$  is the phase-to-neutral voltage,  $i_{s,1}$  the phase current,  $v_{M,n}$  the middle point voltage with respect to the mains neutral, and  $v_{AM}$  the switch voltage defined as:

$$v_{AM} = \begin{cases} 0 & \text{if } Q_1 \text{ is turned - on} \\ v_{0,h} & \text{if } Q_1 \text{ is turned - off and } i_{s,1} > 0 \\ -v_{0,l} & \text{if } Q_1 \text{ is turned - off and } i_{s,1} < 0 \end{cases}$$

(2)

$v_{0,h}$  and  $v_{0,l}$  being respectively the upper and lower output voltages. Hence, we may express  $v_{AM}$  as follows:

$$v_{AM} = \left[ \frac{v_{0,h} + v_{0,l}}{2} \operatorname{sgn}(i_{s,1}) + \frac{v_{0,h} - v_{0,l}}{2} \right] \cdot (1 - s_1)$$

(3)

where sgn is the signum function, and  $s_1$  the switching function defined as:

$$s_1 = \begin{cases} 0 & \text{if } Q_1 \text{ is turned - off} \\ 1 & \text{if } Q_1 \text{ is turned - on} \end{cases}$$

(4)

In the same way, we can write for the other two phases the following equations:

$$v_{s,2n} = L \frac{di_{s,2}}{dt} + v_{M,n} + v_{BM}$$

(5)

and:

$$v_{s,3n} = L \frac{di_{s,3}}{dt} + v_{M,n} + v_{CM}$$

(6)

where:

$$v_{BM} = \left[ \frac{v_{0,h} + v_{0,l}}{2} \operatorname{sgn}(i_{s,2}) + \frac{v_{0,h} - v_{0,l}}{2} \right] \cdot (1 - s_2)$$

(7)

and

$$v_{CM} = \left[ \frac{v_{0,h} + v_{0,l}}{2} \operatorname{sgn}(i_{s,3}) + \frac{v_{0,h} - v_{0,l}}{2} \right] \cdot (1 - s_3)$$

(8)

$s_2$  and  $s_3$  being the switching functions corresponding to  $Q_2$  and  $Q_3$  respectively.

In the nominal steady-state regime with a balanced load,  $v_{0,h}$  and  $v_{0,l}$  are equal to  $v_0/2$ , where  $v_0 = v_{0,h} + v_{0,l}$  is the overall output voltage. We may thus rewrite equations (3), (7) and (8) as follows:

$$v_{AM} \cong \frac{v_0}{2} \operatorname{sgn}(i_{s,1}) (1 - s_1) \tag{9.a}$$

$$v_{BM} \cong \frac{v_0}{2} \operatorname{sgn}(i_{s,2}) (1 - s_2)$$

(9.b)

$$v_{CM} \cong \frac{v_0}{2} \operatorname{sgn}(i_{s,3})(1-s_3)$$

(9.c)

Fig. 1. Three-phase, three-switch, three-level rectifier

Fig. 2. Single-phase equivalent circuit

Furthermore, assuming that the utility voltages are balanced sine waves, and that the neutral is disconnected, it follows:

$$v_{s,n}(t) + v_{s,2n}(t) + v_{s,3n}(t) = 0$$

,  $\forall t$  (10)

and:

$$i_{s1}(t) + i_{s2}(t) + i_{s3}(t) = 0$$

,  $\forall t$  (11)

Using equalities (10) and (11) in equations (1), (5) and (6) yields:

$$v_{M,n} = -\frac{1}{3} \left( v_{AM} + v_{BM} + v_{CM} \right) \tag{12}$$

which can be rewritten using expressions (9):

$$v_{M,n} = -\frac{v_0}{6} \sum_{k=1}^{3} \operatorname{sgn}(i_{s,k}) (1 - s_k)$$

(13)

The values of  $v_{M,n}$  are given in Tab. 1 with respect to the switching states  $s_k$  and the sign of line currents  $i_{s,k}$ ,  $k \in \{1, 2, 3\}$ . Thus, the value of  $v_{M,n}$  depends only on the output voltage  $v_0$ . Referring to equations (1), (5) and (6), it is noticed that, in order to ensure line current waveshaping, the following two conditions must be always respected:

$$\left|v_{s,kn}(t)\right| > \pm v_{M,n}(t)$$

,  $\forall t \text{ and } \forall k \in \{1, 2, 3\}$  (14)

$$|v_{s,kn}(t)| < \pm \left(v_{M,n} + \frac{v_0}{2}\right), \quad \forall t \text{ and } \forall k \in \{1, 2, 3\}$$

(15)

Conditions (14) and (15) limit the choice of the output voltage value in the range:

$$\frac{3}{2}V_{s}\sqrt{6} < v_{0} < 3V_{s}\sqrt{6} \tag{16}$$

i.e., between  $3.68V_S$  and  $7.34V_S$ , where  $V_S$  is the RMS-value of the phase-to-neutral mains voltage.

# III – STATE-SPACE AVERAGE MODELING OF THE CONVERTER

#### 3.1. Basic model

The modeling approach applied to the converter in Fig. 1 is based on the state-space averaging technique [4]. In this method, all variables are averaged on a sampling period  $T_S$ . Including equations (3), (7), (8) and (12) in the system equations (1), (5) and (6), the equivalent average model of the converter, viewed on the AC side, is as follows:

$$\begin{bmatrix} v_{s,1n} \\ v_{s,2n} \\ v_{s,3n} \end{bmatrix} = L \frac{d}{dt} \begin{bmatrix} i_{s,1} \\ i_{s,2} \\ i_{s,3} \end{bmatrix} + \mathbf{G} \left( \frac{v_0}{2} \mathbf{SGN} + \frac{\Delta v_0}{2} \mathbf{I}_3 \right) \begin{bmatrix} 1 - d_1 \\ 1 - d_2 \\ 1 - d_3 \end{bmatrix}$$

(17)

where:

$$\mathbf{G} = \begin{bmatrix} 2/3 & -1/3 & -1/3 \\ -1/3 & 2/3 & -1/3 \\ -1/3 & -1/3 & 2/3 \end{bmatrix}$$

$$\mathbf{SGN} = \begin{bmatrix} \operatorname{sgn}(i_{s,1}) & 0 & 0 \\ 0 & \operatorname{sgn}(i_{s,2}) & 0 \\ 0 & 0 & \operatorname{sgn}(i_{s,3}) \end{bmatrix}$$

$\Delta v_0 = v_{0,h} - v_{0,l}$ , and  $\mathbf{I}_3$  is the third-order identity matrix.  $d_1$ ,  $d_2$  and  $d_3$  are the duty cycles of switches  $Q_1$ ,  $Q_2$  and  $Q_3$  respectively. Note that system (17) is a time-varying model that depends on the sign of the line currents  $i_{s,1}$ ,  $i_{s,2}$  and  $i_{s,3}$ .

|                                               | Switching functions $s_1$ , $s_2$ and $s_3$ |          |          |          |          |          |          |          |

|-----------------------------------------------|---------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| Conditions                                    | 111                                         | 110      | 101      | 011      | 100      | 001      | 010      | 000      |

| $i_{s,1} > 0$ , $i_{s,2} < 0$ , $i_{s,3} > 0$ | 0                                           | $-v_0/6$ | $v_0/6$  | $-v_0/6$ | 0        | 0        | $-v_0/3$ | $-v_0/6$ |

| $i_{s,1} > 0$ , $i_{s,2} < 0$ , $i_{s,3} < 0$ | 0                                           | $v_0/6$  | $v_0/6$  | $-v_0/6$ | $v_0/3$  | 0        | 0        | $v_0/6$  |

| $i_{s,1} > 0$ , $i_{s,2} > 0$ , $i_{s,3} < 0$ | 0                                           | $v_0/6$  | $-v_0/6$ | $-v_0/6$ | 0        | $-v_0/3$ | 0        | $-v_0/6$ |

| $i_{s,1} < 0$ , $i_{s,2} > 0$ , $i_{s,3} < 0$ | 0                                           | $v_0/6$  | $-v_0/6$ | $v_0/6$  | 0        | 0        | $v_0/3$  | $v_0/6$  |

| $i_{s,1} < 0, i_{s,2} > 0, i_{s,3} > 0$       | 0                                           | $-v_0/6$ | $-v_0/6$ | $v_0/6$  | $-v_0/3$ | 0        | 0        | $-v_0/6$ |

| $i_{s,1} < 0$ , $i_{s,2} < 0$ , $i_{s,3} > 0$ | 0                                           | $-v_0/6$ | $v_0/6$  | $v_0/6$  | 0        | $v_0/3$  | 0        | $v_0/6$  |

Tab. 1. Values of  $v_{M,n}$  with respect to the switching states and the sign of line currents

Therefore, it is not suitable for a stationary control design process. In order to overcome this drawback, the following input transformation is proposed:

$$d'_{k} = (1 - d_{k}) \left[ \operatorname{sgn}(i_{s,k}) + \frac{\Delta v_{0}}{v_{0}} \right] , \forall k \in \{1, 2, 3\}$$

(18)

Adding equation (18) to equation (17) gives:

$$\mathbf{v}_{s} = L \frac{d \,\mathbf{i}_{s}}{dt} + \frac{v_{0}}{2} \,\mathbf{G} \,\mathbf{d}' \tag{19}$$

where  $\mathbf{v_s} = [v_{s,1n}, v_{s,2n}, v_{s,3n}]^T$  is the input voltage vector,  $\mathbf{i_s} = [i_{s,1}, i_{s,2}, i_{s,3}]^T$  the input current vector and  $\mathbf{d'} = [d'_1, d'_2, d'_3]^T$  the new control vector.

Furthermore, at the load level, the average model of the converter is viewed as:

$$C_0 \frac{d v_{0,h}}{dt} + i_{0,h} = i_+ = \frac{1}{2} \sum_{k=1}^{3} (1 - d_k) i_{s,k} \left[ 1 + \operatorname{sgn}(i_{s,k}) \right]$$

(20.a)

$$C_0 \frac{d v_{0,l}}{dt} + i_{0,l} = i_- = -\frac{1}{2} \sum_{k=1}^{3} (1 - d_k) i_{s,k} \left[ 1 - \operatorname{sgn}(i_{s,k}) \right]$$

(20.b)

where  $i_{0,h}$  and  $i_{0,l}$  are the upper and lower output currents,  $i_+$  and  $i_-$  the DC side currents of the diode bridge. Introducing the overall output voltage  $v_0$ , the output voltage unbalance  $\Delta v_0$  and transformation (18) into equations (20) yields:

$$C_0 \frac{d v_0}{dt} + i_{0,h} + i_{0,l} \cong \sum_{k=1}^{3} d'_k i_{s,k} \left[ 1 - \frac{\Delta v_0}{v_0} \operatorname{sgn}(i_{s,k}) \right]$$

(21.a)

$$C_0 \frac{d(\Delta v_0)}{dt} + i_{0,h} - i_{0,l} \cong \sum_{k=1}^{3} d'_k i_{s,k} \left[ \text{sgn}(i_{s,k}) - \frac{\Delta v_0}{v_0} \right]$$

(21.b)

In the derivation of equations (21), it was assumed that  $\Delta \nu_0/\nu_0 << 1$ . Equations (19) and (21) represent the basic low-frequency model of the converter in the stationary frame. Although equation (19) is time-invariant, the sub-system (21) is not. Nevertheless, knowing that the output voltages variations are relatively slow with respect to the mains

frequency, it seems more convenient, from a control design perspective, to consider their average on a mains period  $T_0$  instead of the one computed on a sampling period  $T_S$ . Furthermore, the basic model can be significantly reduced by applying Park's transformation, as discussed in the next subsection.

#### 3.2. Frame transformation

The model defined by equations (19) and (21) can be expressed in a new rotating frame using Park's transformation. The Park's matrix is defined as [5]:

$$\mathbf{K} = \frac{2}{3} \begin{bmatrix} \sin(\mathbf{w}_0 t) & \sin(\mathbf{w}_0 t - 2\mathbf{p}/3) & \sin(\mathbf{w}_0 t - 4\mathbf{p}/3) \\ \cos(\mathbf{w}_0 t) & \cos(\mathbf{w}_0 t - 2\mathbf{p}/3) & \cos(\mathbf{w}_0 t - 4\mathbf{p}/3) \\ 3/2 & 3/2 & 3/2 \end{bmatrix} (22)$$

where  $\mathbf{w}_0$  is the mains angular frequency. Defining the new vectors  $\mathbf{v}_s^r$ ,  $\mathbf{i}_s^r$  and  $\mathbf{d}^r$  as follows:

$$\mathbf{v}_{s}^{\prime} \stackrel{\Delta}{=} \begin{bmatrix} v_{s,d} & v_{s,q} & v_{s,0} \end{bmatrix}^{T} = \mathbf{K} \mathbf{v}_{s}$$

(23.a)

$$\mathbf{i}_{\mathbf{s}}^{r} \stackrel{\triangle}{=} \begin{bmatrix} i_{s,d} & i_{s,q} & i_{s,0} \end{bmatrix}^{T} = \mathbf{K} \mathbf{i}_{\mathbf{s}}$$

(23.b)

$$\mathbf{d'}^r \stackrel{\Delta}{=} \begin{bmatrix} d'_d & d'_a & d'_0 \end{bmatrix}^T = \mathbf{K} \, \mathbf{d'}$$

(23.c)

equations (19) and (21) can be arranged as given in (24). The voltage and current zero sequence components  $v_{s,0}$  and  $i_{s,0}$  are eliminated, as shown by (10) and (11). A time-invariant equivalent model of the converter can be elaborated by averaging the term  $[\mathbf{K} \mathbf{SGN}^{-1} \mathbf{K}^T]^{-1}$  over the mains period  $T_0$ , as mentioned above. Furthermore, the generality of the modeling approach would not be lost if we assume balanced sine wave line currents. It follows:

$$<\left[\mathbf{K}\cdot\mathbf{SGN}^{-1}\cdot\mathbf{K}^{\mathrm{T}}\right]^{-1}>_{T_0} \cong \boldsymbol{a}\begin{bmatrix}0&0&\cos\boldsymbol{j}\\0&0&\sin\boldsymbol{j}\\\cos\boldsymbol{j}&\sin\boldsymbol{j}&0\end{bmatrix}$$

(25)

$$v_{s,d} = L \frac{di_{s,d}}{dt} - L \mathbf{w}_0 i_{s,q} + \frac{v_0}{2} d'_d$$

(24.a)

$$v_{s,q} = L \frac{di_{s,q}}{dt} + L \mathbf{w}_0 i_{s,d} + \frac{v_0}{2} d_q'$$

(24.b)

$$C_{0} \frac{dv_{0}}{dt} + i_{0,h} + i_{0,l} = \frac{3}{2} \left( d'_{d} i_{s,d} + d'_{q} i_{s,q} \right) - \frac{\Delta v_{0}}{v_{0}} \left( \mathbf{d'}^{r} \right)^{T} \left[ \mathbf{K} \, \mathbf{SGN}^{-1} \, \, \mathbf{K}^{T} \right]^{-1} \mathbf{i}_{s}^{r}$$

(24.c)

$$C_{0} \frac{d \left(\Delta v_{0}\right)}{dt} + i_{0,h} - i_{0,l} = -\frac{3}{2} \frac{? v_{0}}{v_{0}} \left(d'_{d} i_{s,d} + d'_{q} i_{s,q}\right) + \left(\mathbf{d'}^{r}\right)^{T} \left[\mathbf{K} \, \mathbf{SGN}^{-1} \, \mathbf{K}^{T}\right]^{-1} \, \mathbf{i}_{s}^{r}$$

(24.d)

where j denotes the phase shift between the phase voltage and the corresponding line current. The parameter a is estimated by:

$$\mathbf{a} \cong \frac{2}{\mathbf{p}} \cong 0.64 \tag{26}$$

Note that  $\langle x \rangle_{T_0}$  is the average of x over  $T_0$ . In a unity power factor operating mode,  $\mathbf{j}$  equals zero and, hence, we may rewrite system (24) as follows:

$$v_{s,d} = L \frac{di_{s,d}}{dt} - L \mathbf{w}_{0} i_{s,q} + \frac{v_{0}}{2} d'_{d}$$

$$v_{s,q} = L \frac{di_{s,q}}{dt} + L \mathbf{w}_{0} i_{s,d} + \frac{v_{0}}{2} d'_{q}$$

$$C_{0} \frac{dv_{0}}{dt} = \frac{3}{2} \left( d'_{d} i_{s,d} + d'_{q} i_{s,q} \right) - \mathbf{a} \frac{\Delta v_{0}}{v_{0}} d'_{0} i_{s,d} - i_{0,h} - i_{0,l}$$

$$C_{0} \frac{d \left( \Delta v_{0} \right)}{dt} = \mathbf{a} d'_{0} i_{s,d} - \frac{3}{2} \frac{\Delta v_{0}}{v_{0}} \left( d'_{d} i_{s,d} + d'_{q} i_{s,q} \right) - i_{0,h} + i_{0,l}$$

(27)

As shown by equations (27), the converter in Fig. 1 may thus be represented in low-frequency domain by a fourth-order nonlinear dynamic system, having  $i_{s,d}$ ,  $i_{s,q}$ ,  $v_0$  and  $\Delta v_0$  as state variables,  $d'_d$ ,  $d'_q$  and  $d'_0$  as control inputs,  $v_{s,d}$  and  $v_{s,q}$  as disturbance inputs.

# IV - STEADY-STATE OPERATING REGIME

In the following, the theoretical expressions and waveforms of all system variables are established in the steady-state regime assuming:

- a balanced three-phase voltage source, i.e.:

$$v_{s,1n}^{*}(t) = V_{s}^{*} \sqrt{2} \sin(\mathbf{w}_{0}t)$$

$$v_{s,2n}^{*}(t) = V_{s}^{*} \sqrt{2} \sin(\mathbf{w}_{0}t - 2\mathbf{p}/3)$$

$$v_{s,2n}^{*}(t) = V_{s}^{*} \sqrt{2} \sin(\mathbf{w}_{0}t - 4\mathbf{p}/3)$$

(28)

where  $V_s^*$  is the steady-state RMS-value of the mains phase-to-neutral voltage,

- a unity power factor operating condition, i.e.:

$$i_{s,1}^{*}(t) = I_{s}^{*} \sqrt{2} \sin(\mathbf{w}_{0}t)$$

$$i_{s,2}^{*}(t) = I_{s}^{*} \sqrt{2} \sin(\mathbf{w}_{0}t - 2\mathbf{p}/3)$$

$$i_{s,3}^{*}(t) = I_{s}^{*} \sqrt{2} \sin(\mathbf{w}_{0}t - 4\mathbf{p}/3)$$

(29)

$I_S^*$  being the steady-state RMS-value of the line currents,

- and balanced output voltages, i.e.:

$$v_{0,h}^* = v_{0,l}^* = \frac{V_0^*}{2} \tag{30}$$

${V_0}^{st}$  denotes the steady-state fixed value of the overall output voltage. The asterisks in expressions (28) to (30) characterize the steady-state regime. Applying Park's transformation to the voltage and current expressions (28) and (29) yields time-invariant vectors expressed in the rotating frame as:

$$\mathbf{v}_{s}^{r} \stackrel{\Delta}{=} \begin{bmatrix} v_{s,d}^{*} \\ v_{s,q}^{*} \\ v_{s,0}^{*} \end{bmatrix} = \begin{bmatrix} V_{s}^{*} \sqrt{2} \\ 0 \\ 0 \end{bmatrix} \quad \text{and} \quad \mathbf{i}_{s}^{r} \stackrel{\Delta}{=} \begin{bmatrix} i_{s,d}^{*} \\ i_{s,q}^{*} \\ i_{s,0}^{*} \end{bmatrix} = \begin{bmatrix} I_{s}^{*} \sqrt{2} \\ 0 \\ 0 \end{bmatrix} \quad (31)$$

Substituting expressions (31) into system (27), the steady-state values of the control inputs are obtained as follows:

$$d'_{d}^{*} = \frac{2 V_{S}^{*} \sqrt{2}}{V_{0}^{*}}$$

$$d'_{q}^{*} = -\frac{2 L \mathbf{w}_{0} I_{S}^{*} \sqrt{2}}{V_{0}^{*}}$$

$$d'_{0}^{*} = \frac{i_{0,h}^{*} - i_{0,l}^{*}}{\mathbf{a} I_{S}^{*} \sqrt{2}}$$

(32)

It follows from equations (32) that  $d_d^{\prime*}$ ,  $d_q^{\prime*}$  and  $d_0^{\prime*}$  control respectively the output voltage, the input current and the load unbalance. Furthermore, the power conservation law is verified:

$$3V_S^*I_S^* = \frac{V_0^*}{2} \left( i_{0,h}^* + i_{0,l}^* \right) \tag{33}$$

Referring to the stationary frame, the steady-state control inputs are expressed as follows:

$$\begin{bmatrix} d_1'^* \\ d_2'^* \\ d_3'^* \end{bmatrix}^{\Delta} = \mathbf{K}^{-1} \begin{bmatrix} d_d'^* \\ d_q'^* \\ d_0'^* \end{bmatrix} = \begin{bmatrix} \hat{d}' \sin(\mathbf{w}_0 t - \mathbf{f}) + d_0'^* / 3 \\ \hat{d}' \sin(\mathbf{w}_0 t - \mathbf{f} - 2\mathbf{p}/3) + d_0'^* / 3 \\ \hat{d}' \sin(\mathbf{w}_0 t - \mathbf{f} - 4\mathbf{p}/3) + d_0'^* / 3 \end{bmatrix}$$

(34)

where:

$$\hat{d}' = \frac{2V_s^* \sqrt{2}}{V_s^* \cos f} \tag{35}$$

and:

$$\operatorname{tg} \mathbf{f} = \frac{L\mathbf{w}_0 I_s^*}{V_s^*} \tag{36}$$

Using equation (18), we may set therefore expression (37) (in the bottom of this page), for  $k \in \{1, 2, 3\}$ . This expression shows that the duty cycles  $d_1^*$ ,  $d_2^*$  and  $d_3^*$  vary periodically, with a  $T_0/2$  period. It also emphasizes the control saturation phenomenon, which takes place periodically. Its maximum duration angle is given by:

$$\mathbf{g} = \mathbf{f} + \sin^{-1} \left( \frac{\left| d_0'^* \right|}{3\hat{d}'} \right)$$

(38)

or, using equations (32), (33) and (35):

$$\mathbf{g} = \mathbf{f} + \sin^{-1} \left( \frac{\Delta i_0^*}{i_{0,h}^* + i_{0,l}^*} \frac{\cos \mathbf{f}}{2 \, \mathbf{a}} \right)$$

(39)

where  $\Delta i_0^* \stackrel{\Delta}{=} |i_{0,h}^* - i_{0,l}^*|$ . It is noticed from expressions (36) and (39) that, in order to reduce the undesirable effects of the control saturation, the load unbalance must be limited and the inductor value L has to be minimized.

Furthermore, following equations (13) and (18), the averaged middle point voltage may be expressed as:

$$v_{M,n} \cong -\frac{v_0}{6} \sum_{k=1}^{3} \left[ 1 - \frac{\Delta v_0}{v_0} \operatorname{sgn}(i_{s,k}) \right] d'_k$$

(40)

Using equation (34), it follows in steady state regime:

$$v_{M,n}^* = -\frac{V_0^*}{6} \sum_{k=1}^3 d_k^{\prime *} = -\frac{V_0^* d_0^{\prime *}}{6}$$

(41)

Concerning the steady-state expressions of DC-side currents  $i_+$  and  $i_-$ , they could be easily established as:

$$i_{+}^{*} = \frac{1}{2} \sum_{k=1}^{3} d_{k}^{\prime *} i_{s,k}^{*} \left[ 1 + \operatorname{sgn}(i_{s,k}^{*}) \right]$$

(42.a)

and:

$$i_{-}^{*} = \frac{1}{2} \sum_{k=1}^{3} d_{k}^{\prime *} i_{s,k}^{*} \left[ 1 - \operatorname{sgn}(i_{s,k}^{*}) \right]$$

(42.b)

Substituting equations (29) and (34) into (42.a), it yields after some manipulation to the expressions given (in the bottom of this page) by (43) for current  $i_+^*$ . Similar expressions are obtained for current  $i_-^*$ , but their corresponding intervals are shifted by  $\boldsymbol{p}$ . Note that currents  $i_+^*$  and  $i_-^*$  have practically a third harmonic sine wave shape.

#### V – DESIGN CRITERIA

### 5.1. Inductors design

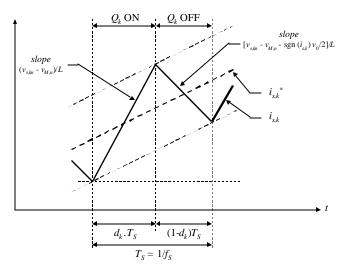

In order to ensure current waveshaping in steady-state regime, the common value of mains series inductors have to satisfy the following conditions, as described in Fig. 3:

$$v_{s,kn}^* - v_{M,n} > L \frac{di_{s,k}^*}{dt}$$

, when  $i_{s,k}^* > 0$  (44.a)

$$v_{s,kn}^* - v_{M,n} - \frac{V_0^*}{2} < L \frac{di_{s,k}^*}{dt}$$

$$v_{s,kn}^* - v_{M,n} < L \frac{di_{s,k}^*}{dt}$$

, when  $i_{s,k}^* < 0$  (44.b)

$$v_{s,kn}^* - v_{M,n} + \frac{V_0^*}{2} > L \frac{di_{s,k}^*}{dt}$$

$$d_{k}^{*} = 1 - d_{k}^{'*} \operatorname{sgn}(i_{s,k}^{*}) = \begin{cases} 1 - \hat{d}' \sin[\mathbf{w}_{0}t - \mathbf{f} - 2(k-1)\mathbf{p}/3] - d_{0}^{'*}/3 &, 2(k-1)\mathbf{p}/3 < \mathbf{w}_{0}t < \mathbf{p} + 2(k-1)\mathbf{p}/3 \\ 1 + \hat{d}' \sin[\mathbf{w}_{0}t - \mathbf{f} - 2(k-1)\mathbf{p}/3] + d_{0}^{'*}/3 &, \mathbf{p} + 2(k-1)\mathbf{p}/3 < \mathbf{w}_{0}t < 2\mathbf{p} + 2(k-1)\mathbf{p}/3 \end{cases}$$

$$\begin{cases} \frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ 2 \cos \mathbf{f} + \cos(2\mathbf{w}_{0}t - \mathbf{f} - 4\mathbf{p}/3) \right] - \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t - 2\mathbf{p}/3) &, 0 < \mathbf{w}_{0}t < \mathbf{p}/3 \\ \frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ \cos \mathbf{f} - \cos(2\mathbf{w}_{0}t - \mathbf{f}) \right] + \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t) &, \mathbf{p}/3 < \mathbf{w}_{0}t < 2\mathbf{p}/3 \end{cases}$$

$$i_{+}^{*} = \begin{cases} \frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ 2 \cos \mathbf{f} + \cos(2\mathbf{w}_{0}t - \mathbf{f} - 2\mathbf{p}/3) \right] - \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t - 4\mathbf{p}/3) &, 2\mathbf{p}/3 < \mathbf{w}_{0}t < \mathbf{p} \end{cases}$$

$$\frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ \cos \mathbf{f} - \cos(2\mathbf{w}_{0}t - \mathbf{f} - 2\mathbf{p}/3) \right] + \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t - 2\mathbf{p}/3) &, \mathbf{p} < \mathbf{w}_{0}t < 4\mathbf{p}/3 \end{cases}$$

$$\frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ 2 \cos \mathbf{f} + \cos(2\mathbf{w}_{0}t - \mathbf{f} - 4\mathbf{p}/3) \right] - \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t - 2\mathbf{p}/3) &, \mathbf{p} < \mathbf{w}_{0}t < 4\mathbf{p}/3 \end{cases}$$

$$\frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ 2 \cos \mathbf{f} + \cos(2\mathbf{w}_{0}t - \mathbf{f} - 2\mathbf{p}/3) \right] + \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t - 4\mathbf{p}/3) &, 5\mathbf{p}/3 < \mathbf{w}_{0}t < 5\mathbf{p}/3 \end{cases}$$

$$\frac{\sqrt{2}}{2} \hat{d}' I_{s}^{*} \left[ \cos \mathbf{f} - \cos(2\mathbf{w}_{0}t - \mathbf{f} - 2\mathbf{p}/3) \right] + \frac{\sqrt{2}}{3} d_{0}^{'*} I_{s}^{*} \sin(\mathbf{w}_{0}t - 4\mathbf{p}/3) &, 5\mathbf{p}/3 < \mathbf{w}_{0}t < 2\mathbf{p} \end{cases}$$

$$(43)$$

for each  $k \in \{1, 2, 3\}$ . The value of  $v_{M,n}$ , corresponding to each case, is given in Tab.1. After some mathematical developments, we obtain the following condition:

$$L < \min\left(\frac{V_0^* \sqrt{2} - 3V_S^* \sqrt{3}}{6w_0 I_S^*}, \frac{6V_S^* \sqrt{3} - V_0^* \sqrt{2}}{6w_0 I_S^*}\right)$$

(45)

The range of the inductor value L is thus maximized if:

$$V_0^* = \frac{9}{4} V_s^* \sqrt{6} \cong 5.51 V_s^* \tag{46}$$

Furthermore, the inductors are also designed for current ripple limitation. In this perspective, reasoning around the peak value of the line currents yields:

$$L > \frac{1}{f_s \left( \Delta i_s \right)_{\text{max}}} \left( 2 V_s^* \sqrt{2} - \frac{V_0^*}{4} - \frac{6 V_s^{*2}}{V_0^*} \right) \tag{47}$$

where  $f_S$  is the switching frequency and  $(\Delta i_S)_{\text{max}}$  the acceptable current ripple. Finally, the inductors value is chosen accordingly to conditions (45) and (47).

Fig. 3. Line current waveshaping

#### 5.2. Capacitors design

The two DC side capacitors of the converter are designed in the case of a balanced load (i.e.,  $\Delta i_0^* = 0$ ). Referring to the expression (43), the magnitude of the DC side upper current ripple can be obtained as:

$$\left(\hat{\Delta}\hat{i}_{+}^{*}\right) = \frac{V_{S}^{*}I_{S}^{*}}{V_{0}^{*}} \left(\frac{2}{\cos \mathbf{f}} - 1\right) \tag{48}$$

It follows:

$$C_{0} > \frac{2V_{s}^{*} I_{s}^{*}}{3\mathbf{w}_{0} V_{0}^{*} (\Delta v_{0})_{\text{max}}} \left(\frac{2}{\cos \mathbf{f}} - 1\right)$$

(49)

where  $(\Delta v_0)_{max}$  is the admissible output voltage ripple.

#### VI - SIMULATION RESULTS

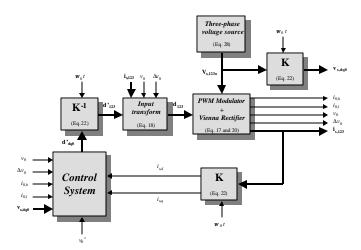

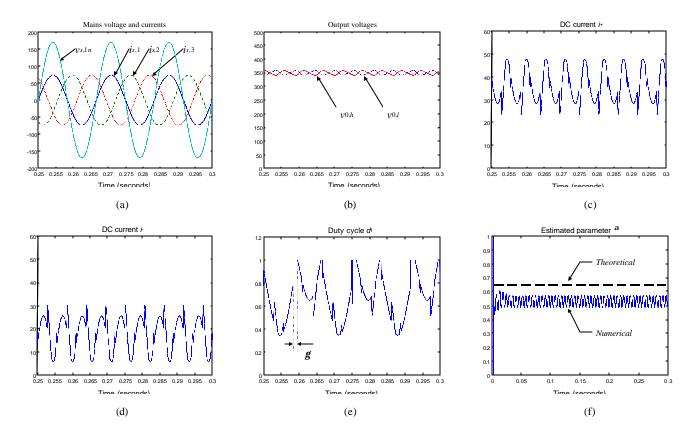

In order to verify the theoretical development in sections III and IV, a simulation work is carried out using Matlab/Simulink tool. A numerical version of the converter in Fig. 1 is implemented in low-frequency domain, as indicated in Fig. 4. The numerical values of the converter parameters and steady-state operating point are given in the appendix. The load is purely resistive. The design of the control system is not presented in this paper. The simulation results are presented in Fig. 5. As shown in Fig. 5.a, the converter operates under a unity power factor condition. Furthermore, as indicated in Fig. 5.b, the upper and lower output voltages are practically equal at  $V_0^*/2$ , with a relatively low voltage ripple, despite the load unbalance. In addition, referring to Fig. 5.c and 5.d, one may easily notice that the DC currents  $i_{+}$  and  $i_{-}$  have practically the shape of two opposite-phase third-harmonic sine waves, as discussed in section IV. Furthermore, the control saturation angle g noticed in Fig. 5.e is equal to 24 degrees and, therefore, satisfies equation (39). Finally, the estimated parameter a, presented in Fig. 5.f, oscillates around 0.53, which is slightly different from the theoretical value given in (26).

Fig. 4. Numerical implementation of the converter

# VII - CONCLUSION

A new low-frequency time-invariant model of a three-phase, three-switch, three-level rectifier has been established in this paper. The steady-state unity power factor operating mode was analyzed, and design criteria concerning the choice of the output voltage and the reactive components were also presented. The proposed modeling approach has been verified numerically using Matlab/Simulink. The model thus obtained would be suitable for control design implementation.

#### **APPENDIX**

Phase-to-neutral voltage RMS-value Overall output voltage Utility frequency Switching frequency Mains series inductors Output capacitors Upper load resistor Lower load resistor

$$V_S^* = 120 \text{ V}$$

$V_0^* = 700 \text{ V}$

$f_0 = 60 \text{ Hz}$

$f_S = 50 \text{ kHz}$

$L = 1 \text{ mH, each}$

$C_0 = 1 \text{ mF, each}$

$R_{0,h} = 9.8 \Omega$

$R_{0,l} = 19.6 \Omega$

[3]

[4]

[5]

### REFERENCES

- [1] J. W. Kolar and H. Ertl, "Status of the techniques of three-phase rectifier systems with low effects on the mains", 21st INTELEC, Copenhagen, Denmark, June 6-9, 1999.

- [2] J. W. Kolar and F. C. Zach, "A novel three-phase utility interface minimizing line current harmonics of high-power telecommunications rectifier modules", IEEE Transactions on Industrial Electronics, vol.44, No.4, pp. 456-467, Aug. 1997.

- J. W. Kolar, F. Stögerer, J. Miniböck and H. Ertl, "A new concept for reconstruction of the input phase currents of a three-phase/switch/level PWM (Vienna) rectifier based on neutral point current measurement", *PESC'2000*, vol.1, pp. 139-146, 2000.

- R. D. Middlebrook and S. Cuk, "A general unified approach to modeling switching-converter power stages", Proceedings of the IEEE Power Electronics Specialists Conf., Cleveland, OH., June 8-10, 1976.

- R. Wu, S. B. Dewan and G. R. Slemon, "Analysis of an ac-to-dc voltage source converter using PWM with phase and amplitude control", *IEEE Transactions on Industry Applications*, vol.27, No.2, pp. 355-364, Mar./Apr. 1991.

Fig. 5. Simulation results for the steady-state regime. a) Mains voltage and currents, b) Upper and lower output voltages, c), d) Upper and lower DC side currents, e) Duty cycle of switch  $Q_1$ , f) Estimated parameter a