# A New Method for Characterizing the Spatial Distributions of Interface States and Oxide-Trapped Charges in LDD n-MOSFET's

Robert Giahn-Horng Lee, Jen-Shien Su, and Steve S. Chung, Senior Member, IEEE

$V_{

m fb,str}$

Abstract—Previous studies showed that simultaneous determination of the interface states  $(N_{\rm it})$  and oxide-trapped charges  $(Q_{\rm ox})$  in the vicinity of the drain side in MOS devices was rather difficult. A new technique which allows a consistent characterization of the spatial distributions of both hot-carrier-induced  $N_{\rm it}$  and  $Q_{\rm ox}$  is presented. Submicron LDD n-MOS devices were tested and charge pumping measurements were performed. The spatial distributions of both  $N_{\rm it}$  and  $Q_{\rm ox}$  have been justified by two-dimensional (2-D) device simulation of the I-V characteristics for devices before and after the stress. Comparison of the drain current characteristics between simulation and experiment shows very good agreement. Moreover, results show that fixed-oxide charge effect is less pronounced to the device degradation for the experimental LDD-type n-MOS devices.

#### NOMENCLATURE

| A, B                | Empirical parameters involved in the $N_{ m it}$ and        |

|---------------------|-------------------------------------------------------------|

|                     | $Q_{\rm ox}$ calculation.                                   |

| $C_{\text{ox}}$     | Gate oxide capacitance per unit area                        |

|                     | $(= \varepsilon_{\rm ox}/t_{\rm ox})$ (F/cm <sup>2</sup> ). |

| $C_{ m ox,cp}$      | Gate oxide capacitance per unit area (F/cm <sup>2</sup> )   |

|                     | by considering the 2-D fringing effect.                     |

| f                   | Frequency of gate pulse (Hz).                               |

| $I_{ m cp}$         | Charge pumping current (A).                                 |

| $I_{\mathrm{cp},d}$ | Charge pumping current flowing between                      |

|                     | drain and substrate (A).                                    |

| $I_{ m cp,vir,max}$ | Maximum charge pumping current before                       |

|                     | stress (A).                                                 |

| $I_D$               | Drain current (A).                                          |

| $L_{ m eff}$        | Effective channel length contributing to                    |

|                     | charge pumping current (cm).                                |

| $L_m$               | Gate mask length (cm).                                      |

| $N_{ m it}$         | Interface state density (1/cm <sup>2</sup> ).               |

| $N_{ m it,vgh}$     | Interface state density derived from                        |

| , 0                 | $I_{\rm cp} - V_{\rm gh} \ (1/{\rm cm}^2).$                 |

| $N_{ m it,vgl}$     | Interface state density derived from                        |

|                     | $I_{\rm cp} - V_{\rm gl}(1/{\rm cm}^2)$ .                   |

| q                   | Magnitude of electronic charge (C).                         |

| $Q_{ m ox}$         | Oxide-trapped charges (C/cm <sup>2</sup> ).                 |

| $t_{ m ox}$         | Gate oxide thickness (cm).                                  |

|                     |                                                             |

Manuscript received January 25, 1995; revised July 24, 1995. The review of this paper was arranged by Associate Editor C.-Y. Lu. This work was supported by the National Science council, Taiwan, R.O.C., under Contract NSC82-0404-E009-134.

The authors are with the Department of Electronic Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. Publisher Item Identifier S 0018-9383(96)00256-0.

|                        | stressed device (V).                                                             |

|------------------------|----------------------------------------------------------------------------------|

| $V_{ m fb,vir}$        | Local flatband voltage distribution for                                          |

| ,                      | fresh device (V).                                                                |

| $V_{ m gh}$            | High level of applied gate pulse string (V).                                     |

| $V_{ m gl}$            | Base level of applied gate pulse string (V).                                     |

| $V_{ m DS}$            | Drain-source bias (V).                                                           |

| $V_{ m GS}$            | Gate-source bias (V).                                                            |

| $V_S$                  | Applied source bias (V).                                                         |

| $V_T$                  | General notation for $V_{T,vir}$ and $V_{T,str}$ (V).                            |

| $V_{T, m str}$         | Local threshold voltage distribution for                                         |

|                        | stressed devices (V).                                                            |

| $V_{T,\mathrm{vir}}$   | Local threshold voltage distribution for                                         |

|                        | fresh devices (V).                                                               |

| W                      | Effective channel width (cm).                                                    |

| $x_1, x_2$             | Boundaries of the damaged region in the                                          |

|                        | channel direction (cm).                                                          |

| $x_{Lc}$               | Center point of the channel (cm).                                                |

| $x_{Ld}$               | End point of $L_{\text{eff}}$ on drain side (cm).                                |

| $x_{Ls}$               | End point of $L_{\rm eff}$ on source side (cm).                                  |

| $arepsilon_{	ext{ox}}$ | Permittivity of gate oxide (F/cm).                                               |

| $\Delta V_{ m fb}$     | Shifts of local flatband voltage before and                                      |

|                        | after stress (i.e., $\Delta V_{\rm fb} = V_{\rm fb,str} - V_{\rm fb,vir}$ ) (V). |

| $\Delta V_T$           | Shifts of local threshold voltage before and                                     |

|                        | after stress (i.e., $\Delta V_T = V_{T,\text{str}} - V_{T,\text{vir}}$ ) (V).    |

|                        |                                                                                  |

General notation for  $V_{\rm fb,vir}$  and  $V_{\rm fb,str}$  (V).

Local flatband voltage distribution for

#### I. INTRODUCTION

HOT carrier effects and the associated device or circuit degradation are increasingly important in VLSI/ULSI reliability issues. This hot-carrier-induced phenomenon constitutes a threat to the long-term reliability of such devices in that the injected carriers may lead to both oxide trapped charges  $(Q_{\rm ox})$  and the formation of interface states  $(N_{\rm it})$  at the Si-SiO<sub>2</sub> interface [1]. These damages may cause gradual aging of device characteristics, such as the threshold voltage shift, transconductance reduction, drain current degradation, etc., [1]-[4].

Recently, the charge pumping (CP) technique [5]–[11] has been proven to be a powerful method for the analysis of the interface properties of the  $Si-SiO_2$  system. So far, however, it has not been simple to form a definite picture of the lateral

distributions of  $N_{\rm it}$  and  $Q_{\rm ox}$  along the channel from a variety of experimental techniques and results.

In order to determine the  $N_{it}$  and  $Q_{ox}$ , one may vary the reverse source/drain biases to modulate the junction depletion layer edges (change with the so-called body effect) such that the spatial distributions of  $N_{\rm it}$  and  $Q_{\rm ox}$  can be determined [12], [13]. Nevertheless, the assumption used in [12], [13] that  $V_T(x)$  and  $V_{\rm fb}(x)$  distributions do not change with applied source/drain biases is not in accordance with reality and such variations will affect the occupancy of monitored interface states [10]. To circumvent the aforementioned problem, a new measurement set-up for CP currents-constant field approach, has been proposed by Ancona et al. [7] and applied well to MOSFET's by Chen et al. [10]. However, it should be noted that the presence of  $Q_{ox}$ , which has not been taken into account as yet for determining the depletion edge, will affect the  $V_T(x)$  and  $V_{fb}(x)$  distributions as well. Although it can be reflected in the change of the derivative of  $I_{cp}$  curve [14], usually such variation is a very insensitive parameter. As a consequence, the algorithm for calculating  $N_{\rm it}$  and  $Q_{\rm ox}$  which is not self-consistent, makes it questionable whether such additional effort is justified, as the authors pointed out [10].

In this paper, a new characterization technique which allows the simultaneous characterization of the distributions of both  $N_{\rm it}$  and  $Q_{\rm ox}$  will be presented. It was calculated based on a conventional charge pumping measurement and a characterization algorithm. In the charge pumping measurement, a fixed base (high) level with varying high (base) level gate pulses is used while the source and drain are biased at zero volts such that high reverse bias, as in [10], can be avoided. For detailed illustration and experimental verification, we will apply this new technique to LDD n-MOSFET's. Finally, these extracted  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  will be implemented using 2-D device simulation to justify the validity of the proposed method.

#### II. DEVICE PREPARATION

The experimental LDD n-MOSFET's used in this work were fabricated using a standard poly-Si gate twin-well CMOS process. The tested samples have 0.7  $\mu m$  mask gate length and 20  $\mu m$  channel width. The gate oxide thickness is 14 nm and the sidewall spacer is 0.15  $\mu m$ . The LDD n $^-$  region is performed by Phosphorous implant with dosage of  $2\times 10^{13}$  cm $^{-2}$  and energy 80 kev. The channel profile and source/drain profile have been calibrated against SIMS data.

#### III. DESCRIPTION OF THE NEW METHOD

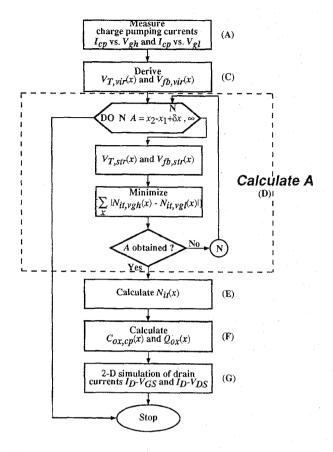

In this section, we will first present the experimental setup of the charge pumping measurement and then propose a new method to determine the spatial distributions of the channel-hot-carrier induced  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  from the measured data. The goal of this work is to obtain these information with the aid of numerical calculations that can be easily programmed into an existing simulation framework, while with less measurement efforts. The extraction procedure used to characterize the damage profiles is shown by the flow diagram in Fig. 1.

Fig. 1. Procedure of the proposed new technique to characterize  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$ . Inside each parentheses is the subsection character. Detailed descriptions will be presented in each of these subsections.

There are five major steps involved in this extraction algorithm.

- Step 1: Measure charge pumping currents  $I_{\rm cp}$  for the tested device before and after the stress.

- Step 2: Derive local threshold  $V_{T, vir(x)}$  and flatband voltages  $V_{\mathrm{fb,vir}}(x)$  of fresh devices from the measured  $I_{\mathrm{cp}}$ 's before stress in Step 1.

- Step 3: Determine the local threshold  $V_{T,\rm str}(x) = V_{T,\rm vir}(x) + \Delta V_T(x)$  and flatband voltages  $V_{\rm fb,str}(x) = V_{\rm fb,vir}(x) + \Delta V_{\rm fb}(x)$  of stressed devices from the measured  $I_{\rm cp}$ 's in Step 1, and then determine the shifts of local threshold  $\Delta V_T(x)$  and flatband  $\Delta V_{\rm fb}(x)$  voltages after the stress.

- Step 4: Calculate  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  based on the results in Step 3.

- Step 5: Compare the simulated I-V characteristics with the measurements after hot-carrier stress.

To illustrate this scheme, a step-by-step procedure will be described in more detail as follows.

### A. Experimental Setup and Measured Charge Pumping Current

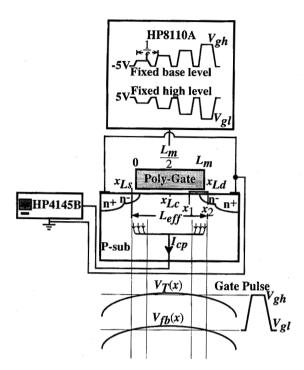

The basic setup for charge pumping measurement along with appropriate notations is shown schematically in Fig. 2. The gate of an LDD n-MOSFET device under test is connected to

Fig. 2. Basic experimental setup for charge pumping measurement, schematic diagram of an LDD MOSFET cross section and the corresponding notations.

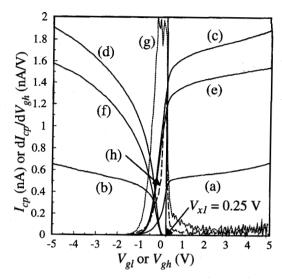

a pulse generator (HP8110A) while the drain and source are biased at ground voltage. Two kinds of 1-MHz pulse strings with rising/falling gradient of 25 ns/V are used in our CP measurements [11]. First, we use fixed base level,  $V_{\rm gl}$  at -5 V, and sweep  $V_{\mathrm{gh}}$ , then in the same way use fixed high level,  $V_{\mathrm{gh}}$ at +5 V, and sweep  $V_{\rm gl}$  ( $V_{\rm gh}$  and  $V_{\rm gl}$  are varied between -5 and +5 V) to measure CP currents for fresh (i.e., "virgin") and stressed LDD n-MOSFET's. The CP currents were measured after a channel-hot-carrier stress at  $V_{GS} = 3$  V and  $V_{DS} = 7$ V for  $10^4$  s. Fig. 3 shows the measured CP currents  $I_{\rm cp} - V_{\rm gh}$ and  $I_{\rm cp}-V_{\rm gl}$  for fresh and stressed devices. Since the local threshold voltage and local flatband voltage are not laterally uniform due to the variation of doping profile, for a certain  $V_{\rm gh}$  $(V_{\rm gl})$  value, only the interface states situated in the region, where the criteria of  $V_{\rm gh} > V_T(x)$  and  $V_{\rm gl} < V_{\rm fb}(x)$  are met as shown in Fig. 2, can be detected and contribute to charge pumping current. As a result, when  $V_{\rm gh}$  ( $V_{\rm gl}$ ) exceeds the maximum (minimum) local threshold (flatband) voltage eventually, the whole detected region is covered, and then the  $I_{

m cp}$  will become saturated at high  $V_{

m gh}$   $(V_{

m gl})$  values.

# B. Formulation of $I_{\rm cp}$ Versus $V_{\rm gh}$ or $V_{\rm gl}$ Relationship

Since the magnitude of  $I_{\rm cp}$  is a measure of the total amount of interface states, based on [5], [10]  $I_{\rm cp}$  versus  $V_{\rm gh}$  curve after the stress can be expressed by

$$I_{\rm cp}(V_{\rm gh}) = qWf \int_{x_{Ls}}^{x_{Ld}} N_{\rm it,vgh}(x) u[V_{\rm gh} - V_{T,\rm str}(x)] dx$$

Fig. 3. (a)  $I_{\rm cp}$  versus  $V_{\rm gh}$  (fresh), (b)  $I_{\rm cp}$  versus  $V_{\rm gl}$  (fresh), (c)  $I_{\rm cp}$  versus  $V_{\rm gh}$  (stressed), (d)  $I_{\rm cp}$  versus  $V_{\rm gl}$  (stressed), (e)  $I_{\rm cp,d}$  versus  $V_{\rm gh}$  (stressed) and (f)  $I_{\rm cp,d}$  versus  $V_{\rm gl}$  (stressed) curves of a W/Lm (= 20  $\mu$ m/0.7  $\mu$ m) LDD n-MOSFET's with stress condition at  $V_{\rm DS}=7$  V and  $V_{\rm GS}=3$  V, measured at zero drain/source bias. (g) and (h) are the derivatives of curves (c) and (a), respectively.

$$= qWf \int_{x_{Ls}}^{x_{Ld}} N_{\text{it,vgh}}(x)$$

$$\times u \left[ V_{\text{gh}} - V_{T,\text{vir}}(x) + \frac{Q_{\text{ox}}(x)}{C_{\text{ox,cp}}(x)} \right] dx. \quad (1b)$$

Similarly, for the  $I_{\rm cp}$  versus  $V_{\rm gl}$  relationship after the stress, we have

$$I_{cp}(V_{gl}) = qWf \int_{x_{Ls}}^{x_{Ld}} N_{it,vgl}(x)u[V_{fb,str}(x) - V_{gl}]dx$$

$$= qWf \int_{x_{Ls}}^{x_{Ld}} N_{it,vgl}(x)$$

$$\times u \left[V_{fb,vir}(x) - \frac{Q_{ox}(x)}{C_{ox,cp}(x)} - V_{gh}\right]dx$$

$$u \left[ \cdots \right] \text{ is a function}$$

(2b)

with u defined by a step function

$$u(f(x)) = \begin{cases} 0, & f(x) < 0\\ 1, & f(x) \ge 0 \end{cases}$$

(3)

where

$$V_{T,\text{str}}(x) = V_{T,\text{vir}}(x) - \frac{Q_{\text{ox}}(x)}{C_{\text{ox,cp}}(x)}$$

(4)

and

$$V_{\rm fb,str}(x) = V_{\rm fb,vir}(x) - \frac{Q_{\rm ox}(x)}{C_{\rm ox,cp}(x)}.$$

(5)

In (4) and (5), we make the implicit assumption that  $\Delta V_T(x) (= V_{T,\mathrm{str}}(x) - V_{T,\mathrm{vir}(x)})$  at a position x along the channel is the same as  $\Delta V_{\mathrm{fb}}(x) (= V_{\mathrm{fb,str}}(x) - V_{\mathrm{fb,vir}}(x))$  during CP measurements. This can be justified from device simulation, in which we put several different values of  $Q_{\mathrm{ox}}$

in the simulator and we see that  $\Delta V_T(x)$  and  $\Delta V_{\rm fb}(x)$  are approximately equal. In addition, to first-order approximation the influence of  $N_{\rm it}$  has the same effect on  $\Delta V_T$  and  $\Delta V_{\rm fb}$  (refer to Fig. 10 of [13]). From (1) and (2), we can see that there are two unknown variables  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  of interest in these two equations. Therefore,  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  can be calculated numerically by solving the above two equations iteratively until the convergence is achieved. However, this self-consistent calculation for  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  usually requires a huge computing time. For the purpose of easy computation, we use a very unique way to find the solutions in the following subsections.

# C. Derivation of Local Threshold $V_{T,vir(x)}$ and Flatband $V_{fb,vir}(x)$ Voltages of Fresh Devices

By assuming symmetrically identical nature of the source and drain sides and the uniform interface state distribution for the tested devices before the stress, the local threshold  $V_{T,\mathrm{vir}(x)}$  and flatband  $V_{\mathrm{fb,vir}}(x)$  voltages can be obtained from the CP currents  $I_{\mathrm{cp}} - V_{\mathrm{gh}}$  and  $I_{\mathrm{cp}} - V_{\mathrm{gl}}$ , respectively, and represented by the following expressions [11]:

1) For the local threshold voltage  $V_{T,vir(x)}$  of fresh devices

$$V_{T, \text{vir}}(x) = V_{gh}$$

and

$$x(V_{\rm gh}) = x_{Lc} + \left(1 - \frac{I_{\rm cp}(V_{\rm gh})}{I_{\rm cp,vir,max}}\right) \cdot (x_{Ld} - x_{Lc}). \quad (6)$$

2) For the local flatband voltage  $V_{\rm fb,vir}(x)$  of fresh devices

$$V_{\text{fb,vir}}(x) = V_{\text{gl}}$$

and

$$x(V_{\rm gl}) = x_{Lc} + \frac{I_{\rm cp}(V_{\rm gl})}{I_{\rm cp,vir,max}} \cdot (x_{Ld} - x_{Lc}).$$

(7)

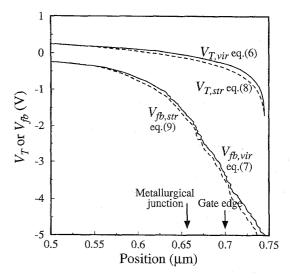

Here, the channel end point on drain side  $x_{Ld}$ , that can be detected with charge pumping method, is determined by simulating the majority-carrier concentrations to define the effective channel length  $L_{\rm eff}$  which contributes to the charge pumping current [6], [13], while the center point of the channel  $x_{Lc}$  depends on the gate mask length. In this case, MINIMOS 4 is used to calculate the majority-carrier distribution. The channel end point on drain side  $x_{Ld}$  was at 0.745  $\mu$ m while  $V_{\rm gl}$  was held at -5 V. The center point of the channel  $x_{Lc}$  was 0.35 mm. From (6) and (7), we can directly obtain the local threshold  $V_{T,{\rm vir}(x)}$  and flatband  $V_{\rm fb,vir}(x)$  voltage distributions of fresh devices as shown with solid lines along the channel in Fig. 4.

# D. Determination of the Local Threshold $V_{T,str}(x)$ and Flatband $V_{fb,str}(x)$ Voltages for Stressed Devices

First of all, we assume the two channel-hot-carrier induced  $V_{T,\rm str}(x)$  and  $V_{\rm fb,str}(x)$ , can be empirically formulated as (8) and (9), for the damaged region near the drain side, while

Fig. 4. Local threshold  $V_T(x)$  and flatband  $V_{\rm fb}(x)$  voltage distributions along channel before and after the stress.

$V_{T,\text{str}}(x)$  in the undamaged region remains unchanged as  $V_{T,\text{vir}(x)}$  (refer to Fig. 18 of [11]).

$$V_{T,\text{str}}(x) = \begin{cases} B \cdot \ln\left(1 - \frac{x - x_1}{A}\right) + V_{T,\text{vir}}(x_1) & x_1 \le x \le x_2 \\ V_{T,\text{vir}}(x) & 0 < x < x_1 \text{ or } x_2 < x \end{cases}$$

(8)

where

$$B = \frac{V_{T,\text{vir}}(x_2) - V_{T,\text{vir}}(x_1)}{\ln(1 - \frac{x_2 - x_1}{4})}$$

and

$$V_{\text{fb,str}}(x) = V_{\text{fb,vir}}(x) + (V_{T,\text{str}}(x) - V_{T,\text{vir}}(x)). \tag{9}$$

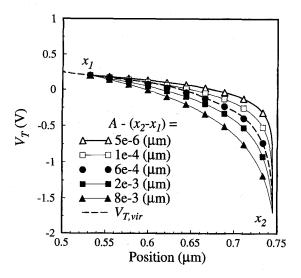

Here,  $x_1$  and  $x_2$  are the boundaries of the oxide damaged region. In the above  $V_{T,\mathrm{str}}(x)$  formula, A is the only unknown variable to be determined. It should be noted that all the probable values of A are located between  $x_2-x_1+\delta x$  and  $\infty$  (this can be seen from (8)). Fig. 5 shows the calculated  $V_{T,\mathrm{str}}(x)$  distributions from (8) with different values of A's for demonstration. In this figure, it illustrates that if the  $V_{T,\mathrm{str}}(x)$  curve is above the  $V_{T,\mathrm{vir}(x)}$  curve, it corresponds to negative charges (electrons) being injected into the oxide which contributes to the rising of threshold and flatband voltages after the stress. In contrast,  $V_{T,\mathrm{str}}(x)$  below  $V_{T,\mathrm{vir}(x)}$ , shows the presence of positive charges (holes).

Before determining the value of A, we should first introduce the derivation  $N_{\rm it,vgh}(x)$  and  $N_{\rm it,vgh}(x)$  from  $I_{\rm cp}-V_{\rm gh}$  (i.e., from (1)) and  $I_{\rm cp}-V_{\rm gl}$  (i.e., from (2)) curves, respectively, by assuming both  $V_{T,\rm str}(x)$  and  $V_{\rm fb,str}(x)$  are given. A detailed description of  $N_{\rm it}(x)$  ( $N_{\rm it,vgh}(x)$  and  $N_{\rm it,vgl}(x)$ ) derivation that incorporates the *optimization technique* is given in the Appendix.

Next, we want to determine the value of A in the following so that it can predict  $Q_{ox}(x)$  from  $V_{T,str}(x)$  (i.e.,  $Q_{ox}(x)$  will

Fig. 5. Calculated  $V_{T,\mathrm{str}}(x)$  distributions with various given values of A's for illustration. Here,  $V_{T,\mathrm{str}}(x)$  is empirically expressed by (8).

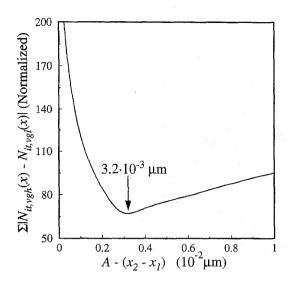

be determined whenever A is known). So far, there are still infinite probable sets of  $N_{\rm it,vgh}(x)$  and  $N_{\rm it,vgl}(x)$  in that A has not yet been determined. However, based on the fact that no test device has two different  $N_{\rm it}(x)$  configurations at a certain point of time, we can confirm that, despite the errors/noise during measurements,  $N_{\rm it,vgh}(x)$  should be completely the same as  $N_{\rm it,vgl}(x)$  in principle. In numerical calculation, it means that the sum of differences between both  $N_{\rm it,vgh}(x)$  and  $N_{\rm it,vgl}(x)$ , as derived in the Appendix, should be minimized (i.e., among all the probable A's, only one value, substituted into (A.1) and (A.2), can meet the criteria). Thus, the unique value A can be determined by minimizing the following expression:

$$\min \left[ \sum_{x} |N_{\rm it,vgh}(x) - N_{\rm it,vgl}(x)| \right]. \tag{10}$$

Here, we can easily use a DO-loop statement in the program to calculate the minimum of (10), in which A is the DO variable and the initial value is  $x_2-x_1+\delta x$ . It is noted that in principle the terminal value of A is  $\infty$  as described previously. However, the terminal and increment values should be appropriately chosen, in such a way that A can be obtained without difficulty. As long as A has been determined from the above algorithm,  $V_{T,\text{str}}(x)$  distribution can thus be obtained from (8). Results of  $V_{T,\text{str}}(x)$  and  $V_{\text{fb,str}}(x)$  for stressed devices using the obtained A value are shown with dashed lines in Fig. 4.

## E. Determination of the Interface State Distribution

Once we have the values of  $V_{T,\text{str}}(x)$ , the coefficients of  $T_0, T_1, \cdots T_n$  in (A.6) can be calculated. Solving (A.11), we can obtain the solutions of  $a_0, a_1, \cdots a_n$ . Finally, the lateral distribution of  $N_{\text{it}}(x)$  can be determined by (A.3).

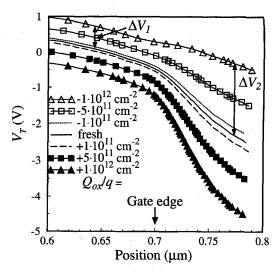

Fig. 6. Local threshold voltage distributions  $V_T(x)$  (defined in [13]) with various uniform oxide charge profiles, simulated with MINIMOS 4. Significant differences in the shifts of  $V_T(x)$  inside and outside gate edge are observed.

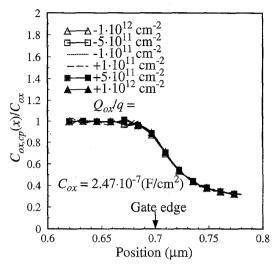

# F. Determination of the Fixed Oxide Charges by Incorporating 2-D Fringing Effect

Usually, the ratio of  $\Delta V_T(x)$  and  $Q_{\rm ox}(x)$  can be regarded as a linear constant  $C_{\rm ox}(=\varepsilon_{\rm ox}/t_{\rm ox})$ , gate oxide capacitance per unit area for convenience. This assumption holds only if the carriers injected into the oxide are strongly located under the gate channel region as in most conventional MOSFET cases. But for LDD or LDD-like MOSFET's, the vast majority of injected carriers reside beyond (or outside) the active channel region (especially, under the n- region). If we still use the constant  $C_{ox}$  to calculate  $Q_{ox}(x)$  without considering capacitive fringing effect for gate oxide [10], [11], this will induce serious errors due to the two-dimensional field induced fringing effect at the gate edge. To consider this 2-D effect, we may calculate a nonlinear capacitance  $C_{\text{ox,cp}}(x)$  using device simulation. First, we calculate the local threshold voltage distributions as in Fig. 6 for several cases with given uniform oxide charge distribution  $Q_{\rm ox}$  covering electron and hole injections. Here, it can be seen that for the same amount of induced  $Q_{\rm ox}$ ,  $\Delta V_T(x)$  is not a constant value, but depends on position (i.e.,  $\Delta V_{T1} \neq \Delta V_{T2}$  as shown in Fig. 6. While without the 2-D effect,  $\Delta V_{T1}$  should be equal to  $\Delta V_{T2}$ ). Given the above,  $C_{

m ox,cp}(x)$  can be estimated according to

$$C_{\rm ox,cp}(x) \equiv \frac{-Q_{\rm ox}}{\Delta V_T(x)}.$$

(11)

The value of  $C_{\rm ox,cp}(x)$  is maximum with  $C_{\rm ox}(=\varepsilon_{\rm ox}/t_{\rm ox})$  in the middle of the gate and decreases gradually toward a much lower value outside the gate edge due to the fringing effect. The results are given in Fig. 7.

By incorporating this 2-D capacitive fringing effect, and then calculating the differences of local threshold voltage  $\Delta V_T(x)$  from Subsection III-D, one can readily obtain the lateral distribution of oxide-trapped charges  $Q_{\rm ox}(x)$  as follows:

$$Q_{\text{ox}}(x) = -C_{\text{ox,cp}}(x) \cdot (V_{T,\text{str}}(x) - V_{T,\text{vir}}(x)). \tag{12}$$

Fig. 7. Calculated local gate-oxide capacitance  $C_{

m ox,cp}$  (normalized) with 2-D fringing effect considered.

#### G. Verification of the Drain Currents by Simulation

To verify the validity of the characterized  $Q_{\rm ox}(x)$  and  $N_{\rm it}(x)$ , device simulator MINIMOS 4 has also been modified so as to incorporate nonuniform  $Q_{\rm ox}(x)$  and  $N_{\rm it}(x)$  distributions. In this simulation, the drain current characteristics of  $I_D-V_{\rm GS}$ , and  $I_D-V_{\rm DS}$  both in normal and reverse modes are simulated and for comparison with experimental results.

#### IV. RESULTS AND DISCUSSIONS

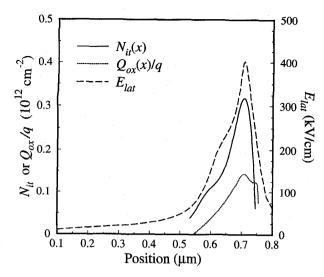

Usually, the range of hot-carrier-induced damaged region is about 0.2 µm and the damage profile is also well correlated with the lateral electric field peak as in [7]. Therefore, it should be noted that both  $x_1$  and  $x_2$  in (8) should be adequately chosen. Here, we let  $x_2 = x_{Ld} = 0.745 \ \mu \text{m}$  (obtained in Section III-C). As for  $x_1$ , it is easy to infer from the principle of charge pumping that the portion of the curves of the  $dI_{\rm cp}/dV_{\rm gh}$  characteristics before and after stress (curves g) should coincide with each other and give the value  $V_{x1}$ , as illustrated in Fig. 3. Thus,  $x_1$  can be obtained by substituting the value of  $V_{x1}$  (as shown in the figure) into (6). In this case,  $V_{x1} = 0.25 \text{ V}$  and  $x_1 = 0.5 \mu\text{m}$ . Values of the optimized A and B are determined from (10). The result is illustrated in Fig. 8, in which  $A - (x_2 - x_1)$  is  $3.2 \times 10^{-3}$   $\mu$ m. As soon as A is determined,  $V_{T,\mathrm{str}}(x)$  and flatband  $V_{\mathrm{fb,str}}(x)$  can be calculated from (8) and (9) as shown in Fig. 4 for comparison. Fig. 9 shows the characterized spatial distributions of  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  from (A.3) and (12), respectively. Shown in the figure is also the lateral electric field which is peaked at the position close to the drain. It further shows that the lateral electric field is closely correlated with the oxide damaged region where  $N_{\rm it}$ and  $Q_{

m ox}$  are generated. By comparing the values of  $N_{

m it}$  and  $Q_{\rm ox}$ , it shows that fixed-oxide charge effect is less pronounced to the device degradation in LDD-type n-MOS devices.

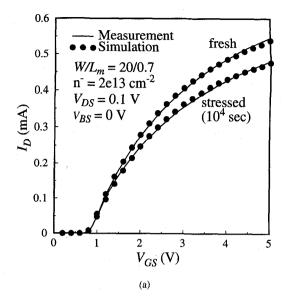

The simulated drain current characteristics  $I_D-V_{\rm GS}$  and  $I_D-V_{\rm DS}$  for both fresh and stressed devices are shown in

Fig. 8. Calculation of the minimum values of (10) for A.

Fig. 10(a) and (b), respectively. Comparison between simulation and experimental results shows very good agreements which also justifies the validity of the extracted  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  distributions.

The advantages of the present method are as follows:

- 1) In this experiment, we can easily obtain the lateral distributions of the induced  $N_{\rm it}$  and  $Q_{\rm ox}$  along the channel merely from one set of CP currents, both  $I_{\rm cp}-V_{\rm gh}$  and  $I_{\rm cp}-V_{\rm gl}$  curves, measured at zero drain/source bias. On one hand, because the drain and source are held constant at zero, this method can avoid the variations of  $V_T(x)$  and  $V_{\rm fb}(x)$  during the inversion and accumulation half cycles. On the other hand, it does not need multiple CP measurements, and hence avoids the likely imposition of re-stress on tested devices.

- 2) Since the variations of the induced  $Q_{\rm ox}$  are taken into account in the calculation of  $N_{\rm it}$  as in (1) and (2), the inconsistency in determining the lateral position of the depletion edge [10] can thus be eliminated in our new method.

- 3) By incorporating 2-D capacitive fringing effect (nonlinear property of oxide capacitance) in calculating  $Q_{\rm ox}(x)$ , overestimation can be eliminated in that  $C_{\rm ox}$  is significantly larger  $C_{\rm ox,cp}(x)$ , especially beyond the gate edge.

- 4) The present method can be applied to LDD MOS devices without difficulty while most of the previous studies [7], [10] are valid only for conventional MOS devices.

## V. CONCLUSION

In this paper, the charge pumping technique has been successfully applied to the characterization of stressed n-channel LDD MOSFET devices. In particular, a new method has been developed for a consistent determination of the lateral distributions of both interface states and oxide-trapped charges.

Fig. 9. Lateral distributions of  $N_{

m it}(x)$ ,  $Q_{

m ox}(x)$  and lateral electric field at  $V_{

m DS}=7$  V and  $V_{

m GS}=3$  V.

By incorporating the spatial distributions of  $N_{\rm it}(x)$  and  $Q_{\rm ox}(x)$  into 2-D device simulator, predictions of I-V characteristics for degraded devices can be accurately made. The simulation results have justified the validity of the proposed technique. It shows that our method can probe the hot-electroninduced oxide damage distribution with less measurements and greater precision. The developed result is expected to be useful for hot carrier reliability and performance studies of submicron or deep-submicron MOS devices.

#### APPENDIX

# NUMERICAL SOLUTION OF INTERFACE STATES $N_{\rm it}(x)$

In this appendix, we will describe the numerical solution of interface state distribution. By assuming that source and drain are symmetrical for fresh devices and damages are induced only near the drain side, the drain component  $I_{\rm cp,d}(=I_{\rm cp}~({\rm stressed})~-I_{\rm cp}~({\rm fresh})/2)$  of CP current that flowing between drain and substrate can be shown as follows (from (3) and (4)):

$$I_{\text{cp},d}(V_{\text{gh}}) = qWf \int_{x_{Lc}}^{x_{Ld}} N_{\text{it,vgh}}(x) u[V_{\text{gh}} - V_{T,\text{str}}(x)] dx$$

(A.1)

and

$$I_{\text{cp},d}(V_{\text{gl}}) = qWf \int_{x_{Lc}}^{x_{Ld}} N_{\text{it,vgl}}(x) u[V_{\text{fb,str}}(x) - V_{\text{gh}}] dx.$$

(A.2)

To obtain the spatial profiles of  $N_{\rm it,vgh}(x)$  and  $N_{\rm it,vgl}(x)$  (we will concentrate on the derivation of  $N_{\rm it,vgh}(x)$  in the following.  $N_{\rm it,vgl}(x)$  can be obtained in the same way) near

Fig. 10. (a) Comparison of the experimental and simulated  $I_D$  characteristics for fresh and stressed devices. (b) Comparison of the experimental and simulated  $I_D$  characteristics for fresh and stressed devices. The results for fresh characteristics are denoted by  $(\bullet)$  and the results for stressed forward  $(\Box)$  and reverse  $(\phi)$  characteristics are also shown.

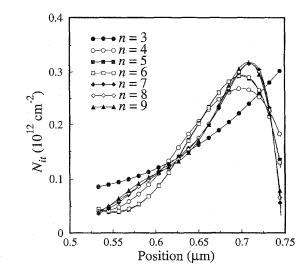

the drain junction, we assume the functional relationship (n can be chosen according to accuracy requirement)

$$N_{\text{it,vgh}}(x) = a_0 + a_1 x + a_2 x^2 + \dots + a_n x^n$$

(A.3)

with errors defined by (A.4), shown at the bottom of the page, where  $I_{\text{cp},d}(V_{\text{gh}})$  is the measured current at a specified  $V_{\text{gh}}$  and  $N_{\text{it,vgl}}(x)$  given by (A.3). We want to minimize the sum

$$E(V_{\rm gh}) = I_{\rm cp,d}(V_{\rm gh}) - qWf \int_{x_{Le}}^{x_{Ld}} N_{\rm it,vgh}(x) u[V_{\rm gh} - V_{T,\rm str}(x)] dx$$

(A.4)

Fig. 11. Calculation of  $N_{\rm it}(x)$  with various n's from (A.3).

of error squares

$$S = \sum_{V_{gh}} E(V_{gh})^2 = \sum_{V_{gh}} \left\{ I_{cp,d}(V_{gh}) - qWf \int_{x_{Lc}}^{x_{Ld}} N_{it,vgh}(x) u[V_{gh} - V_{T,str}(x)] dx \right\}^2.$$

(A.5)

For convenience, we let

$$T_{0} = \int_{x_{Lc}}^{x_{Ld}} u[V_{gh} - V_{T,str}(x)] dx, \qquad (A.6.0)$$

$$T_{1} = \int_{x_{Lc}}^{x_{Ld}} x^{1} u[V_{gh} - V_{T,str}(x)] dx \qquad (A.6.1)$$

and

$$T_n = \int_{x_{L,0}}^{x_{L,0}} x^n u [V_{gh} - V_{T,str}(x)] dx.$$

(A.6.n)

Then, (A.5) can be rewritten as

$$S = \sum_{V_{gh}} \{ I_{cp,d}(V_{gh}) - qWf[a_0T_0 + a_1T_1 + \dots + a_nT_n] \}^2.$$

To find the minimum value of S, all the partial derivatives should be zero, i.e.,

$$\frac{\partial S}{\partial a_0} = \frac{\partial S}{\partial a_1} = \dots = \frac{\partial S}{\partial a_n} = 0.$$

(A.8)

Writing the equations for these gives n+1 equations

$$\begin{split} \frac{\partial S}{\partial a_0} &= \sum_{V_{\rm gh}} (-2qWf) [I_{{\rm cp},d}(V_{\rm gh}) \\ &- qWf(a_0T_0 + a_1T_1 + \dots + a_nT_n)] T_0 = 0 \\ \frac{\partial S}{\partial a_1} &= \sum_{V_{\rm gh}} (-2qWf) [I_{{\rm cp},d}(V_{\rm gh}) \\ &- qWf(a_0T_0 + a_1T_1 + \dots + a_nT_n)] T_1 = 0 \\ &\vdots \\ \end{split} \tag{A.9.1}$$

and

$$\frac{\partial S}{\partial a_n} = \sum_{V_{gh}} (-2qWf)[I_{cp,d}(V_{gh}) - qWf(a_0T_0 + a_1T_1 + \dots + a_nT_n)]T_n = 0.$$

(A.9.n)

Dividing each by -2qWf and rearranging gives the n+1 normal equations to be solved simultaneously

$$a_{0} \sum_{V_{gh}} T_{0}^{2} + a_{1} \sum_{V_{gh}} T_{0}T_{1} + \dots + a_{n} \sum_{V_{gh}} T_{0}T_{n}$$

$$= \frac{1}{qWf} \sum_{V_{gh}} I_{cp,d}(V_{gh})T_{0}, \qquad (A.10.0)$$

$$a_{0} \sum_{V_{gh}} T_{1}T_{0} + a_{1} \sum_{V_{gh}} T_{1}^{2} + \dots + a_{n} \sum_{V_{gh}} T_{1}T_{n}$$

$$= \frac{1}{qWf} \sum_{V_{gh}} I_{cp,d}(V_{gh})T_{1}, \qquad (A.10.1)$$

$$\vdots$$

and

$$a_0 \sum_{V_{gh}} T_n T_0 + a_1 \sum_{V_{gh}} T_n T_1 + \dots + a_n \sum_{V_{gh}} T_n^2$$

$$= \frac{1}{qWf} \sum_{V_{gh}} I_{cp,d}(V_{gh}) T_n. \tag{A.10.n}$$

These equations can be rearranged in matrix form as follows:

$$\left[ \begin{array}{ccccc} \sum_{V_{\mathrm{gh}}} T_0^2 & \sum_{V_{\mathrm{gh}}} T_0 t_1 & \cdots & \sum_{V_{\mathrm{gh}}} T_0 T_n \\ \sum_{V_{\mathrm{gh}}} T_1 T_0 & \sum_{V_{\mathrm{gh}}} T_1^2 & \cdots & \sum_{V_{\mathrm{gh}}} T_1 T_n \\ \vdots & \vdots & \cdots & \vdots \\ \sum_{V_{\mathrm{gh}}} T_n T_0 & \sum_{V_{\mathrm{gh}}} T_n T_1 & \cdots & \sum_{V_{\mathrm{gh}}} T_n^2 \end{array} \right] \left[ \begin{array}{c} a_0 \\ a_1 \\ \vdots \\ a_n \end{array} \right]$$

$$= \frac{1}{qWf} \begin{bmatrix} \sum_{V_{\rm gh}} I_{\rm cp,d}(V_{\rm gh}) T_0 \\ \sum_{V_{\rm gh}} I_{\rm cp,d}(V_{\rm gh}) T_1 \\ \vdots \\ \sum_{V_{\rm gh}} I_{\rm cp,d}(V_{\rm gh}) T_n \end{bmatrix}. \tag{A.11}$$

The solutions of the above equations gives  $a_0, a_1, a_2, \cdots a_n$ . Therefore,  $N_{\rm it,vgh}(x)$  can be calculated from (A.3). The comparison of calculated  $N_{\rm it}$  for various n are shown in Fig. 11, in which n is chosen to be 7 for accuracy and numerical efficiency in this experiment.

#### REFERENCES

- [1] K. R. Hofmann, C. Werner, W. Weber, and G. Dorda, "Hot-electron and hole-emission effects in short n-channel MOSFET's," *IEEE Trans. Electron Devices*, vol. ED-32, p. 691, 1985.

- [2] C. Hu, S. C. Tam, F. C. Hsu, P. K. Ko, T. Y. Chan, and K. W. Terrill, "Hot-electron-induced MOSFET degradation—Model, monitor, and improvement," *IEEE Trans. Electron Devices*, vol. ED-32, p. 375, 1985

- [3] K. K. Ng and G. W. Taylor, "Effects of hot-carrier trapping in n- and p-channel MOSFET's," *IEEE Trans. Electron Devices*, vol. ED-30, p. 871, 1983.

- [4] P. Heremans, R. Bellens, G. Groeseneken, and H. E. Maes, "Consistent model for the hot-carrier degradation in n-channel and p-channel MOSFET's," *IEEE Trans. Electron Devices*, vol. 35, p. 2194, 1988.

- [5] J. S. Brugler and P. G. A. Jespers, "Charge pumping in MOS devices," IEEE Trans. Electron Devices, vol. ED-16, p. 297, 1969.

- [6] G. Groeseneken, H. E. Maes, N. Bertran, and R. F. De Keersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," *IEEE Trans. Electron Devices*, vol. ED-31, p. 42, 1984.

- [7] M. G. Ancona, N. S. Saks, and D. McCarthy, "Lateral distribution of hot-carrier-induced interface traps in MOSFET's," *IEEE Trans. Electron Devices*, vol. 35, p. 2221, 1988.

- [8] B. Doyle, M. Bourcerie, J. C. Marchetaux, and A. Boudou, "Interface state creation and charge trapping in the medium-to-high gate voltage range (V<sub>d</sub>/2 ≥ V<sub>g</sub> ≥ V<sub>d</sub>) during hot-carrier stressing of n-MOS transistors," *IEEE Trans. Electron Devices*, vol. 37, p. 744, 1990.

- [9] P. Habas and S. Selberherr, "A closed-loop extraction of the spatial distribution of interface traps based on numerical model of the chargepumping experiment," in *Proc. Solid State Devices and Materials Conf.*, 1992, p. 170.

- [10] W. Chen, A. Balasinski, and T.-P. Ma, "Lateral profiling of oxide charge and interface traps near MOSFET junctions," *IEEE Trans. Electron Devices*, vol. 40, p. 187, 1993.

- [11] M. Tsuchiaki, H. Hara, T. Morimoto, and H. Iwai, "A new charge pumping method for determining the spatial distribution of hot-carrierinduced fixed charge in p-MOSFET's," *IEEE Trans. Electron Devices*, vol. 40, p. 1768, 1993.

- [12] A. B. M. Elliot, "The use of charge pumping currents to measure surface state densities in MOS transistors," *Solid-State Electron.*, vol. 19, p. 241, 1976.

- [13] P. Heremans, J. Witters, G. Groeseneken, and H. E. Maes, "Analysis of the charge pumping technique and its application for the evaluation of MOSFET degradation," *IEEE Trans. Electron Devices*, vol. 36, p. 1318, 1989.

- [14] W. Chen and T.-P. Ma, "A new technique for measuring lateral distribution of oxide charge and interface traps near MOSFET junctions," IEEE Electron Device Lett., vol. 12, p. 393, 1991.

Robert Giahn-Horng Lee was born in Taipei, Taiwan, Republic of China, in 1965. He received the B.S. degree in electrical engineering from National Cheng-Kung University, Taiwan, in 1987 and the M.S. degree in electronic engineering from National Chiao-Tung University, Taiwan, in 1992. He is currently working toward the Ph.D. degree at the Department of Electronic Engineering and Institute of Electronics, National Chiao-Tung University, His current research interests include CMOS VLSI/ULSI technology, device design, device mod-

eling and simulation, and reliability study of miniaturized MOS devices.

Jen-Shien Su was born in Taiwan, Republic of China, in 1968. He received the B.S. degree in electrical engineering from Tatung Institute of Technology, Taiwan, in 1992 and the M.S. degree in electronic engineering from National Chiao-Tung University, Taiwan, in 1994. His master thesis was on the characterization of hot carrier induced oxide damages in submicron MOS devices.

Steve S. Chung (S'83-M'85-SM'95) received the B.S. degree from the National Cheng-Kung University, Taiwan, in 1973, the M.Sc. degree from the National Taiwan University, in 1975, and the Ph.D. degree from the University of Illinois at Urbana-Champaign, in 1985, all in electrical engineering.

From 1976 to 1978, he worked for an electronic instrument company as Head of the R&D division and subsequently as Manager of the Engineering Division. From 1978 to 1983, he was with the Department of Electronic Engineering and Technology

at the National Taiwan Institute of Technology (NTIT) as a Lecturer. He was also in charge of an Instrument Calibration Center at NTIT. From 1983 to 1985, he held a research assistantship in the Solid State Electronics Laboratory and the Department of Electrical and Computer Engineering at the University of Illinois. In Sept. 1985, he served at NTIT again as an Associate Professor in the Department of Electronic Engineering. Since August 1987, he has been with the Department of Electronic Engineering and Institute of Electronics, National Chiao Tung University, Taiwan, and has been a Full Professor since the Fall of 1989. His current teaching and research interests are in the areas of solid-state device physics and VLSI technology; Spice device modeling; numerical simulation and modeling of submicron and deep-submicron MOS devices, SOI devices, nonvolatile memories and TFT's; characterization and reliability study of VLSI devices and circuits; and computational algorithms for VLSI circuits. He has authored and co-authored more than 60 international journal and conference papers in the above areas.

Dr. Chung has served as a Technical Program Committee Member of the ASIC Conference, IEEE, since 1989.