# A NEW NON-QUASI STATIC MOSFET MODEL

by

**Ibrahim Chamas**

BS, Lebanese University, 2001

Submitted to the Graduate Faculty of

School of Engineering in partial fullfilment

of the requirements for the degree of

Master of Science

University of Pittsburgh

## UNIVERSITY OF PITTSBURGH

## SCHOOL OF ENGINEERING

This thesis was presented

by

**Ibrahim Chamas**

It was defended on

December 6<sup>th</sup>, 2004

and approved by

Hong Koo Kim, Professor, Electrical Engineering Department

Dietrich W. Langer, Professor, Electrical Engineering Department

Thesis Advisor: Mahmoud El Nokali, Professor, Electrical Engineering Department

## A NEW NON-QUASI STATIC MOSFET MODEL

## Ibrahim Chamas, MS

#### University of Pittsburgh, 2004

Recent progress in wireless communication is sustained through integrated circuit technologies that offer a low cost and low power devices that operate in the Radio Frequency (RF) range with relatively low noise figure. The submicrometer CMOS technology presents a serious alternative to the more expensive, high power GaAs and Si bipolar technologies that have been used for the design of high frequency ICs. Design testing and verification through circuit simulation is a critical step in the design cycle of RF integrated circuits (RFICs). Accurate device models are therefore required to reduce design cycles and to achieve success when the circuit is finally committed to silicon.

This thesis addresses the Radio Frequency (RF) small-signal and large-signal models for the MOS transistor. The quasi-static (QS) and non-quasi-static (NQS) models are discussed and the assumptions used in their development are examined. The various charge components are briefly introduced and the source/drain charge partitioning is presented. The limitation of the QS approach at high frequency is investigated using the Bsim3v3.1 model. The development of a first order NQS small-signal model is briefly presented and its suitability for RF applications is indicated. The effect of the distributed gate, channel, and substrate resistances on the high

frequency characteristics of the MOS transistor is examined. We propose a Radio Frequency small-signal equivalent circuit (EC) together with an efficient parameter extraction algorithm that is necessary for the device optimization and the development of accurate large-signal models. The validity of the proposed model and the accuracy of the extraction method are verified by comparing Pspice simulation results of the EC to experimental data and the Bsim3v3.1 model up to 10GHz.

# TABLE OF CONTENTS

| 1.0       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1       | THESIS ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3  |

| 2.0       | QUASI VERSUS NON-QUASI-STATIC MODELING OF MOSFETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

| 2.1       | QUASI-STATIC MODELING (LARGE SIGNAL ANALYSIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6  |

| 2.2       | NON-QUASI STATIC MODELING (LARGE SIGNAL ANALYSIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12 |

| 2.3       | A QUASI –STATIC MEDIUM FREQUENCY SMALL SIGNAL MODELING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

| 2.4       | A COMPLETE QUASI-STATIC SMALL SIGNAL MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24 |

| 2.5       | Y-PARAMETER MODELING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

| 2.6       | A SMALL SIGNAL NON-QAUSI STATIC MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 |

| 2.7       | CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52 |

|           | EFFECT OF EXTRINSIC ELEMENTS ON THE HIGH FREQUENCY PERFORMANGED FOR STREET STRE |    |

| 3.1<br>OP | MODELING AND IMPACT OF THE GATE RESISTANCE ON THE DEVI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 3.2       | CUT-OFF AND MAXIMUM OSCILLATION FREQUENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60 |

| 3.3<br>PE | EFFECT OF SEMI-CONDUCTING SILICON SUBSTRATE ON THE RFORMANCE OF MOSFETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.4       | SCATTERING PARAMETERS (S-PARAMETERS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70 |

| 3.5       | CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71 |

|       | RADIO FREQUENCY MODELING AND PARAMETER EXTRACTION OF S<br>OMETER CHANNEL LENGTH MOSFETS ACCOUNTING FOR FIRST ORDER N |     |

|-------|----------------------------------------------------------------------------------------------------------------------|-----|

|       | CTS                                                                                                                  | _   |

| 4.1   | PROPOSED MODEL ANDPARAMETER EXTRACTION PROCEDURE                                                                     | 76  |

| 4.2   | Y-PARAMETER ANALYSIS AND PARAMETER EXTRACTION                                                                        | 84  |

| 4.    | 2.1 EXTRACTION OF SMALL SIGNAL PARAMETERS                                                                            | 87  |

| 4.3   | MODEL VERIFICATION                                                                                                   | 95  |

| 4.4   | CONCLUSION                                                                                                           | 101 |

| 5.0 C | CONCLUSIONS AND FUTURE WORK                                                                                          | 102 |

| 5.1   | POTENTIAL IMPROVEMENT                                                                                                | 103 |

| 5.2   | FUTURE WORK                                                                                                          | 104 |

| APPEN | NDIX                                                                                                                 | 105 |

| Y-P   | ARAMETER ANALYSIS OF THE PROPOSED RF SMALL-SIGNAL MODEL                                                              | 105 |

| BIBLI | OGRAPHY                                                                                                              | 111 |

# LIST OF TABLES

| Table 1 High frequency figures-of-merit for different technologies     | . 64 |

|------------------------------------------------------------------------|------|

| Table 2 Average and optimized values of the extracted model parameters | . 94 |

# LIST OF FIGURES

| Figure 1 Intrinsic part of the MOSFET is shown in the dashed box                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 Simulated turn-on drain current using the Bsim3v3.1 QS model                                                                |

| Figure 3 Simulated turn-on drain current using the Bsim3v3.1 QS model for the three charge partitioning schemes                      |

| Figure 4 Simulated turn-on source current using the Bsim3v3.1 QS model for the three charge partitioning schemes                     |

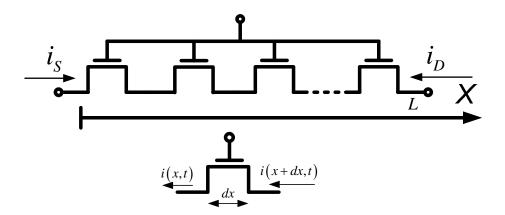

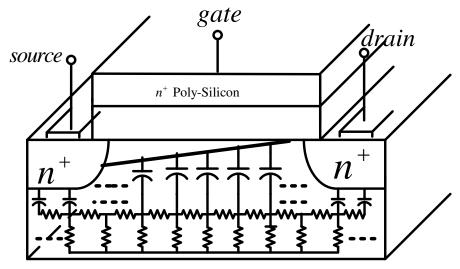

| Figure 5 dividing the transistor into smaller sections along the its length is the key to NQS modeling                               |

| Figure 6 Characteristic of the Drain current using NQS analysis resulting from applying a step input at the gate with zero rise-time |

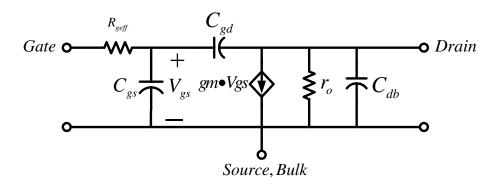

| Figure 7 A medium frequency (QS) small-signal model [9]                                                                              |

| Figure 8 A medium frequency small signal model including the drain to bulk path                                                      |

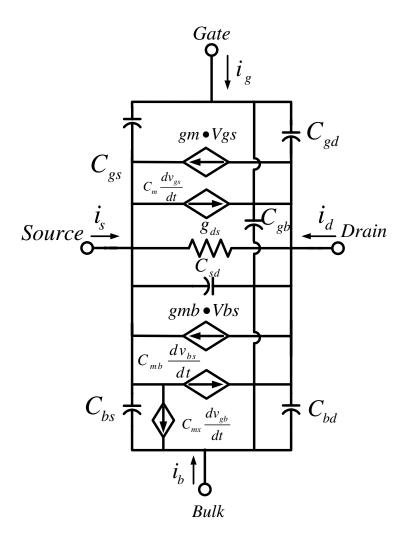

| Figure 9 A complete Quasi-static small signal model                                                                                  |

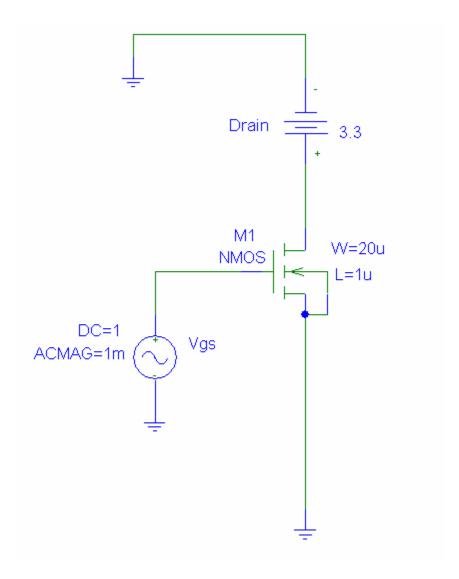

| Figure 10 Circuit schematic used to simulate the frequency response of the drain current for the Bsim3v3.1 complete QS model         |

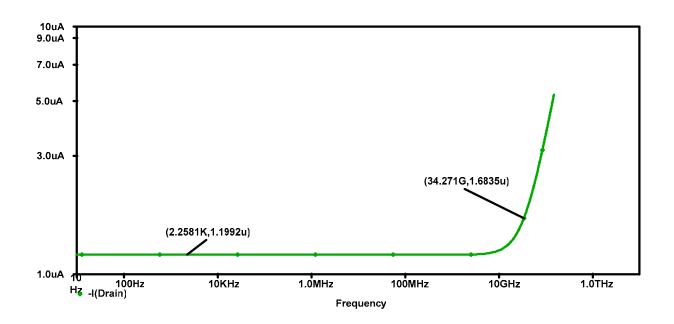

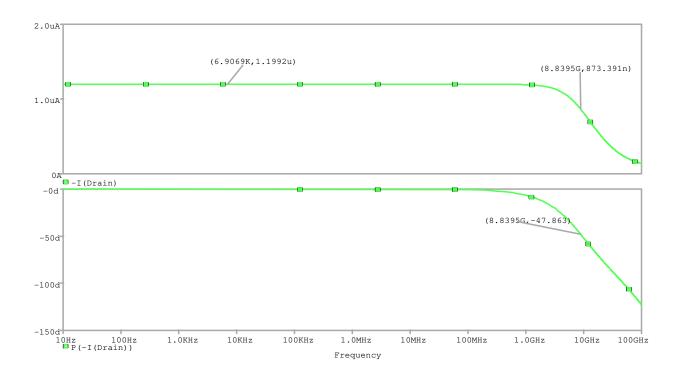

| Figure 11 The magnitude response of the ac drain current generated by the Bsim3v3.1 complete QS model                                |

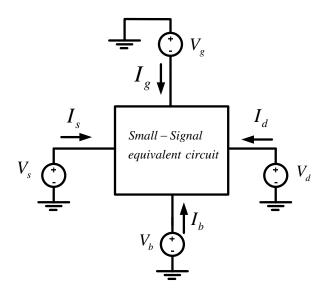

| Figure 12 A setup for deriving the Y-parameter model                                                                                 |

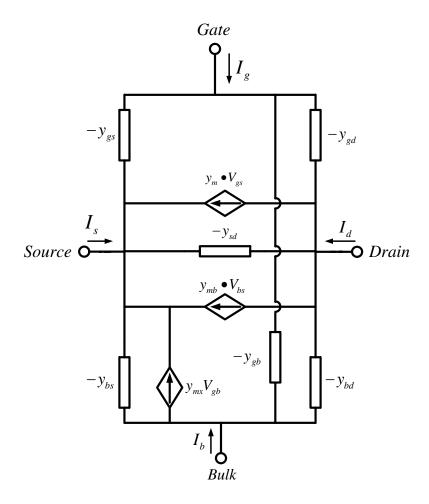

| Figure 13 Y-parameter model                                                                                                          |

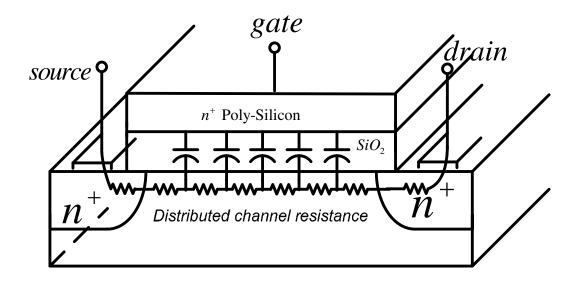

| Figure 14 The oxide capacitance and channel resistance form a distributed RC network 39                                              |

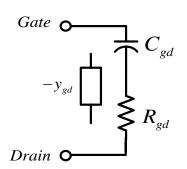

| Figure 15 A first order NQS gate-to-drain equivalent circuit                                                                         |

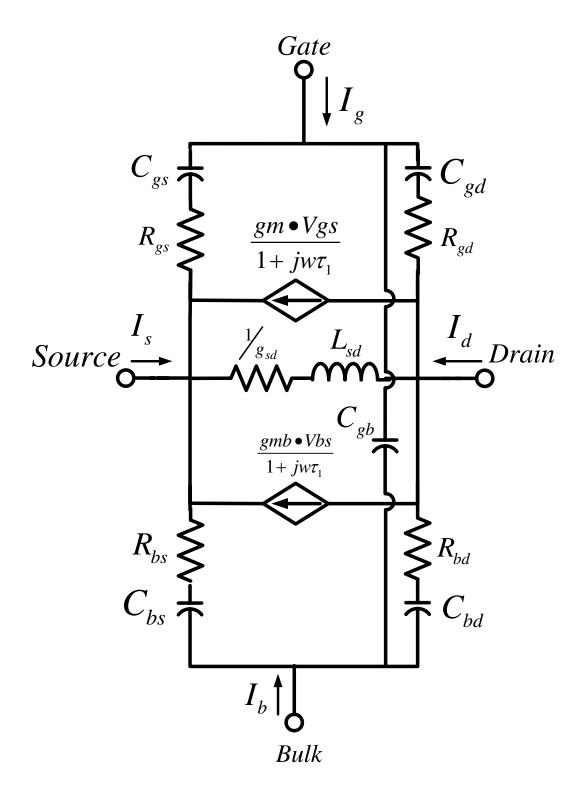

| Figure 16 A first order Non-quasi-static model                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 17 Magnitude and phase of the drain current as predicted by the NQS Bsim3v3.1 model52                                                                                                                                                                                                                                                                  |

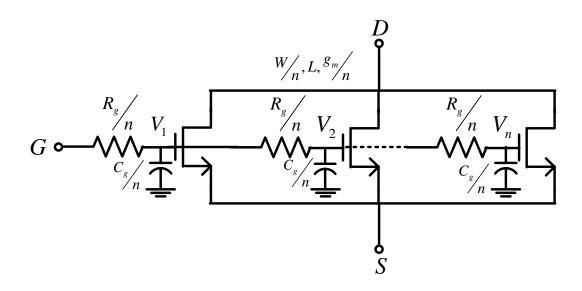

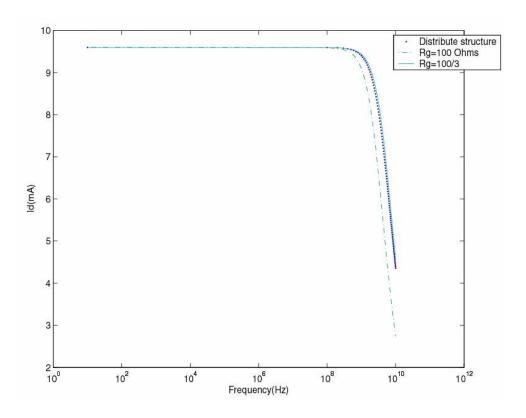

| Figure 18 The gate resistance forms a distributed RC network with the oxide capacitance. The transistor can be divided into subsections to formulate the lumped equivalent gate resistance                                                                                                                                                                    |

| Figure 19 The frequency response of the drain current considering for a polysilicon gate resistance of $100\Omega$ . The distributed structure of the gate resistance can be approximated by a lumped resistance one-third the DC value                                                                                                                       |

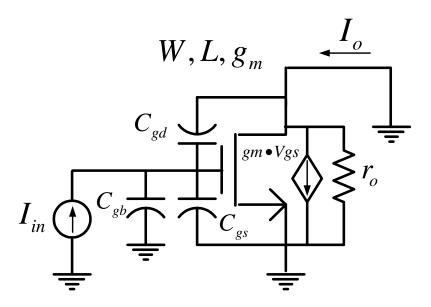

| Figure 20 MOS transistor showing the small-signal elements needed to calculate the cutof frequency $w_T$ .                                                                                                                                                                                                                                                    |

| Figure 21 small signal equivalent circuit including the electrode gate resistance. This model is used to calculate the maximum oscillation frequency                                                                                                                                                                                                          |

| Figure 22 The bulk depletion capacitance and the substrate resistance form a distributed RC network at RF                                                                                                                                                                                                                                                     |

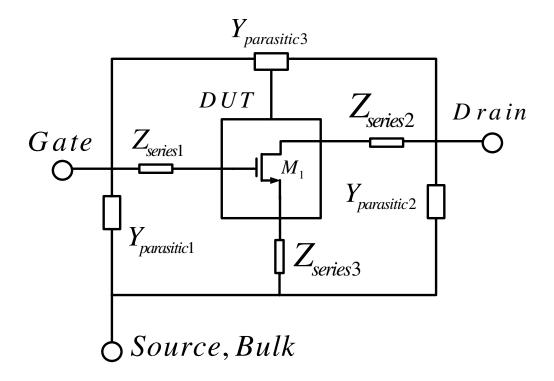

| Figure 23 Equivalent circuit representation of the test structure used to de-embed the measured high frequency data of the MOS transistor                                                                                                                                                                                                                     |

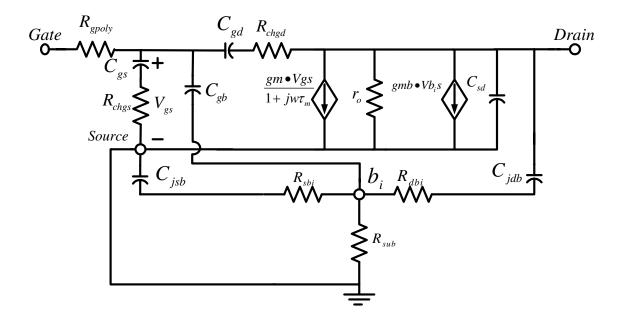

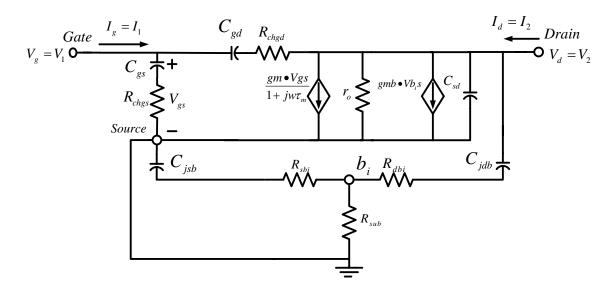

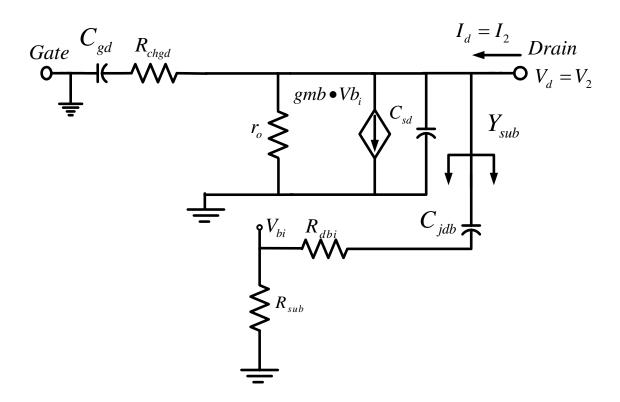

| Figure 24 An RF small-signal MOSFET model based on the first order non-quasi-static effect. The effective gate-to-source and gate-to-drain channel resistance is modeled by $R_{chgs}$ and $R_{chgd}$ respectively. Substrate signal coupling through the intrinsic body node and junction capacitances is examined by introducing a new 3-resistor T-network |

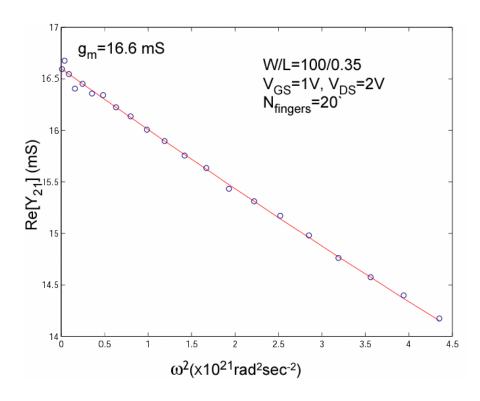

| Figure 25 Extraction of the gate transconductance was obtained from the Y-intercept of $Re[Y_{21}]$ versus $w^2$                                                                                                                                                                                                                                              |

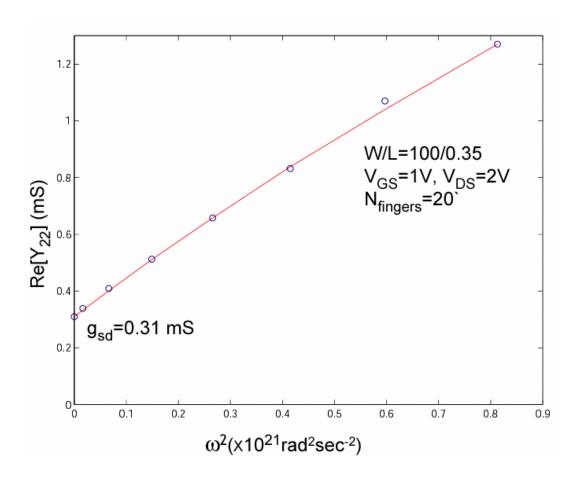

| Figure 26 The drain-to-source conductance was obtained from the Y-intercept of $Re[Y_{22}]$ versus $w^2$                                                                                                                                                                                                                                                      |

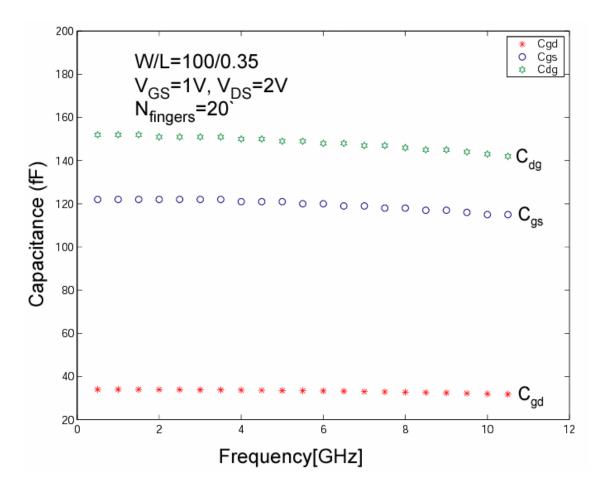

| Figure 27 The extracted gate-to-source, gate-to-drain, and drain-to-gate capacitances are almos constant with frequency, asserting the physical validity of the model and accuracy of the parameter extraction method                                                                                                                                         |

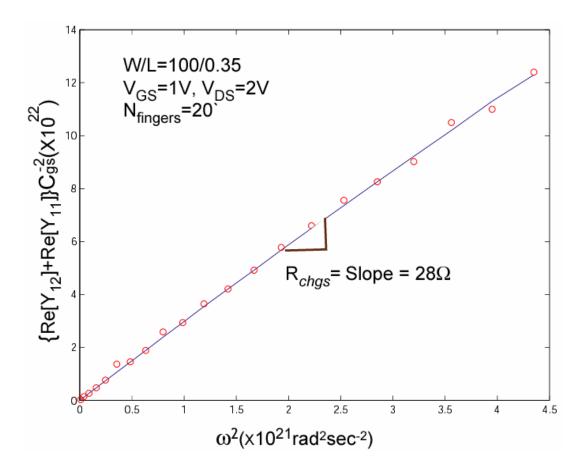

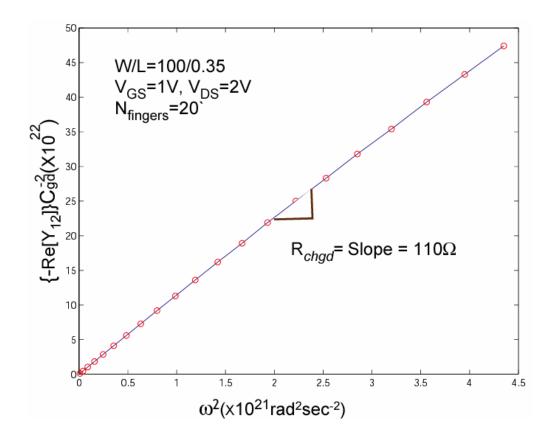

| Figure 28 The effective gate-to-source channel resistance $R_{chgs}$ is determined from the slope of                                                                                                                                                                                                                                                          |

| $\left(\operatorname{Re}\left[Y_{12}\right] + \operatorname{Re}\left[Y_{11}\right]\right)C_{gs}^{-2}$ as a function of $w^2$                                                                                                                                                                                                                                  |

| Figure 29 The effective gate-to-drain channel resistance $R_{chgd}$ is determined from the slope of $-\text{Re}\big[Y_{12}\big]C_{gd}^{-2}$ as a function of $w^2$                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

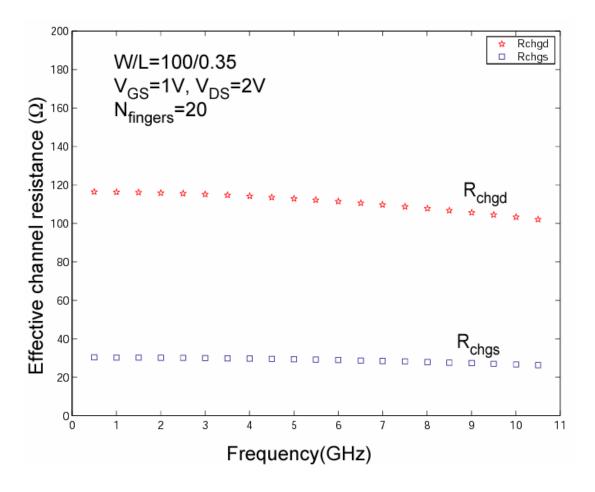

| Figure 30 Frequency dependence of $R_{chgs}$ and $R_{chgd}$ . The results show that these two resistors are almost constant with frequency, verifying the accuracy of the model                                                                                                                                                                               |

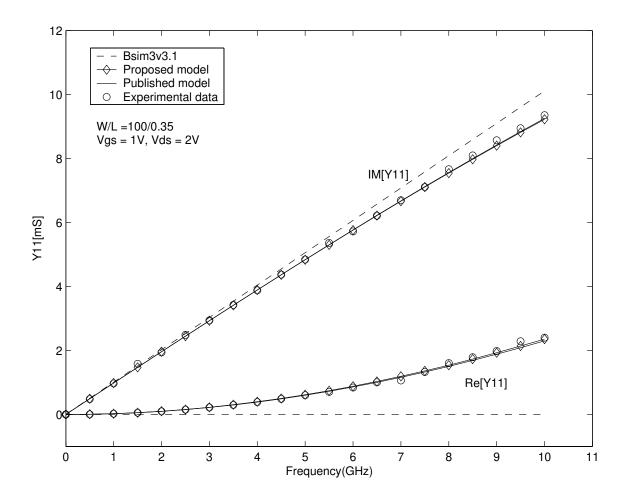

| Figure 31 $Y_{11}$ parameter of measured data, proposed model, Bsim3v3.1 model, and published model. The simulated $Y_{11}$ parameter of the proposed model matches the measured data very well and is more accurate than the Bsim3v3.1 model                                                                                                                 |

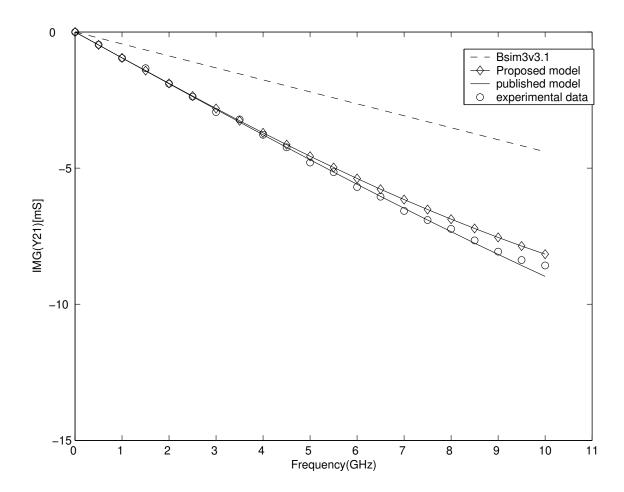

| Figure 32 $Im[Y_{21}]$ parameter of measured data, proposed model, Bsim3v3.1 model, and published model. The simulated $Im[Y_{21}]$ parameter of the proposed model shows a slight deviation from the experimental data above 5GHz but becomes more accurate than the published model at 10GHz.                                                               |

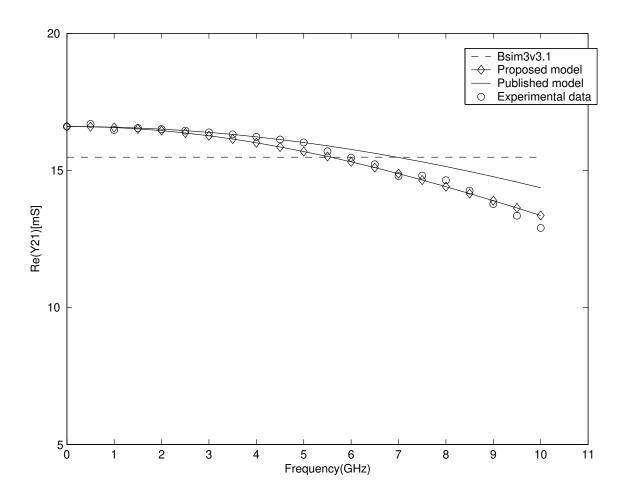

| Figure 33 $Re[Y_{21}]$ parameter of measured data, proposed model, Bsim3v3.1 model, and published model. Being based on NQS analysis, the simulated $Re[Y_{21}]$ of the proposed model is much more accurate than that predicted by the published above 5GHz                                                                                                  |

| Figure 34 $Y_{21}$ parameter of measured data, proposed model, Bsim3v3.1 model, and published model. The simulated $Y_{21}$ parameter of the proposed model matches the measured data very well and is more accurate than the Bsim3v3.1 model                                                                                                                 |

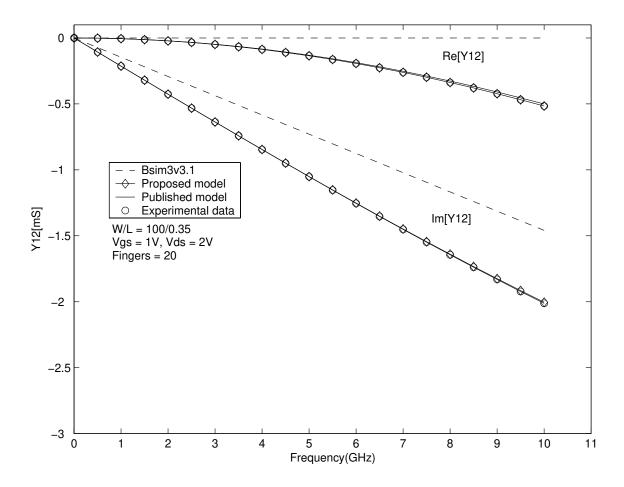

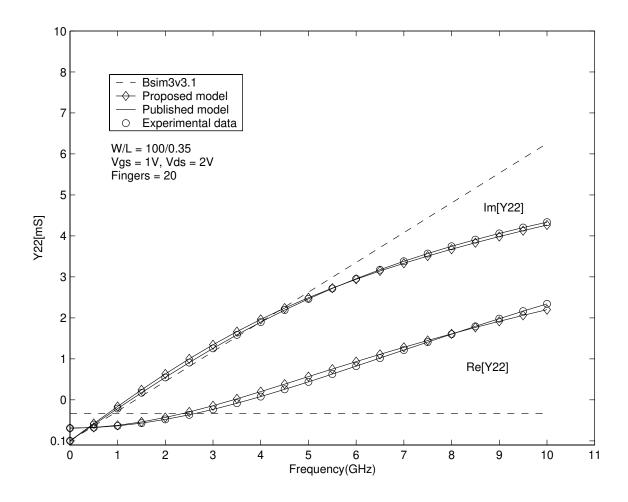

| Figure 35 $Y_{22}$ parameter of measured data, proposed model, Bsim3v3.1 model, and published model. The simulated $Y_{22}$ parameter of the proposed model matches the measured data very well and is more accurate than the Bsim3v3.1 model                                                                                                                 |

| Figure 36 An RF small-signal MOSFET model based on the first order non-quasi-static effect. The effective gate-to-source and gate-to-drain channel resistance is modeled by $R_{chgs}$ and $R_{chgd}$ respectively. Substrate signal coupling through the intrinsic body node and junction capacitances is examined by introducing a new 3-resistor T-network |

| Figure 37 The proposed EC in the $Y_{22}$ measurement setup. The effect of the source-to-bulk junction capacitance $C_{jsb}$ and resistance $R_{sbi}$ on the output admittance is neglected for simplicity                                                                                                                                                    |

#### **ACKNOWLEDGEMENTS**

Without the help, advice, and encouragement of many individuals this work would have never been completed. First, I would like to thank my advisor Professor Mahmoud El Nokali for his support and advice. I believe that I have been truly blessed by working with him over the past two years. I have benefited not only from this knowledge in device modeling, but also from his keen personality. I wish him well in all his future endeavors. Appreciation is also extended to the members of my advisory committee, Professors Hong Koo Kim and Dietrich W. Langer for reviewing this work. Special thanks go to my best friend Ghassan Azour and his parents, Nazih Azour and Nazira Azour for their support, help and encouragement. I would also like to thank Maya Shehab for her love and devotion.

I would also like to acknowledge my friends, Edward Saad, Dany Azour, Wessam Hassanein, Majd Sakr, Amit Gupta, Elizabeth Ellis, Chela Nagieh, and many others for making my life as a graduate student more enjoyable. I would like to thank the graduate program administrator, Sandy Weisberg for her help.

Although I mention my family last, they certainly made the greatest contribution to this work. Their love, care and support over so many years have really helped to shape my future. I thank my father Ramez Chamas for his invaluable advice and my late mother Zakie Chamas for her love and patience. I certainly appreciate the tremendous love from my two sisters

Lara and Rania, and my brother Hassan. I cannot thank them enough for their support and assistance throughout my life. I am also thankful to my brother-in-law Salim Bark for his continuous encouragement. My love goes to Lara's daughters Cherine, Rawan, and Dian, and to Rania's daughter Joel. Finally, I would like to acknowledge the University of Pittsburgh for its support and for the invaluable knowledge that I have gained throughout my stay.

#### 1.0 INTRODUCTION

The possibility of communicating through the "ether" was demonstrated in 1901 when Guglielmo Marconi successfully transmitted radio signals across the Atlantic Ocean. The consequences and prospects of this demonstration were simply overwhelming. However, for many decades, two-way phone conversations would still go over wires and wireless transmission remained limited to one-way radio and television broadcasting. The invention of the transistor, the development of Shannon's information theory, and the conception of the cellular system paved the way for affordable wireless communications. Nowadays, mobile communication systems are moving rapidly from supporting voice only towards integrating digital data and multimedia transmissions as well. Thus, the projected applications for wireless technology are expanding beyond simple cellular phone handsets to include wireless internet connectivity in automobiles, cellular handsets, and personal data assistants (PDAs).

The push for wireless capabilities in the consumer market, in particular, is therefore accompanied by the demand for low-cost, wireless transceivers. Over the past three decades, the number of transistors in silicon (*Si*) based integrated circuits (ICs) has doubled about every 18 months. This well-known trend is referred to as "Moore's law," after Gordon E. Moore of Intel Corporation. Moore recognized the trend in 1965 that continued into the 21<sup>st</sup> century. Moore's primary intent for predicting future levels of integration was to push the improvement of the microprocessor. Thus, the research and development investments to keep track with Moore's law

have typically focused on digital applications. The corresponding economy-of-scale for Si digital ICs has, therefore, dramatically reduced the cost of microprocessors. On the other hand, Si has not been the ideal semiconductor for high frequency analog applications. Radio frequency ICs (RFICs) and monolithic microwave ICs (MMICs) have historically used compound semiconductors synthesized from elements in columns III and V of the periodic table (III-V semiconductors). III-V semiconductors have characteristically high electron mobility and are readily grown on semi-insulating substrates; features that are ideal for high frequency applications. However, high-speed analog and wireless ICs have recently sought to take advantage of the same Si economy-of-scale in an effort to reduce cost. The potential for high integration and lower cost has spurred research and advances in silicon-based technologies that include both bipolar and submicron complementary metal-oxide silicon (CMOS) devices (BiCMOS technologies).

The quadratic improvement in the microwave properties of CMOS devices with downscaling the channel length combined with the possibility of a system-on-chip integration has motivated extensive research on implementing a CMOS radio transceiver. Subtle physical mechanisms that govern the properties of deep sub-micron Mosfets have to be adequately described and incorporated in CAD tools to empower circuit designers with the ability to extract the best performance out of these devices. Design testing and verification through circuit simulation is a critical step in the design cycle of RF integrated circuits (RFICs). Accurate device models are therefore required to reduce design cycles and to achieve success when the circuit is finally committed to silicon. In essence, critical to the success of "RF CMOS" is the development of accurate and scalable RF Mosfet models.

#### 1.1 THESIS ORGANIZATION

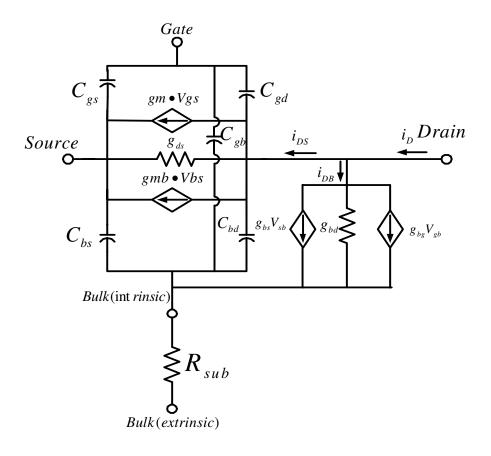

The objective of this research is to develop a physical small-signal equivalent circuit of a MOS transistor that can simulate the device characteristics in the Gega-Hertz range. Extraction of the model parameters is critical and should be considered at the same time the model is developed. To this end, an accurate and efficient parameter extraction procedure is presented. Chapter 2 discusses the quasi-static (QS) and non-quasi-static (NQS) models and the underlying assumptions used in their development. The QS approach assumes that the channel charge can adjust itself instantaneously and is only valid at low frequencies. A complete QS model is presented and the notion of trans-capacitance is introduced. The Bsim3v3.1 model is used to indicate the limitation of the QS model at high frequency. The NQS formulation is briefly introduced and it is shown that the channel resistance plays an important role at high frequencies. This resistance forms a distributed bias dependant RC network with the gate oxide and results in a signal delay between the transistor terminals. Non-quasi-static effects have been demonstrated to exit for both long and short channels and should be included in an RF Mosfet model. A first order NOS model is derived and discussed. Although this model extends the region of validity of the QS models, more elements should be added to enhance the accuracy at RF. These elements are related to the extrinsic parasitics and are discussed in chapter 3. At RF, the extrinsic components of the device play a prominent role in degrading the transistor performance and therefore have to be added to the intrinsic small signal NQS model. Six extrinsic capacitances are to be added: the gate-to-source capacitance  $C_{\it gsex}$  , the gate-drain-capacitance  $C_{\it gdex}$  , the gate-tobulk capacitance  $C_{gbex}$ , the drain-to-bulk capacitance  $C_{dbex}$ , the source-to-bulk capacitance  $C_{sbex}$ ,

and the drain-to-source capacitance  $C_{\it dsex}$ . As for the parasitic resistances they can be divided into four parts: the resistance of the gate material, the substrate resistance, the resistance of the source and drain regions and their contacts. At high frequency the impedances of the capacitive components are comparable or even smaller than that of the resistive components that despite their distributive nature are represented by lumped elements in most models. The resistance of the drain and source regions are less important than the other two resistances and are most of the time omitted for simplicity. This chapter is mainly concerned with the effect of the gate and substrate resistances on the device operation at RF. The rest of the chapter is devoted to the discussion of some important parameters required for RF MOSFET modeling and to briefly introduce the scattering parameters.

Chapter 4 presents a radio-frequency (RF) small signal MOSFET model together with a simple parameter extraction algorithm. The intrinsic part of the proposed equivalent circuit (EC) is based on a first order non-quasi-static (NQS) formulation. The intrinsic and extrinsic components are extracted by performing Y-parameter analysis on the proposed model. Simple analytical expressions for extracting the effective gate-to-source and gate-to-drain channel resistances are developed for the first time. The distributed nature of the substrate resistance at high frequency is modeled using a novel lumped three-resistor T-network. Substrate signal coupling through the intrinsic body node and its effect on the output admittance are carefully examined. Simplified new expressions for the real and imaginary part of the output admittance are developed that prove essential in extracting the substrate related parameters. The physical validity of the model and the accuracy of the extraction method are verified by comparing Pspice simulation results of the EC to experimental data up to 10GHz.

## 2.0 QUASI VERSUS NON-QUASI-STATIC MODELING OF MOSFETS

This chapter discusses the quasi-static (QS) and non-quasi-static (NQS) models and the underlying assumptions used in their development. In order to model the frequency response of a semiconductor device the charge storage effect should be considered. For this reason, the various charge components in the MOS transistor are briefly discussed and the source/drain charge partitioning is presented [1]. To gain more insight into the limitations of the quasi-static approach, the large-signal behavior of the transistor is examined using the Bsim3v3.1 model [2]. Qualitatively, the QS formulation assumes that electrons travel along the channel with infinite speeds and hence ignores the finite time it takes them to cross the channel. The longer the channel is, the more time it takes the electron to travel from the source to the drain and the more the QS model will be in error. We introduce the non-quasi-static (NQS) formulation that divides the channel into sections, each being short enough to operate quasi-statically.

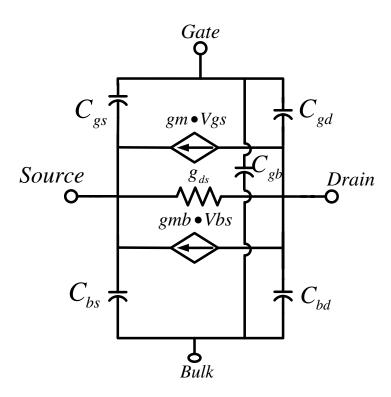

A small-signal quasi-static model for the intrinsic part of the transistor is briefly discussed [3-6]. The model uses five capacitances to simulate the behavior of the transistor in the mid-frequency range. In order to extend the region of validity of the model all capacitive effects have to be considered leading to an improved quasi-static model [7-9]. The failure of the quasi-static models to predict the high frequency behavior of the transistor is examined and the small-signal non-quasi static model is discussed. These small-signal circuits model the intrinsic part of

the device. The impact of the extrinsic elements on the radio frequency operation of the transistor will be discussed in chapter 3.

## 2.1 QUASI-STATIC MODELING (LARGE SIGNAL ANALYSIS)

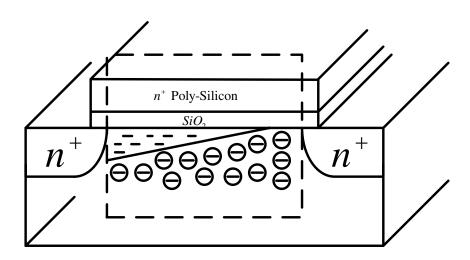

Most circuit applications involve using the MOSFET in dynamic operation where either a small or a large time-varying signal is applied to one of its terminals causing a dynamic change in the transistor charges. The change in the transistor charge is supplied from the outside circuitry through the "charging currents" [10] that exist only in dynamic operation. The intrinsic part of the device is included between the drain and the source diffusion regions and contains the inversion layer, the depletion region, the oxide, and the gate material as depicted in figure 1 in the dashed box. The intrinsic part of the transistor is responsible for the actual operation while the extrinsic components act as parasitics that will limit the frequency performance of the transistor.

Three bias-dependent charge components are present in a MOS transistor namely the inversion, the bulk and the gate charges. The inversion charge is divided into a drain and source charges that are used to evaluate the source and drain charging currents and the corresponding node capacitances. The three charges are found by solving Poisson's equation. A closed form analytical solution is possible for a one-dimensional case by imposing the gradual-channel approximation and by using the charge sheet approximation [11]. As the channel length is scaled down, the electric field along the channel becomes more significant. In this case, a two-dimensional analysis is required. The channel is considered short if the effective channel length

$(L_{\it eff})$  is not much larger than the sum of the drain and source depletion widths. Moreover, if the channel width is narrow, i.e. the width of the transistor is not much larger than the depletion region depth underneath the gate, the electric field along the width of the transistor is significant. Accounting for both short and narrow channel effects requires a three-dimensional numerical analysis [12-14] that gives accurate results, but fails to provide a simple computationally efficient model. A viable alternative consists of proposing empirical and semi-empirical approximations that yield simple equations that are reasonably accurate and computationally efficient [15], [16].

Figure 1 Intrinsic part of the MOSFET is shown in the dashed box

Until recently, most of the MOSFET models in Spice are based on the quasi-static assumption and are inadequate at high frequencies [7], [17-19]. In the quasi-static formulation (QS), the finite time it takes the channel charge to reach equilibrium when a time-varying voltage

is applied is ignored. The channel charge is assumed to follow the signal with no delay and with no degradation in its absolute value. Obviously, this assumption leads to erroneous results if the frequency of the applied signal is of the order of the unity gain transition frequency ( $f_T$ ) [20]. As will be seen later,  $f_T$  is inversely proportional to the square of the effective channel length for long-channel devices. Hence, the shorter the channel is, the larger  $f_T$  will be and the transistor can be successfully described by the quasi-static analysis. For digital applications, the quasi-static model fails if the rise- or fall-time of the applied signal is less than or comparable to the channel transit time.

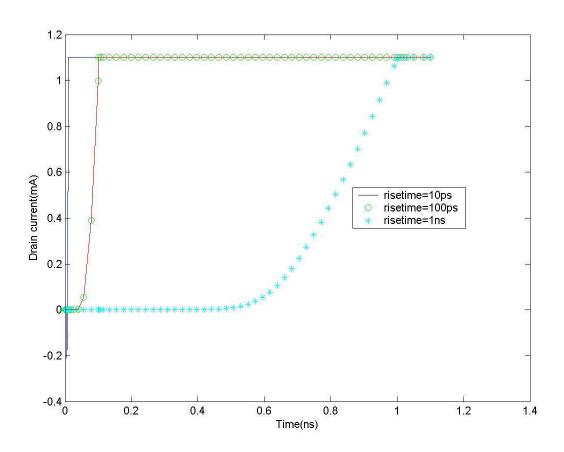

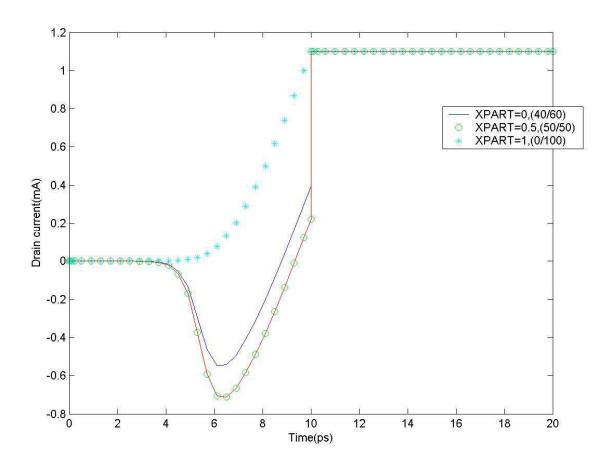

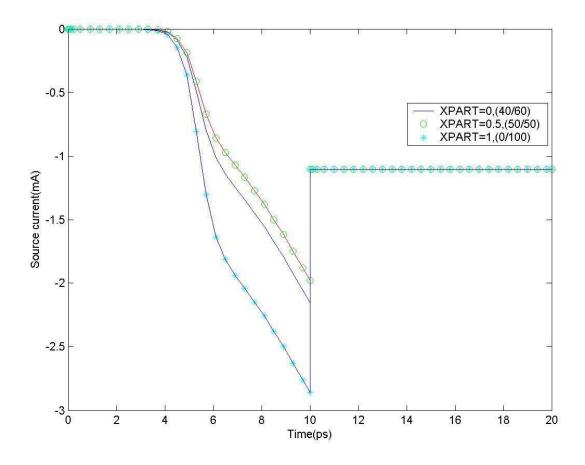

The Bsim3v3.1 will be used to demonstrate the failure of the QS model in predicting the high frequency characteristics of the MOS transistor. The source/drain charge partitioning ratio can be set to the desired value by using the XPART parameter in Cadence. Existing charge partitioning ratios are 0/100, 50/50, and 40/60. They correspond to XPART = 1, 0.5, and 0 respectively. The inversion layer charge is supplied from the voltages applied to the source and drain terminals. The 0/100 charge partitioning scheme assigns all the inversion layer charge to the source region. This partitioning scheme is commonly used by circuit designers to suppress unrealistic large drain current spikes during transient simulation [21]. Unfortunately, this nonphysical solution shifts the problem to the source terminal and should only be used when the source terminal is grounded. The 50/50 partitioning scheme assumes that the source and drain regions contribute equally to the total inversion charge. The 40/60 charge partitioning is the most physical and widely used scheme. It allocates the channel charge to the source and drain regions by assuming that the channel charge is linearly dependent on the distance along the channel [10]. Using Pspice simulation, the drain and source currents that the QS Bsim3v3.1 model predicts for a step input applied at the gate of an NMOS transistor will be investigated. To illustrate the

difference between the three charge partitioning schemes, the simulation is conducted for XPART=0, 0.5, and 1. The effect of the rise time on the simulated currents will also be shown. Intuitively, the QS model will result in unrealistic terminal currents if the rise-time (fall-time) of the gate signal is small. The parameters used in the Bsim3v3.1 model are extracted from the 0.35 µm TSMC CMOS process. The simulated MOS transistor has a channel length and width of 0.35 um and 20 um respectively. The XPART parameter is set to 0 (40/60 partitioning) in this experiment. An input step voltage with a rise-time of 10ps, 100ps and 1ns and a maximum value of 1v is applied at the gate. Using different rise times for a single pulse signal in Pspice is possible through the use of the *parameter* element. Consequently, both a parametetric and a transient analysis are needed. The drain terminal is tied to the supply voltage (3.3 volts) and the source and bulk terminals are tied to ground. This biasing setup ensures that the transistor stays in saturation even when the input signal reaches its maximum value of 1 v. During a transient, the drain (or source) current flows through the intrinsic and extrinsic capacitors of the device. In order to examine the drain and source currents of the intrinsic device, the extrinsic gate-to-source and gate-to-drain overlap capacitors denoted as CGSO and CGDO are set to zero.

Figure 2 shows an initial large negative drain current when the rise time of the gate signal is 10ps. The drain current unrealistically decreases to -0.2 mA and then gradually increases and reaches its steady-state value of 1.1mA around 10ps. This negative drain current is not observed in practice if the transistor is in the saturation region. In reality, the channel is depleted of electrons until the input reaches the threshold voltage which for this technology is 0.51 volts. At that time, electrons enter the channel through the source electrode and start their journey towards the drain. It is only when the electrons reach the drain electrode that the drain current can be observed. The QS formulation ignores this fact and assumes that the channel is instantaneously

charged to its equilibrium value and that the electrons move along the channel with infinite speed. Hence the QS approximation fails to determine the fine details of the current and breaks down if the input changes too fast. As the input signal is made slower (increase its rise-time) the negative drain current decreases and the QS model is more applicable. For a rise-time of 10ns, the drain current stays at zero for a *delay* time around 0.6ps and then increases gradually to its steady state. This is a more realistic result as explained above. Figures 3 and 4 show the simulated drain and source current for the three charge partitioning schemes and for a rise-time of 10ps. Although, the negative drain current spike is suppressed for XPART = 1, the source current shows the maximum negative spike for this partition since all the channel charge is allocated to the source terminal.

Figure 2 Simulated turn-on drain current using the Bsim3v3.1 QS model

Figure 3 Simulated turn-on drain current using the Bsim3v3.1 QS model for the three charge partitioning schemes

Figure 4 Simulated turn-on source current using the Bsim3v3.1 QS model for the three charge partitioning schemes

## 2.2 NON-QUASI STATIC MODELING (LARGE SIGNAL ANALYSIS)

In the previous section we found that the quasi-static model breaks down if the input voltage changes too fast. To alleviate this problem the transistor can be divided into smaller sections, each section being small enough to be modeled quasi-statically. The higher the

frequency of operation, the more sections will be needed and the shorter each section will be. Figure 5 illustrates this point.

Figure 5 dividing the transistor into smaller sections along the its length is the key to NQS modeling

The source and drain currents of each sub-transistor are usually different during transient to account for the inversion layer charge build up. Hence the current through each section is a function of time and position. First, we need to write the equations that govern the behavior of this collection of transistors:

## a) The continuity equation:

$$\frac{\partial i(x,t)}{\partial x} = W \frac{\partial q_I(x,t)}{\partial t}, \qquad (2-1)$$

where  $q_I(x,t)$  is the instantaneous inversion layer charge per unit area.

In steady state, the inversion layer charge is independent of time and hence the current is independent of position.

#### b) Inversion layer charge:

$$q_{I}(x,t) = -C_{ox} \left[ v_{GB}(t) - V_{FB} - \psi_{s}(x,t) - \gamma \sqrt{\psi_{s}(x,t)} \right], \tag{2-2}$$

where,  $C_{ox}$  is the oxide capacitance per unit area,  $v_{GB}(t)$  is the instantaneous gate-to-bulk voltage,  $V_{FB}$  is the flat-band voltage,  $\gamma$  is the body coefficient, and  $\psi_s(x,t)$  is the surface potential in the silicon material.

## c) Current equation [9]:

$$i(x,t) = -\mu W q_I(x,t) \frac{\partial \psi_s(x,t)}{\partial t} + \mu W \phi_t \frac{\partial q_I(x,t)}{\partial x}, \qquad (2-3)$$

where  $\mu$  is the mobility and  $\phi_t$  is the thermal voltage.

Notice that the first term on the right hand side of the equation corresponds to the drift current while the second term represents the diffusion current. Equations (2-1), (2-2), and (2-3) contain three unknowns: i(x,t),  $\psi_s(x,t)$ , and  $q_I(x,t)$ . Solving these equations requires a set of initial and boundary conditions which primarily depend on the applied voltages. The mathematics involved in solving the above system can get tedious. In [1], every point along the channel was assumed to be strongly inverted which simplifies the analysis considerably. In strong inversion, the drift current dominates and the diffusion current can be ignored. Moreover, the surface potential  $\psi_s(x,t)$  can be approximated by  $v_{CB}(x,t)+\phi_0$ , where:  $\phi_0=2\phi_F+6\phi_I$  for uniformly doped silicon [9], and  $v_{CB}(x,t)$  is the channel-to-bulk voltage at position x and at time t. In [22], an input step with zero rise time and amplitude (V) is applied to the gate of the transistor. The drain is biased at Vdd to insure operation in the saturation region at all times and the source and bulk terminals are grounded. In this setup  $v_{CB}(t)=V$ . Numerical techniques have

been adopted to solve equations (2-1, 2-2, and 2-3) [22]. The instantaneous drain and source current are calculated from i(x,t) as follows:

$$i_D(t) = i(L,t) \tag{2-4}$$

$$i_{S}(t) = -i(0,t). \tag{2-5}$$

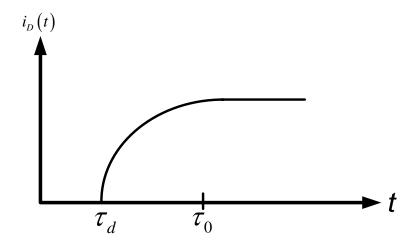

The characteristic of the drain current is sketched in Figure 6 where  $\tau_d$  is the delay time between the application of the input voltage and the flow of the drain current and  $\tau_0$  is the time at which the current reaches 98% of its steady state value.

Figure 6 Characteristic of the Drain current using NQS analysis resulting from applying a step input at the gate with zero rise-time

At this point it is instructive to estimate the average time ( $\tau$ ) it takes the electron to cross the entire channel at DC or steady-state conditions. In the strong-inversion saturation region the electron transit time can be calculated as follows [10]:

$$\tau = \frac{|Q_I|}{I_{DS}} = \frac{\frac{2}{3}WLC_{ox}(V_{GS} - V_T)}{\frac{1}{2}\mu C_{ox}\frac{W}{L}(V_{GS} - V_T)^2} = \frac{4}{3}\tau_0,$$

(2-6)

where:

$$\tau_0 = \frac{L^2}{\mu(V_{GS} - V_T)}. (2-7)$$

Note that equation (2-6) ignores the electron velocity saturation associated with short channel devices and also neglects narrow channel effects that would otherwise make the equation more complicated. However, equation (2-6) is a good estimate of the channel carrier transit time  $\tau$  which is proportional to  $L^2$ . The transit time decreases quadratically with scaling the channel. This result makes scaling a very attractive feature of CMOS in addition to its low cost and its high density of integration. Obviously, the above derivation breaks down if carrier velocity saturation is present along the channel [22]. In this case, the expressions for the inversion layer charge ( $Q_I$ ) and the dc current ( $I_{DS}$ ) will be different. In the extreme case where velocity saturation occurs along the whole channel the value of ( $\tau$ ) can be calculated as:

$$\tau = \frac{L}{v_{dsat}} \,. \tag{2-8}$$

In this case, the transit time  $(\tau)$  is linearly proportional to the channel length. In the case when velocity saturation span part of the channel,  $(\tau)$  will be proportional to  $L^{\alpha}$  where  $\alpha$  is between 1 and 2. On the other hand, the value of the delay time  $\tau_d$  was found to be [1]:

$$\tau_d \approx 0.38\tau_0,\tag{2-9}$$

As seen from Figure 6, the drain current starts increasing at  $\tau_d$ , the time it takes the electron to reach the drain terminal and increases gradually to its steady state value. At  $\tau_0$ , the drain current would have reached around 98% of its steady state value [1]. This picture of the

drain current is a more realistic result than that obtained from the QS formulation which assumes that the channel will be filled with charge instantaneously at t=0 and that the drain current flows immediately and can be negative as seen in Figure 2. A more practical situation occurs when the input signal has a finite rise time [17, 23] rather than being the input step considered before. It has been shown that if the signal rise time is much smaller than  $\tau_0$ , then the current delay time is given by equation (2-9). However, if the rise time is on the order of  $\tau_0$ , the delay time if given by:

$$\tau_d = \sqrt{t_R \tau_0} \ . \tag{2-10}$$

Hence the delay time depends on the rise time. The faster the input changes (short rise time) the faster the drain current reacts (delay is reduced). This result can be explained as follows: as  $t_R$  is made smaller, the transistor will turn on sooner ( $V_{GS} > V_T$ ) and the channel charge entering the source terminal will reach the drain in a shorter time. It has been shown that if the rise time of the input signal is larger than  $20\,\tau_0$ , the numerical solution of (2-1), (2-2), and (2-3) gives roughly the same results as the quasi-static model. The above analysis has been performed considering a long-channel device. Short channel effects such as velocity saturation will change the picture. The extreme case is given by equation (2-8) when a step input is applied and is found to be much larger than the delay time predicted by the long-channel theory [17]. On the other hand, if the rise time of the input signal is much larger than the above limit and the carrier velocity did not saturate then the delay time is found to be less than that predicted by the long-channel theory.

We have seen so far that the QS model breaks down if the input changes too fast compared to the channel transit time. We will find out later on that the small signal quasi-static model fails if the frequency of the input signal is on the order of the unity gain transition frequency  $(f_T)$ . Interestingly,  $f_T$  is on the order of the inverse of the channel transit time. Moreover, the channel length plays an important role in determining the validity of the QS model as seen from equations (2-7) and (2-8).

## 2.3 A QUASI –STATIC MEDIUM FREQUENCY SMALL SIGNAL MODELING

The small-signal model of the intrinsic part of the transistor at medium frequencies is shown in Figure 7. The small signal parameters  $g_m$ ,  $g_{mb}$  and  $g_{ds}$  represent the gate transconductance, bulk transconductance, and output conductance respectively. These three elements model the transport portion of the drain-to-source current and can be evaluated as follows:

$$g_m = \frac{\partial I_{DS}}{\partial V_{CS}} \Big|_{V_{DS}, V_{BS}} \tag{2-11}$$

$$g_{mb} = \frac{\partial I_{DS}}{\partial V_{BS}} \Big|_{V_{DS}, V_{GS}}$$

(2-12)

$$g_{ds} = \frac{\partial I_{DS}}{\partial V_{DS}} \Big|_{V_{GS}, V_{BS}} . \tag{2-13}$$

These small signal parameters are bias dependent and have different expressions for short and long channel devices [10]. These parameters depend on the slope or first-order derivative of the current equation thus presenting a major challenge in modeling MOS transistors for analog and RF applications. It has been shown [7] that although the DC drain current can be accurate, the

error in predicting the drain-to-source conductance  $g_{ds}$  may exceed 50%. Consider a small change in the gate-to-source voltage. Regardless of the pace of that change, the model in Figure 7 predicts that a small signal drain current will flow instantaneously through the voltage-controlled current source  $g_m v_{gs}$  and therefore the Quasi-static assumption is clearly implied by this model.

Figure 7 A medium frequency (QS) small-signal model [9]

The presence of impact ionization, which is more pronounced in short channel devices, adds more components to the model. High electric fields along the channel of sub-micrometer devices can cause carrier velocity saturation. These high fields usually exist when the transistor

is in the saturation region. Although the velocity of the electrons saturate, their random kinetic energy continues to increase. Some of these carriers will have enough energy to cause impact ionization where an electron collides with the silicon lattice and generates an electron-hole pair. The drain absorbs the generated electrons and the holes drift towards the substrate terminal resulting in a drain-to-bulk current [24]. The transistor is then said to be in weak avalanche. In general, the drain current contains two components and is given by:

$$I_{D} = I_{DS} + I_{DB}, (2-14)$$