Open access • Journal Article • DOI:10.1109/JDT.2007.900921

# A New Pixel Circuit Compensating for Brightness Variation in Large Size and High Resolution AMOLED Displays — Source link []

Hau-Yan Lu, Ting-Chang Chang, Ya-Hsiang Tai, Po-Tsun Liu ...+1 more authors Institutions: National Chiao Tung University, National Sun Yat-sen University Published on: 19 Nov 2007 - IEEEVOSA Journal of Display Technology (IEEE) Topics: AMOLED, Threshold voltage, OLED, Transistor and Voltage

Related papers:

- A Novel LTPS-TFT Pixel Circuit Compensating for TFT Threshold-Voltage Shift and OLED Degradation for AMOLED

- · A new four-transistor poly-si pixel circuit for AMOLED

- P-31: A New Threshold Voltage Compensation Technique of Poly-Si TFTs for AMOLED Display Pixel Circuit

- AMOLED Pixel Circuit With Electronic Compensation of Luminance Degradation

- Driving schemes for a-Si and LTPS AMOLED displays

# A New Pixel Circuit Compensating for Brightness Variation in Large Size and High Resolution AMOLED Displays

Hau-Yan Lu, Ting-Chang Chang, Ya-Hsiang Tai, Po-Tsun Liu, Senior Member, IEEE, and Sien Chi

Abstract—A new pixel design and driving method for active-matrix organic light-emitting diode (AMOLED) display using low-temperature polycrystalline silicon thin-film transistor (LTPS-TFT) is proposed. The new circuit consists of five TFTs and one capacitor to eliminate the variation in the threshold voltage of the TFTs, and the drop in the supply voltage in a single frame operation. The proposed pixel circuit has been verified to realize uniform output current by the simulation work using HSPICE software. The simulated error rate of the output current is also discussed in this paper. The novel pixel design has great potential for use in large size and high resolution AMOLED displays.

*Index Terms*—Active-matrix organic light-emitting diode (AMOLED), current–resistance (*I–R*) drop, pixel design, polycrystalline silicon thin-film transistors (poly-Si TFTs), uniformity.

## I. INTRODUCTION

CTIVE-MATRIX organic light-emitting diode (AMOLED) displays with polycrystalline silicon (poly-Si) thin-film transistors (TFTs) and amorphous silicon TFTs have been widely researched and developed because of its superior characteristics in flat displays. These advantages include wide viewing angle, high brightness, fast response time, compact, and light weight [1], [2]. However, it is difficult to implement an AMOLED panel with good image quality because of variations in the threshold voltage and in the mobility of poly-Si TFTs among pixels [3]. Several voltage modulation and current programming schemes have been devised to solve the nonuniformity problem [4]-[7]. The current programming methods can compensate both threshold voltage and mobility variation, these need very high addressing speed for high resolution displays. Although the a-Si backplanes for AMOLED displays exhibit uniform

T.-C. Chang is with the Department of Physics and Institute of Electro-Optical Engineering, National Sun Yat-Sen University, Kaohsiung 804, Taiwan, R.O.C. (e-mail: tcchang@mail.phys.nsysu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JDT.2007.900921

brightness, but it is seriously degraded from its initial value after the electrical stress. When a conventional 2-TFT pixel circuit is applied to AMOLED panel, the OLED current varies due to shift of threshold voltage of driving a-Si:H TFT and OLED. Therefore, various pixel circuits are reported in order to compensate the problem of threshold voltage shift in the driving a-Si:H TFT. However, the previous work using a-Si TFT for compensation circuits only solve the problem in the voltage shift of the driving TFT [8], [9]. Basically, the technology challenges to AMOLED display are distinct for a-Si and poly-Si TFT considerations.

The voltage driving method using poly-Si TFTs formulated by Dawson et al. may effectively compensate for threshold voltage variations. Furthermore the driving current in AMOLED panels and the number of scan lines should be increased with the panel size and the brightness in the high resolution and large size displays. The intrinsic display loading effects of a voltage drop across the parasitic resistance of the supply power line also causes nonuniformity of brightness in voltage-driven AMOLED panels. The drop in the supply voltage on the panel (Vdd infrared (IR) drop) is a critical issue leading to image degradation and crosstalk [10]. The use of AMOLED displays for large size applications is expected to have many advantages, so the driving method and pixel structure should be applicable to large size panels. However, most compensating pixel circuits with simple structures only solve one of the aforementioned problems [11], [12]. Some complicated designs have very uniform output current among pixels but these may reduce the aperture ratio or require additional peripheral driving circuits [13], [14].

This study develops a new driving method with source-follower type connection and the bootstrap, to improve the brightness variation due to the variations in the threshold voltage of the driving TFT and the drop in the supply voltage. The simulation results demonstrate that the variation in the current driving OLED among pixels can be significantly reduced.

# II. PROPOSED PIXEL STRUCTURE AND DRIVING METHOD

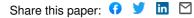

Fig. 1(a) shows the distribution of the threshold voltage among 600 p-channel poly-Si TFTs. The maximum shift of the threshold voltage is about 0.2 V, at a mean threshold voltage of -2.41 V. The electrical characteristics of 600 p-channel poly-Si TFTs had been measured and the threshold voltage of these TFTs were extracted at current density of 10 nA with normalized channel width (W)/channel length (L) ratio. This result confirms the necessity of threshold voltage variation

Manuscript received July 9, 2006; revised October 22, 2006. This work was supported by the MOE ATU Program, the National Science Council, Taiwan, R.O.C., under Contract NSC–96-2120-M-110-001, and supported in part by MOEA Technology Development for Academia Project 94-EC-17-A-07-S1-046.

H.-Y. Lu and S. Chi are with the Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsin-Chu 300, Taiwan, R.O.C.

Y.H. Tai and P.-T. Liu are with the Department of Photonics & Display Institute, National Chiao Tung University, Hsin-Chu 300, Taiwan, R.O.C.

Fig. 1. (a) The distribution of the threshold voltage among 600 TFTs and the maximum shift of the threshold voltage are about 0.2 V. (b) Circuit scheme of conventional pixel circuit (2T1C) and the voltage drop caused by the intrinsic parasitic resistance (R) at Vdd supply power line.

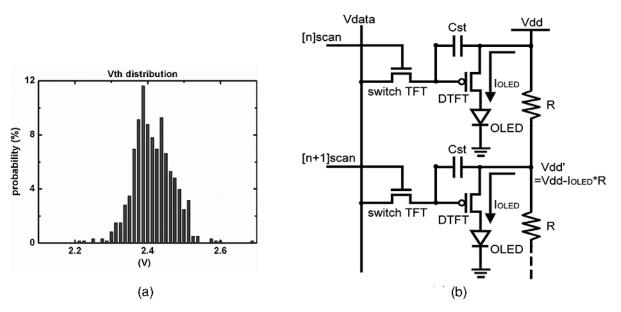

Fig. 2. Proposed pixel design and timing scheme of the signal line.

compensation for brightness uniformity of OLED pixels and gray level expression.

In the conventional architecture, the OLED is driven by the current generated by the potential difference between the gate and the source Vgs of the driving TFT (DTFT), given by |Vdata - Vdd|. However, the driving current that passes through the supply power electrode causes a voltage drop due to the parasitic resistance of the power line, as shown in Fig. 1(b). Even if the pixel circuit can compensate for the variation of the threshold voltage in the DTFT, the Vgs in each DTFT still varies from pixel to pixel along the electrode, generating various driving currents. This phenomenon causes the brightness to be nonuniform from the top to the bottom of the panel.

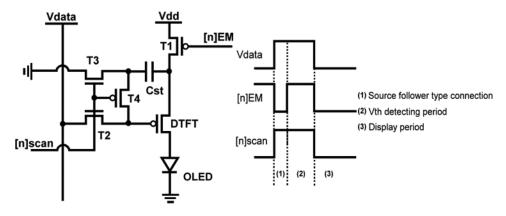

Fig. 2 show the proposed pixel circuit based on poly-Si TFTs and timing scheme of signal line. The design includes one driving TFT (DTFT), four switching TFT (T1, T2, T3, T4) and one capacitor (Cst). Vdata represents a voltage data signal line and Vdd refers to a constant voltage source line. The operation of the proposed circuit is divided into three stages shown in Fig. 3. During stage (1), source-follower type

connection, [n]Scan is set at the high level and [n]EM is set at the low level, respectively, to turn on T1, T2 and T3, so that the node voltage of DTFT connected to the right side of Cst is increased to Vdd, and this node becomes the source of DTFT. Therefore, the pixel circuit is a p-type source follower. The next stage is the Vth detecting period. Only [n]EM is set high to turn off T1 as scan[n] remains high. The source voltage of DTFT is discharged until it is turned off. This node voltage settles from Vdd to Vdata + Vth, where Vth is the threshold voltage of DTFT. Accordingly, the threshold voltage of DTFT and the data signal are stored in the right side of Cst. The left side of Cst is set to ground during stages (1) and (2) so that the drop voltage of Cst is Vdata + Vth. After the pixel scanning period, the third stage, the display period, is implemented. During stage (3), [n]scan and [n]EM are set to low to turn off T2 and T3, however, turn on T4 and T1 so that the gate of DTFT can be connected to the left side of Cst; the source voltage of DTFT is charged up to Vdd from Vdata + Vth. Immediately, the gate voltage of DTFT should be boosted to Vdd-Vdata-Vth by the conservation of charge in the ca-

Fig. 3. The equivalent circuit at each stage in operation.

pacitor as bootstrap is performed. Accordingly, DTFT starts to generate current (I<sub>OLED</sub>), driving the OLED. Cst sustains the gate voltage of DTFT, Vdd-Vdata-Vth, for the period of a frame. I<sub>OLED</sub> is also the saturation current of DTFT. This work focused on eliminating the brightness nonuniformity caused by the variation of the threshold voltage and the drop in supply voltage. The first-order current equation is directly affected by Vth and Vdd. And the minimum design rule for the channel length of TFT devices is 5  $\mu$ m, so that the second-order effect is not thereby considered in the proposed analysis. As a result, in this paper, the first-order equation is used to evaluate if the proposed circuit can exhibit high immunity to both voltage variation in poly-Si TFTs and the drop in the supply voltage.

$$I_{\text{OLED}} = K[\text{Vgs} - \text{Vt}]^2$$

=  $K[(\text{Vdd} - \text{Vdata} - \text{Vth}) - (\text{Vdd}) - (-\text{Vth})]^2$

=  $K[\text{Vdata}]^2$ .

Therefore,  $I_{OLED}$  is independent of the threshold voltage of DTFT and the supply voltage, and is affected only by data voltage. The threshold voltage variations and the drop in supply voltage can be both compensated effectively and uniform brightness image performance can be achieved.

#### **III. SIMULATION RESULTS**

The HSPICE software with the RPI poly-silicon TFT model (Level = 62) were used to verify the proposed circuit. The aspect ratio, mobility and threshold voltage of DTFT were 3.3/5,  $80 \text{ cm}^2/\text{V} \cdot \text{s}$  and -2 V. The Cst was set to 0.4 pF and Vdd were set as 9 V. The high and low level of the signals ([n]Scan and [n]EM) were set as 10 V to -10 V, respectively. The initial data voltage modulated such that the I<sub>OLED</sub> in the following cases was approximately 1  $\mu$ A as luminance and resolution were designed to be 300 Cd/m<sup>2</sup> and 133 PPI. In this work, the variation of the threshold voltage of DTFT is set as  $\pm 0.3 \text{ V}$  to evaluate the validation of this design in the worst case.

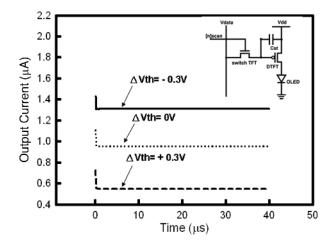

Fig. 4 plots simulation result for the conventional 2-TFTs and 1-capacitor pixel structure, when the threshold voltage of the driving TFT was set to -1.7 V, -2 V, and -2.3 V. The I<sub>OLED</sub> of the conventional 2-TFTs and 1-capacitor pixel structure is fluctuated with the variation of the threshold voltage of DTFT

Fig. 4. Transient simulation results for the conventional 2T1C pixel structure with the variation in the threshold voltage of DTFT.

very seriously. The variation range of  $I_{OLED}$  is about 1.3  $\sim$  0.55  $\mu$ A due to the variation of threshold voltage in the DTFT caused by process variation, nonuniform image quality over the display will become a critical issue.

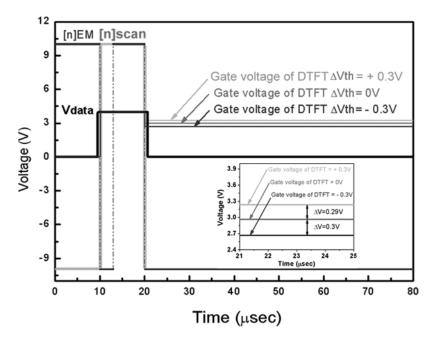

Fig. 5 verifies that the modulated data voltage and the threshold voltage of DTFT are stored in the right side of Cst as the threshold voltages are varied. The difference of the stored voltage in the capacitor almost equals the variation value in threshold voltage, namely, 0.3 V.

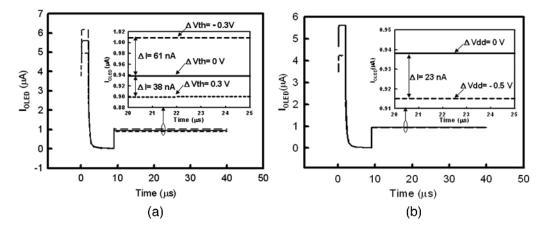

Fig. 6(a) plots the simulation result in  $I_{OLED}$  of the proposed design, when the threshold of the driving TFT was set to -1.7 V, -2 V and -2.3 V. The simulation results indicate that the variation of I<sub>OLED</sub> in the proposed pixel is clearly reduced using the adoption of the new threshold voltage compensation method. In a display period, the variation of I<sub>OLED</sub> in the proposed design is very small, being between around 1.01 and 0.99  $\mu$ A. Therefore the strong immunity to the variation of the threshold voltage in the DTFT in the proposed pixel structure is demonstrated. Fig. 6(b) shows that simulated degradation of the supply voltage on the panel is 0.5 V. According to Fig. 6(b), the deviation of  $I_{OLED}$  in the presented pixel structure is less than 2.5%, confirming the effectiveness of the prevention against the degradation of the supply voltage. The conventional 5 T pixel circuit proposed by Komiya is considered to compare the proposed one. [15] From the simulation result, the  $I_{OLED}$  degradation is 68.4% in the same simulation condition.

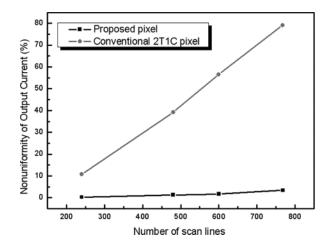

Fig. 7 shows the comparison of the  $I_{OLED}$  degradation in the conventional pixel structure (2T1C) with that in the proposed structure (5T1C), which is caused by the drop in the supply voltage as the number of scan lines increase (240, 480, 600, 768) [16]. The *y*-axis shows the non-uniformity of output current and the *x*-axis indicates the distance from the supply voltage point to each pixel by the number of scan lines. As increasing the number of scan lines for large size or high resolution AMOLED displays, the resistance of the power line leading to the larger supply voltage drop in the conventional 2T1C pixel design. In contrast, in the proposed 5T1C pixel design, the number of scan lines increases, and the maximum degradation of  $I_{OLED}$

Fig. 5. Gate voltage stored in the capacitor with varied threshold voltages of DTFT.

Fig. 6. (a) The transient simulation results for the proposed pixel structure. With the threshold voltage shift of DTFT set as  $\pm 0.3$  V, the variation of output current is about  $1.01 \sim 0.99 \,\mu$ A. (b) The transient simulation results for the proposed pixel structure. The deviation of I<sub>OLED</sub> in the proposed pixel structure is less than 2.5% in the degradation of the supply voltage on panel is 0.5 V.

Fig. 7. Comparison of nonuniformity of output current between the conventional pixel structure (2T1C) and the proposed one (5T1C), caused by the drop in supply voltage with increasing number of scan lines (240, 480, 600, 768).

is just approximately 3.1%. Therefore, the proposed pixel structure is a promising candidate for use in large size and high resolution AMOLED displays.

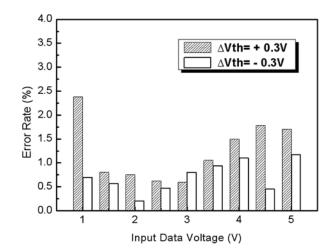

Fig. 8 shows the error rate of  $I_{OLED}$  in the proposed pixel circuit due to the threshold voltage variation. The output current errors of conventional 2T1C pixel circuit are all above 20% when input data voltage ranges 0.5–5 V, which is below 2.5% in proposed pixel circuit.

#### IV. CONCLUSION

A new voltage-modulation pixel circuit is developed for application to large size and high-resolution AMOLED displays. The nonuniformity of the output current is improved substantially using the proposed compensation operation. The average deviation of the TFT driving current is about 50 nA as the threshold voltage is varied by 0.3 V and the nonuniformity of the  $I_{OLED}$  with increasing number of the scan lines in the proposed pixel structure is less than 3.1%. Also the error rate of

Fig. 8. Error rate of output current in our proposed pixel circuit due to the threshold voltage variation. The error rate of output current with the proposed design is all less than 2.5% as input data voltage ranges 1-5 V.

the  $I_{OLED}$  with the threshold voltage variation is below 2.5%. The simulation results demonstrate successfully that the proposed circuit has high immunity to both the voltage variation in poly-Si TFTs and the drop in the supply voltage. Therefore, the proposed pixel structure is a promising candidate for the large size and high resolution AMOLED displays.

## ACKNOWLEDGMENT

The authors would like to thank AU Optronics Corporation (AUO), Hsinchu, Taiwan, R.O.C., and Dr. C. W. Chen for his discussions.

#### REFERENCES

- M. Kimura, I. Yudasaka, S. Kanbe, H. Kobayashi, H. Kiguchi, S. I. Seki, S. Miyashita, T. Shimoda, T. Ozawa, K. Kitawada, T. Nakazawa, W. Miyazawa, and H. Ohshima, "Low-temperature polysilicon thin-film transistor driving with integrated driver for high-resolution light emitting polymer display," *IEEE Trans. Electron Devices*, vol. 46, no. 12, pp. 2282–2288, Dec. 1999.

B. T. Chen, Y. J. Kuo, C. C. Pai, C. C. Tsai, H. C. Cheng, and Y. H. Tai,

- [2] B. T. Chen, Y. J. Kuo, C. C. Pai, C. C. Tsai, H. C. Cheng, and Y. H. Tai, "A new pixel circuit for driving organic light emitting diodes with low temperature polycrystalline thin film transistors," in *Proc. Int. Display Manuf. Conf.*, 2005, pp. 378–381.

- [3] V. W. C. Chan, P. C. H. Chan, and C. Yin, "The effect of grain boundaries in the electrical characteristics of large grain polycrystalline thin-film transistor," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1384–1391, Aug. 2002.

- [4] R. Dawson, Z. Shen, D. A. Furest, S. Connor, J. Hsu, M. G. Kane, R. G. Stewart, A. Ipri, C. N. King, P. J. Green, R. T. Flegal, S. Pearson, W. A. Tang, S. Van Slyke, F. Chen, J. Shi, M. H. Lu, and J. C. Sturm, "The impact of the transient response of organic light emitting diodes on the design of active matrix OLED displays," in *IEDM Tech. Dig.*, 1998, pp. 875–878.

- [5] S. H. Jung, W. J. Nam, and M. K. Han, "A new voltage-modulated amoled pixel design compensating for threshold voltage variation in poly-Si TFTs," *IEEE Electron Device Lett.*, vol. 25, no. 10, pp. 690–692, Oct. 2004.

- [6] T. Sasaoka, M. Sekiya, A. Yumoto, J. Yamada, T. Hirano, Y. Iwase, T. Yamada, T. Ishibashi, T. Mori, M. Asano, S. Tamura, and T. Urabe, "A 13.0-inch AMOLED display with top emitting structure and adaptive current mode programmed pixel circuit (TAC)," in *SID Tech. Dig.*, 2001, pp. 384–387.

- [7] J. C. Goh, C. K. Kim, and J. Jang, "A novel pixel circuit for active-matrix organic light-emitting diodes," in *SID Tech. Dig.*, 2003, pp. 494–497.

- [8] J. C. Goh, J. Jang, K. S. Cho, and C. K. Kim, "A new a-Si:H thin-film transistor pixel circuit for active-matrix organic light-emitting diodes," *IEEE Electron Device Lett.*, vol. 24, no. 9, pp. 583–585, Sep. 2003.

- [9] J. H. Lee, B. H. You, W. J. Nam, H. J. Lee, and M. K. Han, "A new a-Si:H TFT pixel design compensating threshold voltage degradation of TFT and OLED," in *SID Tech. Dig.*, 2007, pp. 264–267.

- [10] Y. C. Lin and H. P. D. Shieh, "Improvement of brightness uniformity by ac driving scheme for AMOLED display," *IEEE Electron Device Lett.*, vol. 25, no. 11, pp. 728–730, Nov. 2004.

- [11] J. C. Goh, H. J. Chung, J. Jang, and C. H. Han, "A new pixel circuit for active matrix organic light emitting diodes," *IEEE Electron Device Lett.*, vol. 23, no. 9, pp. 544–546, Sep. 2002.

- [12] Y. H. Tai, B. T. Chen, Y. J. Kuo, C. C. Tsai, K. Y. Chiang, Y. J. Wei, and H. C. Cheng, "A new pixel circuit for driving organic light-emitting diode with low temperature," *J. Display Technol.*, vol. 1, no. 1, pp. 100–104, Sep. 2005.

- [13] H. J. In, I. H. Jeong, J. S. Kang, O. K. Kwon, and H. K. Chung, "A novel feedback-type AMOLEDs driving method for large-size panel applications," in *SID'05 Tech. Dig.*, 2005, pp. 252–255.

- [14] H. Miyake, Y. Yamazaki, J. Koyama, M. Hayakawa, M. Osame, S. Seo, and S. Yamazaki, "A voltage driving AMOLED display with luminance control," in *SID'05 Tech. Dig.*, 2005, pp. 240–243.

- [15] N. Komiya, C. Y. Oh, K. M. Eom, J. T. Jeong, H. K. Chung, S. M. Choi, and O. K. Kwon, "Comparison of Vth compensation ability among voltage programming circuits for AMOLED panels," in *IDW '03 Tech. Dig.*, 2003, pp. 257–278.

- [16] M. Stewart, R. S. Howell, L. Pires, M. K. Hatalis, W. Howard, and O. Prache, "Polysilicon VGA active matrix OLED displays-technology and performance," in *IEDM Tech. Dig.*, 1998, pp. 871–874.

Hau-Yan Lu was born in Taiwan, R.O.C., in 1980. He received the B.S. degree from the Department of Physics from National Sun Yat-sen University, Kaohsiung, Taiwan, R.O.C., in 2002. He is currently pursuing the Ph.D. degree in Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsin-Chu, Taiwan, R.O.C.

Currently, his research interests focus on low-temperature poly-Si TFTs driving circuits for AMLCDs and AMOLEDs, reliability and device characteristics of poly-Si TFTs.

**Ting-Chang Chang** is a chair professor in Department of Physics, National Sun Yat-Sen University. In his specialty, he has made pioneering contributions to semiconductor device technology, ULSI memory devices and TFT-LCD Displays. He has published 150 articles in SCI journals and obtained 28 U.S. and 70 Taiwan patents. He proposed the project of Industry-Academy Cooperation with United Micoelectronics Corporation to research nano-porous low-k materials for ULSI application, and received great progress and achievement. He thereby had the honor to win the "Award of Industry-Academy Cooperation" from Ministry of Education in 2002. This is a remarkable honor in academic achievement. Currently, his interests are in the study of nonvolatile memory devices and nano-dot technology.

Ya-Hsiang Tai received the B.S. and Ph.D. degrees in electronic engineering from National Chiao Tung University, Hsinchu, Taiwan, R.O.C., in 1990 and 1996, respectively.

He became a member of Industrial Technology Research Institute/Electronics Research & Service Organization and the TFT LCD development as a panel designer. He joined the project of low temperature polycrystalline silicon (LTPS) thin-film transistor (TFT) development in Prime View International in 2000. In 2001, he entered Toppoly

Optoelectronics Corporation, Taiwan, R.O.C., to lead the team of LTPS TFT LCD panel design. He joined the faculty of National Chiao Tung University in 2003, where he is currently an assistant professor in the Department of Photonics and Display Institute. His current research emphases are in the areas of TFT device physics, active matrix display panel design, and system on panel.

Dr. Tai is a member of Phi Tau Phi.

**Po-Tsun Liu** (SM'07) received the Ph.D. degree in the Institute of Electronics from the National Chiao Tung University in January 2000.

He joined the NationalNano Device Laboratory (NDL), Taiwan, as an associate researcher from January 2000, and became the leader of Department of Electro-optics and Bio-technology in March 2004. He has made a great deal of pioneering contributions to low-permittivity (low-k) dielectrics, copper interconnects and thin film transistors (TFTs) technologies. In his research on low-k dielectrics, he utilized plasma treatment technique for the first time to improve electrical characteristics of low-k silicate materials. In addition, he and his collaborators developed a novel technology to pattern low-k materials directly by using electron-beam lithography and X-ray radiation technology, instead of typically used photoresist coating and etch processing. He joined the faculty of National Chiao Tung University (NCTU) as an associate professor at the Department of Photonics and Display Institute on October in 2004. His main research focuses on the flat panel display (FPD) technologies, specialized in thin film transistors (TFTs), the advanced nano-scale semiconductor device technology, nanocrystal nonvolatile memory devices, and nano-fabrication technologies. To date, he has published 100 articles of SCI international journals, 51 international conference papers, and obtained 52 U.S. and Taiwan patents.

Dr. Lu is a member of the Society for Information Display. Because of the prominent contributions, he was selected in Marquis Who's Who in the World (20th edition, 2003).

**Sien Chi** received the B.S.E.E. degree from National Taiwan University, Taipei, Taiwan, R.O.C., and the M.S.E.E. degree from National Chiao-Tung University, Hsinchu, Taiwan, in 1959 and 1961, respectively, and the Ph.D. degree in electro-physics from Polytechnic Institute, Brooklyn, NY, in 1971.

From 1971 to 2004, he was a Professor at National Chiao-Tung University. He is currently a Chair Professor at Yuan-Ze University, Chung Li, Taiwan, R.O. C. His research interests are optical-fiber communications, optical solitons, optical modulation format, and optical-fiber amplifiers. From 1998 to 2001, he was the Vice President of the National Chiao-Tung University.

Dr. Chi is a Fellow of both the Optical Society of America (OSA) and the Photonics Society of Chinese Americans (PSCA). He was the Symposium Chair of the International Symposium of Optoelectronics in Computers, Communications, and Control, in 1992, which was coorganized by the National Chiao-Tung University and The International Society for Optical Engineers (SPIE). Since 1996, he has been the Chair Professor of the Foundation for Advancement of Outstanding Scholarship.