Received March 4, 2022, accepted March 24, 2022, date of publication March 30, 2022, date of current version April 8, 2022. *Digital Object Identifier* 10.1109/ACCESS.2022.3163262

# A New Single-Source Nine-Level Quadruple Boost Inverter (NQBI) for PV Application

ASHUTOSH KUMAR SINGH<sup>®1</sup>, (Member, IEEE), RAVI RAUSHAN<sup>®2</sup>, (Member, IEEE), RAJIB KUMAR MANDAL<sup>®1</sup>, AND MD. WASEEM AHMAD<sup>®2</sup>

<sup>1</sup>Department of Electrical Engineering, National Institute of Technology Patna, Patna, Bihar 800005, India

<sup>2</sup>Department of Electrical and Electronics Engineering, National Institute of Technology Karnataka, Surathkal, Karnataka 575025, India

Corresponding author: Ashutosh Kumar Singh (ashutoshk.phd19.ee@nitp.ac.in)

This work was supported by the Science and Engineering Research Board, Government of India, under Project Number SRG/2021/001834.

**ABSTRACT** Multi-level inverters (MLIs) with switched capacitors are becoming popular due to their utilization in AC high-voltage applications as well as in the field of renewable energy. To achieve the required magnitude of output voltage, the switched capacitor (SC) technique employs a lesser number of DC sources in accordance with the voltage across the capacitor. Designing an efficient high-gain MLI with fewer sources and switches needs a rigorous effort. This paper introduces a prototype of a nine-level quadruple boost inverter (NQBI) topology powered by one solar photo-voltaic source using fewer capacitors, switches, and diodes when compared to the other SC-MLIs topology. The suggested NQB inverter produces nine levels of voltage in its output by efficiently balancing the voltages of the two capacitors. The various SC-MLIs are compared in order to highlight the benefits and drawbacks of the proposed nine-level quadruple boost inverter (NQBI) topology. To validate the efficacy of the proposed solar photovoltaic based NQBI without grid connection, detailed experimental results are presented in a laboratory setting under various test conditions.

**INDEX TERMS** NQBI, reduced switch count, switched capacitor inverter, SPWM technique.

# I. INTRODUCTION

Multi-level inverters (MLIs) are the most popular means for voltage conversion from DC to AC power, and are used in fuel cell and photo-voltaic (PV) based sustainable or renewable energy systems (RES). The core advantages of MLIs include, higher voltage output with minimal switch stress voltage, lowered dv/dt, and a better output voltage harmonic profile. Over the last few decades, the three most common forms of MLIs have been proposed: the flying capacitor (FC) topology, the diode clamped neutral point clamped (NPC) topology, and the cascaded H-bridge (CHB) topology. In order to maintain the voltage balance of capacitors, external hardware circuits and complex control algorithms are needed in the case of the FC-MLI and NPC-MLI topologies. In CHB-MLI, a large number of DC sources are employed, which results in a higher number of output voltage levels. While implementing the MLI with RES, voltage boosting is expected to achieve the higher output voltage. A dc-dc boost converter or transformer is required to achieve the desired higher output voltage. These components results in complex, large, and costly inverter

The associate editor coordinating the review of this manuscript and approving it for publication was Alon Kuperman<sup>(D)</sup>.

systems [1]–[5]. Multilevel inverters based on the SC principle have been identified as a recent advancement to address the aforementioned shortcomings [6]–[18].

The SC-MLIs boost the input voltage along with an increased number of output voltage levels. In [6], a single isolated DC source was proposed without the need for an H-bridge. The individual switches in [6] are subjected to less voltage stress, but as the voltage level rises, the number of capacitors and power electronics switches also increases.

The SC-MLI topologies proposed in [7], [8] have inherent capacitor voltage balancing and boosting abilities and are suggested for renewable energy conversion due to low voltage stress. Though both topologies has same number output voltage levels and switch count, [7] uses one additional capacitor than [8] to develop better voltage boost.

A nine-level H-bridge based switched capacitor inverter and its three-phase application is also explored in [17]. The inverter topology has self capacitor voltage balance capacity but lacks the boosting ability. Three nine-level SC-based inverters with a single source topology have been suggested in [9], [10], [18], in which capacitor voltage balance is performed without complicated circuits or auxiliary power. On the other hand, the voltage multiplication factor for them

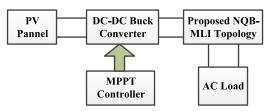

**FIGURE 1.** Schematic diagram of proposed inverter based off-grid PV system with AC loads.

is two. The converter with a voltage multiplication factor of four is suggested in [11]. This topology uses fewer power electronics switches, but the number of capacitors and diodes is more. In [12], the SC-MLI uses a single isolated DC source for a quadruple boost in the output voltage, but the topology requires more switching devices. Several topologies having a wide range of higher voltage applications are mentioned in [13]–[16]; however, they require more components to produce a (9-L) output voltage. The cost of inverter topology and losses increases with an increase in the number of components. This work proposes a nine-level quadruple boost inverter (NQBI) topology to resolve the shortcomings of the traditional topologies established in previous research. The significant benefits of the proposed topology are mentioned below:

- In the NQBI topology, the amplitude of the output voltage can be attained up to four times the voltage magnitude of the DC source.

- The NQBI topology has self-voltage balancing capability. Hence, no extra hardware circuits are required to control the capacitor voltage.

- The NQBI topology can be connected with a load having a standard range of power factor.

- The NQB inverter is designed with a significantly reduced component count.

The structure of this paper is as follows: In Section II, the design and operation of the proposed inverter are discussed. Section III compares the performance of the proposed topology with the other states of SC-MLI. The experimental results are presented in Section IV. Section V gives the conclusion of the paper.

# **II. PROPOSED NQBI TOPOLOGY BASED PV SYSTEM**

The proposed system using NQBI for an off-grid solar photovoltaic application is shown in FIGURE 1. The DC-DC buck converter is connected to the PV output, and the maximum power point tracking (MPPT) method is implemented to obtain the maximum output power. The suggested NQBI configuration is depicted in FIGURE 2. The proposed MLI can produce a 9-L output voltage with a quadruple boost in the output voltage and requires only ten power electronics switches.

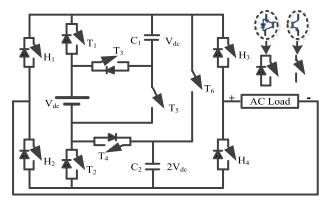

This inverter topology has a level-generating part, which can provide four voltage levels by quadruple boosting and employing two capacitors,  $C_1$  and  $C_2$  with a voltage rating of  $V_{dc}$  and  $2V_{dc}$ , respectively, as seen in Figure 2. The switches

FIGURE 2. Proposed NQBI topology.

TABLE 1. The switching states, output voltage and state of capacitors of the proposed NQBI.

| T <sub>1</sub> | T <sub>2</sub> | T3 | $T_4$ | $T_5$ | T <sub>6</sub> | $H_1$ | H <sub>2</sub> | H <sub>3</sub> | $H_4$ | $V_0(xV_{dc})$ | $C_1$ | C <sub>2</sub> |

|----------------|----------------|----|-------|-------|----------------|-------|----------------|----------------|-------|----------------|-------|----------------|

| 0              | 0              | 1  | 1     | 0     | 0              | 0     | 1              | 1              | 0     | 4              | D     | D              |

| 1              | 0              | 0  | 1     | 1     | 0              | 0     | 1              | 1              | 0     | 3              | С     | D              |

| 0              | 1              | 1  | 0     | 0     | 1              | 0     | 1              | 1              | 0     | 2              | D     | С              |

| 1              | 1              | 0  | 0     | 1     | 0              | 0     | 1              | 1              | 0     | 1              | С     | -              |

| 1              | 0              | 0  | 0     | 1     | 0              | 1     | 0              | 1              | 0     | Zero           | C     | _              |

| 1              | 0              | 0  | 0     | 1     | 0              | 0     | 1              | 0              | 1     | Zero           | C .   | -              |

| 1              | 1              | 0  | 0     | 1     | 0              | 1     | 0              | 0              | 1     | -1             | С     | -              |

| 0              | 1              | 1  | 0     | 0     | 1              | 1     | 0              | 0              | 1     | -2             | D     | С              |

| 1              | 0              | 0  | 1     | 1     | 0              | 1     | 0              | 0              | 1     | -3             | С     | D              |

| 0              | 0              | 1  | 1     | 0     | 0              | 1     | 0              | 0              | 1     | -4             | D     | D              |

Where: 0/1 = OFF/ON switch, '-' = capacitor constant voltage, D/C = discharging/charging of capacitor.

$T_5$  and  $T_6$  are configured as reverse blocking switches to prevent the unnecessary discharge of the capacitors  $C_1$  and  $C_2$ . The alternating polarity can be generated by the polarity generating part composed of four switches  $H_1$ ,  $H_2$ ,  $H_3$  and  $H_4$ . Table1 shows the possible switching states and modes of capacitors to achieve the nine-level AC output voltage.

# A. ANALYSIS OF SELF VOLTAGE BALANCE AND CAPACITANCE OF C $_1$ AND C $_2$

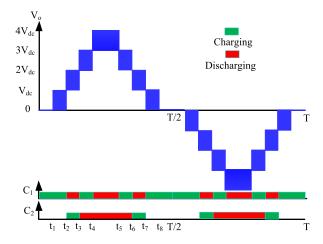

The proposed NQBI has self voltage balancing ability as it implements serial-parallel linking technique for charging and discharging of capacitors C<sub>1</sub> and C<sub>2</sub>. The capacitor C<sub>1</sub> gets connected to DC source and charged upto V<sub>dc</sub> when T<sub>1</sub> and T<sub>5</sub> are simultaneously in on-state during  $\pm 0, \pm V_{dc}$  and  $\pm 3V_{dc}$  output voltage level as shown in TABLE 1. The capacitor C<sub>1</sub> is connected in series with DC source and the capacitor  $C_2$  gets connected in parallel when  $T_2$ ,  $T_3$  and  $T_6$  are in ON state. The capacitor C1 discharges while capacitor C2 charges upto  $2V_{dc}$  during  $\pm V_{dc}$  output voltage level. Both capacitors (C<sub>1</sub> & C<sub>2</sub>) and DC source are connected in series when T<sub>2</sub>,  $T_4$  are simultaneously turned on and  $\pm 4V_{dc}$  voltage level is attained. FIGURE 3 displays the charging and discharging patterns of  $C_1$  and  $C_2$  for one cycle of output voltage. The capacitor voltage of C1 and C2 starts to reduce from the nominal value under discharging mode of operation. The overall capacitance value C1 and C2 needed for an appropriate ripple of voltages ( $\Delta V$ ), peak load current ( $I_{o, peak}$ ), frequency of output voltage and corresponding maximum discharge time

FIGURE 3. Output voltage and charging pattern of capacitors.

FIGURE 4. LS-PWM modulation technique.

of  $\Delta T_1$  and  $\Delta T_2$  are as follows:

$$C_{1} = \frac{I_{\text{o,peak}}}{\pi \times f \times \Delta V} \times \Delta T_{1}$$

$$C_{2} = \frac{I_{\text{o,peak}}}{\pi \times f \times \Delta V} \times \Delta T_{2}$$

(1)

where  $\Delta T_1 = t_5 - t_4$  is the interval of the voltage level  $4V_{dc}$ and  $\Delta T_2 = t_6 - t_3$  is the interval of the voltage level of  $(3V_{dc}$ and  $4V_{dc})$  [11].

### **B. PULSED-WIDTH MODULATION TECHNIQUE**

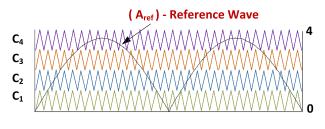

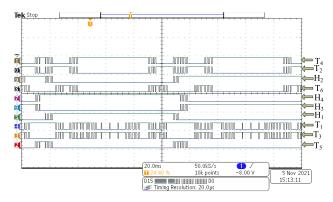

The NQBI is being controlled with sinusoidal pulse-width modulation, in which a sinusoidal reference signal ( $v_{ref}$ ) of required amplitude ( $v_m$ ) is simultaneously compared with eight level-shifted carrier waves of equal amplitude ( $A_C$ ) as depicted in FIGURE 4. The generated gate-pulses for the proposed NQBI is shown in the FIGURE 5. The magnitude of the reference signal varies according to the modulation index to obtain the desired magnitude of output voltage. The modulation index is expressed as follows:

$$M_{\rm i} = \frac{v_{\rm m}}{4A_{\rm C}}.$$

(2)

# C. POWER LOSS ANALYSIS OF THE PROPOSED NQBI TOPOLOGY

The losses in the inverter occur due to the existing non-idealities in the inverter components. Three types of major losses occurring in the proposed NQBI are switching

FIGURE 5. Gate-pulses for the proposed nine-level inverter.

losses ( $P_{sw}$ ), conduction losses ( $P_c$ ) and ripple losses ( $P_{ripple}$ ) considered. Hence, total power loss ( $P_{loss}$ ) occurring in the NQBI is

$$P_{\text{loss}} = P_c + P_{sw} + P_{\text{ripple}} \tag{3}$$

During each switching transition, the voltage and current overlap due to intrinsic delays in the switching of IGBT, which leads to switching loss. It can be expressed as:

$$P_{sw} = \sum_{\text{switches}} \sum_{\text{within } 1/f_o} \left( \frac{V_{\text{on}} \times I_{\text{on}} \times T_{\text{on}}}{6} + \frac{V_{\text{off}} \times I_{\text{off}} \times T_{\text{off}}}{6} \right) \times f_{sw} \quad (4)$$

where,  $V_{on}$  is the voltage across the IGBT in the pre-ON state. The current that flows through the power switch after it has been turned on is referred to as  $I_{on}$ .  $T_{on}$  is the time span during which the ON state is in transition. The voltage across the power switch, the current that runs through a power switch before the transition to the OFF state, and the transition duration of the OFF state are  $V_{off}$ ,  $I_{off}$ , and  $T_{off}$  respectively. The switching frequency and the frequency of the fundamental output voltage are denoted by  $f_0$  and  $f_{fsw}$  respectively.

Conduction losses are power losses that occur as a result of the internal resistance provided by the switch while the switch is in the conduction mode, and can be expressed as

$$P_c = \sum_{\text{all switches}} I_{switch}^2 \times R_{\text{on}}$$

(5)

In which  $I_{switch}$  is the amount of current that flows through a switch with an internal resistance of  $R_{on}$ .

The ripple losses caused by the charging and discharging of the capacitors are also a significant component in the overall power loss of the SC-MLI. It is possible to lose power when the parallel capacitor connected to the DC source is charged. The charging current flows through the capacitor and, as a result of a difference between the input source and the capacitor voltage, the ripple voltage  $\Delta V_{\rm C}$  results, which causes the power loss. The ripple power loss of a capacitor can be computed using the following formula:

$$P_{\text{ripple}} = \sum_{\text{all capacitors}} C \times \Delta V_C^2 \times f_{sw}$$

(6)

TABLE 2. Proposed NQBI topology of power loss profile.

| Power loss of               | Psw    | P <sub>con</sub> | Ploss  |

|-----------------------------|--------|------------------|--------|

| $H_1$ (W)                   | 0.015  | 0.62             | 0.635  |

| - ( )                       |        |                  |        |

| $H_2$ (W)                   | 0.015  | 0.61             | 0.625  |

| $H_3$ (W)                   | 0.0044 | 0.602            | 0.6064 |

| $H_4$ (W)                   | 0.0044 | 0.603            | 0.6074 |

| $T_1$ (W)                   | 0.047  | 1.11             | 1.157  |

| $T_2$ (W)                   | 0.113  | 1.56             | 1.674  |

| $T_3$ (W)                   | 0.136  | 1.56             | 1.696  |

| $T_4$ (W)                   | 0.05   | 0.75             | 0.8    |

| $T_5$ (W)                   | 0.074  | 0.55             | 0.624  |

| $T_6$ (W)                   | 0.076  | 0.45             | 0.526  |

| $C_1$ (W)                   | 1.11   |                  |        |

| $C_2$ (W)                   | 3.44   |                  |        |

| P <sub>Total loss</sub> (W) | 13.5   |                  |        |

| Output power (W)            | 500    |                  |        |

| Efficiency (%)              | 97.3   |                  |        |

The component-wise power loss for the proposed inverter at an output power of 0.5 kW has been listed in Table 2. The proposed NQB inverter exhibits 97.3 efficiency at 0.5kW output power.

#### **III. COMPARATIVE ANALYSIS**

The voltage boosting capability of the proposed topology, along with nine voltage levels at the output terminal, makes it a suitable candidate for injecting high power quality into the load/grid.

A comparison is carried out with the other MLI topologies that can produce quadruple voltage at their terminals, and the result is shown in the TABLE 3. As evident from the table, topologies suggested in [11] and [15] requires fewer active switches, but the number of diodes is greater than the proposed NQBI topology. Furthermore, the proposed topology has two capacitors of  $V_{dc}$  and  $2V_{dc}$  rating for quadruple voltage increase, while the topology of [11] requires two capacitors of  $2V_{dc}$  rating and one capacitor of  $V_{dc}$  rating. Having a greater number of capacitors in an MLI leads to an increase in cost and difficulty managing charging and discharging. The topology suggested in [12] requires two capacitors but at the expense of twelve active switches, as against ten active switches required in the proposed inverter.

Another important benchmark for comparison of SC topologies is the number of conducting power electronic components in the loading of capacitors, i.e. the NSC. In order to accommodate the charge current of the capacitor, equipment in the charging loop must be of greater current rating. The proposed topology would need only four devices with higher current ratings. Topologies proposed in [6], [9], [11]–[16] requires more devices in the loading loop, resulting in higher costs and losses as compared to the proposed topology in this paper. The total number of power electronic devices conducting (TCD) at each voltage level is also considered for comparison. Furthermore, from TABLE 3, it can be inferred that during the inverter's operation of the proposed NQBI, a minimum number of conduction devices is required at any stage compared to other state-of-the-art topologies. The total average standing voltage per unit (TSV<sub>pu</sub>) of the proposed

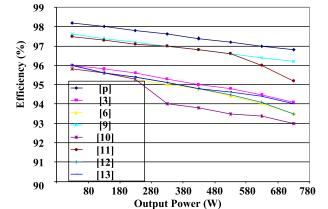

FIGURE 6. Calculated efficiency comparison of proposed nine-level inverter with existing inverter topologies.

inverter is greater than that of other MLIs, except for [15]. The proposed NQBI's cost function (CF) can be defined as:

$$CF = N_{sw} + N_c \left( 1 \times N_{C-V_{dc}} + 2 \times N_{C-2V_{dc}} \right) + N_{sc} + N_d + \alpha * TSV_{pu} + \beta * TCD_{avg}$$

(7)

where weight coefficients of  $TSV_{pu}$  and  $TCD_{avg}$  are  $\alpha$  and  $\beta$  respectively. The CF is regulated by the expense of the power electronic switches, capacitors, and gate driver circuits.

TABLE 3 enlist CF of various typologies for different values of weight coefficient  $\alpha$  and  $\beta$ . The CF value of the proposed NQB-MLI is found to be less than that of other MLIs. Different topologies are modelled in PLECS programme with specification:  $V_{dc} = 30V$ ,  $C = 4700\mu$ F and carrier frequency=5kHz. FIGURE 6 shows the efficiency of different topologies with various loading conditions. The maximum efficiency of the suggested topology is 98.2 %, as evident from FIGURE 6. Moreover, because of the lower component count of lower voltage ratings and lesser conduction losses, the performance of the suggested NQB-MLI is found to be better than all other topologies.

# IV. HARDWARE IMPLEMENTATION AND RESULTS ANALYSIS

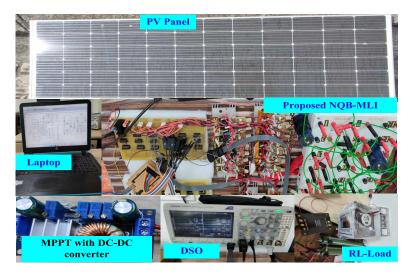

A laboratory prototype of the proposed NQBI-based standalone solar PV system was developed to validate its operations as shown in FIGURE 7.

The specifications of the components utilised to design the proposed NQBI are listed in TABLE 4. The detailed specifications of the solar panel considered as a source are represented in TABLE 5. The technical details of the DC-DC constant voltage constant current MPPT converter utilized for the realization of the proposed system are shown in TABLE 6.

The R-C based circuit is designed to introduce a dead time of 0.002 ms between the switches in the same leg to avoid the resulting shoot-through current through them.

The switching pulse generated at unity modulation index (MI) under level shifted PWM is fed to the respective switches of NQBI and corresponding voltage and current

| Topology N <sub>sw</sub> N <sub>gd</sub> N <sub>d</sub> N <sub>com</sub> |      | Nc   | N VC |       | Nsc  | TSV <sub>p.u.</sub> | TCD              |      |           |              | CF (with value of $\alpha$ and $\beta$ ) |              |                     |                    | G        |          |          |          |   |

|--------------------------------------------------------------------------|------|------|------|-------|------|---------------------|------------------|------|-----------|--------------|------------------------------------------|--------------|---------------------|--------------------|----------|----------|----------|----------|---|

| Topology                                                                 | INSW | 1 gd | 1°d  | 1 Com | INC. | V <sub>dc</sub>     | 2V <sub>dc</sub> | 1 sc | 15 v p.u. | $\pm 1^{st}$ | $\pm 2^{nd}$                             | $\pm 3^{rd}$ | $\pm 4^{\text{th}}$ | TCD <sub>avg</sub> | 0.5, 0.5 | 1.0, 1.0 | 1.5, 0.5 | 0.5, 1.5 |   |

| [6]                                                                      | 17   | 17   | 0    | 17    | 3    | 3                   | 0                | 9    | 5.5       | 8            | 8                                        | 8            | 8                   | 8                  | 35.75    | 42.5     | 41.25    | 43.75    | 4 |

| [11]                                                                     | 8    | 8    | 3    | 11    | 3    | 1                   | 2                | 6    | 5.75      | 5            | 5                                        | 5            | 5                   | 5                  | 27.375   | 32.75    | 33.125   | 32.375   | 4 |

| [12]                                                                     | 12   | 12   | 0    | 12    | 2    | 1                   | 1                | 6    | 5.25      | 6            | 7                                        | 6            | 6.5                 | 6.5                | 26.875   | 32.75    | 32.125   | 33.375   | 4 |

| [13]                                                                     | 17   | 17   | 5    | 22    | 4    | 4                   | 0                | 12   | 5.5       | 10           | 9.5                                      | 8.5          | 8.5                 | 9                  | 45.25    | 52.5     | 50.75    | 54.25    | 4 |

| [14]                                                                     | 13   | 13   | 0    | 13    | 3    | 3                   | 0                | 6    | 6.25      | 8            | 7                                        | 6            | 5                   | 6.5                | 28.375   | 34.75    | 34.625   | 34.875   | 4 |

| [15]                                                                     | 8    | 8    | 6    | 14    | 3    | 3                   | 0                | 6    | 8         | 8            | 4                                        | 5            | 5                   | 5.5                | 29.75    | 36.5     | 37.75    | 35.25    | 4 |

| [16]                                                                     | 10   | 10   | 3    | 13    | 3    | 3                   | 0                | 6    | 6.25      | 8            | 5                                        | 5            | 5                   | 5.75               | 28       | 34       | 34.25    | 33.75    | 4 |

| [9]                                                                      | 10   | 10   | 1    | 11    | 2    | 2                   | 0                | 3    | 5.75      | 5            | 5                                        | 5            | 4                   | 4.75               | 21.25    | 26.5     | 29.37    | 28.87    | 2 |

| [17]                                                                     | 8    | 8    | 2    | 10    | 3    | 3                   | 0                | 3    | 5         | 5            | 4                                        | 6            | 5                   | 5                  | 29.5     | 42       | 49.5     | 34.5     | 2 |

| [18]                                                                     | 10   | 10   | 1    | 11    | 2    | 1                   | 1                | 3    | 5.55      | 5            | 4                                        | 5            | 5                   | 4.75               | 20.25    | 25.50    | 28.37    | 27.87    | 2 |

| Proposed NQBI                                                            | 10   | 10   | 0    | 10    | 2    | 1                   | 1                | 3    | 6.25      | 5            | 5                                        | 5            | 4                   | 4.75               | 20.25    | 25.50    | 28.37    | 27.87    | 4 |

## TABLE 3. Comparison of various topologies with the proposed NQB-MLI topology.

$N_{sw}$ =Quantity of power electronics switches,  $N_{gd}$ =Quantity of gate driver circuits,  $N_d$ =Quantity of additional diodes,  $N_{com}$ =Sum of  $N_{sw}$  and  $N_d$ ,  $N_c$ =Quantity of capacitor,  $V_C$  = Capacitor voltage rating,  $N_{sc}$  = Quantity of devices conducting in charging capacitors,  $TSV_{p.u.}$  = Total standing voltage in per unit, G= Gain, and TCD = Total conducting device.

FIGURE 7. Experimental prototype of the proposed NQBI topology.

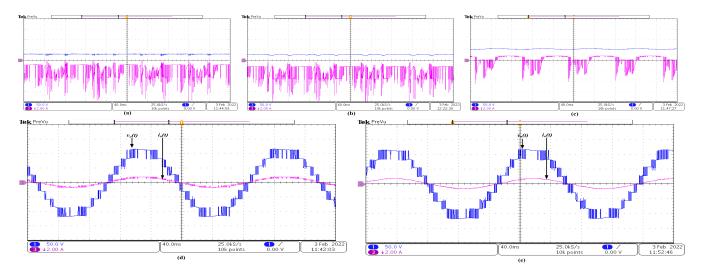

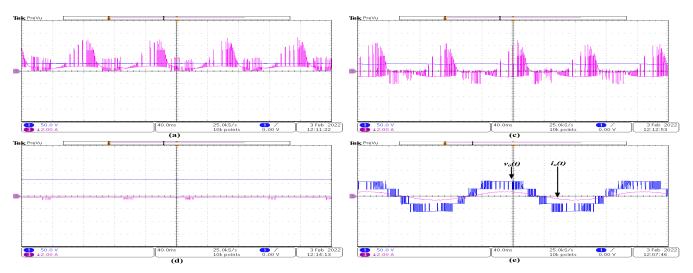

**FIGURE 8.** Experimental waveforms at modulation index 1 (a) Output vol the DC-DC converter, (b) capacitor voltage  $V_{C1}$ , (c) capacitor voltage  $V_{C2}$  (d)output voltage and current at  $Z_L = 160\Omega$  and (e) output voltage and current at  $Z_L = 160\Omega + 200 \text{ mH}$ .

waveform of the DC/DC converter, switched capacitors ( $C_1$  and  $C_2$ ) and the output of inverter are presented in FIGURE 8. The output of the DC-DC converter acting as the DC source for the proposed NQBI is 30 V. It is observed from FIGURE 8 that the voltage across capacitor  $C_1$  ( $V_{C1}$ ) matches the voltage of the DC source, while the voltage across capacitor  $C_2$  ( $V_{C2}$ )

FIGURE 9. Experimental waveforms at modulation index 0.5 (a) Output vol the DC-DC converter, (b) capacitor voltage  $V_{C1}$ , (c) capacitor voltage  $V_{C2}$  (d) output voltage and current at  $Z_L = 80\Omega + 200 \text{ mH}$ .

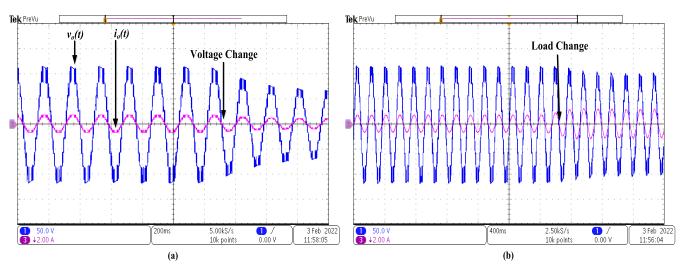

FIGURE 10. Experimental waveforms of (a) output voltage and current Output under voltage variation of DC -DC converter from 30V to 18V and (b) output voltage and current under load variation from  $Z_{L1} = 160\Omega + 200 \text{ mH}$  to  $Z_{L2} = 80\Omega + 200 \text{ mH}$ .

TABLE 4. Detailed specifications for the design of NQBI topology.

| IGBT Switches       | CT60AM 18F IGBT               |

|---------------------|-------------------------------|

| Controller          | Arduino mega 2560             |

| Optocoupler         | TLP250                        |

| $C_1$ and $C_2$     | $1000 \mu F$ and $2000 \mu F$ |

| Resistive load      | 0-160 Ω                       |

| Inductive load      | 0-200 mH                      |

| Carrier frequency   | 5KHz                          |

| Reference frequency | 50Hz                          |

| dead time           | 0.002ms                       |

|                     |                               |

holds twice the voltage across C<sub>1</sub>. The capacitor voltage for both switched capacitors C<sub>1</sub> and C<sub>1</sub> is seen to be balanced. The output voltage  $(v_0(t))$  and current  $(i_0(t))$  waveform for resistive load  $(Z_L = 80\Omega)$  is shown in FIGURE 8 (d). It is observed that the  $v_0(t)$  waveform has nine levels and  $i_0(t)$ is in phase with  $v_0(t)$ . Moreover, the output voltage  $(v_0(t))$

#### TABLE 5. Specification for the solar panel.

| Output Power          | 375 Watts        |

|-----------------------|------------------|

| Panel Technology      | Mono Crystalline |

| voltage at max power  | 39.00 volts      |

| current at max power  | 9.62 amps        |

| open circuit voltage  | 44.50 volts      |

| short circuit current | 9.90 amps        |

waveform and current  $(i_0(t))$  waveform for resistive-inductive load  $(Z_L = 80\Omega + 200 \text{ mH})$  is shown in FIGURE 8 (e). It is observed that the current  $i_0(t)$  lags behind the voltage  $v_0(t)$ by some phase-angle.

To further verify the operation of proposed NQB inverter at lower modulation index (say 0.5), the voltage and current waveform of the DC/DC converter, switched capacitors ( $C_1$ and  $C_2$ ) and the output of inverter is obtained and represented in FIGURE 9. The voltage and current waveform of the

FIGURE 11. Blocking voltages across switches.

TABLE 6. Technical specification of DC-DC constant voltage constant current MPPT controller.

| Input voltage               | 6-36V            |

|-----------------------------|------------------|

|                             | 6-36V            |

| MPPT voltage setting range  |                  |

| Output current range        | 0.05-5A          |

| Operating temperature       | -40 to 85 degree |

| Operating frequency         | 180 KHz          |

| Conversion efficiency       | up to 95%        |

| Short circuit protection    | Yes              |

| Over temperature protection | Yes              |

capacitors show that only C<sub>1</sub> is engaged actively. The reduced output voltage ( $v_0(t)$ ) with five levels and respective current ( $i_0(t)$ ) waveform for resistive-inductive load ( $Z_L = 80\Omega + 200mH$ ) is shown in FIGURE 9 (d).

FIGURE 10 illustrates the inverter output waveforms for dynamic source and load conditions at unity modulation index. FIGURE 10(a) shows the voltage  $(v_0(t))$  and current  $(i_0(t))$  waveform when the resistive-inductive load is changing from  $Z_{L1} = 160\Omega + 200 \text{ mH}$  to  $Z_{L2} = 80\Omega + 200 \text{ mH}$ . It is observed that the magnitude of load current increases as the impedance decreases. The phase difference between  $v_0(t)$  and  $i_0(t)$  also varies accordingly. In addition to that FIGURE 10 (b) shows the output voltage  $(v_0(t))$  and current  $(i_0(t))$  waveforms for resistive load  $(Z_1 = 160\Omega)$  when the input DC voltage is varied from 30 volts to 18 volts corresponding to the variation in irradiates. The voltage appearing across the switches of the NQBI are shown in FIGURE 11. The maximum blocking voltage across switches  $T_1$ ,  $T_2$ ,  $T_3$ , T<sub>4</sub>, T<sub>5</sub> are 30V, 60V, 30V, 60V and 30V respectively. The maximum blocking voltage across all four switches H<sub>1</sub>, H<sub>2</sub>, H<sub>3</sub> and H<sub>4</sub> are 120 V as they are operating as polaritygenerating parts.

It is evident from the experimental results that the operation of the proposed NQBI-based PV system is effective and reliable. The output of the NQB inverter is found to be stable under a variety of operating conditions, including changes in load type and load impedance.voltage across both capacitors is also balanced to provide a nine-level output voltage under load variation without any capacitor voltage balancing technique.

#### **V. CONCLUSION**

A reduced-switch, nine-level, switched-capacitor-based quadruple boost inverter topology is proposed in this paper. The NQBI is suggested for PV applications by using a solar PV panel as the only source. Though the inverter topology employs two capacitors of unequal voltage rating, the capacitor voltage equilibrium is established without employing an additional voltage balancing strategy. The comparative study shows that the proposed nine-level inverter topology has several advantages over other popular nine-level switched-capacitor inverter topologies, such as performance, total component count, and manufacturing cost. Finally, the results from the experiments show that the proposed NQB inverter-based PV system can work.

#### REFERENCES

- B. P. Reddy, M. Rao A, M. Sahoo, and S. Keerthipati, "A fault-tolerant multilevel inverter for improving the performance of a pole-phase modulated nine-phase induction motor drive," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1107–1116, Feb. 2018.

- [2] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," *Energy Convers. Manage.*, vol. 50, pp. 2761–2767, Nov. 2009. [Online]. Available: https://www. sciencedirect.com/science/article/pii/S0196890409002489

- [3] M. Vijeh, M. Rezanejad, E. Samadaei, and K. Bertilsson, "A general review of multilevel inverters based on main submodules: Structural point of view," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9479–9502, Oct. 2019.

- [4] N. Prabaharan and K. Palanisamy, "Analysis and integration of multilevel inverter configuration with boost converters in a photovoltaic system," *Energy Convers. Manage.*, vol. 128, pp. 327–342, Nov. 2016. [Online]. Available: https://www.sciencedirect. com/science/article/pii/S0196890416308962

- [5] I. Colak, E. Kabalci, and R. Bayindir, "Review of multilevel voltage source inverter topologies and control schemes," *Energy Convers. Manage.*, vol. 52, no. 2, pp. 1114–1128, Feb. 2011. [Online]. Available: https://www.sciencedirect.com/science/article/pii/S0196890410004085

- [6] A. Taghvaie, J. Adabi, and M. Rezanejad, "A self-balanced step-up multilevel inverter based on switched-capacitor structure," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 199–209, Jan. 2018.

- [7] T. Roy, M. W. Tesfay, B. Nayak, and C. K. Panigrahi, "A 7-level switched capacitor multilevel inverter with reduced switches and voltage stresses," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 12, pp. 3587–3591, Dec. 2021.

- [8] Y. Wang, Y. Yuan, G. Li, Y. Ye, K. Wang, and J. Liang, "A T-type switchedcapacitor multilevel inverter with low voltage stress and self-balancing," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 5, pp. 2257–2270, May 2021.

- [9] M. D. Siddique, S. Mekhilef, S. Padmanaban, M. A. Memon, and C. Kumar, "Single-phase step-up switched-capacitor-based multilevel inverter topology with SHEPWM," *IEEE Trans. Ind. Appl.*, vol. 57, no. 3, pp. 3107–3119, May 2021.

- [10] J. S. M. Ali and V. Krishnasamy, "Compact switched capacitor multilevel inverter (CSCMLI) with self-voltage balancing and boosting ability," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4009–4013, May 2019.

- [11] J. Liu, W. Lin, J. Wu, and J. Zeng, "A novel nine-level quadruple boost inverter with inductive-load ability," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4014–4018, May 2019.

- [12] N. Sandeep, J. S. M. Ali, U. R. Yaragatti, and K. Vijayakumar, "Switched-Capacitor-Based quadruple-boost nine-level inverter," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7147–7150, Aug. 2019.

- [13] H. K. Jahan, M. Abapour, and K. Zare, "Switched-capacitor-based singlesource cascaded H-bridge multilevel inverter featuring boosting ability," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1113–1124, Feb. 2019.

- [14] Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/parallel conversion with inductive load," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 878–887, Feb. 2012.

- [15] Y. M. Ye, K. W. E. Cheng, J. F. Liu, and K. Ding, "A step-up switchedcapacitor multilevel inverter with self-voltage balancing," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6672–6680, Dec. 2014.

- [16] E. Babaei and S. S. Gowgani, "Hybrid multilevel inverter using switched capacitor units," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4614–4621, Sep. 2014.

- [17] W. Lin, J. Zeng, J. Hu, and J. Liu, "Hybrid nine-level boost inverter with simplified control and reduced active devices," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 2, pp. 2038–2050, Apr. 2021.

- [18] M. D. Siddique, S. Mekhilef, N. M. Shah, N. Sandeep, J. S. M. Ali, A. Iqbal, M. Ahmed, S. S. M. Ghoneim, M. M. Al-Harthi, B. Alamri, F. A. Salem, and M. Orabi, "A single DC source nine-level switchedcapacitor boost inverter topology with reduced switch count," *IEEE Access*, vol. 8, pp. 5840–5851, 2020.

**RAVI RAUSHAN** (Member, IEEE) received the B.Tech. degree in electrical engineering and the M.Tech. degree in mechatronics from the Maulana Abul Kalam Azad University of Technology, Kolkata, in 2010 and 2012, respectively, and the Ph.D. degree from the Indian Institute of Technology (Indian School of Mines) Dhanbad, in 2018. He is currently working as an Assistant Professor with the Department of Electrical and Electronics Engineering, National Institute of Technology

Karnataka (NITK), Surathkal, India. His research interests include power electronic converters and its application in renewable energy.

**RAJIB KUMAR MANDAL** received the B.E. degree from MACT Bhopal, in 1999, the M.E. degree from Jadavpur University, in 2004, and the Ph.D. degree from NIT Patna, India, in 2018. He is currently working as an Assistant Professor with NIT Patna.

**ASHUTOSH KUMAR SINGH** (Member, IEEE) received the B.Tech. degree in electrical and electronics engineering from the Motihari College of Engineering, Motihari, in 2016, and the M.Tech. degree in electrical engineering from the National Institute of Technology Patna, Patna, India, in 2019, where he is currently pursuing the Ph.D. degree. His research interest includes switched capacitor power electronic converters.

**MD. WASEEM AHMAD** received the B.Tech. and M.Tech. degrees in electrical engineering from Aligarh Muslim University, Aligarh, India, in 2008 and 2011, respectively, and the Ph.D. degree in electrical engineering from the Indian Institute of Technology Kanpur, Kanpur, India, in 2018. He worked as a Research Fellow with the Department of Electrical and Computer Engineering, National University of Singapore, Singapore, and a Graduate Trainee Engineer at Siemens Ltd.,

India. He is currently an Assistant Professor with the National Institute of Technology Karnataka, Surathkal, India. His research interests include fault diagnostics and condition monitoring of power electronic converters.

...