# A New, Soft-Switched, High-Power-Factor Boost Converter with IGBTs

Yungtaek Jang and Milan M. Jovanović

Delta Products Corporation Power Electronics Laboratory P.O. Box 12173 5101 Davis Drive Research Triangle Park, NC 27709, U.S.A.

*Abstract* — A new soft-switching technique that improves performance of the high-power-factor boost rectifier by reducing switching losses is introduced. The losses are reduced by an active snubber which consists of an inductor, capacitor, rectifier, and an auxiliary switch. Since the boost switch turns off with zero current, this technique is well suited for implementations with insulated-gate bipolar transistors. The reverse-recoveryrelated losses of the rectifier are also reduced by the snubber inductor which is connected in series with the boost switch and the boost rectifier. In addition, the auxiliary switch operates with zero-voltage switching. A complete design procedure and extensive performance evaluation of the proposed active snubber using a 1.2-kW prototype operating from a 90 V<sub>rms</sub>-265 V<sub>rms</sub> input are also presented.

# 1. Introduction

Recently, several high-speed insulated-gate bipolar transistor (IGBT) families suitable for high-frequency switch-mode-power-supply applications have been introduced. Capable of operating at switching frequencies as high as 150 kHz and exhibiting a relatively small conduction loss at high currents, these IGBTs appear as a viable alternative to traditionally used metal-oxidesemiconductor field-effect transistors (MOSFETs) in many high-voltage, high-current applications such as boost input-current shapers. Nevertheless, to achieve efficient and reliable operation of an IGBT, it is necessary to ensure that the IGBT is switched under favorable switching conditions. Specifically, due to the IGBT's collector current "tail" effect during the turn-off, which increases the turn-off switching loss and limits the maximum switching frequency, the optimal performance of the IGBT can be achieved by turning-off the IGBT at zero current.

A zero-current-switching (ZCS) boost converter suitable for applications with IGBTs was introduced in [2]. Although in this circuit the boost switch is turned off at zero current, the circuit exhibits a strong undesirable resonance between the snubber inductor and the output capacitance of the switches, which requires additional clamp and/or snubber circuits [3].

In this paper, a soft-switching technique which is suitable for IGBT applications, and which does not suffer

from undesirable resonances of circuit's components is proposed. The proposed technique improves the performance of the boost input-current shaper by eliminating the switching losses with a new zero-currentzero-voltage-switched (ZC-ZVS) active-snubber circuit that consists of a snubber inductor, a clamp diode, a clamp capacitor, and an auxiliary switch. The ZC-ZVS snubber reduces the reverse-recovery-related losses of the rectifier and also provides soft switching of the main and auxiliary switches. Specifically, the main switch turns off with ZCS, whereas the auxiliary switch turns on with ZVS. In addition, because the proper operation of the ZC-ZVS snubber requires that the conduction period of the main switch and the auxiliary switch overlap, the proposed boost converter with active snubber is not susceptible to failures due to accidental transient overlapping of the main and auxiliary switch gate drives. Moreover, the complexity and cost of the converters using the proposed technique is further reduced because the proposed ZC-ZVS active snubber requires a simple non-isolated (direct) gate drive for both switches.

Also, a complete design procedure of this soft-switched boost converter for a server application and extensive experimental evaluations of its performance are presented. The evaluation was performed on a single-phase 1.2-kW, 80-kHz prototype operating in the universal line voltage range of 90  $V_{rms}$ -265  $V_{rms}$ .

# 2. Analysis of Operation

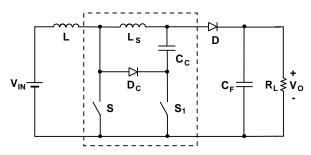

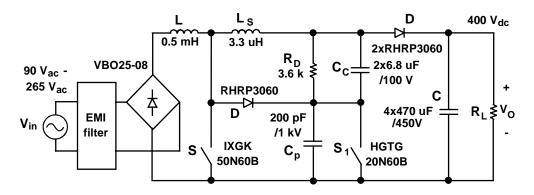

The circuit diagram of the boost converter that employs the new ZC-ZVS active snubber is shown in Fig. 1. The circuit in Fig. 1 uses snubber inductor  $L_S$ , which is connected in series with main switch S and rectifier D, to control the di/dt rate of the rectifier. Along with S, and  $L_S$ , auxiliary switch S<sub>1</sub>, clamp capacitor C<sub>C</sub>, and clamp diode D<sub>C</sub> form a ZC-ZVS active snubber as indicated by dashed lines in Fig. 1.

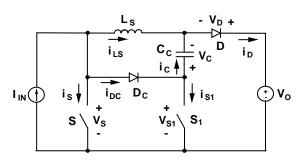

To simplify the analysis of operation, it is assumed that the inductance of boost inductor L is large so that it can be represented by constant-current source  $I_{IN}$ , and that the output-ripple voltage is negligible so that the voltage across the output filter capacitor can be represented by constant-voltage source  $V_0$ . Also, it is assumed that in the on state, semiconductors exhibit zero resistance, *i.e.*, they are short circuits. However, the output capacitance of the

Fig. 1. Boost power stage with new ZC-ZVS active snubber.

switches and the reverse-recovery charge of the rectifier are not neglected in this analysis. The circuit diagram of the simplified converter is shown in Fig. 2.

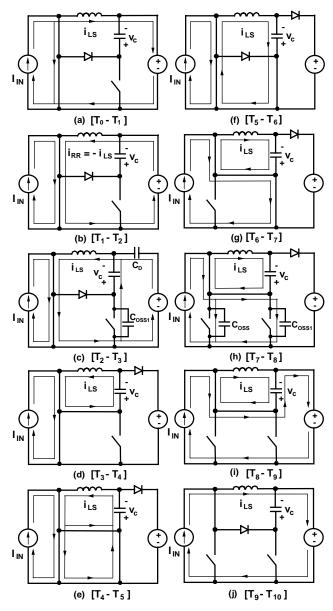

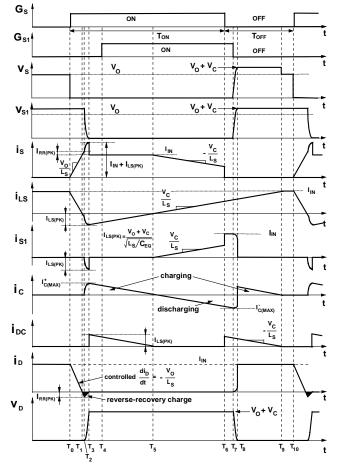

To further facilitate the explanation of the operation, Fig. 3 shows topological stages of the circuit in Fig. 1 during a switching cycle, whereas Fig. 4 shows the powerstage key waveforms. As can be seen from the gate-drive timing diagrams for the boost and auxiliary switches in Fig. 4, the proposed circuit operates with an overlapping gate drive of the switches where the main switch turns on and off slightly prior to the auxiliary switch, *i.e.*, both switches conduct simultaneously during the major period of the on-time and share the current.

Before main switch S is turned on at  $t=T_0$ , the entire input current  $I_{IN}$  flows through snubber inductor  $L_S$  and boost rectifier D. At the same time, main switch S is off blocking output voltage  $V_0$ , whereas, auxiliary switch  $S_1$ is off blocking a voltage which is the sum of output voltage  $V_0$  and clamp-capacitor voltage  $V_C$ , *i.e.*,  $V_0+V_C$ .

After switch S is turned on at  $t=T_0$ , a constant voltage  $V_0$  is applied across  $L_s$ , as shown in the equivalent circuit in Fig. 3(a). As a result, inductor current  $i_{LS}$  and rectifier current  $i_D$  decrease linearly, whereas switch current  $i_s$  increases at the same rate. The rate of the rectifier current decrease is governed by

$$\frac{\mathrm{di}_{\mathrm{D}}}{\mathrm{dt}} = -\frac{\mathrm{V}_{\mathrm{O}}}{\mathrm{L}_{\mathrm{S}}}.$$

(1)

Since the rate of the boost-rectifier-current decrease is controlled by snubber inductance  $L_s$ , the rectifier recovered charge and the associated losses can be reduced by a proper selection of the  $L_s$  inductance. Generally, a

Fig. 2. Simplified circuit diagram of the proposed boost power stage showing reference directions of currents and voltages.

larger inductance, which gives a lower  $di_D/dt$  rate, results in a more efficient reduction of the reverse recoveryassociated losses [1].

At t=T<sub>1</sub>, when i<sub>LS</sub> and i<sub>D</sub> decrease to zero, the entire input current I<sub>IN</sub> flows through switch S, as shown in Fig. 4. Ideally, when i<sub>D</sub> falls to zero at t=T<sub>1</sub>, rectifier D should stop conducting. However, due to a residual stored charge, reverse-recovery current i<sub>RR</sub> will flow through rectifier D, as shown in Fig. 3(b). When, at t=T<sub>2</sub>, the stored charge is recovered from the junction of rectifier D and the rectifier regains its blocking capability, a resonant circuit consisting of snubber inductor L<sub>S</sub>, snubber capacitor C<sub>C</sub>, output capacitor C<sub>OSS1</sub> of auxiliary switch S<sub>1</sub>, and junction capacitor C<sub>D</sub> of rectifier D is formed, as shown in Fig. 3(c). As a result, during the T<sub>2</sub>-T<sub>3</sub> interval, the drain voltage of auxiliary switch S<sub>1</sub> decreases from V<sub>O</sub>+V<sub>C</sub> to zero in a resonant fashion. At t=T<sub>3</sub>, when V<sub>S1</sub> falls to zero,

Fig. 3. Topological stages of the proposed boost power stage.

peak resonant current  $I_{LS(PK)}$ , which flows in the negative direction through  $L_s$ , is given by

$$I_{LS(PK)} = i_{LS}(t = T_3) = \frac{V_0 + V_C}{\sqrt{L_S/C_{EQ}}},$$

(2)

where  $C_{EQ} = C_{OSS1}C_C/(C_{OSS1}+C_C)+C_D \approx C_{OSS1} + C_D$ because for a properly designed circuit  $C_C >> C_{OSS1}$ . From Fig. 3(c), the peak current of clamp capacitor  $C_C$  at t=T<sub>3</sub>,  $I_{C(MAX)}^+$ , is

$$I_{C(MAX)}^{+} = i_{C}(t = T_{3}) = \frac{C_{OSS1}}{C_{OSS1} + C_{D}} \frac{V_{O} + V_{C}}{\sqrt{L_{S}/C_{EQ}}}.$$

(3)

After the voltage across auxiliary switch  $S_1$  falls to zero at t=T<sub>3</sub>, clamp diode  $D_C$  starts conducting, as shown in Fig. 3(d). When  $D_C$  is conducting, clamp capacitor voltage  $V_C$  is applied across  $L_S$  and snubber-inductor current  $i_{LS}$ increases linearly, as illustrated in Fig. 4. If the capacitance of clamp capacitor  $C_C$  is large, capacitor voltage  $V_C$  is almost constant so that inductor current  $i_{LS}$ increases and capacitor current  $i_C$  decreases linearly, *i.e.*,  $di_{LS}/dt = -di_C/dt = V_C/L_S$ . Otherwise,  $i_{LS}$  and  $i_C$  change in a resonant fashion. This topological stage ends at t=T<sub>5</sub>, when  $i_C$  reaches zero and clamp diode  $D_C$  stops conducting. As can be seen from Fig. 4, to achieve ZVS of auxiliary switch  $S_1$ , it is necessary to turn on  $S_1$  before

Fig. 4. Key waveforms of the proposed boost power stage

t=T<sub>5</sub>, *i.e.*, S<sub>1</sub> should be turned on while clamp diode D<sub>C</sub> is conducting. In Fig. 4, auxiliary switch S<sub>1</sub> is turned on at t=T<sub>4</sub>. It should be noted that after t=T<sub>4</sub>, current i<sub>LS</sub> or a part of it may continue flowing through S<sub>1</sub> depending on the relative values of on-impedances of S<sub>1</sub> and D<sub>C</sub>, as shown in Fig. 3(e). Since auxiliary switch S<sub>1</sub> starts conducting after clamp diode D<sub>C</sub> ceases to conduct at t=T<sub>5</sub>, auxiliary-switch current i<sub>S1</sub> continues to increase linearly, as illustrated in Fig. 3(f). At the same time, mainswitch current i<sub>S</sub> decreases at the same rate because the sum of i<sub>S1</sub> and i<sub>S</sub> is equal to the constant input current I<sub>IN</sub>.

When main switch S is turned off at  $t=T_6$ , the current which was flowing through switch S is diverted to auxiliary switch  $S_1$  through clamp diode  $D_C$  as shown in Fig. 3(g). It should be noted that at the moment of switch S turn-off at  $t=T_6$ , the current of S is smaller than  $I_{IN}$ , as shown in Fig. 4. In addition, the voltage across switch S during its turn-off is clamped to zero by conducting clamp diode  $D_C$  and auxiliary switch  $S_1$ , as can be seen from Fig. 3(g). As a result, switch S is turned off with a greatly reduced channel current and with zero voltage. In fact, the circuit can be designed to achieve complete ZCS of main switch S during the turn-off time, as it will be discussed later. During the  $T_6-T_7$  interval, input current  $I_{IN}$  flows through  $S_1$ , whereas  $C_C$  continues to discharge through  $L_s$ . This interval ends at  $t=T_7$  when auxiliary switch  $S_1$  is turned off. It should be noted that auxiliary switch  $S_1$ shares the input current with main switch S during the time interval between  $t=T_5$  and  $t=T_6$ , as shown in Fig. 3(f) and Fig. 4. Therefore, by the addition of auxiliary switch  $S_1$ , the overall rms current of main switch S is reduced.

After switch  $S_1$  is turned off at t= $T_7$ , current  $I_{IN}$  flowing through switch  $S_1$  is diverted from the switch to its output capacitance  $C_{OSS1}$ , as shown in Fig. 3(h). As a result, the voltage across auxiliary switch S<sub>1</sub> starts to increase linearly from zero to  $V_0 + V_c$  due to the constant charging current I<sub>IN</sub>. At the same time, because of conducting D<sub>C</sub>, voltage V<sub>S</sub> of main switch S also increases from zero towards  $V_0 + V_c$ . When the voltage across switches S and  $S_1$  reaches  $V_0 + V_c$  at t=T<sub>8</sub>, rectifier D starts conducting, as shown in Fig. 3(i). During the  $T_8$ - $T_9$  time interval,  $i_{LS}$ continues to increase toward I<sub>IN</sub>, while clamp capacitor C<sub>C</sub> is being charged by the difference of input current I<sub>IN</sub> and snubber inductor current iLS, i.e., by IIN - iLS. When, at t=T<sub>9</sub>, i<sub>LS</sub> reaches I<sub>IN</sub>, clamp diode D<sub>C</sub> stops conducting and the entire input current flows through D, as shown in Fig. 3(j). The circuit stays in this topological stage until the next switching cycle is initiated at  $t=T_{10}$ .

At light load operation, when input current  $I_{IN}$  is smaller than the peak resonant current  $I_{LS(PK)}$  described in Eq. (2), the charge balance of clamp capacitor  $C_C$  is completed during switch-on period. During the  $T_0$ - $T_5$  interval, the key waveforms and power-stage operation when  $I_{IN}$  is smaller than  $I_{LS(PK)}$  are the same as in the case when  $I_{IN}$  is greater than  $I_{LS(PK)}$ , as shown in Figs. 3 and 4. However, after t= $T_5$ , the operation when  $I_{IN}$  is smaller than  $I_{LS(PK)}$  is different from that shown in Fig. 3 and 4. Since when  $I_{IN}$  is smaller than  $I_{LS(PK)}$  snubber-inductor current  $i_{LS}$  reaches  $I_{IN}$ level before main switch S is turned off, auxiliary switch  $S_1$  carries the entire input current until  $S_1$  is turned off after  $i_{LS}$  reaches  $I_{IN}$  level. Therefore, to achieve a complete ZCS of the main switch, the peak resonant current  $I_{LS(PK)}$  should be designed to be greater than input current  $I_{IN}$  over the entire load and line range.

As can be seen from the waveforms in Fig. 4, to achieve a complete ZCS turn-off of main switch S, it is necessary that the clamp-capacitor current  $i_C$  at the moment when S is turned off is equal to input current  $I_{IN}$ , *i.e.*,

$$i_{\rm C}(t=T_6) = I_{\rm IN}.\tag{4}$$

Moreover, since for a properly designed circuit the  $T_6-T_7$  time interval is much shorter than the  $T_5-T_6$  time interval in Fig. 4, the value of clamp capacitor current  $i_C$  at t= $T_6$  and t= $T_7$  is approximately the same, *i.e.*,

$$i_{\rm C}(t=T_6) \approx i_{\rm C}(t=T_7) = I_{\rm C(MAX)}^-$$

(5)

where  $I_{C(MAX)}^{-}$  is the maximum discharging current, as indicated on the  $i_{C}$  waveform in Fig. 4. From Eqs. (4) and (5), the ZCS condition for S can be defined as

$$I_{C(MAX)}^{-} = I_{IN}.$$

(6)

Since for the circuit design so that  $I_{C(MAX)}^- = I_{IN}$ ,  $C_C$  charging occurs only during the T<sub>2</sub>-T<sub>5</sub> interval, *i.e.*, the charging interval T<sub>8</sub>-T<sub>9</sub> shown in Fig. 4 does not exist, the charge balance of C<sub>C</sub> requires that

$$I_{C(MAX)}^{+} = i_{C}(t=T_{3}) \approx I_{C(MAX)}^{-} \approx I_{IN}.$$

(7)

From Eqs. (4) and (7), the ZCS condition can be written as

$$\frac{1}{C_{OSS1}} \sqrt{L_{S}(C_{OSS1} + C_{D})} \le \frac{V_{O} + V_{C}}{I_{IN}}.$$

(8)

If Eq. (8) is satisfied at the maximum power, *i.e.*, for  $I_{IN}=I_{IN(MAX)}$ , complete ZCS of switch S is achieved in the full load range. It should be noted that because auxiliary switch S<sub>1</sub> and rectifier D are both turned on under ZVS condition, external capacitance can be added across S<sub>1</sub> or D without incurring additional switching losses. If it is necessary to satisfy Eq. (8) for given V<sub>O</sub>,  $I_{IN(MAX)}$ ,  $L_S$ ,  $V_C$ , and for given  $C_{OSS1}$  and  $C_D$ , external capacitance can be added in parallel with  $C_{OSS1}$  or C<sub>D</sub>. However, since main switch S is always turned off with ZVS, the complete ZCS of main switch S is not necessary to improve overall performance of the converter. Therefore, the main switch current during turn-off (at t=T<sub>6</sub> in Fig. 4) needs to be optimized so that the peak resonant current  $I_{LS(PK)}$  is not excessive.

As can be seen from Fig. 4, the voltage stress of main switch S, auxiliary switch  $S_1$ , and rectifier D is  $V_O + V_C$ . Therefore, the voltage stress of main switch S in the proposed converter is higher for the amount of  $V_C$ compared to the corresponding stress in the conventional, "hard"-switched boost converter. To keep the voltage stress of switch S and switch  $S_1$  within reasonable limits, it is necessary to properly select clamp-voltage level  $V_C$ . The derivation of  $V_C$  dependence on the circuit parameters can be simplified by recognizing that in the boost converter in Fig. 1, the rectifier-current commutation interval  $T_0$ - $T_2$  is much shorter than on-time period  $T_{ON}$  of switch S, and that capacitor charging period  $T_8$ - $T_9$  is zero. In addition, the duration of the commutation periods  $T_2$ - $T_3$  and  $T_7$ - $T_8$  are negligible compared to the on-time interval of main switch S.

From Fig. 4, it can be seen that, from t=T<sub>3</sub> to t=T<sub>5</sub>, clamp capacitor C<sub>C</sub> is charged with current i<sub>C</sub> which has a constant slope of di<sub>C</sub>/dt = V<sub>C</sub>/L<sub>S</sub>. Therefore, since the circuit is designed to achieve ZCS of main switch S,  $i_C(t=T_3) = I_{C(MAX)}^+ = I_{IN}$ , and since the duration of the time interval from t=T<sub>2</sub> to t=T<sub>5</sub> is approximately one-half of the on-time of switch S, clamp-capacitor voltage V<sub>C</sub> can be expressed as

$$V_{\rm C} \approx L_{\rm S} \frac{I_{\rm IN}}{DT_{\rm S}/2} = 2 \frac{L_{\rm S} f_{\rm S} I_{\rm IN}}{D}, \qquad (9)$$

where D is the duty-cycle of switch S,  $T_S$  is the switching period, and  $f_S$  is the switching frequency. Since for a lossless boost power stage for which the current commutation interval  $T_0$ - $T_2$  is much shorter than  $T_{ON}$ , the voltage-conversion ratio  $V_O/V_{IN}$  is given by

$$\frac{V_{\rm O}}{V_{\rm IN}} = \frac{I_{\rm IN}}{I_{\rm O}} = \frac{1}{1 - D} \,. \tag{10}$$

Eq. (10) can be written as

$$V_{\rm C} \approx 2L_{\rm S}f_{\rm S}I_{\rm O}\left(\frac{V_{\rm O}^{2}}{(V_{\rm O} - V_{\rm IN})V_{\rm IN}}\right).$$

(11)

According to Eq. (11),  $V_C$  is the maximum at full load  $I_{O(MAX)}$  and high line  $V_{IN(MAX)}$ . For given input and output specifications, *i.e.*, for given  $I_{O(MAX)}$ ,  $V_{IN(MAX)}$ , and  $V_O$ , clamp-capacitor voltage  $V_C$  can be minimized by minimizing the  $L_S f_S$  product.

It should be noted that the control of the proposed boost converter can be implemented in the same way as in its conventional "hard" switched counterpart as long as an additional gate-drive circuit is provided. Specifically, in the input-current-shaping applications, the proposed converter can be implemented with any known control technique, such as average current, peak current, or hysteretic control.

#### 3. Design of a 1.2-kW, HPF Boost Rectifier

A 1.2-kW, HPF boost experimental rectifier was designed for the following specifications.

#### Input

- Voltage V<sub>in</sub>: 1-phase, 90 V<sub>rms</sub> 265 V<sub>rms</sub>

- Line Frequency f<sub>L</sub>: 47 63 Hz

- THD: < 5%

- Power Factor: > 0.99 (100% load)

### Output

- Voltage V<sub>0</sub>: 400 V<sub>dc</sub>

- Power  $P_0$ : 1.2 kW

- Ripple Voltage: < 6.5 V<sub>peak-peak</sub> (100/120 Hz)

- Switch Frequency f<sub>s</sub> : 80 kHz

#### 3.1 Design of Active Snubber Circuit

To reduce the reverse-recovery-related losses, the di<sub>D</sub>/dt rate of the majority of fast-recovery rectifiers should be kept below approximately 100 A/µs [4]. Generally, slower rectifiers require slower di<sub>D</sub>/dt rates than faster rectifiers to achieve the same level of reduction of the reverserecovery-related losses. As a rule of thumb, the practical range of snubber inductance  $L_s$  is from 2  $\mu$ H to 20  $\mu$ H. In fact, without a snubber, the rate of rectifier-current change is mainly decided by the parasitic inductance of the trace between boost switch S and rectifier D, which is generally less than several hundreds nanohenrys. As a result, the rate of rectifier-current change of the boost rectifier without a snubber inductor is approximately 2000 A/ $\mu$ s (V<sub>O</sub>/L<sub>P</sub> =  $400/0.2 \times 10^{-6}$ ). To reduce the stored charge which is directly proportional to the reverse-recovery-related losses, snubber inductor L<sub>S</sub> must be added.

Generally, the maximum value of snubber inductance L<sub>s</sub> is limited by the voltage stress on switch S and auxiliary switch  $S_1$ . As can be seen from Fig. 2, the voltage stress of switches S and  $S_1$  are the same and equal to  $V_0 + V_c$ . During the period when clamp diode  $D_c$  is not conducting, auxiliary switch  $S_1$  blocks the voltage which is the summation of the clamp capacitor voltage and the output voltage. Boost switch S blocks the same voltage when clamp diode D<sub>C</sub> is conducting. Compared to the corresponding stress in the conventional, "hard"-switched boost converter, the voltage stress of boost switch S in the proposed converter is higher for the amount of clamp voltage V<sub>C</sub>. To keep the voltage stress of switches S and  $S_1$  within reasonable limits, it is necessary to properly select clamp-voltage level V<sub>C</sub>. Clamp-capacitor voltage V<sub>c</sub> can be calculated by using Eq. (11). According to Eq. (11),  $V_C$  is the maximum at full load  $I_{O(MAX)}$  and high line  $V_{IN(MAX)}$ , since switching frequency  $f_S$  and output voltage Vo are constant. For given input and output specifications, *i.e.*, for given I<sub>O(MAX)</sub>, V<sub>IN(MAX)</sub>, f<sub>S</sub>, and V<sub>O</sub>, the voltage stresses on the main and auxiliary switches can be minimized by minimizing snubber inductor L<sub>S</sub>. From the specifications, the maximum input voltage  $V_{IN(MAX)}$  = 375 V, the maximum output current  $I_{O(MAX)} = 3 A$ , switching frequency  $f_S = 80$  kHz, and output voltage  $V_O =$ 400 V. To reduce  $di_D/dt$  rate the value of snubber inductor  $L_S$  was chosen to be approximately 3.3  $\mu$ H. This value results in  $di_D/dt = 120$  A/µs and  $V_C = 27$  V. The maximum voltage stress of the switch is below 427 V which is quite acceptable even for a 500-V rated device.

Since the average voltage across the clamp-capacitor is independent from the size of the clamp capacitor  $C_C$  as shown in Eq. (11), the value of  $C_C$  can be selected to

minimize the switch-frequency voltage ripple. Since the energy stored in the snubber inductor contributes to the voltage ripple during a switching cycle, the maximum switch-frequency voltage ripple  $V_{C(P-P)}$  can be expressed as

$$V_{C(P-P)} = I_{O(max)} \sqrt{\frac{L_S}{C_C}} .$$

(12)

The choice of two  $6.8 \,\mu\text{F}/100 \,\text{V}$  ceramic capacitors in parallel for the clamp capacitor limits the magnitude of the maximum peak-to-peak ripple voltage to approximately  $1.5 \,\text{V}$ .

#### 3.2 Selection of Components

#### Semiconductors

The peak voltage stress on switch S is approximately 430 V as explained in Section 3.1. The peak current stress on S, which is equal to the peak input current is approximately 21.6 A at full load and low line. An IXGK 50N60B IGBT from IXYS ( $V_{CES} = 600 \text{ V}$ ,  $I_{C90} = 50 \text{ A}$ ,  $V_{F}$ = 2.5 V) is used for boost switch S. The peak voltage stress on auxiliary switch S<sub>1</sub> is the same as that of switch S. Also, the peak current stress on  $S_1$  is equal to the peak current stress of S, i.e., it is equal to the input current at full load and low line. However, the average current of  $S_1$ ,  $\langle i_{S1} \rangle$ , is much smaller than the average current of S,  $\langle i_{S} \rangle$ , as can be seen from Fig. 4. As a result, a smaller IGBT can be selected for  $S_1$ . In the experimental circuit, an HGTG 20N60B3 IGBT from Harris ( $V_{CES} = 600 \text{ V}$ ,  $I_{C110}$ = 20 A,  $V_F = 2 V$ ) is used for S<sub>1</sub>. Although S<sub>1</sub> turns on with ZVS and can be implemented with a MOSFET device, in the experimental circuit an IGBT is also used for auxiliary switch  $S_1$  together with boost switch S. To reduce the turn-off switching loss of S<sub>1</sub> and optimize the peak value of snubber-inductor current  $I_{LS(PK)}$ , a capacitor (200 pF/1 kV) is connected in parallel with  $S_1$ .

Since, output diode D has the same voltage stress as that of switch S and must conduct a maximum load current of 3 A, two RHRP3060 diodes from Harris ( $V_{RRM} =$ 600 V,  $I_{FAVM} =$  30 A,  $t_{rr} =$  40 ns) connected in parallel were used for output diode D. To reduce the conduction loss of the output diode, the devices which have a significantly higher current rating than the maximum current were selected. The voltage stress of clamp diode D<sub>C</sub> is the same as that of output diode D. However, since the circulating current through L<sub>S</sub>-D<sub>C</sub> loop is small, a RHRP3060 diode is used for D<sub>C</sub>.

#### Boost inductor

Since the desired inductance of boost inductor L is 0.5 mH, four 0.125 mH inductors are built using a toroidal core (Magnetics, Kool- $\mu$  77071-A7) and 45 turns of magnet wire (AWG #12). Four small-size cores are used to reduce the overall height of the power supply.

Fig. 5. Experimental 1.2 kW, boost power stage with a ZC-ZVS active snubber.

### Snubber inductor

Snubber inductor  $L_s$ =3.3  $\mu$ H was built using a toroidal core (Magnetics, Kool- $\mu$  77312-A7) and 12 turns of magnet wire (AWG #12).

#### Clamp Capacitor

Two 6.8  $\mu$ F, 100 VDC, ceramic capacitors connected in parallel are used for clamp capacitor C<sub>C</sub> to limit the magnitude of the maximum peak-to-peak ripple voltage to approximately 1.5 V. Since the peak clamping capacitor voltage is approximately 30 V for this prototype, 100 VDC ceramic capacitors are utilized.

#### 4. Experimental Results

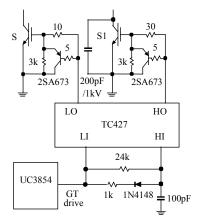

The component values of the experimental circuit power stage are shown in Fig. 5. The control circuit was implemented with the average-current PFC controller UC3854. The TC427 driver is used to generate the required gate-drive signal for the main switch and the auxiliary switch, as shown in Fig. 6.

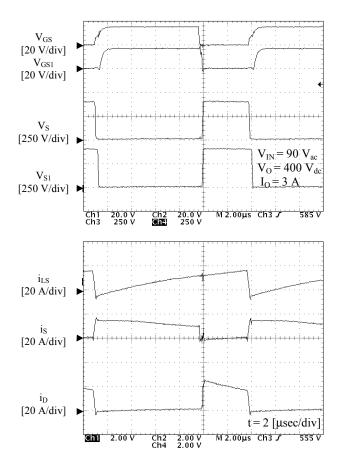

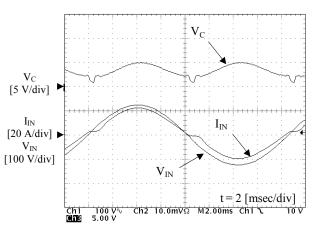

Figure 7 shows the oscillograms of key waveforms of the experimental converter with the IGBT implementation at the low line and full power. The oscillograms in Fig. 7 is taken at the peak of the line current, i.e., when the duty cycle is at the minimum. As can be seen comparing corresponding waveforms in Figs. 4 and 7, there is a good agreement between the experimental and theoretical

Fig. 6. Gate-drive circuit for the boost and auxiliary switches.

waveforms. As can be seen from Fig. 7, auxiliary switch  $S_1$  is turned on with ZVS since its voltage  $V_{S1}$  falls to zero before gate-drive signal  $V_{GS1}$  becomes high. However, boost switch S is "hard" switched, *i.e.*, S is turned on while voltage across it is equal to output voltage  $V_0 = 400$  V. Despite the "hard" turn on of boost switch S, all waveforms are free from parasitic ringing, since the output capacitance of IGBTs is much smaller than that of MOSFETs. Also, it should be noted that the boost-rectifier-current turn-off rate, which is controlled by  $L_S$ , is approximately  $di_D/dt = 120$  A/µs, as indicated in Fig. 7. With this  $di_D/dt$  rate, peak reverse-recovery current  $I_{RR}$  is

Fig. 7. Measured key waveforms of experimental converter at  $P_0$ = 1.2 kW and  $V_{IN}$  = 90  $V_{rms}$ . Time base: 2 µs/div.

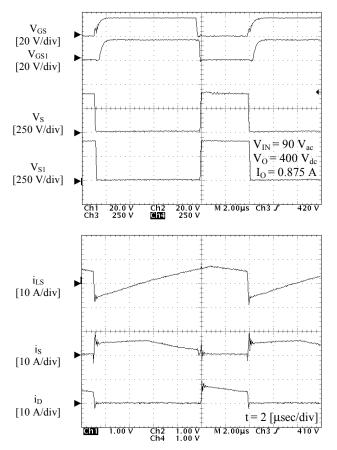

Fig. 8. Measured key waveforms of experimental converter at  $P_0 = 350$  W and  $V_{IN} = 90$  V<sub>ac</sub>. Time base: 2 µs/div.

reduced to approximately 4 A, which corresponds to a recovered charge of approximately 100 nC.

The key waveforms of the experimental prototype at light load operation is shown in Fig. 8. When input current  $I_{IN}$  is smaller than the peak resonant current  $I_{LS(PK)}$ , the charge balance of clamp capacitor  $C_C$  is completed during the switch-on period as shown in Fig. 8.

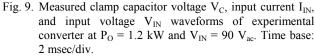

Figures 9 and 10 show the measured waveforms of the input line current and clamp capacitor voltage  $V_C$  of the prototype rectifier delivering 1.2 kW at 90 V and 265 V input voltages, respectively. Since the maximum duty cycle is not limited by the addition of the active snubber circuit, the input current waveforms with and without the active snubber circuit are nearly identical.

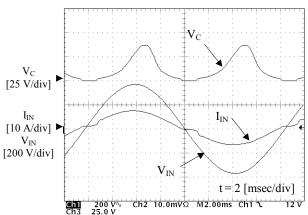

Figure 11 shows the measured efficiencies of the experimental converter with and without the active snubber at the minimum and maximum line voltages as functions of the output power. As can be seen from Fig. 11, for both line voltages the active snubber improves the conversion efficiency in the entire measured power range (200 W to 1.2 kW). Nevertheless, the efficiency improvement is more pronounced at the minimum line and higher power levels where the reverse-recovery losses are greater. Specifically, at the maximum line (265 V<sub>rms</sub>), the efficiency improvement at 1.2 kW is 0.9%. However, at the minimum line, the implementation without the active snubber cannot deliver more than approximately 900 W

due to the thermal runaway of the switch caused by the excessive reverse-recovery losses. Even at  $P_0 = 900$  W, the active snubber improves the efficiency by approximately 3.4%, which translates into approximately 30% reduction of the losses.

Figure 12 shows the measured temperatures of the experimental converter with and without the active snubber at the minimum line voltage as functions of the The ambient temperature output power. was approximately 26°C during the measurements. As can be seen from Fig. 12, at the same power levels, the temperatures of the semiconductor components in the implementation with the active snubber are significantly lower than those in the implementation without the snubber. As indicated in Figs. 11 and 12, at the maximum line (265  $V_{rms}$ ) and full power (1.2 kW), the case temperatures of the boost rectifier and boost switch in the implementation with the snubber are  $T_d = 37^{\circ}C$  and  $T_s = 35^{\circ}C$ , respectively, whereas the corresponding temperatures in the implementation without the snubber are  $T_d = 41^{\circ}C$  and  $T_s = 39^{\circ}C$ . Similarly, at the minimum

Fig. 10. Measured clamp capacitor voltage  $V_C$ , input current  $I_{IN}$ , and input voltage  $V_{IN}$  waveforms of experimental converter at  $P_O = 1.2 \text{ kW}$  and  $V_{IN} = 265 \text{ V}_{ac}$ . Time base: 2 msec/div.

#### **EFFICIENCY** [%]

Fig. 11 Measured efficiencies of the experimental converter with and without ZC-ZVS active snubber at the minimum and maximum line voltages as functions of the output power. Note that the maximum possible output power for the implementation without the snubber is limited to 900 W.

#### 100 w/ ZC-ZVS snubber F 90 w/o snubber \* 80 boost switch S 70 60 Vin = 90 Vac snubber switch S1 Vo = 400 V 50 40 30 output diode D 20 200 400 600 800 1000 1200 300 500 700 900 1100 **OUTPUT POWER [W]**

#### **TEMPERATURE** [deg C]

Fig. 12 Measured switch temperature of the experimental converter with and without ZC-ZVS active snubber at the minimum line voltage as functions of the output power.

line voltage (90  $V_{rms}$ ) and full power, the rectifier and switch temperatures in the implementation with the snubber are  $T_d = 41^{\circ}$ C and  $T_s = 86^{\circ}$ C. As can be seen from Figs. 11 and 12, the implementation without the snubber cannot deliver the full power of 1.2 kW at the minimum line because the rectifier becomes thermally unstable at approximately 900 W. In fact, for the implementation without the snubber the temperature of the boost switch is  $T_s = 93$  °C at 900 W, which is significantly higher than the temperature of the switches ( $T_s = 61$  °C,  $T_{S1} = 56$  °C) in the implementation with the snubber at the same output power.

## 5. Conclusion

An active-snubber technique which reduces the reverserecovery-related losses of the rectifier and also provides lossless switching for the main and auxiliary switches is described. A complete design procedure of a boost inputcurrent shaper with the proposed active snubber is presented. Also, performance evaluations on a 1.2-kW prototype for server applications are given. It is shown that the proposed active-snubber technique can significantly extend the maximum power range at which a fast-recovery rectifier can be reliably employed.

#### References

- [1] K. Wang, F.C. Lee, G. Hua, D. Borojević, "A comarative study of switching losses of IGBTs under hard-switching, zero-voltage-switching, and zero-current-switching," *IEEE Power Electronics Specialists' Conf. (PESC) Rec.*, pp. 1196-1204, June 1994.

- [2] G. Hua, X. Yang, Y. Jiang, F.C. Lee, "Novel zero-currenttransition PWM converters," *IEEE Power Electronics Specialists' Conf. (PESC) Rec.*, pp. 538 - 544, June 1993.

- [3] K. Wang, G. Hua, F.C. Lee, "Analysis, design and experimental results of ZCS-PWM Boost Converters," *International Power Electronics Conf. Proc.*, pp. 1202-1207, Yokahama, Japan, April 1995.

- [4] Y. Khersonsky, M. Robinson, D. Gutierrez, "New fast recovery diode technology cuts circuit losses, improves reliability," *Power Conversion & Intelligent Motion* (*PCIM*) Magazine, pp. 16 - 25, May 1992.