# A New Test/Diagnosis/Rework Model for Use in Technical Cost Modeling of Electronic Systems Assembly

Thiagarajan Trichy, Peter Sandborn, Ravi Raghavan, and Shubhada Sahasrabudhe

CALCE Electronic Products and Systems Center University of Maryland College Park, MD 20742

### Abstract

This paper presents a test/diagnosis/rework analysis model for use in technical cost modeling of electronic assemblies. The approach includes a model of test operations characterized by fault coverage, false positives, and defects introduced in test, in addition to rework and diagnosis operations that have variable success rates and their own defect introduction mechanisms. The model can accommodate an arbitrary number of rework attempts on any given assembly and can be used to optimize the fault coverage and rework investment during system tradeoff analyses.

The model's implementation allows all inputs to the model to be represented as probability distributions thereby accommodating inevitable uncertainties in input data present during tradeoff activities and uses Monte Carlo methods to determine model outputs.

## **1. Introduction**

At a fundamental level, electronic system design is a tradeoff analysis activity with uncertain inputs. This tradeoff includes factors such as size and performance, but often the most important factor in the tradeoff is cost. The various costs that affect the manufacture of the system are the fabrication or assembly cost, test/inspection cost, rework cost, and waste disposition cost. In addition, there are significant nonmanufacturing life cycle costs associated with system sustainment, end-of-life, and other issues. Of the manufacturing costs, the test and the rework costs can be very important drivers that significantly affect the total cost of manufacturing for many products. Modeling the test/diagnosis/rework costs accurately may determine the extent to which the system designer can control and optimize the manufacturing cost.

Technical cost modeling (e.g., [1], [2]) is one method that is useful for economic tradeoff analysis. Technical Cost Modeling (TCM) is defined as a processbased, "bottoms-up" approach to cost estimation, with total cost broken into a set of individual cost elements (process steps). Each of these elements is estimated separately, and then summed to provide an estimate of the total cost. Thus, the complex task of cost estimation is reduced to a set of simpler algorithms, which can be estimated based on science, engineering, accounting, or expert judgment. The modeling of a process flow (sequence of process steps) is central to TCM, [3].

The goal of TCM is to understand the overall and component costs of a product and how these costs change when product and/or process changes are made. Specifically, this includes dividing cost into its constituent components: variable cost elements, which includes materials, labor, and utility; and the fixed cost which includes equipment, elements, tooling. maintenance, and the cost of capital. Once these costs are established, sensitivity analysis can be performed to understand the impact of changes to key parameters like annual production volume, process yield, throughput and tooling cost.

Consequently, a detailed test/rework model, which includes diagnosis and the effects of factors like false positives and defects introduced by the test, diagnosis, and rework, which can be included within technical cost models is a critical component necessary for design tradeoff analysis.

The context that interests us in this paper is electronic board assembly. In board assembly the tradeoff problem addressed is: at what point(s) in the process do I stop and test, how much test (fault coverage) do I pay for at those point(s), when in the process do I rework, and how many attempts do I make to rework before scrapping a defective assembly? The answer to these questions is application specific necessitating a comprehensive test/diagnosis/ rework model for use in tradeoff analysis.

The next section of this paper outlines the existing test/rework models that can currently be used with technical cost modeling. Section 3 describes the new model developed by the authors. Section 4 demonstrates the new model by providing example results.

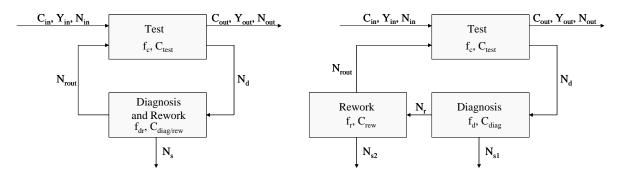

Figure 1 – Example test/diagnosis/rework models currently in use for technical cost modeling. C = cost, Y = yield, N = number of parts,  $f_c = fault$  coverage,  $f_{dr} = fraction$  of parts that are diagnosible and reworkable,  $f_r = fraction$  of parts that are reworkable,  $f_d = fraction$  of parts that are diagnosible, and  $N_s = number$  of parts scrapped.

### 2. Existing Models

There are several existing test/rework models that are applicable to TCM. The basic test/rework models, that are currently in use, are shown in Figure 1. In the example test/diagnosis/rework models shown in Figure 1 all parts coming from production are tested; the diagnosis and repair are applied to all the parts that are identified as defective during the test; and all reworkable parts are retested. Many versions of these models supporting some subset of the variables shown have been developed including single rework attempt models and multiple rework attempt models [4]-[10]. Athough the detail accomodated in these models varies, in general they do not account for new defects introduced during the test, diagnosis or rework processes; false positives in testing, or uncertainties in the input data.

In order to accommodate the additional effects and obtain a model that is readily useable in a technical cost modeling environment, we have formulated the new more comprehensive test/diagnosis/rework model that is discussed in the next section.

#### 3. Detailed Test/Diagnosis/Rework Model

The objective of the new test economics model is to accommodate the test/diagnosis/rework effects relevant to printed circuit board fabrication and electronic system assembly processes. In these processes, defect insertion during test and rework operations is not un-common (e.g., from handling and/or probes making physical contact with the board), false positives<sup>1</sup> can be a significant problem especially in board fabrication, multiple rework attempts are made when dealing with expensive systems such as multichip modules, and complex rework operations that may include reassembly of significant portions of the system are performed.

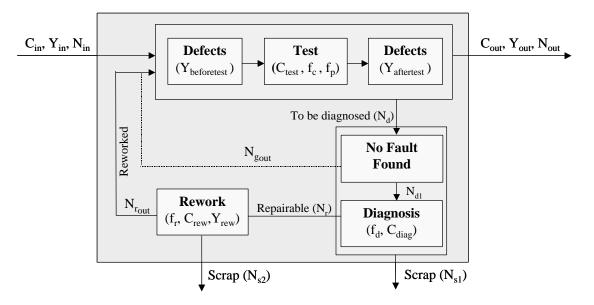

Figure 2 shows the content of the new test/ diagnosis/rework model. In the following description we use the word "part" to refer to the item being tested (e.g., a board assembly). Inputs to this model are the accumulated cost and yield of upstream processes (Cin and Y<sub>in</sub>), N<sub>in</sub> is not a required input and is included for convenience in the formulation of the model.<sup>2</sup> The test portion of the model is the top most group of three steps. This model can be used to account for defects introduced by the test operation both prior to the actual test (e.g., loading the part into the tester or stationing the probes on the part) and after the test result is recorded (e.g., unloading the part from the tester). The parts that are determined to be faulty go on to the diagnosis step. Three outcomes are possible from diagnosis: 1) no fault is found in which case the part goes back for retesting, 2) the part is determined to be reworkable and sent on to rework, or 3) the part is determined to be non-reworkable and sent to scrap. The rework process operates on the reworkable parts and scraps parts that can not be successfully reworked. The reworked parts are re-tested and if the reworked parts are found to be faulty again, the parts are again sent for diagnosis. This rework process can be performed a fixed number of times (attempts). The new model simultaneously considers the effect of fault coverage and false positives on the cost and yield.

<sup>&</sup>lt;sup>1</sup> A false positive is a positive test result in subjects who do not possess the attribute for which the test is conducted.

$<sup>^2</sup>$  In general yield and cost results from this model are independent of  $N_{\rm in}$ , however, if equipment, tooling, or other non-recurring costs are included, the results become dependent on  $N_{\rm in}$  and can be computed from accumulations of time specific equipment is occupied or the quantity of tooling used to produce a specific quantity of parts, see equations (18)-(20) and associated discussion.

Figure 2 – Organization of the new test/diagnosis/rework mode. Table I describes the symbols appearing in this figure.

|                           | Table I – Nomenclature used in Figure 2 a                                  | ind thre          | oughout the discussion in this paper.                                                                                                                                                                                                                                                                                      |  |

|---------------------------|----------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C <sub>in</sub>           | Cost of a part entering the                                                | N <sub>in</sub>   | Number of parts entering the                                                                                                                                                                                                                                                                                               |  |

|                           | test/diagnosis/rework process                                              |                   | test/diagnosis/rework process                                                                                                                                                                                                                                                                                              |  |

| C <sub>test</sub>         | Cost of test/part                                                          | N <sub>d</sub>    | Total number of parts to be diagnosed                                                                                                                                                                                                                                                                                      |  |

| C <sub>diag</sub>         | Cost of diagnosis/part                                                     | Ngout             | Number of no fault found parts                                                                                                                                                                                                                                                                                             |  |

| C <sub>rew</sub>          | Cost of rework/part (may be a computed quantity, see Section 4.2)          | N <sub>d1</sub>   | $N_d - N_{gout}$                                                                                                                                                                                                                                                                                                           |  |

| C <sub>out</sub>          | Effective cost of a part exiting the test/diagnosis/rework process         | N <sub>r</sub>    | Number of parts to be reworked                                                                                                                                                                                                                                                                                             |  |

| $f_c$                     | Fault coverage                                                             | N <sub>rout</sub> | Number of parts actually reworked                                                                                                                                                                                                                                                                                          |  |

| $\mathbf{f}_{\mathbf{p}}$ | False positives fraction, or the probability of testing a good part as bad | N <sub>s1</sub>   | Number of parts scrapped by diagnosis process                                                                                                                                                                                                                                                                              |  |

| $\mathbf{f}_{d}$          | Fraction of parts determined to be reworkable                              | N <sub>s2</sub>   | Number of parts scrapped during rework                                                                                                                                                                                                                                                                                     |  |

| f <sub>r</sub>            | Fraction of parts actually reworked                                        | N <sub>out</sub>  | Number of a parts exiting the<br>test/diagnosis/rework process, includes<br>good parts and test escapes                                                                                                                                                                                                                    |  |

| Y <sub>in</sub>           | Yield of a part entering the test/diagnosis/rework process                 | [                 |                                                                                                                                                                                                                                                                                                                            |  |

| Y <sub>beforetest</sub>   | Yield of processes that occur entering the test                            |                   | Versions of C <sub>in</sub> , Y <sub>in</sub> and N <sub>in</sub> appear both<br>with and without subscripts in the<br>proceeding discussion. When the<br>variables appear with out subscripts they<br>refer to the values entering the process.<br>When they have subscripts, they represent<br>specific rework attempts. |  |

| Yaftertest                | Yield of processes that occur exiting the test                             |                   |                                                                                                                                                                                                                                                                                                                            |  |

| Y <sub>rew</sub>          | Yield of the rework process (may be a computed quantity, see Section 4.2)  |                   |                                                                                                                                                                                                                                                                                                                            |  |

| Yout                      | Effective yield of a part exiting the test/diagnosis/rework process        |                   |                                                                                                                                                                                                                                                                                                                            |  |

thi 7

There are several assumptions made in the formulation of this model:

- Defects introduced by the diagnosis step are not explicitly treated.

- False positive (f<sub>p</sub>) and fault coverage (f<sub>c</sub>) act simultaneously and they are independent of each other, i.e., the fault coverage acts only on bad parts and the false positive acts either only on good parts or on all parts.

The cost incurred by all the parts that eventually pass the test step is given by,

$$C_{1} = \sum_{i=0}^{n} \left( C_{in_{i}} + C_{test} \right) N_{out_{i}}, \qquad (1)$$

where n is the number of rework attemps allowed, i.e., the maximum number of attempts to rework an individual part is n and N<sub>outi</sub> is number of parts passed by the test in the i<sup>th</sup> rework attempt (see (8) and associated discussion). When i=0, C<sub>1</sub> is the total cost of the parts that pass the test without ever going through diagnosis or rework. The cost incurred by all the parts scrapped by the diagnosis step is given by,

$$C_{2} = \sum_{i=1}^{n} \left( C_{in_{i}} + C_{test} + C_{diag} \right) N_{sl_{i}} , \qquad (2)$$

and the cost incurred by all the parts scrapped by the rework step is given by,

$$C_{3} = \sum_{i=1}^{n} \left( C_{in_{i}} + C_{test} + C_{diag} + C_{rew} \right) N_{s2_{i}} , \quad (3)$$

where  $N_{s1i}$  and  $N_{s2i}$  are defined in (10) and (11). After the final rework (n<sup>th</sup> rework attempt), the parts that do not pass the test are scrapped. The first term in (4) accounts for the defective parts scrapped by the final test, and the second term accounts for any false positives that are encountered during the final test,

$$C_{4} = N_{d_{n+1}} (C_{in_{n}} + C_{test}) + N_{in_{n}} Y_{in_{n}} Y_{beforetest} f_{p} (C_{in_{n}} + C_{test})$$

(4a)

when f<sub>p</sub> applies to only good parts, and

$$C_4 = N_{d_{n+1}} \left( C_{in_n} + C_{test} \right) + N_{in_n} f_p \left( C_{in_n} + C_{test} \right) (4b)$$

when f applied to all parts

when  $f_p$  applied to all parts.

$N_{inn}$  appearing in (4) is defined in (13). The total cost of all the parts (including scrapped parts) is the sum of  $C_1$  through  $C_4$ . The total effective cost per output part associated with this model is the total cost divided by the total number of output parts (parts that are eventually passed by the test),

$$C_{out} = \frac{C_1 + C_2 + C_3 + C_4}{N_{out}}.$$

(5)

The treatment of the false positives affects both the number of parts moving through the process and the yield of those parts. The test step is characterized by both fault coverage and false positives ( $f_p$  = probability of testing a good part as bad which should not be confused with the escape fraction which is the probability of testing bad parts as good). Let us assume that the false positives are created by the test <u>before</u> the identification of faults. Let the number of parts that come into the test affected by the false positives be N<sub>1</sub> and the yield coming in be Y<sub>1</sub>. Let the number of parts going out (after false positives are created) be N<sub>2</sub> and their yield be Y<sub>2</sub>. These parts consist of both good (g) and bad parts (b) such that N<sub>1</sub>=N<sub>1g</sub>+N<sub>1b</sub> and N<sub>2</sub>=N<sub>2g</sub>+N<sub>2b</sub>, Figure 3.

$$\begin{array}{c} \underline{Y_{1}, N_{1}(N_{1g}, N_{1b})}, \\ f_{p} \end{array} \xrightarrow{Y_{2}, N_{2}(N_{2g}, N_{2b})} \\ f_{p}N_{1g} \text{ or } f_{p}N_{1} \end{array}$$

*Figure 3 – Notation for false positive formulations.*

There are several approaches to modeling the affect of the false positives. If we assume that the number of false positives sent to diagnosis by the test step will be  $f_pN_{1g}$  based on the assumption that false positives only act on good parts. The false positive fraction is given by,

$$f_{p} = \frac{N_{1g} - N_{2g}}{N_{1g}}$$

(6a)

$$Y_{2} = \frac{N_{2g}}{N_{2}} = \frac{(1 - f_{p})N_{1g}}{(N_{1} - f_{p}N_{1g})} = \frac{(1 - f_{p})Y_{1}}{1 - f_{p}Y_{1}}.$$

(7a)

An alternative assumption is that the number of false positives sent to diagnosis by the test step will be  $f_pN_1$  based on the assumption that false positives act on all parts.<sup>3</sup> The false positive fraction is given by,

<sup>&</sup>lt;sup>3</sup> In this case, the false positives can be created from already defective parts, i.e., defective parts are detected as defective by the test step for the wrong reasons.

$$f_{p} = \frac{N_{1} - N_{2}}{N_{1}}$$

(6b)

$$Y_{2} = \frac{N_{2g}}{N_{2}} = \frac{(1 - f_{p})N_{1g}}{(1 - f_{p})N_{1}} = \frac{N_{1g}}{N_{1}} = Y_{1}, \quad (7b)$$

in other words,  $f_p$  in this case reduces the good and bad parts proportionately thus leaving the yield unchanged.

The number of parts moving through the process are shown in (8)-(13),

$$N_{out_{i}} = N_{in_{i}} \left( 1 - f_{p} Y_{in_{i}} Y_{beforetest} \right) \left( \frac{\left( 1 - f_{p} \right) Y_{in_{i}} Y_{beforetest}}{1 - f_{p} Y_{in_{i}} Y_{beforetest}} \right)^{f_{c}}$$

$$N_{d1} = N_{in_{i}} \left( 1 - f_{p} Y_{in_{i}} Y_{beforetest} \right) - N_{out}.$$

$$(8a)$$

$$(9a)$$

$N_{dl_i} = N_{in_i} (I - I_p Y_{in_i} Y_{beforetest}) - N_{out_i}$ when  $f_p$  applies to only good parts, and

$$\begin{split} \mathbf{N}_{out_{i}} &= \mathbf{N}_{in_{i}} \left( \mathbf{l} - \mathbf{f}_{p} \right) \!\! \left( \mathbf{Y}_{in_{i}} \mathbf{Y}_{beforetest} \right)^{f_{c}} \\ \mathbf{N}_{dl_{i}} &= \mathbf{N}_{in_{i}} \left( \mathbf{l} - \mathbf{f}_{p} \right) \!\! - \! \mathbf{N}_{out_{i}} + \mathbf{f}_{p} \mathbf{N}_{in_{i}} \left( \mathbf{l} - \mathbf{Y}_{in_{i}} \mathbf{Y}_{beforetest} \right) \end{split}$$

(8b)

when f<sub>p</sub> applied to all parts.

$$N_{sl_{i}} = (1 - f_{d})N_{dl_{i}}$$

(10)

(9b)

$$N_{s2_i} = (1 - f_r)N_{r_i}$$

(11)

$$N_{r_i} = f_d N_{dl_i}$$

(12)

$$N_{in_{i}} = \begin{cases} N_{in} \text{ when } i = 0 \\ f_{r} N_{r_{i}} + f_{p} N_{in_{i-1}} Y_{in_{i-1}} Y_{beforetest} \text{ when } i > 0 \end{cases}$$

(13)

where parameters without subscripts ( $N_{in}$ ,  $C_{in}$ , and  $Y_{in}$ ) indicate values entering the process (Figure 2) and the form of (8) follows from [11]. The total number of parts that successfully pass the test process is given by,

$$N_{out} = \sum_{i=0}^{n} N_{out_i} . \qquad (14)$$

The part counting in (8)-(13) assumes that all false positives on good parts go through diagnosis and back into test without scrapping of parts in diagnosis or rework. The formulation is also only valid when  $f_p < 1$ ,  $Y_{in} > 0$  and  $Y_{beforetest} > 0$ . The input cost ( $C_{ini}$ ) that appears in (1)-(4) is given by  $C_{in}$  when i = 0 and by (15) when i > 0.

$$C_{in_{i}} = \frac{\left(C_{in_{i-1}} + C_{test} + C_{diag}\right)f_{p}Y_{in_{i-1}}Y_{beforetest}N_{in_{i-1}}}{N_{in_{i}}} + \frac{\left(C_{in_{i-1}} + C_{test} + C_{diag} + C_{rew}\right)f_{r}N_{r_{i-1}}}{N_{in_{i}}}$$

(15)

The input yield  $(Y_{ini})$  that appears in (4) and (8)-(15) is given by  $Y_{in}$  when i = 0 and by (16) when i > 0.

$$Y_{in_{i}} = \frac{f_{p}Y_{in_{i-1}}Y_{beforetest}N_{in_{i-1}} + Y_{rew}f_{r}N_{r_{i-1}}}{N_{in_{i}}}.$$

(16)

The final yield of parts that successfully pass the process is given using the general result in [11], [12], by,

$$Y_{out} = \frac{\sum_{i=0}^{n} Y_{aftertest} N_{out_i} \left( \frac{(1 - f_p) Y_{in_i} Y_{beforetest}}{1 - f_p Y_{in_i} Y_{beforetest}} \right)^{1 - f_c}}{N_{out}}$$

(17a)

when f<sub>p</sub> applies to only good parts, and

$$Y_{out} = \frac{\sum_{i=0}^{n} Y_{aftertest} N_{out_i} (Y_{in_i} Y_{beforetest})^{1-f_c}}{N_{out}} \quad (17b)$$

when  $f_p$  applied to all parts.

Note,  $N_{in}$  cancels out of (5) and (17) making the total cost per part and final yield independent of the number of parts that start the process, which is intuitively correct since no volume-sensitive effects (such as material or equipment costs) are included in the model so far.

In order to support the calculation of equipment costs associated with the test, diagnosis and rework activities, the total time spent in each activity can be accumulated. The effective tester, diagnosis, and rework time per part can be formulated using (8)-(13),

$$\Gamma_{\text{total test}} = \frac{T_{\text{test}}}{N_{\text{out}}} \sum_{i=0}^{n} N_{\text{in}_{i}}$$

(18)

$$T_{\text{total diag}} = \frac{T_{\text{diag}}}{N_{\text{out}}} \sum_{i=1}^{n} \left( N_{dl_i} + B \right)$$

(19)

where

$B = \begin{cases} f_p N_{in_i} Y_{in_i} Y_{beforetest}, \text{ when } f_p \text{ applies to only good parts} \\ f_p N_{in_i}, \text{ when } f_p \text{ applies to all parts} \end{cases}$

$$T_{\text{total rew}} = \frac{T_{\text{rew}}}{N_{\text{out}}} \sum_{i=1}^{n} N_{r_i}$$

(20)

where  $T_{test}$ ,  $T_{diag}$ , and  $T_{rew}$  represent the equipment times for individual parts.

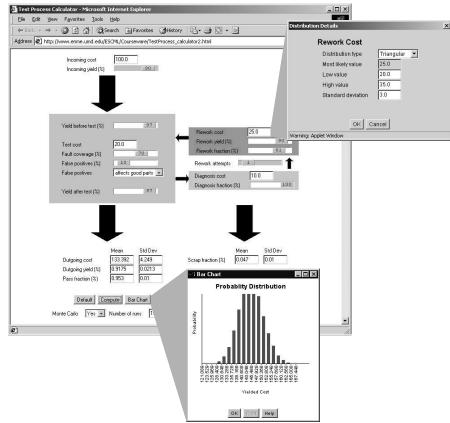

Dick et al. [13] point out that one of the main drawbacks in using economics models in general, and specifically for making test strategy decisions using economics models, is arriving at misleading results because of inaccurate inputs. To accommodate uncertainties in input data, the model has been implemented within a Monte Carlo analysis framework similar to that in [13]. Each non-integer input can have a designated distribution type (triangular distributions are used as an example in Section 4). Random numbers are used to select values from the distributions with which to perform the analysis. When a sufficiently large sample size has been completed, histograms of the output parameters can be created and mean and standard deviations of the solutions determined.

The model discussed in this paper is being used within several technology tradeoff analysis software tools and cost analysis tools. For testing and tutorial purposes, a standalone version of the model has been implemented in the web-based Java applet shown in Figure 4.

#### **4. Example Results**

This section presents example results generated using the model discussed in Section 3 and the application of the model to an electronic power module.

#### **4.1 Example Results**

The baseline data used for the first example in this section is given in Table II. The results in this section are presented in terms of yielded cost. Yielded cost is defined as cost divided by yield. In electronic assembly, yielded cost represents the effective cost per good (non-defective) assembly for a manufacturing process [14].

Figure 4 – Web-based interface for the model discussed in this paper (www.enme.umd.edu/ESCML/Courseware/TestProcess\_calculator2.html).

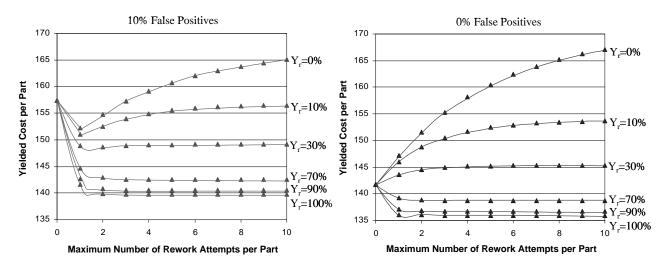

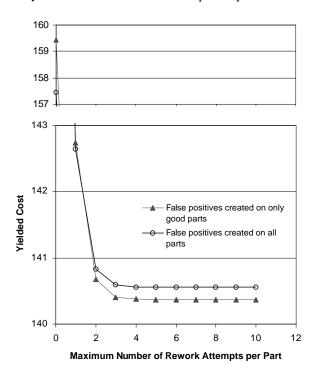

Figure 5 – Variation of final yielded cost (cost divided by yield) of parts that pass the test/diagnosis/rework process with the number of allowed rework attempts per part. In this example, false positives are only created on good parts.

|                   |     |                                                      | 7    | 4                       |     |

|-------------------|-----|------------------------------------------------------|------|-------------------------|-----|

| C <sub>in</sub>   | 100 | f <sub>c</sub>                                       | 70%  | Y <sub>in</sub>         | 90% |

| C <sub>test</sub> | 20  | f <sub>r</sub>                                       | 81%  | Y <sub>beforetest</sub> | 97% |

| C <sub>diag</sub> | 10  | $\mathbf{f}_{\mathbf{d}}$                            | 100% | Yaftertest              | 97% |

| C <sub>rew</sub>  | 25  | fp                                                   | 10%  | Y <sub>rew</sub>        | 90% |

| Rework attempts   | 2   | False positives are<br>created on good<br>parts only |      |                         |     |

*Table II – Baseline data for example results.*

Figure 5 shows that when false positives are created and rework yield is low, there is an optimum number of rework attempts per part (2 for  $Y_{rew} = 30\%$ , 1 for  $Y_{rew} = 10\%$  or less). If no false positives are created, depending on the rework yield, the cost of performing the rework, and the rework success rate, rework may not be economically viable.

Figure 6 shows the effect of whether the false positives are created on just the good parts or all the parts. With no rework (in the zero rework attempts case, parts that are identified as defective are scrapped without diagnosis), if a fixed false positive fraction only affects good parts, the resulting per part yielded cost is higher than if the false positives affect all parts – while the same number of parts are scrapped in both cases, when the false positive fraction affects all parts, some defective parts are removed resulting in a low yielded cost. When many rework attempts are allowed, false positive creation on just good parts results in an overall lower yield part (because the false positive creation didn't remove any defective parts),

and also a lower overall cost part (because fewer parts were reworked) – the net effect in this case is that the overall yielded cost per part is lower.

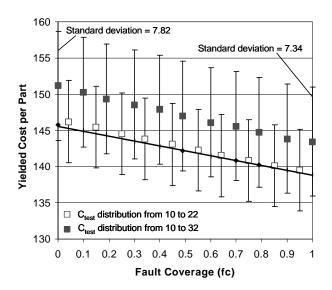

Figure 7 shows an example from the Monte Carlo analysis. The solid line on the plot represents the

Figure 6 – Effect of the false positives definition on the part population.

solution found using only the most likely values of the input parameters. The two solutions with error bars have the same most likely values but a mixture of more realistic symmetric and asymmetric triangular distributions applied, Table III. The error bars represent plus or minus one standard deviation. The standard deviation of the solid squares is larger because the range of  $C_{test}$  values assumed in the distribution is larger. The standard deviations on the yielded cost are also found to be larger for smaller values of fault coverage using the data in Table III. This is due to an increase in the standard deviation of the yield as fault coverage drops (yield depends on quantities raised to the 1-f<sub>c</sub> power).

| Table III – Data for example Monte Carlo results. All |

|-------------------------------------------------------|

| distributions are triangular with the parameters      |

| denoted in the table by most likely (low high)        |

| denoted in the table by - most likely (low,high). |                     |  |  |  |

|---------------------------------------------------|---------------------|--|--|--|

| C <sub>in</sub>                                   | 100 no distribution |  |  |  |

| C <sub>test</sub>                                 | 20 (10,22)          |  |  |  |

| C <sub>diag</sub>                                 | 10 (5,15)           |  |  |  |

| C <sub>rew</sub>                                  | 25 (20,35)          |  |  |  |

| Rework attempts                                   | 2                   |  |  |  |

| f <sub>c</sub>                                    | 70% no distribution |  |  |  |

| $\frac{f_c}{f_r}$                                 | 81% (78,90)         |  |  |  |

| $f_d$                                             | 100% (92,100)       |  |  |  |

| f <sub>p</sub>                                    | 10% (5,15)          |  |  |  |

| Ý <sub>in</sub>                                   | 90% no distribution |  |  |  |

| Y <sub>beforetest</sub>                           | 97% (90,100)        |  |  |  |

| Y <sub>aftertest</sub>                            | 97% (90,100)        |  |  |  |

| Y <sub>rew</sub>                                  | 90% (80,100)        |  |  |  |

| False positives are created on good parts only    |                     |  |  |  |

#### 4.2 Application of the Model to an AEPS Module

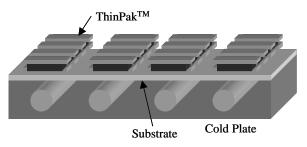

The model developed in this paper has been used to optimize the location of test/diagnosis/rework operations in the manufacturing process for an Advanced Electronic Power Systems (AEPS) module. AEPS refers to a system built around a packaging concept that replaces complex power electronics circuits with a single multi-function device that is intelligent and/or programmable. For example, depending on the application, an AEPS might be configured to act as an AC to DC rectifier, DC to AC inverter, motor controller, actuator, frequency changer, circuit breaker etc. The AEPS module considered here consists of 16 ThinPak<sup>TM</sup> devices [15], Figure 8. A ThinPak<sup>TM</sup> is a ceramic chip scale package for discrete

Figure 7 – Point solution versus solutions with distributed input parameters

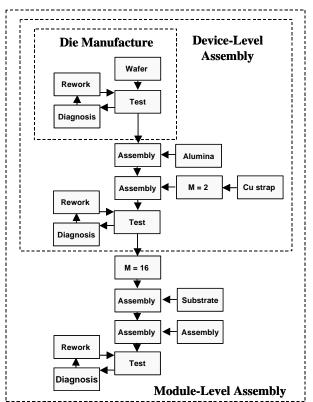

3-terminal high power devices. A simplified process flow for the AEPS module is shown in Figure 9.<sup>4</sup> The test economics challenge with the AEPS module is to determine where to perform test and rework operations: die level, device level, and/or module level.

Not all permutations of test and rework shown in Figure 9 were analyzed. Die level rework was omitted, the die used in the ThinPak<sup>TM</sup> devices are

Figure 8 – AEPS module (600V half bridge) with 16 ThinPak<sup>TM</sup> devices mounted on it.

<sup>&</sup>lt;sup>4</sup> The multiplier step, denoted by "M", appears twice in the AEPS module process flow. The "M=2" process step denotes the assembly of two copper straps with the die-alumina lid assembly to complete the Thinpak<sup>TM</sup> device level assembly. Similarly, the "M=16" process step denotes the assembly of sixteen Thinpak<sup>TM</sup> devices on the substrate during the module level assembly.

Figure 9 – Simplified process flow for the AEPS module including candidate test/diagnosis/rework operations.

relatively inexpensive and no practical methods of reworking defective die are available. We also did not consider device-level test or rework in the present analysis.

The analysis performed on the AEPS module includes a variable rework model where  $C_{rew}$  and  $Y_{rew}$  are not treated as constants (as in the analysis in Section 4.1), but are variables based on the assumption that rework is dominated by the replacement of defective ThinPak<sup>TM</sup> devices.  $C_{rew}$  and  $Y_{rew}$  are determined using,

$$C_{\text{rew}} = C_{\text{rew-fixed}} + C_{\text{device}} N_{\text{device}_{i}} (1 - Y_{\text{device}})$$

(21)

$$Y_{\text{rew}} = Y_{\text{rework process}} Y_{\text{device}}^{N_{\text{device}_i}(l-Y_{\text{device}})}, \quad (22)$$

where  $C_{device}$  and  $Y_{device}$  are the cost and yield of the ThinPak<sup>TM</sup> devices when they enter the module assembly process.  $N_{devicei}$  is the total number of ThinPak<sup>TM</sup> devices replaced in the previous rework attempt given by,

$$N_{device_{i}} = N_{device_{i-1}} \left( 1 - Y_{device} \right)$$

(22)

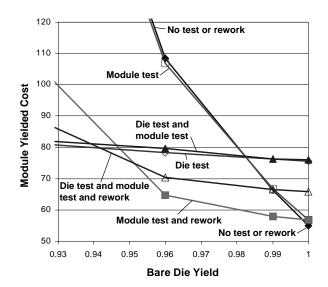

Figure 10 – Test/diagnosis/rework placement for an AEPS module containing 16 devices. The system yielded cost are means from Monte Carlo analysis.

where  $N_{device0} = 16$  in our example case.

Figure 10 shows results of an analysis on the AEPS module. When the yield of the die is 100%, no test or rework is the most economical solution (this result is intuitive). Module test is relatively inexpensive and scraps defective modules prior to shipping, however, it has overall effect on the yielded cost (the ratio of cost to yield). When die test is introduced, the cost shifts up by an amount equal to the test cost per die multiplied by 16. Again, performing module test along with die test improves the yield of modules exiting the process, but has little effect on the overall yielded cost. When module-level rework is performed, some of the scrapped modules are recovered thus reducing the cost. For die with yields between 0.998 and 0.952 module test and rework is the most economical. For 0.952 > yield >0.942 die test and module test and rework is best and for yield < 0.942 die test only is the best solution.

#### **5. Discussion and Summary**

This paper details a test/diagnosis/rework analysis model for use in technical cost modeling of electronic assemblies. The approach includes a model of test operations characterized by fault coverage, false positives, and defects introduced in test, in addition to rework and diagnosis operations that have variable success rates and their own defect introduction mechanisms. The model can accommodate an arbitrary number of rework attempts on any given assembly and can be used to optimize the fault coverage and rework investment during system tradeoff analyses.

The method presented in this paper is appropriate for use when the entire test/diagnosis/rework is either

a) summarized into a single process where the describing parameters (e.g.,  $f_c$ ,  $f_p$ ,  $C_{test}$ ,  $C_{diag}$ ,  $C_{rew}$ , ...) represent effective values averaged over a range of fault types. In this case the false positive fraction,  $f_p$ , should act only on good parts, i.e., parts without the fault(s) that the particular test step corresponds to.

b) divided into individual fault-specific processes, where the describing parameters represent values specific to a particular fault (in this case,  $Y_{in}$  would be with respect to a particular fault type). In this case the false positive fraction,  $f_p$ , should act on all parts.

## Acknowledgements

This work was supported in part by the Electronic Building Block (PEBB) program from the Office of Naval Research under "Decision Support for Design of High Performance, High Reliability PEBB," Grant #N000149810842; and an ECTC educational grant from the NSF Packaging Research Center at the Georgia Institute of Technology and the IEEE.

# References

- 1. J. Busch, "Cost Modeling as a Technical Management Tool", *Research Technology Management*, November, 1994.

- L. H. Ng and F. R. Field, "Cost Modeling for Printed Circuit Board Fabrication," *Printed Circuit Fabrication*, Vol. 12, No. 2, March 1989.

- 3. C. Bloch and Ranganathan, R., "Process Based Cost Modeling", *IEEE Transactions on Components, Hybrids, and Manufacturing Technologies*, pp. 288-294, June 1992.

- C. Dislis, J. H. Dick, I.D. Dear, I. N. Azu, and A. P. Ambler, "Economics Modeling for the Determination of Test Strategies for Complex VLSI Boards", *Proc. International Test Conference*, pp. 210-217, 1993.

- M. Abadir, A. Parikh, L. Bal, P. Sandborn, and C. Murphy, "High Level Test Economics Advisor", *Journal of Electronic Testing: Theory and Applications*, Vol. 5, pp. 195-206, May 1994.

- 6. P. A. Sandborn and Moreno, H., *Conceptual Design of Multi-chip Modules and Systems*, Kluwer Academic Publishers, pp. 152-169, Boston, 1994.

- 7. M. Tegethoff and T. Chen "Defects, Fault Coverage, Yield and Cost, in Board Manufacturing," *Proc. International Test Conference*, pp. 539-547, 1994.

- 8. M. Scheffler, D. Ammann, A. Thiel, C. Habiger, and G. Troster, "Modeling and Optimizing the Costs of Electronic Systems," *IEEE Design & Test of Computers*, Vol. 15, No. 3, pp. 20-26, July-September 1998.

- 9. C. Dislis, J. H. Dick, I. D. Dear, and A. P. Ambler, *Test Economics and Design for Testability, Ellis Horwood*, 1995.

- V. Garg, D. J. Stogner, C. Ulmer, D. Schimmel, C. Dislis, S. Yalamanchili, and D. S. Wills, "Early Analysis of Cost/Performance Trade-Offs in MCM Systems", *IEEE Transactions on Component, Packaging and Manufacturing Technology*, Part B, Vol. 20, No. 3, pp. 308-319, Aug. 1997.

- 11. T. W. Williams and N. C. Brown, "Defect Level as a Function of Fault Coverage", *IEEE Transactions on Computers*, pp. 987-988, December 1981.

- V. Agrawal, S. Seth, and P. Agrawal, "Fault Coverage Requirement in Production Testing of LSI Circuits," *IEEE J. of Solid-State Circuits*, Vol. SC-17, No. 1, pp. 57-61, Feb. 1982.

- J. H. Dick, E. Trischler, C. Dislis, and A. P. Ambler, "Sensitivity Analysis in Economic Based Test Strategy Planning," *Journal of Electronic Testing: Theory and Applications (JETTA)*, Vol. 5, pp. 239-252, May 1994.

- 14. D. Becker and P. Sandborn, "On the Use of Yielded Cost in Modeling Electronic Assembly Processes," to be published *IEEE Trans. on Electronics Packaging Manufacturing.*

- 15. P. McCluskey, R. Iyengar, S. Azarm, Y. Joshi, P. Sandborn, P. Srinivasan, B. Reynolds, D. Gopinath, T.K. Trichy, and V. Temple, "Rapid Reliability Optimization of Competing Power Module Topologies Using Semi-Analytical Fatigue Models," *Proceedings of the PowerSystems World HFPC'99 Conference*, Chicago, IL, pp. 184-194, November 1999.