Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# A New Transformerless Ultra High Gain DC-DC Converter for DC Microgrid Application

Shahrukh Khan<sup>1</sup>, [Student Member, IEEE], Mohammad Zaid<sup>\*1</sup>, [Member, IEEE], Arshad Mahmood<sup>1</sup>, Abbas Syed Nooruddin<sup>1</sup>, Javed Ahmad<sup>2</sup>, Mamdouh L. Alghaythi<sup>3</sup>, [Member, IEEE], <sup>4</sup>Basem Alamri [Member, IEEE], Mohd Tariq<sup>1</sup>, [Senior Member, IEEE], Adil Sarwar<sup>1</sup>, [Senior Member, IEEE], Chang-Hua Lin<sup>2</sup>, [Member, IEEE]

<sup>1</sup>Department of Electrical Engineering, Aligarh Muslim University, Aligarh, 202002, India

<sup>2</sup>Department of Electrical Engineering, National Taiwan University of Science and Technology, No. 43, Keelung Rd., Sec.4, Da'an Dist., Taipei City 10607, Taiwan

<sup>3</sup>Department of Electrical Engineering, Faculty of Engineering, Jouf University, Sakaka 72388, Saudi Arabia

<sup>4</sup>Department of Electrical Engineering, College of Engineering, Taif University, Taif 21944, Saudi Arabia

Corresponding author: \*Mohammad Zaid (mohammad.zaid@zhcet.ac.in)

**ABSTRACT** High gain dc-dc converters are used in several applications which include solar photovoltaic system, switch-mode power supplies and fuel cells. In this paper, an ultra-high gain dc-dc boost converter is proposed and analysed in detail. The converter has a gain of six times as compared with the boost converter. The high gain is achieved by utilizing switched inductors and switched capacitors. A modified voltage multiplier cell (VMC) with switched inductors is proposed. The converter has a single switch which makes its operation easy. Moreover, the voltage across the switch, diodes and capacitors are less than the output voltage which increases the overall efficiency of the converter. The converter performance in steady-state is analysed in detail and it is compared with other latest high gain converters. The working of the converter in non-ideal conditions is also discussed in detail. The loss analysis is done using PLECS software by incorporating the real models of switches and diodes from the datasheet. To confirm and validate the working of the proposed converter a hardware prototype of 200 W is developed in the laboratory. The converter achieves high gain at low duty ratios and its performance is found to be good in open and closed loop conditions.

INDEX TERMS Boost Converter, DC Microgrid, Duty cycle, Ultra High Gain, Voltage stress

#### I. INTRODUCTION

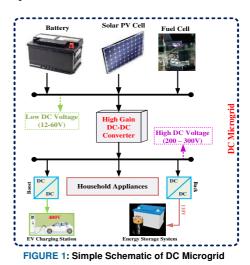

Power electronics play an important role to extract maximum energy from renewable and clean energy sources. Figure 1 shows a schematic of a DC microgrid. High gain dc-dc converters act as a medium between the load and the source and boost the low voltage(12V-60V) generated by the battery, solar photovoltaic (PV) and fuel cell to high DC voltage(200-300V). Moreover, a high gain dc-dc converter in a DC microgrid maintains the dc-link voltage to the desired value [1]. A combination of supercapacitors and a high gain dc-dc converter is also employed nowadays in a DC microgrid because supercapacitors have high power density but a low voltage rating. High gain converters are nowadays used in level three fast charging of electric vehicle (EV). A combination of a high gain converter with an inverter can be used to feed AC loads in islanded mode operation of a DC microgrid. High gain converters have gained prominence because the traditional boost converters and their variants [1] are associated with poor efficiency and high duty cycle operation to achieve the high gain. Also, there is a problem of reverse recovery in the diode at an increased duty cycle. These converters are broadly classified into isolated and non-isolated structures. Isolated converters isolate the output from the input electrically dividing circuit into two separate sections preventing the direct flow of current. This is achieved by using a high-frequency transformer but it increases the size and cost [3]-[6] of the converter. Isolated topologies are favoured in high power applications and where common ground between source and load is required.

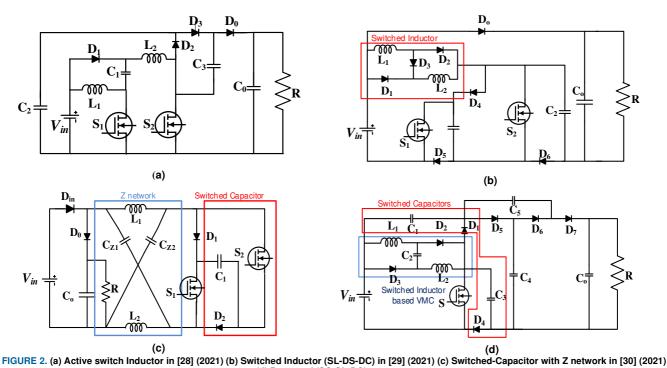

(d) Proposed (SC-SL-DC) converter Non-isolated converters are favoured where isolation of input from output is not required. They can be classified as coupled and non-coupled types [7]. The coupled inductor topologies can produce very high voltage gain with low stress on the semiconductor switch but the problems with leakage inductance can result in large voltage spikes across the switch for which a clamped circuit needs to be designed. To achieve a high gain capacitor-diode voltage multiplier cell and cascading of two or more converters is employed. Several new and modified topologies use voltage multiplier circuit (VMC) made of switched capacitors and inductors to increase the gain of the converter. The quadratic boost (QBC) and cubic boost topologies can produce high gain at low duty cycles with reduced stress on switching devices [8]-[10] but at higher duty ratios the efficiency may decrease with an increase in current. Further, the inductor core is more prone to enter saturation at higher duty cycles. In [11] a new quadratic boost converter is proposed with lower inductor current ripple and low stress across the switch. Another class of high gain boost converter is a quasi-z-source or z-source converter that is used to increase the gain of the converter where the inductor is replaced by an impedance network but these converters have a restricted duty cycle [12],[13] operation. Interleaved boost converters are being used to acquire high output voltage and high efficiency [14] with a lesser number of switches. In a multiphase interleaved converter is introduced along with a z-source network to achieve high gain. The input current ripple is low therefore there the need for an input filter does not arise. The problem with interleaved converters is that a voltage boost circuit is needed at the end to increase the gain [15] of the converter. Several new converter topologies have been discussed in [16] with the well-known Cockcroft-Walton voltage multiplier cell. A new single-ended primary inductor

converter (SEPIC) is presented in [17] with a single switch is used to achieve high gain. Another new SEPIC converter with both buck and boost topology is presented in [18]. Single input multiport output is a good way of getting different output voltage using a single input. These converters have better voltage regulation capability and low stress across the output capacitor as compared to single input [19],[20] single-output (SISO) converter. They can be used as individual SISO converters.

A quadratic boost converter is proposed by using the voltage lift technique (VL) in [21]. In [22] VL technique is used to get desired value of gain but the converter utilizes two switches that are switched alternately. A hybrid converter based on voltage multiplier cell (VMC) and switched capacitor cells with high gain is presented in [23]. It overcomes shortcomings such as high voltage and current stress on the power devices. A converter with a similar gain is presented by authors in [24] but the stress on two switches is different and it uses the diode voltage capacitor multiplier and switched inductor voltage multiplier to achieve high gain. A high step-down interleaved converter is presented in [25] using a similar concept of switched/series capacitor using six switches. A novel switched impedance networkbased converter is presented in [26]. It utilizes a voltage doubler-switched capacitor network to achieve higher gain at lower duty ratios. A multistage structure can significantly increase the gain but efficiency can be low due to a greater number of components. A hybrid zeta boost converter with a switched inductor is proposed in [27] but its voltage gain is not very high. A new tranformerless active switched network is presented in [28] by using two switches but the gain achieved is lower than the proposed topology in this paper. A switched capacitor network-based topology is presented in the paper [29]. In [30] the switched inductor topology has used two inductor and two switches but the voltage gain is not very high. A modified SEPIC converter is presented in [32] to achieve high voltage gain. In [34] the converter uses parallel input and series output (PISO) technique to increase voltage gain. Furthermore, the stress voltage of switches and diodes has been reduced.

In this article, the proposed high gain converter has a VMC made up of switched inductors. A combination of switched capacitors and VMC achieves ultra-high gain with only one switch and two inductors. High gain topologies proposed in [28], [29], [30], [31] utilize two switches and have much less voltage gain as compared with the proposed converter in this paper. The attractive features of the proposed converter are

- The converter achieves a voltage conversion ratio of six times that of the conventional boost converter.

- The converter uses a single switch that has low voltage stress i.e. one-third of output voltage.

- A coupled inductor is not used so the problem of leakage inductance is avoided.

- The voltage stress on all the semiconductor devices is equal. The devices with a uniform rating and low internal resistance can be used.

The paper discusses the structure and principle of operation of the converter in section II. Steady-state operation of the proposed converter in the continuous and discontinuous mode of operation is presented in section III and IV respectively. In section V and VI non-ideal gain analysis and comparative study of the proposed structure is presented respectively. Experimental results and efficiency of the converter are shown in section VII. In section VIII conclusion is presented.

## II. OPERATING PRINCIPLE OF PROPOSED CONVERTER (SC-SL-DC)

## A. CIRCUIT DESCRIPTION

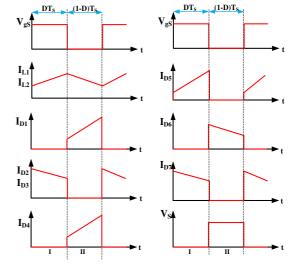

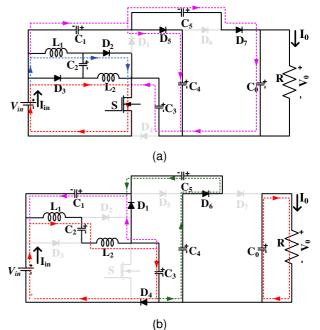

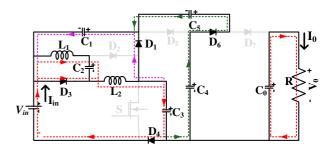

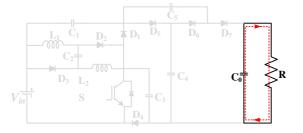

The proposed dc-dc converter topology is presented in Figure 2. The converter consists of a single switch (S), two inductors ( $L_1$  and  $L_2$ ), seven diodes ( $D_1, D_2, ..., D_7$ ) and six capacitors including one capacitor  $C_0$  as an output filter which filters the output pulsating current and provide a smoothed output voltage. The combination of ( $L_1, L_2, D_1, D_2$  and  $C_1$ ) is a modified switched capacitor cell while the combination of ( $C_1, D_1, C_3$  and  $D_4$ ) is switched capacitor cell. Some important waveforms for the proposed converter are shown in Figure 3. All capacitors are sufficiently large, therefore the voltage across capacitors is assumed to be constant. And all components are assumed as ideal.

#### **B. MODES OF OPERATION**

This converter can be operated in both CCM and DCM modes of operation. The CCM operation of the proposed converter has two modes. In the first mode when the switch is conducting and the second one is analyzed when the switch is turned OFF. Analysis of the proposed converter for one switching period under CCM mode and in steady-state is as follows:

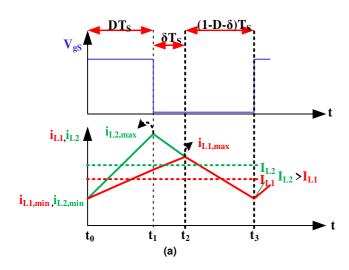

FIGURE 3. Waveforms associated with the converter in CCM

FIGURE 4: Modes of operations for the proposed converter (a) When the switch is ON (b) When the switch is OFF

#### MODE I: WHEN SWITCH IS ON (0 < t < DTs)

Mode I of operation is shown in Figure 4(a). In this interval, the switch is turned ON and the diodes  $D_2$ ,  $D_3$ ,  $D_5$  and  $D_7$  are forward biased. The voltage across inductors  $L_1$  and  $L_2$  is equal to the input voltage (V<sub>in</sub>) by which they are magnetized and therefore, inductor currents  $I_{L1}$  and  $I_{L2}$  increase linearly. In this mode, Capacitor C<sub>1</sub> discharges and transfer its energy through capacitor C<sub>5</sub> and load. During this interval, C<sub>2</sub> and C<sub>3</sub> discharge through L<sub>2</sub> and C<sub>4</sub>. Thus, related equations can be drawn out as follows:

The voltage across inductors appears as shown (1)

$$\begin{cases} V_{L1} = L_1 \frac{dI_{L1}}{dt} = V_{in} \\ V_{L2} = L_2 \frac{dI_{L2}}{dt} = V_{in} \end{cases}$$

(1)

The voltage across capacitors is derived from Figure 4(a) using KVL and KCL as follows:

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3110668, IEEE Access

IEEE Acces

$$\begin{cases} V_{C2} = -V_{in} \\ V_{C4} + V_{C5} = V_o \\ V_{C1} + V_{C5} + V_{C3} = V_o - V_{in} \end{cases}$$

(2)

Current relations through capacitors, inductors, diodes and switch can be estimated as follows:

$$\begin{cases} C_1 \frac{dV_{C1}}{dt} = I_{C1} = I_{in} - I_{L1} - I_{D3} \\ C_2 \frac{dV_{C2}}{dt} = I_{C2} = I_{L1} - I_{D2} \\ C_3 \frac{dV_{C3}}{dt} = I_{C3} = I_{L2} + I_{D2} - I_S \\ C_4 \frac{dV_{C4}}{dt} = I_{D5} \\ C_0 \frac{dV_{C0}}{dt} = I_{C0} = I_{C5} - I_0 \end{cases}$$

(3)

### MODE II: WHEN SWITCH IS OFF ( $DT_s < t < T_s$ )

In this interval, the switch is turned OFF and the diodes  $D_1$ , D<sub>4</sub> and D<sub>6</sub> are forward biased and the other three diodes are reversed biased. The circuit diagram is shown in Figure 4(b). During this interval,  $V_{in}$  charges  $C_1$  and  $L_1$  charges  $C_2$ . Inductor L<sub>2</sub> transfer its stored energy to C<sub>3</sub>. Output capacitor C<sub>0</sub> transfer its energy to load R.

Using KVL and KCL in mode II, the voltage across inductors come out as follows:

$$V_{L1} + V_{L2} = L_1 \frac{dI_{L1}}{dt} + L_2 \frac{dI_{L2}}{dt} = V_{in} - V_{C2} - V_{C3}$$

(4)

In (2), it is derived that

(2), it is derived the

$$V_{C2} = -V_{in}$$

Equation (4) can now be written as

$$V_{L1} + V_{L2} = 2V_{in} - V_{C3} \tag{5}$$

The voltage across the capacitors can be written by applying KVL in Figure 4(b)

$$\begin{cases} V_{C4} - V_{C5} = V_{C3} \\ V_{C3} - V_{C1} = V_{in} \end{cases}$$

(6)

Current passing through capacitors relations can be shown as follows:

$$\begin{cases}

C_{1} \frac{dV_{C_{1}}}{dt} = I_{C1} = I_{in} - I_{L1} \\

C_{2} \frac{dV_{C2}}{dt} = I_{C2} = I_{L1} = I_{L2} \\

C_{3} \frac{dV_{C3}}{dt} = I_{C3} = I_{L1} - I_{D1} \\

C_{4} \frac{dV_{C4}}{dt} = C_{5} \frac{dV_{C5}}{dt} = I_{C4} = I_{C5} = I_{C1} - I_{D1} \\

C_{0} \frac{dV_{C0}}{dt} = I_{C0} = -I_{0}

\end{cases}$$

(7)

#### **III.STEADY STATE ANALYSIS IN CCM**

### A. CALCULATION OF CAPACITOR VOLTAGES AND **VOLTAGE GAIN**

Applying the principle of volt-second balance on inductors  $L_1$  and  $L_2$  and using (1), (2), (4) and (6) the voltage conversion ratio, M can be derived as shown.

$$\int_{0}^{DT_{S}} (V_{L1} + V_{L2}) dt + \int_{DT_{S}}^{T_{S}} (V_{L1} + V_{L2}) dt = 0$$

Where,  $T_{\rm S}$  is switching time period.

Using this equation following results can be drawn out as.

$2V_{in}D + (2V_{in} - V_{C3})(1 - D) = 0$ (8) It is clear from (8), that

$$V_{C3} = \frac{2V_{in}}{(1-D)}$$

(9)

From (6) it can be written that

$$V_{C4} - V_{C5} = V_{C3}$$

Using (9) in (6) the following equation can be written

$$V_{C4} - V_{C5} = \frac{2V_{ln}}{(1-D)} \tag{10}$$

Again from (2)

$$V_{C4} + V_{C5} = V_o \tag{11}$$

Solving (10) and (11), it can be shown that

$$V_{2} = V_{12} = \frac{V_{12}}{V_{12}}$$

$$\begin{cases} V_{C4} = \frac{-0}{2} + \frac{u_{1}}{(1-D)} = \frac{-0}{3} \\ V_{C5} = \frac{V_0}{2} - \frac{V_{in}}{(1-D)} = \frac{V_0}{3} \end{cases}$$

(12)

From (2) again,

$$V_{C1} + V_{C5} + V_{C3} = V_o - V_{in}$$

(13)

Also, from (6)

$$V_{C1} = V_{C3} - V_{in} \tag{13}$$

Putting this value in equation (13), it can be shown that  $V_{C5} + 2V_{C3} = V_o$ (14)

Using (12) and (14), it can be drawn out easily.

$$V_{C3} = \frac{V_0}{4} + \frac{V_{in}}{2(1-D)} = \frac{V_0}{3}$$

(15)

From (9) and (15), voltage gain is derived as,

$$M = \frac{V_0}{V_{in}} = \frac{6}{(1-D)}$$

(16)

According to (16), it can be seen that the voltage gain of the proposed converter is six times higher than that of the conventional boost converter.

### **B. VOLTAGE AND CURRENT STRESSES OF POWER** DEVICES

In Figure 4, by applying KVL the voltage appeared across the switch  $(V_{sw})$ , diodes $(V_d)$  and capacitors  $(V_c)$  when they are not conducting, can be expressed as

$$\begin{cases} V_{SW} = V_{C3} = \frac{V_0}{3}, V_{D1} = V_{C4} - V_{C3} = \frac{V_0}{3} \\ V_{D2} = V_{D3} = \frac{V_0}{3}, V_{D4} = V_{C3} = \frac{V_0}{3} \\ V_{D5} = V_{D6} = V_{C5} = \frac{V_0}{3}, V_{D7} = V_0 - V_{C4} = \frac{V_0}{3} \end{cases}$$

(17)

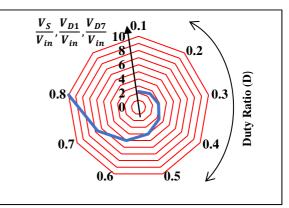

The stress on different semiconductor devices is shown in Figure 9.

Assuming a lossless circuit, it can be written

$$P_{in} = P_{out} \Rightarrow V_{in}I_{in} = V_oI_o \tag{18}$$

Where  $I_{in}$  and  $I_0$  are input and output currents respectively. From (18) and (16), it can be written down:

$$\frac{I_{in}}{I_0} = \frac{V_0}{V_{in}} = M = \frac{6}{(1-D)}$$

(19)

From (19), dc input current can be calculated as,

$$I_{in} = \left(\frac{6}{1-D}\right) I_0 \tag{20a}$$

Applying the principle of current balance on the capacitors  $C_1$  and  $C_2$  and using (3) and (7) it can be written as:

$$\int_{0}^{DT_{S}} (I_{in} - I_{L1} - I_{D3}) dt + \int_{DT_{S}}^{T_{S}} (I_{in} - I_{L1}) dt = 0 \quad (20b)$$

$$\int_{0}^{DT_{S}} (I_{L1} - I_{D2}) dt + \int_{DT_{S}}^{T_{S}} (I_{L1}) dt = 0$$

After solving the above equation, the average current through inductors can be found out as

$$I_{L1} = I_{L2} = I_L = \left(\frac{3}{1-D}\right) I_0$$

(21)

The dc values of current through the semiconductor devices can be found as

$$\begin{cases} I_{SW_{avg}} = \frac{5+D}{1-D} I_O \\ I_{D1} = I_{D2} = I_L = \left(\frac{3}{1-D}\right) I_O \\ I_{D3} = I_{D4} = I_{D5} = I_{D6} = I_{D7} = I_O \end{cases}$$

(22)

### C. SELECTION OF INDUCTORS AND CAPACITORS

For a given suitable value of ripple of inductor currents  $\Delta I_{L1}$ and  $\Delta I_{L2}$  at a fixed value of switching frequency  $f_s$  for this converter, inductances can be extracted from (1) as:

$$\begin{cases} L_1 = \frac{V_{in}D}{\Delta I_{L1}f_s} \\ L_2 = \frac{V_{in}D}{\Delta I_{L2}f_s} \end{cases}$$

(23)

Moreover, within the valid range of voltage ripple, the value of capacitances can be calculated from (3) and (7) as:

$$\begin{cases} C_1 = \frac{3V_0}{\Delta V_{C1}f_S R}, C_2 = \frac{3V_0}{\Delta V_{C2}f_S R} \\ C_3 = \frac{2V_0}{\Delta V_{C3}f_S R}, C_4 = \frac{V_0}{\Delta V_{C4}f_S R} \\ C_5 = \frac{V_0}{\Delta V_{C5}f_S R}, C_o = \frac{V_0}{\Delta V_{C0}f_S R} \end{cases}$$

(24)

To obtain the desired output voltage at the given input voltage, duty cycle D can be calculated. From (16), the duty cycle is:

$$D = \frac{V_0 - 6V_{in}}{V_0}$$

(25)

## IV. EFFECT OF UNEQUAL INDUCTANCES ON VOLTAGE GAIN

The operation of the converter depends on the inductance values of inductor  $L_1$  and  $L_2$ . The current through the inductor will have different slopes and it will change the current waveform of the inductor due to different values of inductances of  $L_1$  and  $L_2$ .

## A. IF INDUCTANCE VALUE L1 IS LARGER THAN L2

The current waveform through the inductor  $L_1$  and  $L_2$  is shown in Figure 5. The converter SC-SL-DC is operated in three modes.

(b) FIGURE 5. (a) Inductor current waveforms when L1>L2 (b) Mode II MODE I: WHEN SWITCH IS ON ( $0 < t < t_1$ )

The Switch is turned ON. This mode is same as Mode I and the equivalent circuit is shown in Figure 4(a). Diode D<sub>1</sub>, D<sub>4</sub>, D<sub>6</sub> are reverse biased while the diodes D<sub>2</sub>, D<sub>3</sub>, D<sub>5</sub> and D<sub>7</sub> are forward biased. The voltage across the inductors L<sub>1</sub> and L<sub>2</sub> is equal to input voltage by which they are magnetized and therefore, inductor currents I<sub>L1</sub> and I<sub>L2</sub> increase linearly with different slopes. The slope of inductor currents of L<sub>1</sub> and L<sub>2</sub> can be achieved as

$$\frac{dI_{L1}}{dt} = \frac{V_{in}}{L_1} \tag{26}$$

$$\frac{dI_{L2}}{dt} = \frac{V_{in}}{L_2} \tag{27}$$

In this mode the current through  $L_1$  is less than current through  $L_2$  because the inductance value of  $L_1 > L_2$ .

#### MODE II: WHEN SWITCH IS ON $(t_1 < t < t_2)$

Switch is just turned OFF. This mode occurs for a very duration of  $\delta T_S$  as shown in Figure 5(a). The equivalent circuit in this mode is shown in Figure 5(b). Diode D<sub>1</sub>, D<sub>3</sub>, D<sub>4</sub> and D<sub>6</sub> are forward biased while the diodes D<sub>2</sub>, D<sub>5</sub> and D<sub>7</sub> are reverse biased. Inductor current I<sub>L1</sub> is smaller than I<sub>L2</sub> as shown in Figure 5(a). The current through L<sub>1</sub> has positive slope and magnetizes in this period and the current L<sub>2</sub> has large negative slope and discharge in this period. The current through D<sub>3</sub> will be difference between inductor current I<sub>L2</sub> and I<sub>L1</sub>.

The slope of inductor currents of  $L_1$  and  $L_2$  can be achieved as

$$\frac{dI_{L1}}{dt} = \frac{-V_{C2}}{L_1} = \frac{V_{in}}{L_1}$$

(28)

$$\frac{dI_{L2}}{dt} = \frac{V_{in} - V_{C3}}{L_2}$$

(29)

In this mode the current through  $L_1$  is less than current through  $L_2$  because the inductance value of  $L_1 > L_2$  and this mode ends when  $I_{L1}=I_{L2}$  and converter operates in Mode III.

#### MODE III: SWITCH IS OFF (t<sub>2</sub> < t < DT<sub>s</sub>)

Switch is OFF. The equivalent circuit is same as Mode II in CCM as shown in Figure 4(b). Diode  $D_1$ ,  $D_4$ ,  $D_6$  are forward biased while the diodes  $D_2$ ,  $D_3$ ,  $D_5$  and  $D_7$  are reverse biased. The inductors  $L_1$  and  $L_2$  are in series and the current through inductors  $L_1$  and  $L_2$  are equal and demagnetize with equal negative slope which can be achieved as follows

$$\frac{dI_{L1}}{dt} = \frac{2V_{in} - V_{C3}}{L_1 + L_2} \tag{30}$$

$$\frac{dI_{L2}}{dt} = \frac{2V_{in} - V_{C3}}{L_1 + L_2} \tag{31}$$

IEEEAccess\*

The average of voltage across the inductor is zero. Therefore,  $L \rightarrow D(U_{-}) + S(U_{-}) + \frac{L_1(2V_{in}-V_{C3})}{L_1(2V_{in}-V_{C3})} = 0$

$$L_{1} \rightarrow D(V_{in}) + \delta(V_{in}) + \frac{1}{L_{1}+L_{2}} (1 - D - \delta) = 0$$

(32)

$$L_{2} \rightarrow D(V_{in}) + \delta(V_{in} - V_{C3}) + \frac{L_{2}(2V_{in} - V_{C3})}{L_{1}+L_{2}} (1 - D - \delta) = 0$$

(33)

Also,

$$V_{2}$$

$$V_{C3} = \frac{V_0}{3} \tag{34}$$

On solving (32)-(34), the voltage gain of proposed converter SC-SL-DC can be obtained as

$\frac{V_0}{V_{in}}\Big|_{L1>L2} = \frac{6}{(1-D)}$ (35)

The voltage gain is same as equation (16) but the average value of inductor current  $L_1$  is less than inductor current  $L_2$ .

### A. IF INDUCTANCE VALUE L2 IS LARGER THAN L1

The current waveform through the inductor  $L_1$  and  $L_2$  is shown in Figure 6. The converter SC-SL-DC is operated in three modes as discussed below

FIGURE 6. (a) Inductor current waveforms when L1<L2 (b) Mode II

#### MODE I: WHEN SWITCH IS ON $(0 < t < t_1)$

The Switch is turned ON. This mode is same as Mode I and the equivalent circuit is shown in Figure 4(a). Diode D<sub>1</sub>, D<sub>4</sub>, D<sub>6</sub> are reverse biased while the diodes D<sub>2</sub>, D<sub>3</sub>, D<sub>5</sub> and D<sub>7</sub> are forward biased. The voltage across the inductors L<sub>1</sub> and L<sub>2</sub> is equal to input voltage by which they are magnetized and therefore, inductor currents I<sub>L1</sub> and I<sub>L2</sub> increase linearly with different slopes. The slope of inductor currents of  $L_1$  and  $L_2$  can be achieved as

$$\frac{dI_{L1}}{dt} = \frac{V_{in}}{L_1} \tag{36}$$

$$\frac{U_{L2}}{V_{L2}} = \frac{V_{in}}{V_{L2}} \tag{37}$$

In this mode the current through  $L_2$  is less than current through  $L_2$  because the inductance value of  $L_1 \le L_2$ .

### MODE II: WHEN SWITCH IS ON $(t_1 < t < t_2)$

Switch is just turned OFF. This mode occurs for a very duration of  $\delta T_S$  as shown in Figure 6(a). The equivalent circuit in this mode is shown in Figure 6(b). Diode D<sub>1</sub>, D<sub>2</sub>, D<sub>4</sub> and D<sub>6</sub> are forward biased while the diodes D<sub>3</sub>, D<sub>5</sub> and D<sub>7</sub> are reverse biased. Inductor current I<sub>L2</sub> is smaller than I<sub>L1</sub> as shown in Figure 6(a). The current through L<sub>2</sub> has positive slope and magnetizes in this period and the current L<sub>1</sub> has large negative slope and discharge in this period. The current through D<sub>2</sub> will be difference between inductor current I<sub>L1</sub>

The slope of inductor currents of  $L_1$  and  $L_2$  can be achieved as

$$\frac{dI_{L1}}{dt} = \frac{V_{in} - V_{C3}}{L_1}$$

(38)

$$\frac{dI_{L2}}{dt} = \frac{-V_{C2}}{L_2} = \frac{V_{in}}{L_2}$$

(39)

In this mode the current through  $L_2$  is less than current through  $L_1$  because the inductance value of  $L_1 < L_2$  and this mode ends when  $I_{L1}=I_{L2}$  and converter operates in Mode III.

### MODE III: SWITCH IS OFF (t<sub>2</sub> < t < DT<sub>s</sub>)

Switch is OFF. The equivalent circuit is same as Mode II in CCM as shown in Figure 4(b). Diode  $D_1$ ,  $D_4$ ,  $D_6$  are forward biased while the diodes  $D_2$ ,  $D_3$ ,  $D_5$  and  $D_7$  are reverse biased. The inductors  $L_1$  and  $L_2$  are in series and the current through inductors  $L_1$  and  $L_2$  are equal and demagnetize with equal negative slope which can be achieved as follows

$$\frac{dI_{L1}}{dt} = \frac{2V_{in} - V_{C3}}{L_1 + L_2} \tag{40}$$

$$\frac{dI_{L2}}{dt} = \frac{2V_{in} - V_{C3}}{L_1 + L_2} \tag{41}$$

The average of voltage across the inductor is null. Therefore,  $V_{L} = P(W_{L}) + S(W_{L} = W_{L}) + \frac{L_{1}(2V_{in} - V_{C3})}{L_{1}(2V_{in} - V_{C3})} (4 - P_{L} = S)$

$$L_1 \to D(V_{in}) + \delta(V_{in} - V_{C3}) + \frac{1}{L_1 + L_2} (1 - D - \delta) = 0$$

(42)

$$L_2 \to D(V_{in}) + \delta(V_{in}) + \frac{L_2(2V_{in} - V_{C3})}{L_1 + L_2} (1 - D - \delta) = 0$$

(43)

Also,

$$c_3 = \frac{v_0}{3} \tag{44}$$

On solving (42)-(44), the voltage gain of proposed converter SC-SL-DC can be obtained as

V

$$\left. \frac{v_0}{v_{in}} \right|_{L2 > L1} = \frac{6}{(1-D)} \tag{45}$$

From equation (35) and (45) it can be seen that the voltage gain is unaffected with unequal values of inductances  $L_1$  and  $L_2$  i.e. six times the traditional boost converter (TBC).

However, the average value of current through the inductors are changed.

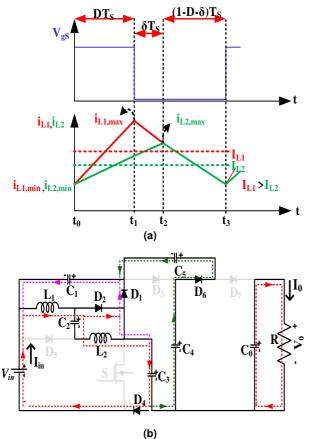

FIGURE 7. Waveforms associated with the converter in DCM

FIGURE 8. Conduction diagram in DCM Mode (Mode III)

#### **IV.STEADY STATE ANALYSIS IN DCM**

#### MODE I: WHEN SWITCH IS ON $(0 < t < DT_s)$

This mode is the same as Mode I of CCM mode and equivalent circuitry is depicted in Figure 4(a). Both the inductors  $L_1$  and  $L_2$  are magnetized by the input source voltage  $V_{in}$ . The current rises from zero to maximum value in both the inductors till the time,  $t_1$ =DT.

#### MODE II: WHEN SWITCH IS OFF ( $DT_S < t < D_1T_S$ )

This mode is equivalent to mode II of CCM. All the inductors demagnetize from their maximum value to zero at time  $t_2=D_1T$ .

### MODE III: WHEN SWITCH IS OFF AND INDUCTOR CURRENT IS ZERO ( $D_1T_s < t < T_s$ )

In this mode, all diodes  $D_1$ - $D_7$  are reverse biased. Inductor current in this interval ( $t_2 < t < t_3$ ) is zero. Energy is provided by capacitor  $C_0$  to load R. The equivalent circuit diagram and associated waveforms are depicted in Figure 7 and Figure 8. Applying the volt-sec balance principle on the inductors yields the following relation

$$D_1 = \frac{6D}{\frac{VO}{V_1 - 6}} \tag{46}$$

$$I_L = I_{D1} + I_{D4} + I_{D6} = 3I_0 \tag{47}$$

$$\frac{SVO}{R} = \frac{1}{2}D(D+D_1)\frac{Vm}{Lf_S}$$

(48)

$$\frac{V_o}{V_{in}} = \frac{D(D+D_1)R}{6Lf_S} \tag{49}$$

Using the value of  $D_1$  from (46) in (49) the following quadratic equation is obtained

$$\left(\frac{v_o}{v_{in}}\right)^2 - 6\frac{v_o}{v_{in}} - \frac{6D^2}{\beta} = 0$$

(50)

Defining  $\beta_L = \frac{6Lf_S}{R}$  as normalized inductor time constant, the ideal voltage gain (M<sub>DM</sub>)in DCM mode is calculated as

$$M_{DM} = \frac{v_0}{v_{in}} = 3 + \sqrt{9 + \frac{6D^2}{\beta_L}}$$

(51)

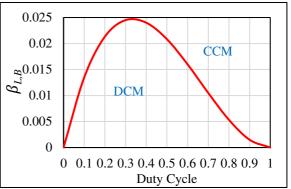

If the converter is to be operated at the boundary of CCM and DCM, then the voltage gain of both modes will be equal. The normalized inductor time( $\beta_{L,B}$ ) constant at the boundary is calculated as

$$\beta_{L,B} = \frac{D(1-D)^2}{6}$$

(52)

A plot between  $\beta_{L,B}$  and duty ratio D is shown illustrated in Figure 8. The converter operates in CCM mode if  $\beta_L > \beta_{L,B}$  and the reverse is true for DCM mode.

FIGURE 9. Semiconductor stress plot at different values of duty cycle

FIGURE 10. Normalized inductor time constant at the boundary versus duty cycle curve

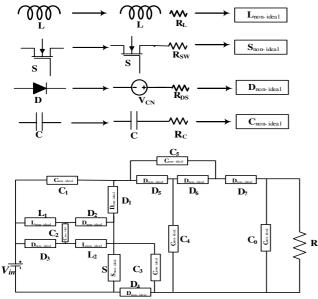

## V. PRACTICAL MODEL OF THE PROPOSED CONVERTER

The equivalent circuit of the proposed converter is shown in Figure 11.  $R_L$  is the equivalent series resistance (ESR) of the inductor  $R_{SW}$  is the switch ON-state resistance,  $R_{DS}$  and  $V_{CN}$  denote the diode internal resistance and voltage drop respectively.  $R_C$  is the equivalent series resistance (ESR) of the capacitors.

FIGURE 11: Non-ideal model with parasitic elements

## A. EFFECT OF NON-IDEALITIES ON VOLTAGE GAIN

## EFFECT OF NON-IDEAL INDUCTORS ON VOLTAGE GAIN

The effect of non-ideal inductors having parasitic resistances on voltage gain is analysed and other elements are assumed ideal.

The voltage across inductor  $L_1$  and  $L_2$  in both modes can be found as:

MODE I: The useful voltage relations are:

$$\begin{cases} V_{L1} = V_{in} - I_{L1}R_{L1} \\ V_{L1} = V_{in} - I_{L2}R_{L2} \\ V_{C2} = -V_{in} \end{cases}$$

(53)

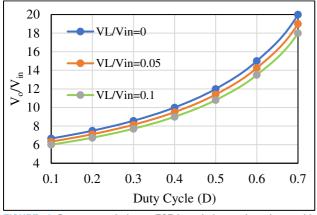

FIGURE 12: Drop across inductor ESR is varied to analyse the non-ideal effect of the inductor on voltage gain

FIGURE 13: Variation of voltage gain with different ratio of ESR resistance at a different duty cycle

MODE II: The useful voltage relations are:

$$\begin{cases} V_{L1} + V_{L2} = V_{in} - V_{C2} - V_{C3} - I_{L1}(R_{L1} + R_{L1}) \\ V_{C3} = \frac{V_0}{3} \end{cases}$$

(54)

If  $R_{L1} = R_{L1} = R_L$  Then  $V_{L1} = V_{L2}$

Therefore,  $R_{L1} = R_{L1} = L_{L1}$

MODE I: The inductor voltages are

$$V_{L1} = V_{L2} = V_{in} - I_L R_L \tag{55}$$

MODE II: The inductor voltages are

$$V_{L1} = V_{L2} = V_{in} - I_L R_L - \frac{V_O}{6}$$

(56)

Since the average value of the voltage inductor is zero in the switching time interval.

$$D(V_{in} - I_L R_L) + (1 - D)(V_{in} - I_L R_L - \frac{V_0}{6})$$

(57)

The ratio of output voltage to the input voltage is derived using (57)

$$\frac{V_o}{V_{in}} = \frac{6\left(1 - \frac{I_L R_L}{V_{in}}\right)}{(1-D)} = \frac{6\left(1 - \frac{V_{LD}}{V_{in}}\right)}{(1-D)}$$

(58)

Where  $I_L R_L = V_{LD}$  is the drop across  $R_L$ Using the value of  $I_L$  from expression (21)

$$\frac{\frac{V_o}{V_{in}} = \frac{6\left(1 - \frac{\frac{3V_o R_L}{(1 - D) R}}{V_{in}}\right)}{(1 - D)}}{\frac{V_o}{V_{in}} = \frac{6}{(1 - D)\left[1 + \frac{18}{(1 - D)^2 R}\right]}}$$

(59)

(60)

The effect of non-idealities on voltage gain is given by (58) and (60) in the CCM mode of operation of the converter and the plot of both the expression is presented in Figure 12 and Figure 13.

#### EFFECT OF NON-IDEAL SWITCH ON VOLTAGE GAIN

The voltages across the inductors in both modes can be found as:

$$\begin{cases} V_{L1} = V_{in} - I_{SW} R_{SW} \\ V_{L2} = V_{in} - I_{SW} R_{SW} \end{cases}$$

(61)

$$V_{L1} = V_{L2} = \frac{V_{in} - V_{C2} - V_{C3}}{2} \tag{62}$$

$$V_{C2} = -V_{in} + I_{SW}R_{SW} \tag{63}$$

Multidisciplinary : Rapid Review : Open Access Journal

Since the average value of voltage across the inductor is zero. Therefore, the expression can be derived as follows

$$D(V_{in} - I_{SW}R_{SW}) + (1 - D)(\frac{V_{in} - V_{C2} - V_{C3}}{2})$$

(64)

$$D(V_{in} - I_{SW}R_{SW}) + (1 - D)(\frac{2V_{in} - I_{SW}R_{SW} - \frac{1}{3}}{2})$$

(65)

The ratio of output voltage to the input voltage is derived using (65)

$$\frac{v_o}{v_{in}} = \frac{6\left(1 - \frac{I_S R_{SW}(1+D)}{2V_{in}}\right)}{(1-D)} = \frac{6\left(1 - \frac{V_{SD}(1+D)}{2V_{in}}\right)}{(1-D)}$$

(66)

Where  $I_S R_{SW} = V_{SD}$  is the voltage drop across the switch. Using the value of  $I_{SW}$  from expression (22)

$$\frac{V_{O}}{V_{in}} = \frac{6 \left(1 - \frac{(5+D)(1+D)V_{O}R_{SW}}{2(1-D) R}\right)}{V_{in}}$$

(67)

$$\frac{V_O}{V_{in}} = \frac{6}{(1-D)\left[1 + \frac{3(5+D)(1+D)R_{SW}}{(1-D)^2 R}\right]}$$

(68)

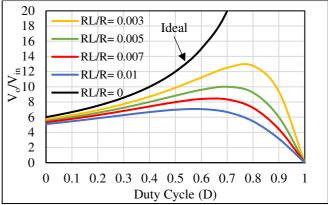

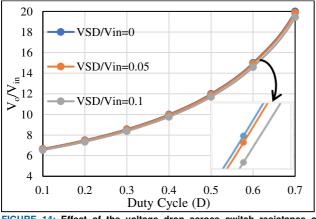

The effect on voltage gain is given by (66) and (68) and the plot of both the expressions are shown in Figure 14 and 15a respectively. From Figure 15a it can be inferred that the gain rapidly decreases with an increase in the parasitic resistance of the switch, especially at higher duty ratios.

FIGURE 14: Effect of the voltage drop across switch resistance on voltage gain

FIGURE 15(a): Variation of voltage gain when the ON-state resistance of the switch is increased.

EFFECT OF NON-IDEAL DIODES ON VOLTAGE GAIN

The effect of non-ideal diodes  $(D_1-D_7)$  having parasitic resistance  $(R_D)$  and forward cut in voltage  $(V_{CN})$  on voltage gain is analysed and other elements are assumed ideal. **MODE I:** The inductor voltage relations are:

$$\begin{cases} V_{L1} = V_{in} - I_L R_D - V_{CN} \\ V_{L2} = V_{in} - I_L R_D - V_{CN} \end{cases}$$

(69)

The inductor voltage relations are:

**MODE II:** The inductor voltage relations are:

$$V_{L1} = V_{L2} = \frac{V_{in} - V_{C2} - V_{C3} - V_{CN} - \frac{I_0 R_D}{(1-D)}}{2}$$

(70)

$$V_{C2} = -V_{in} + \frac{2I_L R_D}{D} + 2V_{CN}$$

(71)

$$V_{C3} = \frac{V_O}{3} \tag{72}$$

Since the average value of voltage across the inductor is null. Therefore, the expression can be derived as follows

$$D(V_{in} - I_L R_D - V_{CN}) + (1 - D) \left(\frac{V_{in} - V_{C2} - V_{C3} - V_{CN} - \frac{I_O K_D}{(1 - D)}}{2}\right)$$

(73)

The effect on voltage gain is given by (74)

$$\frac{V_O}{V_{in}} = \frac{6(1 - \frac{V_C N}{V_{in}})}{(1 - D)\left[1 + \frac{(6 + D - D^2)R_D}{D(1 - D)^2 R}\right]}$$

(74)

### EFFECT OF ESR OF CAPACITORS ON VOLTAGE GAIN

The ON and OFF state current through the capacitors is found using (3) and (7).

The effect of ESR of capacitors ( $C_1$  to  $C_5$ ) on voltage gain is analysed and other elements are assumed ideal.

The voltage across inductor  $L_1$  and  $L_2$  in both modes can be found as:

MODE I: The useful voltage relations are:

$$V_{L2} = V_{L2} = V_{in} (75)$$

$$V_{C2} = -V_{in} + \frac{3I_0 R_{C2}}{D}$$

(76)

$$V_{C4} + V_{C5} = V_O - \frac{I_O R_{C4}}{D} + \frac{I_O R_{C5}}{D}$$

(77)

$$V_{C1} + V_{C3} + V_{C5} = V_0 - V_{in} + \frac{2I_0}{D} (R_{C1} + R_{C3} + R_{C5})$$

(78)

MODE II: The useful voltage relations are:

$$V_{L1} = V_{L2} = \frac{V_{in} - V_{C2} - V_{C3} - \frac{3I_0 R_{C2}}{(1-D)} - \frac{2I_0 R_{C3}}{(1-D)}}{2}$$

(79)

$$V_{C4} - V_{C5} = V_{C3} + \frac{2I_0 R_{C3}}{(1-D)} + \frac{I_0 R_{C4}}{(1-D)} + \frac{I_0 R_{C5}}{(1-D)}$$

(80)

$$V_{C3} - V_{C1} = V_{in} + \frac{2I_o(R_{C1} - R_{C3})}{(1 - D)}$$

(81)

Since the average value of voltage across the inductor is zero. Therefore, the expression can be derived as follows

$$D(V_{in}) + (1-D)(\frac{V_{in} - V_{C2} - V_{C3} - \frac{S_{10}K_{C2}}{(1-D)} - \frac{2I_{0}K_{C3}}{(1-D)}}{2})$$

(82)

$$\frac{2V_{in}}{(1-D)} = V_{C2} + V_{C3} + \frac{310K_{C2}}{(1-D)} + \frac{210K_{C3}}{(1-D)}$$

(83)

Using (76) in (83)

$$\frac{2V_{in}}{(1-D)} = V_{C3} + \frac{3I_0R_{C2}}{D(1-D)} + \frac{2I_0R_{C3}}{(1-D)}$$

(84)

$V_{C1}$ ,  $V_{C3}$ ,  $V_{C5}$  are obtained using (76),(77) and (78) and putting these relations in (79) the effect of ESR values of capacitors on voltage gain is obtained as

Multidisciplinary : Rapid Review : Open Access Journal

$$\frac{V_O}{V_{in}} = \frac{6}{(1-D)} - \frac{1}{D(1-D)} \left( \frac{4I_O R_{C1} + 9I_O R_{C2} + 4I_O R_{C3} + I_O R_{C4} + (3-2D)I_O R_{C5}}{V_{in}} \right)$$

(85)

For simplicity, it is assumed that

$$R_{C1} = R_{C2} = R_{C3} = R_{C4} = R_{C5} = R_C$$

$$\frac{V_O}{V_{in}} = \frac{6}{(1-D)} - \frac{(21-2D)I_OR_C}{D(1-D)V_{in}}$$

$$\frac{V_O}{V_{in}} = \frac{6}{(1-D)\left[1 + \frac{(21-2D)R_C}{D(1-D)R_I}\right]}$$

(86)

(87)

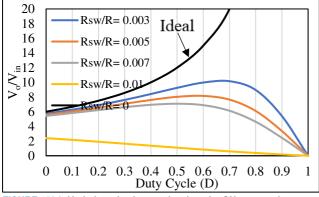

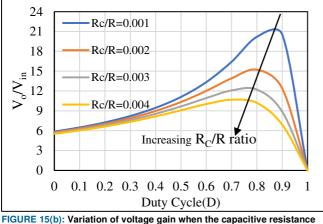

Figure 15(b) shows the variation in gain when the capacitor resistance is increased. The gain decreases especially at higher duty ratios and low value of load resistance.

FIGURE 15(b): Variation of voltage gain when the capacitive resistance is increased.

### COMBINED EFFECT OF NON-IDEALITIES ON VOLTAGE GAIN

The combined effect of all parasitic elements on voltage gain can be found by considering all the non-idealities of components of the proposed converter.

The deviation from voltage gain can be obtained as follows  $V_O = 6$   $18I_OR_L = 3(5+D)(1+D)I_OR_{SW}$

$$\frac{1}{V_{in}} = \frac{1}{(1-D)} - \frac{1}{V_{in}} - \frac{2V_{in}}{2V_{in}} - \frac{1}{2V_{in}} - \frac{1}{2V_{in}} - \frac{1}{D(1-D)^2 V_{in}} - \frac{1}{D(1-D)V_{in}} - \frac{1}{D(1-D)V_{in}} - \frac{1}{D(1-D)V_{in}}$$

(89)

Where  $I_0 = \frac{v_0}{R}$  is output load current.

The combined effect of non-idealities on the voltage gain can be derived as

$$\frac{V_O}{V_{in}} = \frac{6(1 - V_{CN}/V_{in})}{(1 - D)\left[1 + a\frac{R_L}{R} + b\frac{R_{SW}}{R} + c\frac{R_D}{R} + d\frac{R_C}{R}\right]}$$

(90)

Where,

$$\begin{cases} a = \frac{18}{(1-D)^2}, b = \frac{3(5+D)(1+D)}{(1-D)^2} \\ c = \frac{(6+D-D^2)}{D(1-D)^2}, d = \frac{(21-2D)}{D(1-D)} \end{cases}$$

B. POWER LOSS ANALYSIS OF THE PROPOSED CONVERTER

LOSSES IN PROPOSED CONVERTER DUE TO SWITCH The practical power switch has conduction and switching losses. The conduction loss in the switch during the ON state by the parasitic resistance  $R_{SW}$ .

$$P_{Sw_{cond}} = I_{SW_{rms}}^{2} \times R_{SW}$$

(91)

Where  $I_{SW_{rms}}$  is root mean square value of switch current and it is equal to

$$I_{SWrms} = \frac{5+D}{\sqrt{D(1-D)}} I_o \tag{92}$$

$$P_{Sw_{cond}} = \frac{(5+D)^2}{D(1-D)^2} I_o^2 R_{SW}$$

(93)

$$P_{Sw_{cond}} = \frac{(5+D)^2}{D(1-D)^2} \frac{R_{SW}}{R} P_0$$

(94)

Where  $P_0$  is the output power of the resistive load. The switching loss ( $P_{Sw_{switching}}$ ) of the power switch can be calculated with the approximate relation shown in (95).

$$P_{Sw_{switching}} = \frac{(t_r + t_f)(I_{SWavg}V_{Sw}) * f_s}{2}$$

(95)

Where,  $t_r$ = total rise time of the switch,  $t_f$ = total fall time,  $f_s$ = switching frequency.

$$V_{S} = \frac{V_{o}}{3}, I_{SWavg} = \frac{5+D}{1-D}I_{o}$$

(96)

$$P_{Sw_{switching}} = \frac{(t_r + t_f)(5 + D)V_o^2 f_s}{3R(1 - D)}$$

(97)

Total loss in the switch  $(P_{SW_{loss_{total}}})$  is the sum of conduction and switching loss and can be expressed as

$$P_{SW_{loss_{total}}} = P_{Sw_{cond}} + P_{Sw_{switching}}$$

(98)

$$P_{SW_{loss_{total}}} = \left(\frac{(5+D)^2}{D(1-D)^2} \frac{R_{SW}}{R} + \frac{(t_r + t_f)(5+D)f_s}{3(1-D)}\right) P_o$$

(99)

$$P_{SW_{loss_{total}}} = 3.2W$$

## LOSSES IN PROPOSED CONVERTER DUE TO SEVEN DIODES (D1-D7)

As compared to conduction loss the switching loss in the diode is neglected and only conduction losses are taken into consideration. It is assumed that all diodes have equal resistance  $R_{DS}$  and equal cut in voltage  $V_{CN}$ .

The conduction loss due to parasitic resistance  $(P_{D_r})$  is calculated using

$$P_{D_r} = I_{D_{rms}}^2 R_{DS} \tag{100}$$

The conduction loss  $(P_{D_{CN}})$  due to cut in voltage in forward biased is calculated using

$$P_{D_{CN}} = V_{CN} I_{D_{dc}} \tag{101}$$

Total conduction loss in the diode  $(P_{D_{loss}})$  is the sum of both losses

$$P_{D_{loss}} = P_{D_r} + P_{D_{CN}} = I_{D_{rms}}^2 R_{DS} + V_{CN} I_{D_{dc}}$$

(102)

Total conduction losses due to in the proposed converter is

the sum of all losses in the diodes

$$P_{D_{loss}total} = \sum_{i=1}^{7} P_{Di,loss} = \sum_{i=1}^{7} (I_{Di_{rms}}^{2} R_{DS} + V_{CN} I_{Di_{dc}})$$

(103)

The root mean square value of current through the diodes is expressed as below

$$I_{D1_{rms}} = I_{D4_{rms}} = I_{D6_{rms}} = \frac{I_o}{\sqrt{(1-D)}}$$

(104)

$$I_{D2_{rms}} = I_{D3_{rms}} = \frac{3I_0}{(1-D)\sqrt{D}}$$

(105)

$$I_{D5_{rms}} = I_{D7_{rms}} = \frac{I_o}{\sqrt{D}} \tag{106}$$

$$\begin{cases}

P_{D1,loss} = \frac{IO}{(1-D)}R_{DS} + V_{CN}I_{O} = \left(\frac{1}{(1-D)}\frac{R_{DS}}{R} + \frac{V_{CN}}{V_{O}}\right)P_{O} \\

P_{D2,loss} = \frac{9IO^{2}}{D(1-D)^{2}}R_{DS} + V_{CN}I_{O} = \left(\frac{9}{D(1-D)^{2}}\frac{R_{DS}}{R} + \frac{V_{CN}}{V_{O}}\right)P_{O} \\

P_{D3,loss} = P_{D2,loss} \\

P_{D4,loss} = P_{D6,loss} = P_{D1,loss} \\

P_{D5,loss} = P_{D7,loss} = \frac{IO^{2}}{D}R_{DS} + V_{CN}I_{O} = \left(\frac{1}{D}\frac{R_{DS}}{R} + \frac{V_{CN}}{V_{O}}\right)P_{O} \\

(107) \\

\begin{cases}

P_{D1,loss} = \sum_{i=1}^{7}P_{Di,loss} = \left(\frac{(20-D-D^{2})}{D(1-D)^{2}}\frac{R_{DS}}{R} + \frac{7V_{CN}}{V_{O}}\right)P_{O}

\end{cases}$$

## LOSSES IN PROPOSED CONVERTER DUE TO TWO INDUCTORS ( $L_1$ and $L_2$ )

The total conduction losses in the two inductors are

$$P_{L_{loss_{total}}} = I_{L1rms}^{2} r_{L1} + I_{L2rms}^{2} r_{L2}$$

(109)

Using equation (21) to find the value of root mean square (rms) value of inductor currents.

$$P_{L_{losstotal}} = \frac{9I_0^2}{(1-D)^2} (r_{L1} + r_{L2})$$

(110)

or it can be equivalently written as

$$P_{L_{loss_{total}}} = \frac{9}{(1-D)^2} \left(\frac{r_{L1}}{R} + \frac{r_{L2}}{R}\right) P_0 \tag{111}$$

It is assumed that the ESR value of both the inductors are equal  $(r_{L1} = r_{L2} = r_L)$  then total loss in the inductor can be expressed as

$$\begin{cases} P_{L_{loss_{total}}} = \frac{18}{(1-D)^2} \left(\frac{r_L}{R}\right) P_O \\ P_{SW_{loss_{total}}} = 5.8W \end{cases}$$

(112)

#### LOSSES IN PROPOSED CONVERTER DUE TO SIX CAPACITORS ( $C_0$ - $C_5$ )

The power loss in the capacitors due to series resistance is

$$P_{C_{loss}} = I_{C_{rms}}^{2} \times R_{C} \tag{113}$$

The total losses in the proposed converter are the sum of losses due to all the capacitors i.e.

$$P_{C_{loss_{total}}} = \sum_{i=0}^{5} P_{Ci_{loss}} = \sum_{i=0}^{5} (I_{Ci_{rms}}^2 \times R_{Ci}) \quad (114)$$

The rms value of current through capacitors can be calculated using the formula

$$I_{C_{rms}} = \sqrt{\frac{1}{T_S} \left( \int_0^{DT_S} I_{C_{ON}}^2 dt + \int_{DT_S}^{T_S} I_{C_{OFF}}^2 dt \right)}$$

(115)

The values of rms currents through capacitors can be earned using (3), (7) and (115)

$$\begin{cases} I_{C1_{rms}} = \frac{2I_O}{\sqrt{D(1-D)}}, P_{C1_{loss}} = \frac{4I_O^2 R_{C1}}{D(1-D)} = \frac{4}{D(1-D)} \frac{R_{C1}}{R} P_O \\ I_{C2_{rms}} = \frac{3I_O}{\sqrt{D(1-D)}}, P_{C2_{loss}} = \frac{9I_O^2 R_{C2}}{D(1-D)} = \frac{9}{D(1-D)} \frac{R_{C2}}{R} P_O \\ I_{C3_{rms}} = \frac{3I_O}{\sqrt{D(1-D)}}, P_{C3_{loss}} = \frac{9I_O^2 R_{C3}}{D(1-D)} = \frac{9}{D(1-D)} \frac{R_{C3}}{R} P_O \\ I_{C4_{rms}} = \frac{I_O}{\sqrt{D(1-D)}}, P_{C4_{loss}} = \frac{I_O^2 R_{C4}}{D(1-D)} = \frac{1}{D(1-D)} \frac{R_{C4}}{R} P_O \\ I_{C5_{rms}} = \frac{I_O}{\sqrt{D(1-D)}}, P_{C5_{loss}} = \frac{I_O^2 R_{C5}}{D(1-D)} = \frac{1}{D(1-D)} \frac{R_{C5}}{R} P_O \\ I_{C0_{rms}} = \sqrt{\frac{1-D}{D}} I_O, P_{C0_{loss}} = \frac{(1-D)I_O^2 R_{C0}}{D} = \frac{1-D}{D} \frac{R_{C0}}{R} P_O \end{cases}$$

(116)

Summation of all individual losses occurring in capacitor gives total losses occurring due to capacitors in the proposed converter

$$P_{C_{loss}_{total}} = P_{C1_{loss}} + P_{C2_{loss}} + P_{C3_{loss}} + P_{C4_{loss}} + P_{C5_{loss}}$$

(117)

If it is assumed that

$R_{C1} = R_{C2} = R_{C3} = R_{C4} = R_{C5} = R_{C0} = R_C$

Then

$$\begin{pmatrix}

P_{C_{loss_{total}}} = \frac{(D^2 - 2D + 25)}{D(1 - D)} \frac{R_C}{R} P_O \\

P_{C_{loss_{total}}} = 2.52W

\end{cases}$$

(118)

Hence total in the proposed converter is the sum of all the losses occurring in the proposed converter that is expressed below.

$$P_{loss_{total}} = \left(\frac{f_s c_s R}{9} + a \frac{R_{SW}}{R} + b \frac{R_{DS}}{R} + c \frac{r_L}{R} + d \frac{R_C}{R} + \frac{7V_{CN}}{V_o}\right) P_o$$

(120)

Where

$$\begin{cases} a = \frac{(5+D)^2}{D(1-D)^2} , b = \frac{(20-D-D^2)}{D(1-D)^2} \\ c = \frac{18}{(1-D)^2}, d = \frac{(D^2-2D+25)}{D(1-D)} \end{cases}$$

The efficiency  $(\eta)$  of the proposed converter can be expressed as below

$$\eta = \frac{P_0}{P_0 + P_{loss_{total}}} \tag{121}$$

$$\eta = \frac{1}{1 + \frac{f_S C_S R}{9} + a \frac{R_{SW}}{R} + b \frac{R_{DS}}{R} + c \frac{r_L}{R} + d \frac{R_C}{R} + \frac{T V_{CN}}{V_0}}$$

(122)

## VI. PERFORMANCE ANALYSIS WITH SIMILAR CONVERTERS

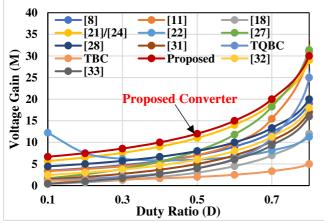

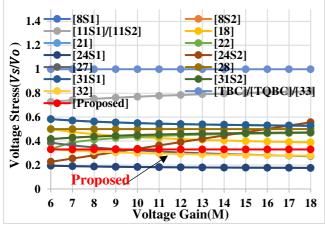

A detailed comparative analysis has been carried out and two traditional topologies and a few very recent high gain converter topologies have been considered. The analysis is based on the number of components, voltage gain and voltage stress across switches as given in Table 1. When compared to conventional boost and conventional quadratic boost converter the proposed topology can obtain a higher gain and the switch stress is considerably low. The converter in [8], adopts two switches and four inductors but its voltage gain is found to be lower than the proposed converter. The converter in [11] also has a lower voltage gain and higher

switch stress than the proposed topology. The converter in [18] uses a total of four inductors which makes the converter bulky and the voltage gains are also low. Converters in [21], [22] and [28] have a relatively lower component count but the voltage gains are substantially less. The converter in [24], has a total of three switches (which could make the control of the converter complicated) but the voltage gains are less and switch stress is found to be higher. In [27] the topology has employed five inductors, two switches and a total of 18 components, and the increased count of components results in increased size of the converter and inefficiency and its voltage gain is quite low as compared to the proposed topology. Voltage gains of the converter proposed in [31] are also considerably less than the proposed converter. The converter in [32] has a total component count of 16 equal to the proposed converter including 3 inductors and 7 capacitors, but the voltage gains are considerably less than the proposed topology. Converter in [4] has adopted a total of 4 switches in its proposed circuit which can make the converter control very complex as compared to a single switch in the topology in this literature and even then, the voltage gains are lower.

FIGURE 16: Voltage gain curve at different duty cycle for comparison

FIGURE 17: Switch voltage stress curve at different duty cycle for comparison

For comparison, a plot of the voltage gain(M) versus the duty ratio(D) for the proposed topology and other similar converters is shown in Figure 16. It can be observed that the proposed topology gives the highest voltage gain even at low values of the duty ratio(D). A gain of almost ten times can be achieved at a duty of 0.4. High gain at a lower duty ratio reduces the current stress of the converter. The voltage gain of converters in [27], [11] is slightly higher than the proposed topology when it is operated at duty ratio values close to D=0.8 but the switch stress is also high at these extreme values of the duty ratio. The plot of voltage stress vs the voltage gain is shown in Figure 17. It can be inferred from this plot that the proposed converter has one of the lowest voltage stresses across the switch.

Based on the comparison results the proposed converter topology is more advantageous as it can achieve high voltage gain, low voltage stress and is controlled by a single switch.

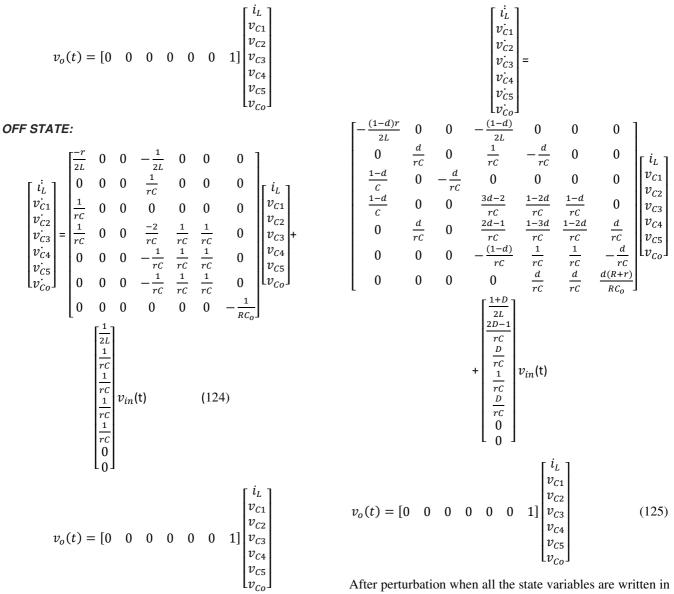

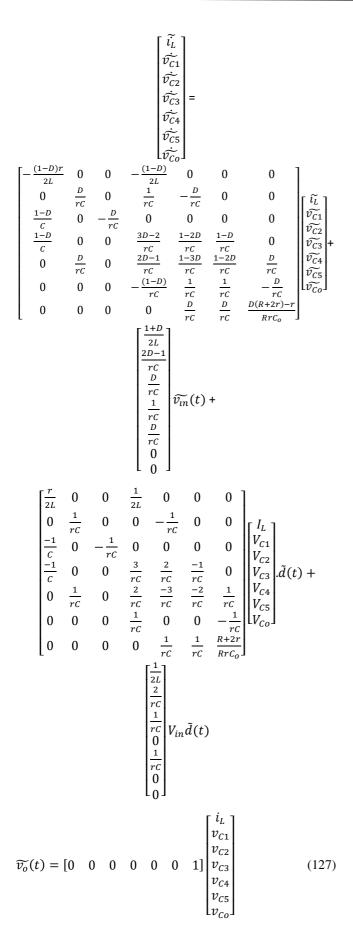

## VII. STATE SPACE MODEL OF THE PROPOSED CONVERTER

To derive the small signal state space model small resistances with capacitors  $C_1$ ,  $C_2$  and  $C_5$  are considered. These resistances are used to simplify the analysis and to eliminate the invalid variables from the state space representation. Assuming the same value of inductors, the inductor current is represented by a single state variable. All the capacitors except the output capacitor have same value. The dynamic equations in ON and OFF state can be represented as shown in equation (123) and equation (124).

ON STATE:

$$\begin{bmatrix} \dot{i}_{L} \\ \dot{v}_{C1} \\ \dot{v}_{C2} \\ \dot{v}_{C3} \\ \dot{v}_{C4} \\ \dot{v}_{C5} \\ \dot{v}_{C0} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 1 & \frac{1}{rc} & -\frac{1}{rc} & 0 & 0 \\ 0 & \frac{1}{rc} & 0 & \frac{1}{rc} & -\frac{1}{rc} & 0 & 0 \\ 0 & \frac{1}{rc} & 0 & \frac{1}{rc} & -\frac{2}{rc} & -\frac{1}{rc} & -\frac{1}{rc} \\ 0 & 0 & 0 & 0 & \frac{1}{rc} & \frac{1}{rc} & -\frac{1}{rc} \\ 0 & 0 & 0 & 0 & \frac{1}{rc} & \frac{1}{rc} & -\frac{1}{rc} \\ 0 & 0 & 0 & 0 & \frac{1}{rc} & \frac{1}{rc} & \frac{r+R}{c_0 rR} \end{bmatrix} \begin{bmatrix} \dot{i}_{L} \\ v_{C1} \\ v_{C2} \\ v_{C3} \\ v_{C4} \\ v_{C5} \\ v_{C0} \end{bmatrix} + \begin{bmatrix} \dot{i}_{L} \\ v_{C1} \\ v_{C1} \\ v_{C2} \\ v_{C3} \\ v_{C4} \\ v_{C5} \\ v_{C6} \end{bmatrix}$$

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3110668, IEEE Access

The converter operates in ON mode with a time d(t) and in OFF mode with a time (1-d(t)). The averaged model by combining (123) and (124) can be obtained and written as shown in (125).

After perturbation when all the state variables are written in terms of dc signal and small signals as shown in (126) the small signal model of the proposed converter neglecting the dc terms can be obtained as shown in (127).

$$\begin{aligned} i_{L} &= I_{L} + \tilde{i}_{L} \\ v_{C1} &= V_{C1} + \tilde{v}_{C1} \\ v_{C2} &= V_{C2} + \tilde{v}_{C2} \\ v_{C3} &= V_{C3} + \tilde{v}_{C3} \\ v_{C4} &= V_{C4} + \tilde{v}_{C4} \\ v_{C5} &= V_{C5} + \tilde{v}_{C5} \\ v_{Co} &= V_{Co} + \tilde{v}_{Co} \end{aligned}$$

(126)

**IEEE**Access

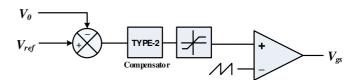

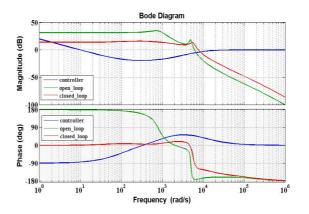

The open loop dynamic response of  $\frac{\widehat{v}_0(s)}{d(s)}$  obtained through PLECS software, plotted in MATLAB for the same values as shown in Table 2. is depicted in Figure 18. From the bode plot of uncompensated system it can be observed that the phase margin at the gain crossover frequency is only 10° which is not desirable. For closed loop stability of the system, the desirable phase margin should be between 45° to 65° to achieve good step response of the system.

## VOLTAGE CONTROLLER DESIGN USING PLECS SOFTWARE

Using PLECS software the uncompensated bode plot can be observed and a proper controller can be designed. A PI controller usually works well for the lower order system. From the uncompensated bode plot it can be observed that the system is stable but it has zeroes in right half plane. To achieve proper phase margin a compensator is designed to remove the steady state error and remove the disturbances at high frequencies, for which the poles are added up at 0 rad/s and 10000 rad/s respectively. Zeroes are added at frequencies of 100rad/s and 1000 rad/s to achieve the desired phase margin. The compensator transfer function is given by (128)

$$G_{c}(s) = \frac{K(s+1/\omega_{z1})(s+1/\omega_{z2})}{s(s+1/\omega_{P1})}$$

$$G_c(s) = \frac{10(s+1/100)(s+1/1000)}{s(s+1/1000)}$$

(128)

From the Figure 18 of the compensated closed loop plot it can be observed that phase margin of closed loop system is  $63^{\circ}$  at the gain crossover frequency which shows that the closed loop system is stable.

FIGURE 18(a) Voltage control Loop

IEEE Access

FIGURE 18(b) Bode plots of open loop, closed loop and compensator.

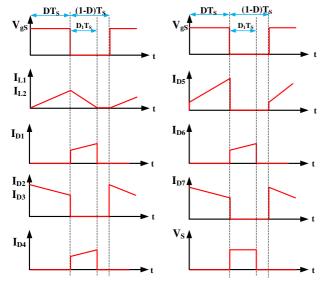

## VII. LABORATORY PERFORMANCE OF THE PROPOSED CONVERTER

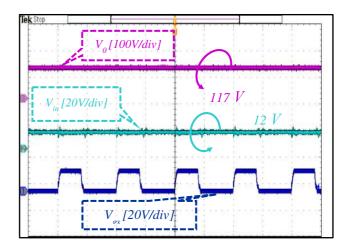

The performance of the proposed converter is determined by building the hardware prototype as shown in Figure 19(a) in the laboratory. The converter is operated at a duty ratio of 40% and 30% in continuous conduction mode at a switching frequency of 50kHz. The design specifications of the presented converter are listed in Table 2 and the experimental set-up is shown in Figure 19(b).

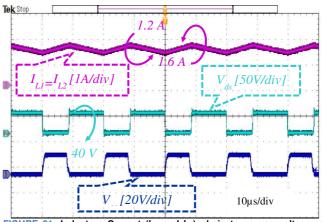

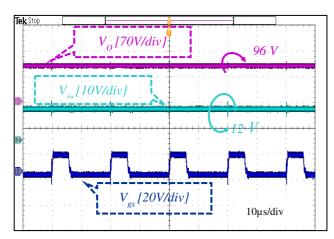

As depicted in Figure 20 measured input and output voltage are 12V and 117V respectively. The output voltage is reduced due to the effect of the parasitic resistance of the diodes, switch, capacitors and inductors. In the same Figure, the ripple observed in the output capacitor ( $C_o$ ) is two per cent (2%) of  $V_o$  that is about 2.24V. The drain to source voltage of the power MOSFET (S) is presented in Figure 20 with respective gate to source signals ( $V_{gs}$ ). The maximum value is found to be 40V which is approximately 34% of the output voltage ( $V_o$ ). When the power switch is triggered using the respective gate signal both the inductor  $L_1$  and  $L_2$  magnetize from 1.2A to 1.6A.

FIGURE 19(a) Hardware Prototype of the proposed converter

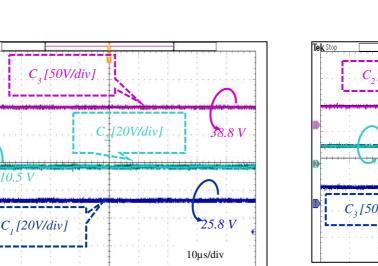

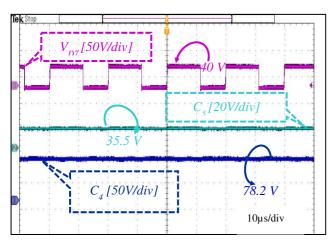

The inductor current peak to peak ripple is about 0.2A (15%) which is near to the value used to design the inductors and when the MOSFET is turned OFF the inductor demagnetize with the effect to reduce current linearly. The average value of both the inductor current is found to be 1.36A. The inductor currents are found to be continuous. Figure 22 and 23 shows the voltage across the capacitors C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>, C<sub>4</sub> and C<sub>5</sub> and is found to be 25.8V, 10.5V, 38.8V, 78.2 and 35.5V respectively with very low voltage ripple and is much less than the output voltage. The voltage across the output diode D<sub>7</sub> is shown and equal to 40V which is the same as the stress across the switch and less than the output voltage equal to 34%. All the results show that the converter is smoothly working in continuous conduction mode.

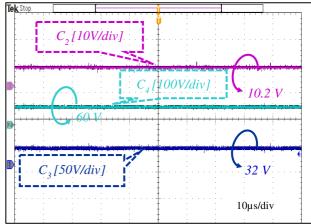

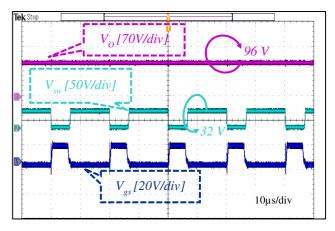

Additional results to verify the working are obtained at D=0.3 and V<sub>in</sub>= 12V. As depicted in Figure 24 for an input of 12 V the output voltage is found to 96 V. The drop in the voltage is due to parasitic and ON state resistances. As shown in Figure 25, the voltage across capacitors C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub> are found to be 10.2 V, 32 V and 60 V respectively. The capacitor voltages are constant with ripple in the voltage close to 2 V.

As can be seen from Figure 26, the voltage stress across the switch  $(V_{sw})$  is observed to be 32 V which is one-third of the  $V_{o}$ .

FIGURE 19(b) Experimental set-up

| Converters | Switch Count<br>(S <sub>C</sub> ) | Inductor<br>count (L <sub>C</sub> ) | Capacitor<br>count (C <sub>C</sub> ) | Diode count<br>(D <sub>C</sub> ) | $M\left(\frac{V_s}{V_{in}}\right)$ | M at<br>D=0.5 | Voltage Stress $\left(\frac{V_s}{V_o}\right)$                    |

|------------|-----------------------------------|-------------------------------------|--------------------------------------|----------------------------------|------------------------------------|---------------|------------------------------------------------------------------|

| TBC        | 1                                 | 1                                   | 1                                    | 1                                | $\frac{1}{(1-D)}$                  | 2             | 1                                                                |

| TQBC       | 1                                 | 2                                   | 2                                    | 3                                | $\frac{1}{(1-D)^2}$                | 4             | 1                                                                |

| [8]        | 2                                 | 4                                   | 3                                    | 7                                | $\frac{3+D}{(1-D)}$                | 7             | $S_1: \frac{2}{3+D}, S_2: \frac{1+D}{3+D}$                       |

| [11]       | 2                                 | 2                                   | 4                                    | 6                                | $\frac{3 - 3D + D^2}{(1 - D)^2}$   | 7             | $\frac{S_{1}:\frac{1}{3-3D+D^{2}},}{S_{2}:\frac{1}{3-3D+D^{2}}}$ |

| [18]       | 1                                 | 4                                   | 6                                    | 3                                | $\frac{3D}{(1-D)}$                 | 3             | $\frac{1}{3D}$                                                   |

| [21]       | 2                                 | 2                                   | 4                                    | 5                                | $\frac{5+D}{(1-D)}$                | 11            | $\frac{1}{5+D}$                                                  |

| [22]       | 2                                 | 2                                   | 2                                    | 4                                | $\frac{1+D}{D(1-D)}$               | 6             | $\frac{D}{1+D}$                                                  |

| [24]       | 3                                 | 4                                   | 2                                    | 5                                | $\frac{5+D}{(1-D)}$                | 11            | $S_1: \frac{1}{5+D}; S_2: \frac{1}{(1-D)(5+D)}$                  |

IEEE Access

| [27]     | 2 | 5 | 3 | 8 | $\frac{1+5D+2D^2}{(1-D)}$                 | 8  | $\frac{1+D}{1+FD+2D^2}$                       |

|----------|---|---|---|---|-------------------------------------------|----|-----------------------------------------------|

| [28]     | 2 | 2 | 4 | 4 | $\frac{(1-D)}{\frac{4}{(1-D)}}$           | 8  | $\frac{1+5D+2D^2}{\frac{1}{2}}$               |

| [31]     | 2 | 4 | 1 | 9 | $\frac{(1-D)}{1+3D}$ $\frac{1+3D}{(1-D)}$ | 5  | $S_1: \frac{1+D}{1+3D}, S_2: \frac{2D}{1+3D}$ |

| [32]     | 1 | 3 | 7 | 5 | $\frac{2+2D}{(1-D)}$ , n=2                | 6  | $\frac{1}{2+2D}$                              |

| [33]     | 4 | 2 | 4 | 7 | $\frac{4D}{(1-D)}$ , m=3                  | 4  | 1                                             |

| Proposed | 1 | 2 | 6 | 7 | $\frac{6}{(1-D)}$                         | 12 | $\frac{1}{3}$                                 |

Table 1 Comparision of SC-SL-DC with the similar type of converter

Table 2: Hardware Specifications of the converter

| Elements            | Specification                    |  |  |  |

|---------------------|----------------------------------|--|--|--|

| Maximum Power       | 200W                             |  |  |  |

| Input Voltage       | 12V/16V                          |  |  |  |

| Switching Frequency | 50kHz                            |  |  |  |

| Duty Ratio          | 40% and 30%                      |  |  |  |

| Load Resistance     | R=400-600 Ω                      |  |  |  |

| Inductors           | $L_1 = L_2 = 330 \mu H$          |  |  |  |

| Capacitors          | $C_2=100\mu F/63V, C_1=C_3=C_4=$ |  |  |  |

|                     | C <sub>5</sub> =47µF/200V &      |  |  |  |

|                     | C <sub>0</sub> =68µF/350V        |  |  |  |

| Power MOSFET        | SPW52N50C3                       |  |  |  |

| Diodes              | SF8L60USM                        |  |  |  |

| Gate Drivers IC     | TLP250H                          |  |  |  |

| Microcontroller     | STM32 Nucleo H743ZI2             |  |  |  |

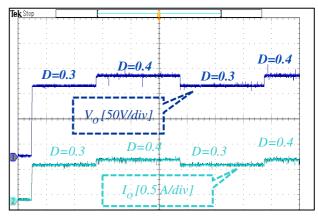

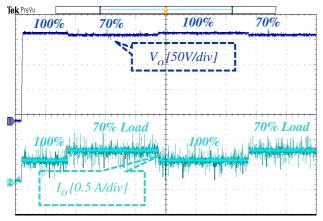

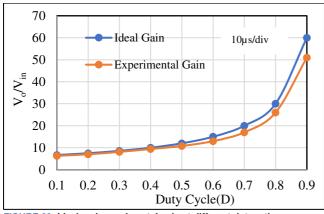

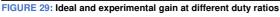

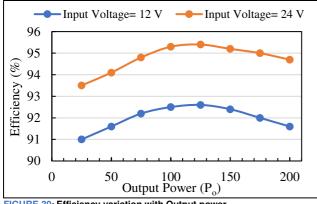

The converter performance is also tested in dynamic conditions when the duty cycle is changed from D=0.3 to D=0.4 at V<sub>in</sub>=16 V. From Figure 27, it can be seen that the output voltage varies from 132 V at D=0.3 to 150 V at D=0.4. From the experimental results, it can be concluded that the converter performance is satisfactory in both steadystate and dynamic conditions. Figure 28 shows the response of the converter when load is decreased to 70% at D=0.45 at Vin =15V. Also, the load current is increased as depicted in the same Figure. This shows that the regulation of the converter is good when load is changed. The output voltage is maintained between 160 V and 150V. Figure 29 shows the experimental voltage gain with the change in the duty cycle. For the same value of load resistance, the gain decreases at a higher duty cycle due to an increase in losses. The efficiency at different values of output power is shown in Figure 30. It can be seen from the plot that at constant output power as the voltage is increased from 12V to 24V the efficiency of the converter increases. This is because to achieve the same power output the current decreases with the increase in output voltage. As a result, the conduction losses decreases and efficiency increases. The power loss in different components in percentage is shown in Figure 31. The

maximum loss occurs in diodes as shown in Figure 32. The selection of devices with a low value of parasitic resistances increases the overall efficiency of the converter.

FIGURE 20: Output voltage (V<sub>0</sub>), Source Voltage (V<sub>in</sub>) and V<sub>gs</sub>

FIGURE 21: Inductors Current (IL1 and IL2), drain to source voltage of switch (Vs) and Vgs at D=0.4

FIGURE 22: Voltage across capacitors C1, C2 and C3 at D=0.4

FIGURE 23: Voltage across capacitors C4, C5 and output diode D7 at D=0.4

FIGURE 24: Output Voltage (Vo), Input Voltage (Vin) at D=0.3

FIGURE 25: Voltage across capacitors C2, C4 and C3 at D=0.3

FIGURE 26: Output Voltage and the voltage across switch at D=0.3

FIGURE 27: Output Voltage and the output current when D is changed from 0.3 to 0.4.

FIGURE 28: Effect of the change in loading at Vin=15 V and D=0.45

FIGURE 30: Efficiency variation with Output power

# CLOSED LOOP VALIDATION USING REAL TIME SIMULATOR, TYPHOON-HIL

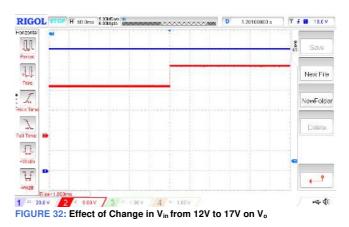

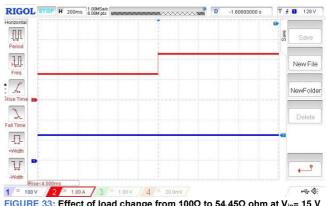

The performance of in closed loop operation is tested using hardware in loop (HIL) operation using Typhoon-HIL. The Typhoon-real time simulator is designed to check the performance of controller in real time. The results with change in input voltage and change in load are shown in Figure 32 and Figure 33. From Figure 32 it can be observed that as the input voltage is changed from 12 V to 17 V the output voltage is held constant at 120 V. Similarly, when load current is increased from 1.2 A to 2.2 A by decreasing the load resistance from 120  $\Omega$  to 55  $\Omega$  the output voltage is held constant by the voltage controller as shown in Figure 33. It can be concluded that the voltage controller is able to maintain the V<sub>0</sub> at reference value.

FIGURE 31: Distribution of losses among components

FIGURE 33: Effect of load change from  $100\Omega$  to  $54.45\Omega$  ohm at  $V_{in}\text{=}~15~V$  on  $V_o$

IEEE Access

#### **VIII. CONCLUSION**

In the proposed work, the converter (SC-SL-DC) has produced a voltage gain with a single switch and voltage multiplier cell made up of switched inductors. The voltage gain of the converter is found to be near 9.75 times at a duty ratio of 0.4 and 8 times at a duty of 0.3. which is high as compared with the quadratic boost converter and other high gain converters. The converter utilizes only two inductors which makes the converter light in weight. It is found that the high value of parasitic resistance of switch and inductors decreases the gain of the converter. Low voltage stress across capacitors leads to the selection of low voltage rating capacitors, which increases the efficiency and decreases the cost of the converter. The converter stress profile is also good as the stress across switch and diodes is one-third of the output voltage. The efficiency of the converter is found to improve if the input voltage is increased. The maximum efficiency is found to be 95.4%. The experimental results show that the converter is working in continuous current mode and the results match with the theoretical analysis. The proposed converter belongs to the non-isolated category and hence is suitable for medium power applications.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the support of Jouf University, Sakaka 72388, Saudi Arabia. This research serves the renewable energy research track, Sakaka independent power photovoltaic solar plant and Saudi Vision 2030 commitment to renewable energy.

The authors would like to acknowledge the financial support from Taif University Researchers Supporting Project Number (TURSP-2020/278), Taif University, Taif, Saudi Arabia.

The authors also acknowledge the support provided by the Hardware-In-the-Loop (HIL) Lab and Non-Conventional Energy (NCE) Lab, Department of Electrical Engineering, Aligarh Muslim University, India.

#### REFERENCES

- [1] F. Blaabjerg and D. M. Ionel, "Renewable Energy Devices and Systems – State-of-the-Art Technology, Research and Development, Challenges and Future Trends," Electric Power Components and Syst., vol. 43, no. 12, pp.1319-1328, 2015.

- [2] Forouzesh M, Siwakoti YP, Gorji SA, Blaabjerg F, Lehman B. Stepup DC–DC converters: a comprehensive review of voltage-boosting techniques, topologies, and applications. IEEE Trans Power Electron. 2017;32(12):9143-9178.

- [3] M. F. Guepfrih, G. Waltrich and T. B. Lazzarin, "High Step-Up Dc-Dc Converter Using Built-in Transformer Voltage Multiplier Cell and Dual Boost Concepts," in IEEE Journal of Emerging and Selected Topics in Power Electronics, doi: 10.1109/JESTPE.2021.3063060.

- [4] V. R. K. Kanamarlapudi, B. Wang, N. K. Kandasamy, and P. L. So, "A new ZVS full-bridge DC-DC converter for battery charging with reduced losses over full-load range," IEEE Trans. Ind. Appl., vol. 54, no. 1, pp. 571–579, Jan. 2018.

- [5] H. Jou, J. Huang, J. Wu, and K. Wu, "Novel isolated multilevel DC-DC power converter," IEEE Trans. Power Electron., vol. 31, no. 4, pp. 2690–2694, Apr. 2016.

- [6] G. Catona et al., "An isolated semiresonant DC/DC converter for high power applications," IEEE Trans. Ind. Appl., vol. 53, no. 3, pp. 2200– 2209, May 2017.

- [7] M. Forouzesh, K. Yari, A. Baghramian, and S. Hasanpour, "Singleswitch high step-up converter based on coupled inductor and switched capacitor techniques with quasi-resonant operation," IET Power Electron., vol. 10, no. 2, pp. 240–250, Oct. 2017.

- [8] S. Khan, A. Mahmood, M. Tariq, M. Zaid, I. Khan and S. Rahman, "Improved Dual Switch Non-Isolated High Gain Boost Converter for DC microgrid Application," 2021 IEEE Texas Power and Energy Conference (TPEC), 2021, pp. 1-6, doi: 10.1109/TPEC51183.2021.9384956.

- [9] Ahmad, J.; Zaid, M.; Sarwar, A.; Lin, C.-H.; Asim, M.; Yadav, R.K.; Tariq, M.; Satpathi, K.; Alamri, B. A New High-Gain DC-DC Converter with Continuous Input Current for DC Microgrid Applications. *Energies* 2021, 14, 2629. https://doi.org/10.3390/en14092629

- [10] Ahmad J, Lin C-H, Zaid M, Sarwar A, Ahmad S, Sharaf M, Zaindin M, Firdausi M. A New High Voltage Gain DC to DC Converter with Low Voltage Stress for Energy Storage System Application. *Electronics*. 2020; 9(12):2067. https://doi.org/10.3390/electronics9122067

- [11] A. Kumar et al., "Switched-LC Based High Gain Converter With Lower Component Count," in IEEE Transactions on Industry Applications, vol. 56, no. 3, pp. 2816-2827, May-June 2020, doi: 10.1109/TIA.2020.2980215.

- [12] Haji-Esmaeili, M.M., Babaei, E., & Sabahi, M. (2018). High Step-Up Quasi-Z Source DC–DC Converter. *IEEE Transactions on Power Electronics*, 33, 10563-10571.

- [13] P. Kumar and M. Veerachary, "Z-Network Plus Switched-Capacitor Boost DC–DC Converter," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 9, no. 1, pp. 791-803, Feb. 2021, doi: 10.1109/JESTPE.2019.2959078.

- [14] A. Chub, D. Vinnikov, E. Liivik and T. Jalakas, "Multiphase Quasi-Z-Source DC–DC Converters for Residential Distributed Generation Systems," in IEEE Transactions on Industrial Electronics, vol. 65, no. 10, pp. 8361-8371, Oct. 2018, doi: 10.1109/TIE.2018.2801860.

- [15] M. Meraj, M. S. Bhaskar, A. Iqbal, N. Al-Emadi and S. Rahman, "Interleaved Multilevel Boost Converter With Minimal Voltage Multiplier Components for High-Voltage Step-Up Applications," in IEEE Transactions on Power Electronics, vol. 35, no. 12, pp. 12816-12833, Dec. 2020, doi: 10.1109/TPEL.2020.2992602.

- [16] Abdel-Rahim O, Funato H, Haruna J. A comprehensive study of three high-gain DC-DC topologies based on Cockcroft-Walton voltage multiplier for reduced power PV applications. IEEJ Trans Electr Electron Eng. 2018;13(4):642-651

- [17] S. Hasanpour, M. Forouzesh, Y. Siwakoti and F. Blaabjerg, "A New High Gain, High-Efficiency SEPIC-Based DC-DC Converter for Renewable Energy Applications," in IEEE Journal of Emerging and Selected Topics in Industrial Electronics, doi: 10.1109/JESTIE.2021.3074864.

- [18] M. R. Banaei and S. G. Sani, "Analysis and Implementation of a New SEPIC-Based Single-Switch Buck–Boost DC–DC Converter With Continuous Input Current," in IEEE Transactions on Power Electronics, vol. 33, no. 12, pp. 10317-10325, Dec. 2018, doi: 10.1109/TPEL.2018.2799876.

- [19] Alizadeh Pahlavani, M.R. and Shokati Asl, E. (2020), DC–DC SIDO converter with low-voltage stress on switches: analysis of operating modes and design considerations. IET Power Electronics, 13: 233-247. https://doi.org/10.1049/iet-pel.2018.6184

- [20] Farhadi-Kangarlu, M, Khiavi, AM, Neyshabouri, Y. A non-isolated single-input dual-output boost DC–DC converter. IET Power Electron. 2021; 14: 936–945. https://doi.org/10.1049/pel2.12076

- [21] S. Khan, M. Zaid, A. Mahmood, J. Ahmad and A. Alam, "A Single Switch High Gain DC-DC converter with Reduced Voltage Stress," 2020 IEEE 7th Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON), 2020, pp. 1-6, doi: 10.1109/UPCON50219.2020.9376578.

- [22] Mohammadzadeh Shahir, F., Babaei, E. and Farsadi, M. (2018), Analysis and design of voltage-lift technique-based non-isolated boost dc-dc converter. IET Power Electronics, 11: 1083-1091. https://doi.org/10.1049/iet-pel.2017.0259

- [23] A. M. S. S. Andrade, T. Faistel, R. A. Guisso and A. Toebe, "Hybrid High Voltage Gain Transformerless DC-DC Converter," in IEEE

Transactions on Industrial Electronics, doi: 10.1109/TIE.2021.3066939.

- [24] Zaid, M, Khan, S, Siddique, MD, et al. A transformerless high gain dc-dc boost converter with reduced voltage stress. Int Trans Electr Energ Syst. 2021;e12877. https://doi.org/10.1002/2050-7038.12877

- [25] Syrigos, SP, Christidis, GC, Mouselinos, TP, Tatakis, EC. A nonisolated DC-DC converter with low voltage stress and high step-down voltage conversion ratio. IET Power Electron. 2021; 14: 1219–1235. https://doi.org/10.1049/pel2.12115

- [26] T. Shanthi, S. U. Prabha and K. Sundaramoorthy, "Non-isolated nstage High Step-up DC-DC Converter for Low voltage DC Source Integration," in IEEE Transactions on Energy Conversion, doi: 10.1109/TEC.2021.3050421.

- [27] M. S. Bhaskar et al., "A New Hybrid Zeta-Boost Converter With Active Quad Switched Inductor for High Voltage Gain," in IEEE Access, vol. 9, pp. 20022-20034, 2021, doi: 10.1109/ACCESS.2021.3054393.

- [28] S. Sadaf, N. Al-Emadi, P. K. Maroti and A. Iqbal, "A New High Gain Active Switched Network-Based Boost Converter for DC Microgrid Application," in IEEE Access, doi: 10.1109/ACCESS.2021.3077055.

- [29] J. Zhao and D. Chen, "Switched-Capacitor High Voltage Gain Z-Source Converter With Common Ground and Reduced Passive Component," in IEEE Access, vol. 9, pp. 21395-21407, 2021, doi: 10.1109/ACCESS.2021.3054880.

- [30] D. Bao, A. Kumar, X. Pan, X. Xiong, A. R. Beig and S. K. Singh, "Switched Inductor Double Switch High Gain DC-DC Converter for Renewable Applications," in IEEE Access, vol. 9, pp. 14259-14270, 2021, doi: 10.1109/ACCESS.2021.3051472.

- [31] N. Gupta *et al.*, "Novel Non-Isolated Quad-Switched Inductor Double-Switch Converter for DC Microgrid Application," 2020 IEEE International Conference on Environment and Electrical Engineering and 2020 IEEE Industrial and Commercial Power Systems Europe (EEEIC / I&CPS Europe), Madrid, Spain, 2020, pp. 1-6, doi: 10.1109/EEEIC/ICPSEurope49358.2020.9160839.

- [32] Babaei, E, Jalilzadeh, T, Sabahi, M, Maalandish, M, Alishah, RS. High step-up DC-DC converter with reduced voltage stress on devices. *Int Trans Electr Energ Syst.* 2019; 29:e2789. https://doi.org/10.1002/etep.2789

- [33] R. S. Alishah, M. Yahya Hassani, S. H. Hosseini, K. Bertilsson and M. Babalou, "Analysis and Design of a New Extendable SEPIC Converter with High Voltage Gain and Reduced Components for Photovoltaic Applications," 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), 2019, pp. 492-497, doi: 10.1109/PEDSTC.2019.8697249.

- [34] M. Babalou, M. Dezhbord, R. S. Alishah and S. Hossein Hosseini, "A Soft-Switched Ultra High Gain DC-DC Converter with Reduced Stress voltage on Semiconductors," 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), 2019, pp. 677-682, doi: 10.1109/PEDSTC.2019.8697533.

**SHAHRUKH KHAN** (Student Member, IEEE) is currently pursuing a B.Tech. degree with the Department of Electrical Engineering, Zakir Husain College of Engineering and Technology (ZHCET), Aligarh Muslim University (AMU), Aligarh, India. He has published and presented research papers on power electronic DC-DC converters in international conferences and reputed journals. His research interest includes the

design and control of power electronic converters, interleaved converters, and maximum power point techniques algorithms. He has won the Best Paper Award in one of his proceedings. He is also selected as a reviewer in various IEEE international conferences. He is the joint Secretary of IEEE Student Branch, AMU for the session 2020–2021

**MOHAMMAD ZAID** (Member, IEEE) received the degree and master's degree from the Zakir Husain College of Engineering and Technology (ZHCET), Aligarh Muslim University (AMU), Aligarh, India. He is currently working as an Assistant Professor with the Department of Electrical Engineering, ZHCET, AMU. He is also a Branch Counsellor of the IEEE Student Branch of the College. He has published research papers in the fields of DC/DC converters, multilevel inverters, and DG placement. The current

research interest includes developing new topologies of high gain DC/DC converters for renewable energy applications.

**ARSHAD MAHMOOD** is currently pursuing his Bachelor of Technology (B. Tech. Degree) in Electrical Engineering from Zakir Husain College of Engineering and Technology, Aligarh Muslim University, Aligarh, India. He has submitted and presented several papers on Power Electronics DC/DC Converters in various conference proceedings and journals. In one of

his proceeding, he has won the best paper award. His area of interest includes high gain dc to dc converter, solar PV systems, and maximum power point techniques.

**ABBAS SYED NOORUDDIN** (Student Member, IEEE) is currently pursuing Bachelors in Technology (B. Tech) with Department of Electrical Engineering, ZHCET, Aligarh Muslim University, Aligarh, India. He has worked on various research projects on High Gain DC-DC converters. His research interests include design and development of power converters, Solar Photovoltaic Systems, Blockchain applications

in Electric Vehicles and Smart Grids. He is an IEEE Student member since 2020 and has held various voluntary positions. He is currently serving as Secretary of IEEE Student Branch, AMU. He is also a member of the Student Activity Committee (SAC) of IEEE UP Section(R-10)

**JAVED AHMAD** received the B.Tech. degree in electrical engineering from Aligarh Muslim University, Aligarh, India, in 2017, and the ME in electrical power from Universiti Teknologi Malaysia, Johor Bharu, Malaysia, in 2019 and currently enrolled in the Ph.D program at National Taiwan University of Science and Technology (Taiwan Tech), Taipei, Taiwan. His research interests include managing hybrid

energy storage systems, DC to DC converters, interleaved converters, multilevel inverter, and power conversion for electric vehicle applications.

**MAMDOUH L. ALGHAYTHI** (Member, IEEE) received the B.S. degree in electrical engineering from Jouf University, Sakaka, Aljouf, Saudi Arabia, in 2012, the M.S. degree in Electrical Engineering from Southern Illinois University, Carbondale, IL, USA, in 2015, and the Ph.D. degree in electrical engineering from the University of Missouri, Columbia, USA, in 2020. He is currently an Assistant Professor with the Electrical Engineering Department, Jouf University,

Saudi Arabia. His current research interests include power electronics, renewable energy systems, high step-up dc-dc converters, microgrids and power converters. He is a Member of the IEEE Power Electronics

**BASEM ALAMRI** (Member, IEEE) received the B.Sc. degree (Hons.) in electrical engineering from the King Fahd University of Petroleum and Minerals (KFUPM), the M.Sc. degree (Hons.) in electrical power systems from King Abdulaziz University, Jeddah, Saudi Arabia, the M.Sc. degree in sustainable electrical power from Brunel University, London, U.K., in 2007 and 2008, respectively, and the Ph.D. degree in electrical power engineering