# A New Two-Dimensional Model for the Potential Distribution of Short Gate-Length MESFET's and its Applications

Shan-Ping Chin, Student Member, IEEE, and Ching-Yuan Wu, Member, IEEE

Abstract—A new analytical technique for calculating the twodimensional (2D) potential distribution of a MESFET device operated in the subthreshold region is proposed, in which the 2D Poisson's equation is solved by the Green's function technique. The potential and electric-field distributions of a nonself-aligned MESFET device are calculated exactly from different types of Green's function in different boundary regions, and the sidewall potential at the interface between these regions can be determined by the continuation of the electric field at the sidewall boundary. The remarkable feature of the proposed method is that the implanted doping profile in the active channel can be treated. Furthermore, a simplified technique is developed to derive a set of quasi-analytical models for the sidewall potential at both sides of the gate edge, the threshold voltage of short gate-length devices, and the drain-induced barrier lowering. Moreover, the developed quasi-analytical models are compared with the results of 2D numerical analysis and good agreements are obtained.

#### Nomenclature

| $\Psi(x, y)$   | Two-dimensional (2D) potential distribution.                                                  |

|----------------|-----------------------------------------------------------------------------------------------|

| _              |                                                                                               |

| $\epsilon$     | Dielectric permittivity of semiconductor.                                                     |

| q              | Elemental charge (=1.6 $\times$ 10 <sup>-19</sup> C).                                         |

| b              | Thickness of active layer.                                                                    |

| $V_{bi}$       | Built-in potential of a Schottky-barrier junc-                                                |

|                | tion.                                                                                         |

| $V_{gs}$       | Gate-source voltage.                                                                          |

| $V_{ds}$       | Drain-source voltage.                                                                         |

| $V_{ m th}$    | Threshold voltage.                                                                            |

| $k_n(k_m)$     | Eigenvalue of the Green's function in the ungate (gate) region.                               |

| $W_d(W_s)$     | Position of depletion layer edge at the drain (source) side of the gate.                      |

| $A_m^d(A_m^s)$ | Fourier coefficient for the excess sidewall potential at the drain (source) side of the gate. |

Manuscript received June 14, 1991; revised January 3, 1992. This work was supported continually for three years by the National Science Council, Taiwan, Republic of China, under Contracts NSC-78-0404-E009-26, NSC-79-0416-E009-01, and NSC-80-0416-E009-05. The review of this paper was arranged by Associate Editor M. D. Feuer.

The authors are with the Advanced Semiconductor Device Research Laboratory and the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, Republic of China.

IEEE Log Number 9201207.

$B_m$  Fourier coefficient for the one-dimensional (1D) potential distribution produced by the ionized impurity concentration.

$N_{d,n}^{s}(x)$  Fourier coefficient for the doping profile in the ungate region at the source side

$$\left(=\frac{c}{b}\int_0^b N_d(x, y)\cos(k_n y)\,dy,\right.$$

$$c = 1$$

for  $n = 0$  and  $c = 2$  for  $n \ge 1$ .

$N_{d,n}^d(x)$  Fourier coefficient for the doping profile in the ungate region at the drain side

$$\left(=\frac{c}{b}\int_0^b N_d(x, y)\cos(k_n y)\,dy,\right.$$

$$c = 1$$

for  $n = 0$  and  $c = 2$  for  $n \ge 1$ .

$N_{d,m}$  Fourier coefficient for the doping profile under the gate

$$\left(=\frac{2}{b}\int_0^b N_d(x, y) \sin(k_m y) dy\right).$$

$\rho(x', y')$  Charge density.

V<sub>1</sub> Average 1D potential due to depletion charge under the gate

$$\left(=\sum_{m=1}^{\infty}\frac{B_m}{(2m-1)\pi}\right).$$

$\overline{V}_s$  Average sidewall potential at the source end of the gate

$$\left(V_1 + \sum_{m=1}^{\infty} \frac{A_m^s}{(2m-1)\pi}\right).$$

$\overline{V}_d$  Average sidewall potential at the drain end of the gate

$$\left(V_1 + \sum_{m=1}^{\infty} \frac{A_m^d}{(2m-1)\pi}\right).$$

$L_g$  Gate length.

$T_{mn}$  Element of the transfer matrix

$$\left(=\frac{2}{b}\int_0^b \sin(k_m y)\cos(k_n y) dy\right).$$

0018-9383/92\$03.00 © 1992 IEEE

| $x_{\min}$          | Location of the minimum channel potential.                                                 |

|---------------------|--------------------------------------------------------------------------------------------|

| $\Psi_{min}$        | Minimum channel potential.                                                                 |

| $oldsymbol{\phi}_b$ | Channel barrier height (= $\Psi_{\min} - V_{gs} + V_{bi}$ ).                               |

| $\phi_b^c$          | Channel barrier height for defining the threshold voltage.                                 |

| $\phi(x)$           | Bottom potential with respect to the source potential (= $\Psi(x, b) - V_{gs} + V_{bi}$ ). |

| $V_{ m th}^0$       | Threshold voltage of a long-gate MESFET                                                    |

|                     | $(=V_{bi}-\Psi_{1d}(b)+\phi_b^c).$                                                         |

#### I. Introduction

THE GaAs MESFET's are widely used in high-speed logic circuit and microwave amplifier. The performance of a GaAs MESFET can be significantly enhanced by scaling down the device geometry. With the improvement on the process technology, a short gate-length MESFET device with sub-quarter-micrometer size can be fabricated. However, the gate-controlling capability will be reduced by the penetration of the electric field from the sidewall at both sides of the gate, and the threshold voltage of a short gate-length device will be influenced by the drain bias.

The short gate-length effect can be exactly analyzed by numerical simulation, based on a full set of semiconductor device equations with reasonable boundary conditions [1]–[3]. However, the numerical simulation is limited by the computation time and is difficult to use in circuit analysis. Furthermore, the results of numerical simulation can only provide discrete data points and are difficult to use in device optimization. The analytical model, which is generally limited by the mathematical treatment for different device structures, becomes very difficult to develop when the multidimensional effect is obvious. However, a simple and accurate analytical model is very important for circuit analysis.

In modeling the short-channel effect in a short gatelength MESFET, the two-dimensiona (2D) Poisson's equation satisfying different surface boundary conditions must be solved to get the 2D potential distribution. In previous work in [4], [5], the 2D Poisson's equation has been solved by a Laplace reduction technique with the 2D Poisson's equation being divided into a 2D Laplace equation and a one-dimensional (1D) ordinary differential equation, and the doping profile in the active channel has been assumed to be uniform. Moreover, in order to avoid the problems resulting from different surface boundary conditions the n<sup>+</sup> region was assumed to contact directly to the gate metal, and the absorption of the electric field by the depletion charges near the source/drain side was not taken into account. For a practical MESFET structure, the spacing between the n<sup>+</sup> region and the gate metal cannot be overlooked because it can reduce the short-channel effects [6] and further enhance the breakdown voltage. In a recent paper [7], the trial function method has been used to solve the 2D Poisson's equation in the ungated part of the channel. However, this method does not clearly take the surface boundary conditions in the ungate region into

Ion implantation has become a widely used process for doping the active channel and source/drain regions of a short gate-length MESFET [8]. Recently, the implanted channel profile has been considered in modeling the I-Vcharacteristics of an implanted MESFET device by using 1D analysis [9]. In general, the effects of both short gate length and implanted channel profile have not been well described in the literature. In order to treat the implanted doping profile in the active channel of a MESFET device, the Green's function technique used in MOSFET modeling [10] is used to solve the 2D Poisson's equation. In this paper, a new analytical technique is developed, in which different types of Green's function are used to calculate the 2D Poisson's equation to satisfy different surface boundary conditions. The problem resulting from different surface boundary conditions can be solved by matching the potential and electric field distributions. In Section II, the boundary conditions for a non-self-aligned MESFET structure and 2D potential distribution calculated by the Green's function technique are presented. In Section III. some approximations are made for a non-selfaligned MESFET in order to simplify the analytical equations derived in Section II. In Section IV, the developed quasi-analytical models are compared with the results calculated by 2D numerical simulation for a wide range of device parameters. Furthermore, the relationship between the short-channel effect and the device structure is discussed. Finally, a conclusion is given in Section V.

### II. THEORETICAL MODEL

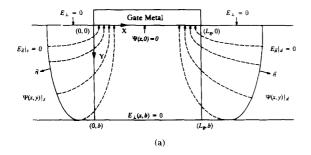

A simplified diagram showing the electric field distribution near the end of the gate metal for a non-self-aligned MESFET device operated in the subthreshold region is illustrated in Fig. 1(a). It is shown that some of the lateral field will be terminated by the edge side of the gate metal if the device has a long gate length, and the channel potential is slightly affected by the lateral field. However, this is not true for a short gate-length device or when the lateral field is large. For a short gate-length MESFET, the channel potential cannot be entirely controlled by the gate bias and will be shifted by the penetration of the lateral field. From this veiwpoint, there are two factors which may play important roles for the short-channel effect in a short gate-length MESFET: one is the lateral field distribution at the sidewall of the gate edge; the other is the efficiency of the gate metal in terminating the lateral field. It is clear that a solution technique for the 2D Poisson's equation satisfying suitable boundary conditions is required to model the short-channel effect. However, it becomes very difficult for a MESFET structure due to the complexity of the boundary conditions. In the following subsections, the Green's function solution technique is proposed to solve the 2D Poisson's equation for a nonself-aligned MESFET structure. Some assumptions and approximations are made to reduce the complexity in order to get a solution analytically.

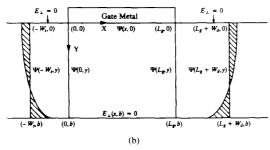

Fig. 1. The schematic diagrams for a non-self-aligned MESFET structure operated in the subthreshold region. (a) Penetration of the sidewall field into the gate-controlled region and the boundary conditions used. (b) Approximation used to develop an analytical model for 2D potential distribution

# A. Boundary Conditions

The cross-sectional view of a GaAs MESFET operated in the subthreshold region is shown in Fig. 1(a), where the x coordinate represents the direction along the surface and the y coordinate represents the direction perpendicular to the surface. Because the mobile carriers are negligibly small when the device is operated in the subthreshold mode, the current continuity equation can be ignored. The charge distribution in the active channel is assumed to be the ionized impurity profile and the 2D Poisson's equation can be written as

$$\frac{\partial^2 \Psi(x, y)}{\partial x^2} + \frac{\partial^2 \Psi(x, y)}{\partial y^2} = -\frac{q}{\epsilon} N_d(x, y). \tag{1}$$

It is assumed that the effect of the surface states on the ungated semiconductor surface is very small and the electric flux vanishes in these regions, hence the surface boundary conditions can be expressed as

$$E_{\perp}(x, 0) = -\frac{\partial \Psi(x, y)}{\partial y}\bigg|_{y=0} = 0,$$

for

$$x < 0$$

or  $x > L_g$  (2)

and

$$|\Psi(x, y)|_{y=0} = 0, \quad \text{for } 0 \le x \le L_{g}$$

(3)

where the gate metal is used as the reference point.

For a practical GaAs MESFET, the effect of the semiinsulating substrate is very sophisticated. In order to simplify the mathematical treatment without losing its validity, the boundary condition in the bottom side of the active layer is set to the Neumann boundary condition and the substrate effect is neglected. The boundary condition in the bottom side of the active channel can be expressed

$$E_{\perp}(x, b) = -\frac{\partial \psi(x, y)}{\partial y}\bigg|_{y=b} = 0.$$

(4)

When the MESFET device is operated in the subthreshold region, the drain current is very small and the ohmic drop across the ungate regions can be neglected. The potentials at both sides of the depletion-layer edge can be expressed as

$$\Psi(x, y)|_{s} = V_{bi} - V_{gs} \tag{5}$$

and

$$\Psi(x, y)|_{d} = V_{bi} - V_{gs} + V_{ds}$$

(6)

where the depletion-layer edges at the source and drain sides are denoted by s and d, respectively.

Moreover, the electric field must vanish in the depletion-layer edges at both sides of the gate, otherwise, this field may cause a large current flow. Therefore, we may write

$$E_{\vec{n}}|_{s} = 0 \tag{7}$$

and

$$E_{\vec{n}}|_d = 0 \tag{8}$$

where  $\vec{n}$  is the outward unit vector at the depletion-layer edge.

## B. Green's Function Solution Technique

The solution of the 2D Poisson's equation in a finite region can be obtained by means of the Green's function technique. Using Green's theorem, the potential distribution can be expressed as [11]

$$\Psi(x, y) = \iint_{V} \frac{\rho(x', y')}{\epsilon} G(x, y; x', y') dx' dy'$$

$$- \int_{S} \Psi(x', y') \frac{\partial G}{\partial n'} dS'$$

$$+ \int_{S} \frac{\partial \Psi(x', y')}{\partial n'} G(x, y; x', y') dS'. \quad (9)$$

The Green's function for a rectangular domain can be expressed in a hyperbolic-sine (hyperbolic-cosine) form. However, this form cannot be directly applied to a MESFET structure shown in Fig. 1(a) because the surface boundary conditions are different for the gated and ungated regions. In order to solve the 2D Poisson's equation with these different surface boundary conditions, the

T

Green's function is chosen as

$$G(x, x'; y, y') = \frac{c}{b} \sum_{n=0}^{\infty} \cos(k_n y) \cos(k_n y') F_I(x; x'; k_n),$$

for  $x \le 0$  (10a)

$$G(x, x'; y, y') = \frac{2}{b} \sum_{m=1}^{\infty} \sin(k_m y) \sin(k_m y') F_{II}(x; x'; k_m),$$

for  $0 \le x \le L_g$ , (10b)

$$G(x, x'; y, y') = \frac{c}{b} \sum_{n=0}^{\infty} \cos(k_n y) \cos(k_n y') F_{III}(x; x'; k_n),$$

for  $x \ge L_g$  (10c)

where  $k_n = n\pi/b$ ,  $k_m = (m - 1/2)\pi/b$ ; n and m are the integers; c = 1 for n = 0 and c = 2 for  $n \ge 1$ ;  $F_1$ ,  $F_{II}$ , and  $F_{III}$  are expressed by

$$F_{I}(x; x', k_{n}) = \begin{cases} \frac{\sinh(k_{n}x) \sinh k_{n}(W_{s} + x')}{k_{n} \sinh(k_{n}W_{s})}, \\ \text{for } x' < x \\ \frac{\sinh(k_{n}x') \sinh k_{n}(W_{s} + x)}{k_{n} \sinh(k_{n}W_{s})}, \\ \text{for } x' > x \end{cases}$$

(11a)

$$F_{II}(x; x'; k_m) = \begin{cases} \frac{\sinh (k_m x) \sinh k_m (L_g - x')}{k_m \sinh (k_m L_g)}, \\ \text{for } x' > x \\ \frac{\sinh (k_m x') \sinh k_m (L_g - x)}{k_m \sinh (k_m L_g)}, \\ \text{for } x' < x \end{cases}$$

(11b)

$$F_{\text{III}}(x; x'; k_n) = \begin{cases} \frac{\sinh k_n(x - L_g) \sinh k_n(L_g + W_d - x')}{k_n \sin (k_n W_d)}, \\ \text{for } x' > x \\ \frac{\sinh k_n(x' - L_g) \sinh k_n(L_g + W_d - x)}{k_n \sinh (k_n W_d)}, \\ \text{for } x' < x. \end{cases}$$

(11c)

It is assumed that the depletion-layer edge at the source (drain) side is perpendicular to the surface at a position  $-W_s(L_g+W_d)$ , as shown in Fig. 1(b). It is noted that, in (11a) and (11c), the hyperbolic-sine function decays exponentially for  $n \ge 1$  and the influence of the sidewall potential at the source (drain) side of the gate due to the high-order terms of the Fourier component for the charge

distribution at the depletion edge can be estimated from  $\exp{(-n\pi W_s/b)}$  or  $\exp{(-n\pi W_d/b)}$  for  $n \ge 1$ . Since the depletion-layer edges at both sides of the gate are far away from the channel region under the gate for a non-self-aligned structure, it is expected that the channel potential is less affected by the detailed shape of the charge distribution in the depletion boundary at both sides of the gate because this charge distribution is described by the high-order terms of the Fourier series. The sidewall potential at both sides of the gate edge  $(x = 0 \text{ and } x = L_g)$  can be determined by using the continuation of the lateral electric field. The Fourier transformation for the sidewall potential at the source/drain side of the gate edge is performed, and the Fourier coefficients of the sidewall potential can be expressed as the superposition of two parts

$$\Psi(0, y) = \sum_{m=1}^{\infty} (A_m^s + B_m) \sin(k_m y)$$

(12a)

and

$$\Psi(L_g, y) = \sum_{m=1}^{\infty} (A_m^d + B_m) \sin(k_m y)$$

(12b)

where  $B_m$  is the Fourier coefficient of the 1D potential distribution due to the ionized impurity profile under the gate and is expressed by

$$B_m = \frac{2}{b} \int_0^b \Psi_{1d}(y) \sin(k_m y) \, dy$$

(13)

in which  $\Psi_{1d}(y)$  is expressed as

$$\Psi_{1d}(y) = \int_0^y \frac{qN_d(y')}{\epsilon} y' dy' + y \int_y^b \frac{qN_d(y')}{\epsilon} dy'. \quad (14)$$

Note that  $\Psi_{1d}(y)$  in (14) is independent of bias conditions;  $A_m^s$  and  $A_m^d$  are the unknown variables, which can be determined by the boundary conditions.

Substituting (5), (11a), and (12a) into (9), the x-component electric field in the ungated region at the source side can be expressed as

$$E_x^s(x, y) = E_{x,0}(x, y) + E_{x,s}^s(x, y) + E_{x,q}^s(x, y)$$

(15)

where  $E_{x,0}^{s}(x, y)$  is the electric field due to the sidewall potential at the source side and is expressed by

$$E_{x,0}^{s}(x, y) = -\frac{\overline{V}_{s}}{W_{s}} - \sum_{n=1}^{\infty} \frac{k_{n} \cosh k_{n}(W_{s} + x)}{\sinh (k_{n}W_{s})}$$

$$\cdot \sum_{m=1}^{\infty} (A_{m}^{s} + B_{m}) T_{mn} \cos (k_{n}y). \quad (16)$$

$E_{x,s}^{s}(x, y)$  is the electric field due to the potential at the depletion-layer edge at the source side and is expressed by

$$E_{x,s}^{s}(x, y) = \frac{V_{bi} - V_{gs}}{W_{s}}.$$

(17)

$E_{x,q}^{s}(x, y)$  is the electric field due to the depletion charge in the ungated region at the source side and is given by

$$E_{x,q}^{s}(x, y) = -\sum_{n=0}^{\infty} \frac{\cos(k_{n}y)}{\sinh(k_{n}W_{s})} \left[ \cosh k_{n}(W_{s} + x) \right]$$

$$\cdot \int_{0}^{x} \frac{qN_{d,n}^{s}(x)}{\epsilon} \sinh(k_{n}x) dx$$

$$+ \cosh(k_{n}x) \int_{x}^{-W_{s}} \frac{qN_{d,n}^{s}(x)}{\epsilon}$$

$$\cdot \sinh k_{n}(W_{s} + x) dx \right]. \tag{18}$$

The boundary condition in (7) is used to determine the unknown parameter  $W_s$ . Integrating (15) over the active channel at  $x = -W_s$ , we can obtain the following equation:

$$\frac{V_{bi} - V_{gs}}{W_s} - \frac{\overline{V}_s}{W_s} - \int_0^{-W_s} \frac{x}{W_s} \frac{q N_{d,0}^s(x)}{\epsilon} dx = 0. \quad (19)$$

The average lateral electric field at the depletion-layer edge at the source side can be eliminated by using (19). Note that the high-order terms in (18) do not exactly vanish due to the assumption of the perpendicular relation between the depletion-layer edge and the surface. However, the sidewall potential at the source side is not strongly affected by this approximation because these terms decay exponentially.

Similarly, the lateral electric field under the gate can be expressed as

$$E_x^g(x, y) = E_{x,0}^g(x, y) + E_{x,L_g}^g(x, y) + E_{x,g}^g(x, y)$$

(20)

where

$$E_{x,0}^{g}(x, y) = \sum_{m=1}^{\infty} k_m (A_m^{s} + B_m)$$

$$\cdot \sin(k_m y) \frac{\cosh k_m (L_g - x)}{\sinh(k_m L_g)}$$

(21)

$$E_{x,L_g}^g(x, y) = \sum_{m=1}^{\infty} -k_m (A_m^d + B_m) \sin(k_m y) \frac{\cosh(k_m x)}{\sinh(k_m L_g)}$$

(

$$E_{x,q}^{g}(x, y) = \sum_{m=1}^{\infty} \frac{qN_{d,m}}{\epsilon} \frac{\sin(k_m y)}{k_m \sinh(k_m L_g)}$$

$$\cdot \left[\cosh(k_m x) - \cosh k_m (L_g - x)\right]. \tag{23}$$

Note that the doping profile  $N_d(x, y)$  under the gate is assumed to be only dependent on the y direction, thus  $N_d$  is independent of x under the gate. The lateral electric field must be continuous at x = 0, so we obtain

$$E_x^s(0, y) = E_x^g(0, y).$$

(24)

Substituting (15) and (20) into (24) and performing the Fourier transformation, i.e.,

$$\frac{2}{b} \int_0^b (E_x^g(0, y) - E_x^s(0, y)) \sin(k_m y) \, dy = 0 \quad (25)$$

we obtain

$$\left(k_{m}B_{m} - \frac{qN_{d,m}}{\epsilon k_{m}}\right) \frac{\cosh(k_{m}L_{g}) - 1}{\sinh(k_{m}L_{g})}$$

$$+ \frac{k_{m}}{\sinh(k_{m}L_{g})} (A_{m}^{s} \cosh(k_{m}L_{g}) - A_{m}^{d})$$

$$+ \frac{2}{(m-1/2)\pi} \frac{1}{W_{s}} \left[\int_{0}^{-W_{s}} \frac{qN_{d,0}^{s}(x)}{\epsilon} (W_{s} + x) dx - V_{bi} + V_{gs} + \overline{V}_{s}\right] + \sum_{n=1}^{\infty} T_{mn}k_{n} \coth(k_{n}W_{s})$$

$$\cdot \sum_{m1=1}^{\infty} (A_{m1}^{s} + B_{m1}) T_{m1,n} + \sum_{n=1}^{\infty} \frac{T_{mn}}{\sinh(k_{n}W_{s})}$$

$$\cdot \int_{0}^{-W_{s}} \frac{qN_{d,n}^{s}(x)}{\epsilon} \sinh k_{n}(W_{s} + x) dx = 0,$$

for  $m = 1, 2, 3, \dots, \infty$  (26)

where the first term in (26) can be eliminated because  $B_m k_m^2 = q N_{d,n} / \epsilon$ .

A similar treatment can be performed for the drain side to obtain another system of equations, and the results are expressed as

$$-\frac{V_{bi} + V_{ds} - V_{gs}}{W_d} + \frac{\overline{V}_d}{W_d} + \int_{L_g}^{L_g + W_d} \frac{x - L_g}{W_d} \frac{q N_{d,0}^d(x)}{\epsilon} dx = 0$$

(27)

and

$$\frac{k_{m}}{\sinh(k_{m}L_{g})} (A_{m}^{d} \cosh(k_{m}L_{g}) - A_{m}^{s})$$

$$- \frac{2}{(m-1/2)\pi} \frac{1}{W_{d}} \left[ \int_{L_{g}}^{L_{g}+W_{d}} \frac{qN_{d,0}^{d}(x)}{\epsilon} \right]$$

$$\cdot (L_{g} + W_{d} - x) dx + V_{bi} - V_{gs} + V_{ds} - \overline{V}_{d}$$

$$+ \sum_{n=1}^{\infty} T_{mn}k_{n} \coth(k_{n}W_{d}) \sum_{m=1}^{\infty} (A_{m1}^{d} + B_{m1})T_{m1,n}$$

$$- \sum_{n=1}^{\infty} \frac{T_{mn}}{\sinh(k_{n}W_{d})} \int_{L_{g}}^{L_{g}+W_{d}} \frac{qN_{d,n}^{d}(x)}{\epsilon}$$

$$\cdot \sinh k_{n}(L_{g} + W_{d} - x) dx = 0,$$

for  $m = 1, 2, 3, \dots, \infty$ . (28)

In order to accurately model the 2D effects, one must obtain self-consistent solution from (19) and (26)-(28).

However, since these equations are too complicated from the viewpoint of an analytical model, some approximations will be made in the following section in order to get a simple expression.

# III. A SIMPLIFIED TECHNIQUE FOR A NON-SELF-ALIGNED MESFET

With the help of a numerical simulation, some approximations can be made for a non-self-aligned structure. First, it is shown that the Fourier coefficients  $(A_m^s)$  and  $A_m^d$  of the excess sidewall potential decrease rapidly with respect to the integer m and the first term is almost five times larger than the second term. Secondly, the hyperbolic-sine function decreases exponentially with respect to the integer m. Therefore, it is expected that the first term is sufficient to predict the channel potential under the gate, especially for the region near the middle of the gate. As a result, the potential distribution under the gate can be approximated by the following equation:

$$\Psi(x, y) \cong \Psi_{1d}(y) + A_1^s \frac{\sinh k_1(L_g - x)}{\sinh (k_1 L_g)} + A_1^d \frac{\sinh (k_1 x)}{\sinh (k_1 L_g)}$$

(29)

where  $k_1$  (=  $\pi/2b$ ) is the eigenvalue for the first term of the Fourier series in the channel region under the gate.

It is clearly seen that the potential distribution under the gate in (29) is expressed in terms of only two variables  $(A_1^s \text{ and } A_1^d)$  which can be solved from (19) and (26)-(28). Similarly, since the doping profile at both sides of the gate is assumed to be independent of x, (26) with m = 1 can be rewritten as

$$\frac{k_{1}}{\sinh (k_{1}L_{g})} \left(A_{1}^{s} \cosh (k_{1}L_{g}) - A_{1}^{d}\right) \\

+ \frac{4}{\pi} \frac{1}{W_{s}} \left(-\frac{qN_{d,0}^{s}}{2\epsilon} W_{s}^{2} - V_{bi} + V_{gs} + \overline{V}_{s}\right) \\

+ \sum_{n=1}^{\infty} T_{1n}k_{n} \coth (k_{n}W_{s}) \sum_{m_{1}=1}^{\infty} A_{m1}^{s} T_{m1,n} \\

+ \sum_{n=1}^{\infty} T_{1n} \frac{qN_{d,n}^{s}}{\epsilon} \frac{1 - \cosh (k_{n}W_{s})}{k_{n} \sinh (k_{n}W_{s})} \\

+ \sum_{n=1}^{\infty} T_{1n}k_{n} \coth (k_{n}W_{s}) \sum_{m_{1}=1}^{\infty} B_{m1}T_{m1,n} = 0 \quad (30)$$

where  $W_s$  can be obtained from (19) and is expressed by

$$W_s = \left[ \frac{2\epsilon}{qN_{d,0}^s} \left( V_{bi} - V_{gs} - \overline{V}_s \right) \right]^{1/2}. \tag{31}$$

Note that the most complicate term in (30) is the third term, which is a coupling term between these Fourier coef-

ficients and can be rewritten as

$$\sum_{n=1}^{\infty} T_{1,n} k_n \coth (k_n W_s) \sum_{m=1}^{\infty} A_{m1}^s T_{m1,n}$$

$$= A_1^s \left[ \sum_{n=1}^{\infty} k_n \coth (k_n W_s) \cdot \left( T_{1n} T_{1n} + T_{1n} \sum_{m=1}^{\infty} \frac{A_{m1}^s}{A_1^s} T_{m1,n} \right) \right]. \quad (32)$$

However, the solution of (30) is insensitive to this term and the ratio  $(A_m^s/A_1^s)$  is almost constant for wide ranges of device parameter and bias conditions. Therefore, this term can be simplified by the numerical analysis and is expressed as

$$\sum_{n=1}^{\infty} T_{1,n} k_n \coth (k_n W_s) \sum_{m=1}^{\infty} A_{m1}^s T_{m1,n} \cong \frac{1.4}{\pi b} A_1^s. \quad (33)$$

Moreover, the average potential can be approximated by

$$\overline{V}_s \cong V_1 + \frac{2}{\pi} A_1^s. \tag{34}$$

Using (31), (33), and (34), (30) can be rewritten in a simple form

$$\alpha A_1^s - \beta A_1^d = \frac{8}{\pi} V_p \left( \frac{V_{bi} - V_{gs} - V_1 - \frac{2}{\pi} A_1^s}{V_p} \right)^{1/2} + \eta(W_s)$$

(35)

where  $\alpha$ ,  $\beta$ ,  $V_1$ , and  $V_p$  are the structure parameters, which are independent of bias conditions and are expressed as

$$\alpha = \frac{\pi}{2} \coth (k_1 L_g) + \frac{1.4}{\pi}$$

(36)

$$\beta = \frac{\pi}{2} \frac{1}{\sinh(k_1 L_a)} \tag{37}$$

$$V_1 = \sum_{m=1}^{\infty} \frac{B_m}{(2m-1)\pi}$$

(38)

$$V_p = \frac{qN_{d,0}^s}{2\epsilon} b^2 \tag{39}$$

and

$$\eta(W_s) = b \left[ \sum_{n=1}^{\infty} T_{1n} k_n \coth(k_n W_s) \sum_{m=1}^{\infty} B_{m1} T_{m1,n} + \sum_{n=1}^{\infty} T_{1n} \frac{q N_{d,n}^S}{\epsilon} \frac{1 - \cosh(k_n W_s)}{k_n \sinh(k_n W_s)} \right]. \tag{40}$$

Equation (35) is very similar to the result of the 1D case with uniformly doped substrate. The second term on the left-hand side of (35) is related to the electric field produced by the boundary condition at the drain side,  $V_1$  is the average potential for the 1D potential distribution due to the depletion charges,  $V_p$  is the effective pinch-off potential and is equal to the pinch-off voltage when the ac-

tive channel is uniformly doped. The relation between the the nonuniformly doped profile and the 2D effect is clearly described in (40), in which  $\eta$  is contributed by two terms: the first term is the 1D sidewall potential due to the ionized impurities under the gate, and the second term is the nonuniformly distributed depletion charges at the source side of the gate. However, from another viewpoint,  $\eta(W_s)$  can be treated as the unmatching part of the lateral field between different regions and must be offset by the sidewall potential. If we assume that  $W_s$  is sufficiently larger than b, then  $\coth(k_n W_s) \cong 1$ , and  $\eta(W_s)$  can be approximated by

$$\eta(W_s) = b \sum_{n=1}^{\infty} T_{1n} \left( \sum_{m1=1}^{\infty} k_n B_{m1} T_{m1,n} - \frac{q N_{d,n}^s}{k_n \epsilon} \right). \quad (41)$$

It should be noted that  $\eta$  is independent of  $W_s$  from this approximation. This means that the variable  $W_s$  is eliminated in (35) and the unknown variables are only  $A_1^s$  and  $A_1^d$ . In general, this approximation is valid for different Gaussian profiles, however, the iteration must be performed to get a self-consistent solution for heavy doping in the ungated region.

The same treatment can be performed for the drain side. Similarly, we can obtain

$$\alpha A_{1}^{d} - \beta A_{1}^{s}$$

$$= \frac{8}{\pi} V_{p} \left( \frac{V_{ds} + V_{bi} - V_{gs} - V_{1} - \frac{2}{\pi} A_{1}^{d}}{V_{p}} \right)^{1/2} + \eta(W_{d})$$

$$(42)$$

where the parameters used are same as those in (35) if the structure parameters are symmetrical for both the source and the drain, i.e.,

$$N_{q,n}^s = N_{q,n}^d$$

, for  $n = 1, 2, 3, \dots, \infty$ .

#### IV. APPLICATIONS AND VERIFICATIONS

It is known that 2D effects in a short gate-length MESFET can be easily demonstrated by measuring the threshold voltage and the subthreshold current of the fabricated short gate-length MESFET's. These two electrical parameter/characteristics are strongly dependent of gate length and applied drain bias. Therefore, the derived equations in Section III will be used to develop the threshold-voltage model and the drain-induced barrier lowering of a short gate-length MESFET in the following subsections. Moreover, a new 2D device simulator [12] based on conventional semiconductor device equations is used to verify the accuracy of the developed analytical models.

# A. Excess Sidewall Potentials and Potential Distribution

In order to calculate the potential distribution under the gate, the sidewall potential and the width of the depletion layer at both sides of the gate must be calculated first. The

first term of the Fourier coefficient for the excess sidewall potential at the source end of the gate can be solved from (31) and (35), and the results are

$$A_1^s = V_p \left[ a_1 + b_1 \left( \frac{V_{bi} - V_{gs} - V_1}{V_p} - c_1 \right)^{1/2} \right]$$

(43)

and

$$W_{s} = \left[ \frac{2\epsilon}{qN_{d,0}^{s}} \left( V_{bi} - V_{gs} - V_{1} - \frac{2}{\pi} A_{1}^{s} \right) \right]^{1/2}$$

(44)

where  $a_1 = [\beta A_1^d + \eta(W_s)]/(\alpha V_p) - 64/(\pi^3 \alpha^2)$ ,  $b_1 = 8/(\pi \alpha)$ , and  $c_1 = 2a_1/\pi - 64/(\pi^4 \alpha^2)$ .

Similarly, the results for the drain side are

$$A_1^d = V_p \left[ a_2 + b_2 \left( \frac{V_{ds} + V_{bi} - V_{gs} - V_1}{V_p} - c_2 \right)^{1/2} \right]$$

(45)

and

$$W_{d} = \left[\frac{2\epsilon}{qN_{d,0}^{d}} \left(V_{bi} - V_{gs} + V_{ds} - V_{1} - \frac{2}{\pi} A_{1}^{d}\right)\right]^{1/2}$$

(46)

where  $a_2 = [\beta A_1^s + \eta(W_d)]/(\alpha V_p) - 64/(\pi^3 \alpha^2)$ ,  $b_2 = 8/(\pi \alpha)$ , and  $c_2 = 2a_2/\pi - 64/(\pi^4 \alpha^2)$ .

Note that the above equations seem to be similar to the 1D results; however, the 2D effects are properly considered. It should be noted that the magnitude of  $A_1^s(A_1^d)$  is proportional to the lateral electric field at the gate edge and is strongly affected by the total amount of the depletion charges that can terminate the electric field. It is expected that the self-aligned structure will have a larger sidewall potential than the non-self-aligned structure if the depletion edges at both sides of the gate touch the  $n^+$  region.

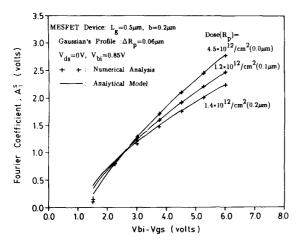

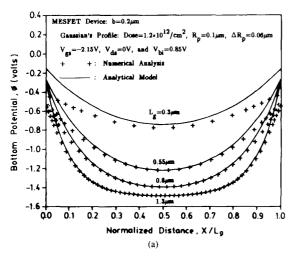

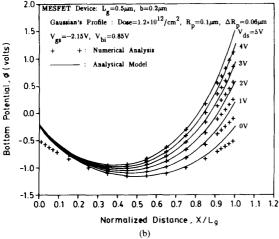

Comparisons between the first term of the Fourier coefficient in the excess sidewall potential at the source side in (43) and the 2D numerical analysis are shown in Fig. 2, in which the active channel thickness is 0.2  $\mu$ m,  $R_p$  is the projected range with the reference point at the semiconductor surface,  $\Delta R_p$  is the standard deviation or the projected straggle, and the doses of ion implantation are chosen to keep the pinch-off voltage of a long gate-length device at 1.5 V. Fig. 3(a) shows the bottom potential versus the normalized distance along the channel  $(x/L_g)$  for various gate lengths. It is clearly seen that the central portion of the bottom potential distribution increases with decreasing gate length, and good agreements between the analytical model and the 2D numerical analysis are obtained for this portion which is important for accurately modeling the threshold voltage as described in the next subsection. Note that there are some discrepancies between comparisons at the gate edges, especially for the case of a shorter gate-length device. These discrepancies are mainly due to the fact that  $A_1^s$  in (43) and  $A_1^d$  in (45) only keep the first term of the Fourier series. The varia-

Fig. 2. Comparisons between the first term of the Fourier coefficients in the excess sidewall potential and the 2D numerical analysis for different Gaussian profiles in the active channel.

Fig. 3. Comparisons of the bottom potential versus the normalized distance  $(x/L_g)$  between the analytical model and the 2D numerical analysis for a Gaussian profile. (a) Various gate lengths with  $V_{ds}=0$  V and  $V_{gs}=-2.15$  V. (b) Various  $V_{ds}$  and  $V_{gs}=-2.15$  V for gate length of 0.5  $\mu$ m.

tion of the bottom potential with the drain bias is shown in Fig. 3(b). It is noted that the potential barrier is lowered by the drain bias, and satisfactory agreements between the analytical model and the 2D numerical simulation are obtained.

#### B. Threshold Voltage

Threshold voltage is a key device parameter in circuit design. A usual definition for the threshold voltage of a MESFET implies an abrupt transition between the turn-off and turn-on regions. The drain current, however, does not immediately decrease to zero for the gate bias below the threshold voltage. Instead, the drain current varies almost exponentially with the gate bias in the subthreshold region due to the formation of the channel barrier. From this viewpoint, we use the formation of the channel barrier to define the threshold voltage. The criterion for the threshold voltage is defined by the condition that the channel barrier height  $(\phi_b)$  is equal to  $\phi_b^c$ , i.e.,

$$\phi_b = \Psi_{\min} + V_{th} - V_{bi} = \phi_b^c, \quad \text{for } V_{ds} = 0.$$

(47)

If the device structure is symmetrical in the source and drain regions and  $V_{ds} = 0$ , we obtain

$$A_1^d = A_1^s. (48)$$

Substituting (48) into (35),  $A_1^s$  can be written as

$$A_1^s = V_p \left[ a_3 + b_3 \left( \frac{V_{bi} - V_{th} - V_1}{V_p} - c_3 \right)^{1/2} \right]$$

(49)

where  $a_3 = \eta (W_s)/[(\alpha - \beta)V_p] - 64/[\pi^3(\alpha - \beta)^2], b_3 = 8/[\pi(\alpha - \beta)], \text{ and } c_3 = 2a_3/\pi - 64/[\pi^4(\alpha - \beta)^2].$

Substituting (48) and (29) into (47), the threshold voltage must satisfy the following equation:

$$V_{\rm th} = V_{\rm th}^0 - 2KA_1^s \tag{50}$$

where  $K = \operatorname{sech} (k_1 L_g/2)/2$ .

From (49) and (50),  $V_{th}$  can be analytically expressed

$$V_{\text{th}} = V_{\text{th}}^{0} - 2KV_{p} \left[ a_{3} + Kb_{3}^{2} + b_{3} \left( \frac{V_{bi} - V_{1} - V_{\text{th}}^{0}}{V_{p}} + 2Ka_{3} + 2b_{3}^{2} K^{2} - c_{3} \right)^{1/2} \right].$$

(51)

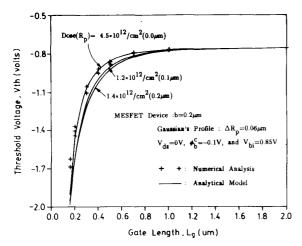

From (51), the K factor is a key parameter used to describe the short gate-length effect. Comparisons between the analytical model and the 2D numerical simulation for various Gaussian profiles in the active channel are shown in Fig. 4, in which the dose of ion implantation is chosen to keep the pinch-off voltage of a long gate-length device at 1.5 V for various profiles. It is shown that the developed analytic threshold-voltage model is valid for gate length down to 0.15  $\mu$ m and different Gaussian profiles in the active channel. It is noted that the 2D effect on the threshold voltage is not obviously influenced by the non-uniform doping profile under the gate. This phenomenon is due to the fact that most of the doping impurities in the

Fig. 4. Comparisons of the threshold voltage versus gate length between the analytical model and the 2D numerical analysis for different Gaussian profiles in the active channel.

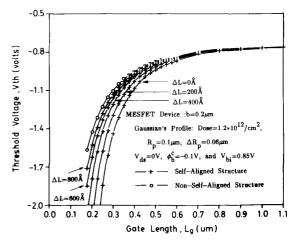

sidewall are screened out by the mobile carriers when the device is operated in near turn-on. The 2D numerical analysis of the threshold voltage for a self-aligned MESFET structure with different sidewall spacings between the gate and the  $n^+$  region is shown in Fig. 5, in which the sidewall spacing is denoted by  $\Delta L$ . It is shown in this figure that the threshold-voltage shift for the direct contact of the gate to the  $n^+$  region is larger than that of a non-self-aligned structure; however, the difference is not obvious if the sidewall spacing is greater than 600 Å. This implies that (51) is also valid for a self-aligned structure for wide ranges of sidewall spacing.

## C. Drain-Induced Barrier Lowering

As gate length decreases, the channel potential will be perturbed by the drain bias. The barrier in the channel will be lowered by the drain voltage. This phenomenon is known as the drain-induced barrier lowering (DIBL) effect. The DIBL effect may produce an excess leakage current injected from the source, resulting in a serious shift of the subthreshold current curve. Therefore, it is important to include the DIBL effect for designing the cutoff characteristics of a short gate-length MESFET.

Equation (29) can be used to model the DIBL effect, in which  $A_s^s$  and  $A_l^d$  can be obtained from (43)–(46), and the minimum of the channel potential can be obtained by

$$\frac{d\Psi(x,\,b)}{dx}\bigg|_{x=x} = 0. \tag{52}$$

Using (29) and (52), the location of the minimum channel potential can be solved as

$$x_{\min} = \frac{1}{k_1} \tanh^{-1} \left[ \frac{\cosh(k_1 L_g) - A_1^s / A_1^d}{\sinh(k_1 L_g)} \right].$$

(53)

Note that  $x_{\min}$  is  $L_g/2$  when  $A_1^s = A_1^d$ . This means that the turn-on point in a non-self-aligned MESFET device is lo-

Fig. 5. The simulated variations of the threshold voltage with respect to the gate length for various spacings in self-aligned and non-self-aligned MESFET's.

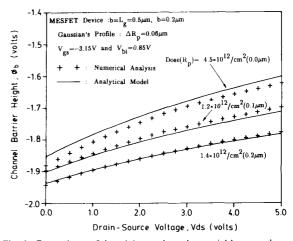

Fig. 6. Comparisons of the minimum channel potential between the analytical model and the 2D numerical analysis for different Gaussian profiles in the active channel.

cated nearly at the middle of the gate if the device is symmetrical in the source and drain regions and  $V_{ds}$  is small. The channel barrier can be written as

$$\phi_b = \Psi_{\min} - V_{bi} + V_{gs}$$

$$= \Psi_{1d}(b) - V_{bi} + V_{gs} + [2A_1^s A_1^d \cosh(k_1 L_g) - (A_1^d)^2 - (A_1^d)^2]^{1/2} / \sinh(k_1 L_g).$$

(54)

Comparisons between the analytical model and the 2D numerical simulations are shown in Fig. 6 for a gate length of 0.5  $\mu m$  and an active layer thickness of 0.2  $\mu m$ . It is clearly seen that the effect of a nonuniform channel profile can be well predicted by the developed analytical model. It is noted that the shift of the channel barrier for the heavily doped case will be larger than for the lightly doped case.

#### V. Conclusion

A new 2D analytical model for the 2D potential and electric field distributions of a non-self-aligned MESFET is presented, in which the effects of implanted profile and surface boundary conditions are properly considered in the proposed model. The problem resulting from different types of surface boundary conditions is treated by matching the sidewall boundary conditions, and the potential distribution is obtained by the Green's function technique. There are no trial solution and fitting parameters used in the developed models. Based on the derived analytical potential distribution, the simplified formula for the sidewall potential, the threshold voltage, and the draininduced barrier lowering can be obtained. From comparisons between the developed analytical models and the 2D numerical simulation, the short-channel effects in nonself-aligned MESFET's can be clearly described by the simplified models.

#### REFERENCES

- T. Wada and J. Frey, "Physical basis of the short-channel MESFET operation," *IEEE J. Solid-State Circuits*, vol. SC-14, no. 2, pp. 398– 412, 1979.

- [2] K. Horio, H. Yanai, and T. Ikoma, "Numerical simulation of GaAs MESFET's on the semi-insulating substrate compensated by deep traps," *IEEE Trans. Electron Devices*, vol. 35, no. 11, pp. 1778– 1785, 1988.

- [3] J. C. Ramirez, P. J. Mcnally, L. S. Copper, J. J. Rosenberg, L. B. Freund, and T. N. Jackson, "Development and experimental verification of a two-dimensional numerical model of piezoelectrically induced threshold voltage shifts in GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. 35, no. 8, pp. 1232–1240, 1988.

- Electron Devices, vol. 35, no. 8, pp. 1232-1240, 1988.

[4] J. D. Marshall and J. D. Meindl, "An analytical two-dimensional model for silicon MESFET's," *IEEE Trans. Electron Devices*, vol. 35, no. 3, pp. 373-383, 1988.

- [5] —, "A sub- and near-threshold current model for silicon MES-FET's," IEEE Trans. Electron Devices, vol. 35, no. 3, pp. 388-390, 1988

- [6] N. Kato, Y. Matsuoka, K. Ohwada, and S. Moriya, "Influence of n<sup>+</sup>-layer-gate gap on short-channel effects of GaAs self-aligned MES-FET's (SAINT)," *IEEE Electron Device Lett.*, vol. EDL-4, no. 11, pp. 417-419, 1983.

- [7] C.-S. Chang, D.-Y. S. Day, and S. Chan, "An analytical two-dimensional simulation for the GaAs MESFET drain-induced barrier lowering: A short-channel effect," *IEEE Trans. Electron Devices*, vol. 37, no. 5, pp. 1182-1186, 1990.

- [8] R. Anholt and T. W. Sigmon, "Ion implantation effects on GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. 36, no. 2, pp. 250– 255, 1989.

- [9] S. N. Mohammad, M. B. Patil, J.-I. Chyi, G. B. Gao, and H. Mor-koç, "Analytical model for *I-V* characteristics of ion-implanted MESFET's with heavily doped channel," *IEEE Trans. Electron Devices*, vol. 37, no. 1, pp. 11-20, 1990.

- vices, vol. 37, no. 1, pp. 11-20, 1990.

[10] P. S. Lin and C. Y. Wu, "A new approach to analytically solving the two-dimensional Poisson's equation and its application in short-channel MOSFET modeling," *IEEE Trans. Electron Devices*, vol. ED-34, no. 9, pp. 1947-1956, 1987.

- [11] J. D. Jackson, Classical Electrodynamics. New York: Wiley, 1975.

- [12] S. P. Chin and C. Y. Wu, "A new methodology for two-dimensional numerical simulation of semiconductor devices," *IEEE Trans. Com*puter-Aided Des., vol. 11, Sept. 1992.

Shan-Ping Chin (S'86) was born in Taiwan, Republic of China, on September 21, 1961. He received the B.S. degree from the Department of Physics, National Tsing-Hua University, Taiwan, Republic of China, in 1985, and entered the Institute of Electronics, National Chiao-Tung University, for graduate study in September 1985. Now, he is a Ph.D. candidate and engages in device physics and new simulation techniques for deep-submicrometer MESFET's in the Advanced Semiconductor Device Research Laboratory.

Ching-Yuan Wu (M'72) was born in Taiwan, Republic of China, on March 18, 1946. He received the B.S. degree from the Department of Electrical Engineering, National Taiwan University, Taiwan, Republic of China, in 1968, and the M.S. and Ph.D. degrees from the State University of New York (SUNY) at Stony Brook, in 1970 and 1972, respectively.

During the 1972-1973 academic year, he was appointed as a Lecturer at the Department of Electrical Sciences, SUNY, Stony Brook. During the

1973-1975 academic years, he was a Visiting Associate Professor at National Chiao-Tung University (NCTU), Taiwan, Republic of China. In 1976, he became a Full Professor in the Department of Electronics and the Institute of Electronics, NCTU. At NCTU, he had been the Director of Engineering Laboratories and Semiconductor Research Center, during 1974-1980; the Director of the Institute of Electronics, during 1978-1984; and the Dean, College of Engineering, during 1984-1990. He was a principal invesigator of the National Electronics Mass Plan-Semiconductor Devices and Integrated-Circuit Technologies during 1976-1979, and had been a Coordinator of the National Microelectronics Researches and High-Level Man-Power Education Committee, National Science Council, Republic of China, during 1982-1988. He has been a Research Consultant at the Electronics Research and Service Organization (ERSO), ITRI; a member of the Academic Review Committee, the Ministry of Education; and the chairman of the Technical Review Committee on Information and Microelectronics Technologies, the Ministry of Economic Affairs. His research activities have been in semiconductor device physics and modelings, integrated-circuit designs and technologies. His present research areas focus on the developments of efficient 2D and 3D simulators for deepsubmicrometer semiconductor devices, design rules and optimization techniques for deep-submicrometer CMOS devices, and key technologies for deep-submicrometer CMOS devices. He has published over 150 papers in the semiconductor field and has served as a reviewer for international journals such as IEEE ELECTRON DEVICE LETTERS, IEEE TRANSACTIONS ON ELECTRON DEVICES, Solid-State Electronics, etc. He received the Academic Research Award in Engineering from the Ministry of Education (MOE), in 1979; the outstanding Scholar award from the Chinese Educational and Cultural Foundation, in 1985. He has also received the outstanding research Professor fellowship from the Ministry of Education and the National Science Council (NSC), Republic of China, during 1982-1991.

Dr. Wu is a member of the Honorary Editorial Advisory Board of Solid-State Electronics and is a board member of the Chinese Engineering Society.

Γ-