# A New ZVS-PWM Full-Bridge Converter

Yungtaek Jang, Senior Member, IEEE, Milan M. Jovanović, Fellow, IEEE, and Yu-Ming Chang

*Abstract*—A full-bridge converter which employs a coupled inductor to achieve zero-voltage switching of the primary switches in the entire line and load range is described. Because the coupled inductor does not appear as a series inductance in the load current path, it does not cause a loss of duty cycle or severe voltage ringing across the output rectifier. The operation and performance of the proposed converter is verified on a 670-W prototype.

*Index Terms*—Coupled inductor, full bridge converter, phase shift control, zero voltage switching.

#### I. INTRODUCTION

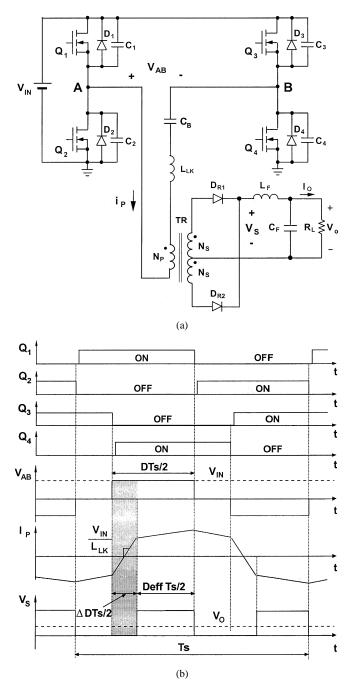

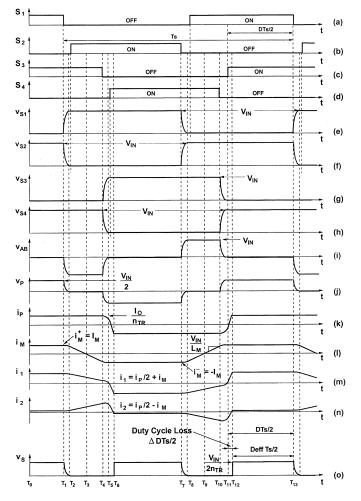

HE full-bridge (FB) zero-voltage-switching (ZVS) PWM converter shown in Fig. 1 is the most widely used soft-switched circuit in high-power applications, [1]-[4]. This constant-frequency converter features ZVS of the primary switches with relatively small circulating energy. The control of the output voltage at constant frequency is achieved by the phase-shift technique. In this technique the switching transition of switches in the  $Q_1-Q_2$  leg of the bridge is delayed, i.e., phase shifted, with respect to the switching transition of corresponding switches in the Q3-Q4 leg. With no phase-shift between the legs of the bridge, no voltage is applied across the primary of the transformer and, consequently, the output voltage is zero. On the other hand, if the phase shift is 180°, the maximum volt-second product is applied across the primary winding, which produces the maximum output voltage. In the circuit in Fig. 1, ZVS of the lagging-leg switches  $Q_1$  and  $Q_2$  is achieved primarily by the energy stored in output filter inductor  $L_F$ . Since the inductance of inductor  $L_F$  is relatively large, the energy stored in inductor L<sub>F</sub> is sufficient to completely discharge output parasitic capacitances  $\mathrm{C}_1$  and  $\mathrm{C}_2$  of switches  $Q_1$  and  $Q_2$  and to achieve ZVS even at very light load currents. However, the discharge of parasitic capacitances  $C_3$  and  $C_4$ of leading-leg switches Q<sub>3</sub> and Q<sub>4</sub> is done by the energy stored in leakage inductance  $L_{\rm LK}$  of the transformer because during the switching of Q<sub>3</sub> or Q<sub>4</sub>, the transformer primary is shorted by the simultaneous conduction of rectifiers D<sub>R1</sub> and D<sub>R2</sub> which carry the output filter inductor current. Since leakage inductance  $L_{LK}$  is small, the energy stored in  $L_{LK}$ is also small so that ZVS of Q<sub>3</sub> and Q<sub>4</sub> cannot be achieved even at relatively high output currents. The ZVS range of the leading-leg switches can be extended to lower load currents by intentionally increasing the leakage inductance of the

Y. Jang and M. M. Jovanović are with the Power Electronics Laboratory, Delta Products Corporation, Research Triangle Park, NC 27709 USA (e-mail: ytjang@deltartp.com).

Fig. 1. Conventional full-bridge ZVS converter and its key waveforms.

transformer and/or by adding a large external inductance in series with the primary of the transformer. If properly sized, the external inductance can store enough energy to achieve ZVS of the leading-leg switches even at low currents. However at full load a large external inductance also stores excessive energy that produces large circulating currents, which adversely affects

Manuscript received September 4, 2002; revised April 7, 2003. This paper was presented at INTELEC'2002. Recommended by Associate Editor C. K. Tse.

Y.-M. Chang is with the Delta Electronics, Inc., Chungli, Taiwan, R.O.C. Digital Object Identifier 10.1109/TPEL.2003.816189

the stress of the semiconductor components as well as the conversion efficiency.

One of the major limitations of the conventional FB ZVS-PWM converter is a loss of duty cycle on the secondary side which is indicated by shaded area in Fig. 1. Generally, a large leakage and/or external inductance extends the time that is needed for the primary current to change direction from negative to positive, and vice versa, as shown in Fig. 1. This extended commutation time results in a loss of duty cycle on the secondary of the transformer, which decreases the conversion efficiency. Namely, to provide full power at the output, the secondary-side duty-cycle loss  $\Delta D$  must be compensated by reducing the turns ratio of the transformer. With a smaller transformer's turns ratio, the reflected output current into the primary is increased, which increases the primary-side conduction losses. In addition, since a smaller turns ratio of the transformer also increases the voltage stress on the secondary-side rectifiers, the rectifiers with a higher voltage rating that typically have higher conduction losses may be required.

Another major limitation of the conventional FB ZVS converter in Fig. 1 is a severe parasitic ringing at the secondary side of the transformer caused by the resonance of the rectifier's junction capacitance with the leakage inductance of the transformer and/or the external inductance during the turn-off of a rectifier. To control the ringing, a snubber circuit is required. If a conventional RC or RCD snubber is used, the conversion efficiency of the circuit may be significantly degraded.

A number of techniques have been proposed to optimize the performance of the FB ZVS converter by extending its ZVS range without the loss of duty cycle and/or secondary-side ringing [5]-[10]. Specifically, in [5] and [8], techniques that virtually eliminate secondary-side ringing in the FB ZVS converters that use an increased value of the leakage inductance of the transformer and/or external inductance to extend the ZVS range are proposed. The approach described in [5] employs an active snubber on the secondary side that requires synchronization between primary switches and an active-snubber switch, which increases the complexity and cost of the circuit. Much simpler and cost-effective approach that employs only two additional clamp diodes on the primary side is described in [8]. In addition, to achieve virtually full-range ZVS without an unreasonably large external inductance, [8] proposes a design optimization approach that besides the energy stored in the external inductor also utilizes energy stored in the magnetizing inductance of the transformer. It should be noted that the techniques described in [5] and [8] do not directly deal with the secondary-side duty-cycle-loss issue.

Techniques that can extend the ZVS range of the FB ZVS-PWM converter without significant duty-cycle loss are described in [6], [7], [9], and [10]. In [6], the ZVS range of the leading-leg switches in the FB ZVS-PWM converter in Fig. 1 is extended to lower load currents without a significant increase of the circulating energy and loss of duty cycle by using a saturable external inductor instead of a linear inductor. If the saturable inductor is designed so that it saturates at higher load currents, the inductor will not store excessive energy at high loads and it will commutate the primary current

in a shorter time than the linear inductor, which will reduce the secondary-side duty-cycle loss. At the same time, at low load currents, when the inductor is not saturated, it will have sufficiently high inductance to store enough energy to provide ZVS of the leading-leg switches even at very light loads. While it was demonstrated that a properly designed saturable inductor can improve the performance of the FB ZVS-PWM converter, the circuit requires a relatively large-size magnetic core to implement the inductor, which increases the cost of the circuit. Generally, a larger core is required to eliminate the thermal problem that is created by excessive core loss, since the saturable core is placed in the primary circuit and its flux swings between the positive and negative saturation levels.

In the approaches proposed in [7], [9], and [10], full-range ZVS of the primary switches is achieved by utilizing energy stored in inductive components of an auxiliary circuit. Since the auxiliary circuit is decoupled from the load, i.e., the load current does not flow through the auxiliary circuit, the extended ZVS range can be obtained with a minimal duty-cycle loss and secondary-side parasitic ringing. In the approach described and analyzed in [7] and [10], the auxiliary circuit comprises of a pair of inductors that are connected between the mid-point of the bridge legs and a mid-point of an input-voltage capacitive divider, whereas in the approach described in [9], the energy stored in the magnetizing inductance of an auxiliary transformer is used to extend the ZVS range. While in the proposed FB ZVS-PWM converters the energy available for ZVS increases as the input voltage increases, which is the desirable direction of change since more energy is required to achieve ZVS at higher input voltages, the stored energy in the proposed FB ZVS converters is independent of load. As a result, the proposed FB ZVS-PWM converters cannot optimally resolve the trade-off between power-loss savings brought about by full-load-range ZVS and power losses of the auxiliary circuit. Ideally, the auxiliary circuit needs to provide very little energy, if any, at full load because the full-load current stores enough energy in the converter's inductive components to achieve a complete ZVS of all switches. As the load current decreases, the auxiliary circuit needs to provide progressively more ZVS energy, with the maximum energy required at no load.

In this paper, a FB ZVS-PWM converter that features this kind of adaptive energy storage in the auxiliary circuit is described. This constant-frequency, FB ZVS converter employs a coupled inductor on the primary side to achieve ZVS in a wide range of load current and input voltage with reduced circulating energy and conduction losses. Because, in the proposed circuit, the energy required to create ZVS conditions does not need to be stored in the leakage inductance, the leakage inductance of the transformer can be minimized. This virtually eliminates the duty cycle loss and also significantly reduces the energy of the secondary-side ringing caused by a resonance between the leakage inductance and junction capacitance of the rectifier. As a result, the proposed circuit exhibits increased conversion efficiency.

## II. NEW FB ZVS CONVERTER WITH COUPLED INDUCTOR

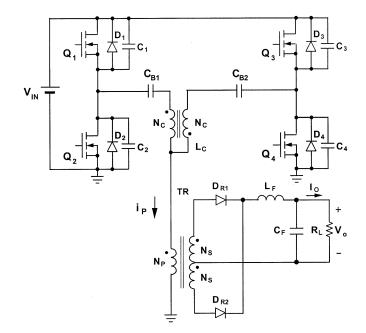

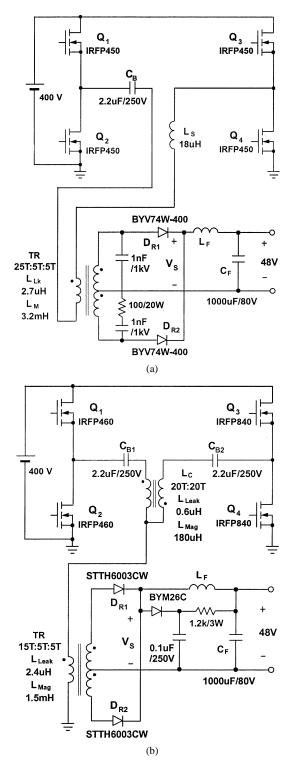

Fig. 2 shows a circuit diagram of the proposed isolated, dc/dc FB ZVS converter that employs a coupled inductor on the pri-

Fig. 2. Proposed full-bridge ZVS converter with coupled inductor.

mary side to extend the ZVS range of the primary switches with a minimum circulating energy and conduction loss. The primary side of the converter consists of two bridge legs  $Q_1$ - $Q_2$  and  $Q_3-Q_4$  connected through two capacitors  $C_{B1}$  and  $C_{B2}$  to the series connection of coupled inductor L<sub>C</sub> and transformer TR. The two primary side capacitors are used to prevent the saturation of the coupled inductor and transformer cores by blocking the flow of any dc current through  $L_C$  and TR. Generally these capacitors are selected large enough so that their voltages are approximately constant during a switching cycle. To regulate the output voltage against load and/or input voltage changes at a constant switching frequency, the circuit requires a phase-shift control. It should be noted that in Fig. 2, the output side of the converter is implemented with a full-wave rectifier with a tapped secondary. However, any other implementation of the secondary side rectification stage is possible.

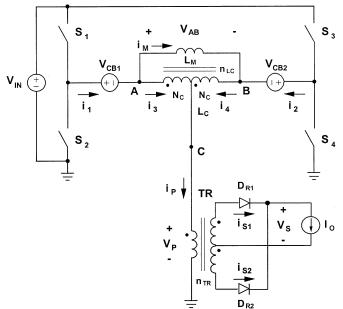

To facilitate the explanation of operation of the circuit in Fig. 2, Fig. 3 shows its simplified circuit diagram. In the simplified circuit, it is assumed that the inductance of output filter  $L_F$  is large enough so that during a switching cycle the output filter can be modeled as a constant current source with a magnitude equal to output current  $I_O$ . Also, it is assumed that the capacitance of blocking capacitors  $C_{B1}$  and  $C_{B2}$  is large enough so that the capacitance of blocking capacitors  $C_{B1}$  and  $C_{B2}$  is large enough so that the capacitors can be modeled as constant voltage sources. Because the average voltages of the coupled inductor windings and the transformer windings during a switching cycle are zero and the pair of switches in each bridge leg operate with 50% duty cycle, the magnitude of voltage sources  $V_{CB1}$  and  $V_{CB2}$  in Fig. 3 are equal to  $V_{IN}/2$ , i.e.,  $V_{CB1} = V_{CB2} = V_{IN}/2$ .

To further simplify the analysis, it is also assumed that the resistance of conducting semiconductor switches is zero, whereas the resistance of the nonconducting switches is infinite. In addition, the leakage inductances of coupled inductor  $L_C$  and transformer TR, as well as the magnetizing inductance of transformer TR are neglected because their effect on the

Fig. 3. Simplified circuit diagram of proposed converter showing reference directions of currents and voltages.

operation of the converter is negligible. The magnetizing inductance of coupled inductor  $L_{\rm C}$  and output capacitances  $C_1-C_4$  of primary switches are not neglected in this analysis since they play a major roll in the operation of the circuit. In Fig. 3, coupled inductor  $L_{\rm C}$  is modeled as an ideal transformer with turns ratio  $n_{\rm LC}=1$  and with parallel magnetizing inductance  $L_{\rm M}$  connected across the windings. The number of turns of each of the windings of  $L_{\rm C}$  is  $N_{\rm C}.$

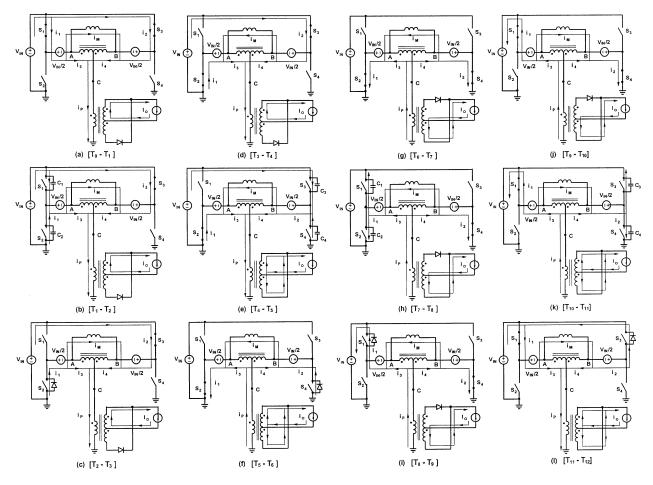

Finally, to further facilitate the analysis, Fig. 4 shows the topological stages of the converter during a switching cycle, whereas Fig. 5 shows the key waveforms. As shown in Fig. 5, at time  $t = T_O$ , switch  $S_1$  in  $S_1$ -S<sub>2</sub> leg and switch  $S_3$  in  $S_3-S_4$  leg are closed and currents  $i_1$  and  $i_2$  flow through the corresponding switch, blocking capacitor, and winding of coupled inductor L<sub>C</sub> into the primary of transformer TR, as can be seen from the equivalent circuit in Fig. 4(a). At the same time, output current  $I_{\rm O}$  flows through the upper secondary of the transformer so that primary current  $i_P = i_1 + i_2 = I_O/n_{TR}$ , where  $n_{TR} = N_P/N_S$  is the turns ratio of the transformer,  $N_{\rm P}$  is the number of primary-winding turns, and  $N_{\rm S}$  is the number of secondary-winding turns. From Fig. 4(a), it can be seen that during this topological stage voltage  $v_{AB}$  must be zero since voltage sources  $\mathrm{V}_{\mathrm{CB1}}$  and  $\mathrm{V}_{\mathrm{CB2}}$  are connected in opposition through closed switches  $S_1$  and  $S_3$ . Furthermore, because of the coupled inductor winding orientation [dot positions in Fig. 4(a)],  $v_{AB} = v_{AC} + v_{CB} = 0$  can only be maintained if the voltages across the coupled inductor windings are zero, i.e., only if  $v_{AC} = v_{CB} = 0$ . Therefore, since in this topological stage the voltage potential of points A, B, and C in Fig. 4(a) must be the same, primary voltage  $v_P = V_{IN} - V_{IN}/2 = V_{IN}/2$ , as shown in Fig. 5(j). It also should be noted that in this topological stage, magnetizing current of the coupled inductor i<sub>M</sub> is constant because  $v_{\rm AC}=v_{\rm CB}=0,$  i.e., the voltage across the windings of  $L_{\rm C}$  is

Fig. 4. Topological stages of proposed converter power stage.

zero, as illustrated in Fig. 5(i). In addition, because the turns ratio of the windings of  $L_C$  is unity  $(n_{LC} = 1)$ , current  $i_3$  flowing through winding AC is equal to current  $i_4$  flowing through winding BC, i.e.,  $i_3 = i_4$ . Finally, from Fig. 3, it can be seen that  $i_1 = i_P/2 + i_M$  and  $i_2 = i_P/2 - i_M$ .

When at  $t = T_1$ , switch  $S_1$  is turned off, current  $i_1$  is diverted from the transistor of switch  $S_1$  to its output capacitance  $C_1$ , as shown in Fig. 4(b). In this topological stage, current  $i_1$ charges capacitor  $C_1$  and discharges capacitor  $C_2$  at the same rate since the sum of the capacitor voltages is equal to constant voltage  $V_{IN}$ , as illustrated in Fig. 5(e) and (f). As a result, the potential of point A starts decreasing causing a decrease of voltages  $v_{AB}$  and  $v_{P}$ . Namely, voltage  $v_{AB}$  decreases from zero toward negative  $\mathrm{V}_{\mathrm{IN}},$  whereas voltage  $\mathrm{v}_{\mathrm{P}}$  decreases from  $V_{IN}/2$  toward zero, as illustrated in Fig. 5(i) and (j). After capacitor  $\mathrm{C}_2$  is fully discharged, i.e., when voltage  $v_{\mathrm{S2}}$  reaches zero, current  $i_1$  starts flowing through antiparallel diode  $D_2$  of switch  $\mathrm{S}_2,$  as shown in Fig. 4(c). Due to negative voltage  $\mathrm{V}_\mathrm{IN}$ applied across winding AB of coupled inductor L<sub>C</sub>, its magnetizing current  $i_M$  decreases with a rate of  $V_{IN}/L_M$ . Since during this topological stage primary current ip does not change, i.e., it stays constant at  $I_O/n_{TR}$ , current  $i_1 = i_P/2 + i_M$  decreases while current  $i_2 = i_P/2 - i_M/2$  increases at the same rate. To achieve zero-voltage turn-on of switch  $S_2$ , it is necessary to turn-on switch  $S_2$  while its antiparallel diode  $D_2$  is conducting. In Fig. 5, switch  $\mathrm{S}_2$  is turned on immediately after voltage  $v_{\mathrm{S}_2}$  has fallen to zero.

Magnetizing current  $i_M$  reaches zero at  $t = T_3$  and it continues to increase in the negative direction, as shown in Fig. 4(d). As a result, current  $i_1$  continues to decrease, whereas current  $i_2$ continues to increase, as seen from waveforms (m) and (n) in Fig. 5. At  $t = T_4$ , switch  $S_3$  is turned off so that current  $i_2$  is diverted from the transistor of switch S3 to its output capacitance  $C_3$ , as shown in Fig. 4(e). Because during this transition  $C_3$  is charging, while  $C_4$  is discharging at the same rate, voltage  $v_{S3}$ increases from zero toward  $V_{IN}$ , whereas voltage  $v_{S4}$  decreases from  $V_{IN}$  to zero, as illustrated in Fig. 5(g) and (h). Since, during this topological stage, the potential of point B decreases from  $V_{IN}/2$  toward  $-V_{IN}/2$ , while the potential of point A is constant at  $-V_{IN}/2$ , voltage  $v_{AB}$  increases from  $-V_{IN}$  toward zero. At the same time, primary voltage  $v_{\rm P}$  increases in the negative direction from zero to  $-V_{IN}/2$  forcing the commutation of the load current from the upper secondary to the lower secondary. If the interconnect inductances and the leakage inductances of transformer TR and coupled inductor L<sub>C</sub> were zero, this commutation would be instantaneous. However, due to the inevitable existence of various parasitic inductances on both the primary and secondary side, the commutation of the load current from one secondary to the other when the primary voltage changes sign is not instantaneous, as shown in Fig. 5. In fact,

Fig. 5. Key waveforms of proposed converter power stage.

when primary voltage  $v_{\rm P}$  becomes negative, the load current is carried by both secondary windings, as shown in Fig. 4(e), i.e., the transformer windings are effectively shorted. Because, during this commutation period, current in the upper secondary  $i_{\rm S1}$  decreases, primary current  $i_{\rm P} = (i_{\rm S1} - i_{\rm S2})/n_{\rm TR}$  changes direction at the moment the current in the lower secondary  $i_{\rm S2}$  becomes larger than current in the upper secondary  $i_{\rm S1}$ . At  $t=T_6$ , the load current completes the commutation from the upper to the lower secondary, as shown in Fig. 4(g). During the topological stage in Fig. 4(g), currents  $i_{\rm M}, i_{\rm P}, i_1$ , and  $i_2$  are constant and flow in the negative direction. To achieve ZVS of switch  $S_4$ , it is necessary to turn on switch  $S_4$  while current  $i_2$  is positive, i.e., while it still flows through antiparallel diode  $D_4$  of switch  $S_4$ . In Fig. 5, switch  $S_4$  is turned on immediately after  $t=T_5$ , i.e., immediately after voltage  $v_{\rm S4}$  falls to zero.

The second half of a switching cycle starts at  $t=T_7$  when switch  $S_2$  is turned off, which initiates the charging of capacitance  $C_2$  of switch  $S_2$  and discharging of capacitance  $C_1$  of switch  $S_1$ , as shown in Fig. 4(h). During this switching transition voltage  $v_{AB}$  increases from zero toward  $V_{IN}$ , while primary voltage  $v_P$  increases from  $-V_{IN}/2$  to zero. This topological stage ends at  $t=T_8$  when voltage  $v_{S1}$  across switch  $S_1$  reaches zero and antiparallel diode  $D_1$  of switch  $S_1$  starts conducting current  $i_1$ , as shown in Fig. 4(i). To achieve ZVS of switch  $S_1$ , switch  $S_1$  needs to be turned on while diode  $D_1$  is conducting.

In Fig. 5, switch  $S_1$  is turned on immediately after voltage  $v_{S1}$ has fallen to zero. Because, after switch S<sub>2</sub> is turned off, voltage  $v_{AB}$  starts increasing, magnetizing current  $i_M$  starts increasing as well, as can be seen from Fig. 5(1). From instant  $t = T_8$ , this increase is linear since constant voltage  $v_{AB} = V_{IN}$  is applied across magnetizing inductance  $L_M$ . At  $t = T_9$ , current  $i_{\rm M}$  becomes positive, as shown in both Fig. 4(j) and Fig. 5(l). Finally, at  $t = T_{10}$ , switch  $S_4$  is turned off, which initiates switching transition in the  $S_3$ - $S_4$  leg. Because during this transition capacitor  $C_3$  is discharging and capacitor  $C_4$  is charging, the potential of point B is increasing from  $-V_{IN}/2$  to  $V_{IN}/2$ . Since during this time, the potential of point A is constant at  $V_{IN}/2$ , voltage  $v_{AB}$  is decreasing from  $V_{IN}$  toward zero, while primary voltage  $v_P$  is increasing from zero toward  $V_{IN}/2$ . As a result, positive primary voltage forces the commutation of the load current from the lower secondary to the upper secondary, as shown in Fig. 4(k). At  $t = T_{11}$ , the capacitance of switch  $S_3$  is fully discharged, and current i2 starts flowing through antiparallel diode  $D_3$  of switch  $S_3$ , as shown in Fig. 4(1). To achieve ZVS, switch  $S_3$  is turned on shortly after  $D_3$  starts conducting. During the topological stage in Fig. 4(1), primary current  $i_{\rm P}$ , current i1, and current i2 continue to increase from negative values toward positive, as seen from waveforms in Fig. 5(k), (m), and (n). Finally, at  $t = T_{12}$ , the commutation of the  $S_3-S_4$  leg is completed so that the circuit enters the same topological stage as shown in Fig. 4(a), awaiting the next switching cycle to be initiated by the controller.

It should be noted that, in the proposed circuit, the value of the magnetizing inductance of coupled inductor  $L_{\rm C}$  has no effect on commutation time of the primary current from one direction to the other. This commutation time is proportional to the sum of leakage the inductances of transformer TR and coupled inductor  $L_{\rm C}$ , because they are effectively in series with the power path. Therefore, to minimize the secondary-side duty-cycle loss and optimize the performance of the circuit, it is necessary to minimize the leakage inductances of transformer TR and coupled inductor  $L_{\rm C}$ . The minimization of the leakage inductances also minimizes the secondary-side parasitic-ringing energy, which further improves the circuit performance.

## **III. DESIGN GUIDELINES**

As can be seen from the waveforms in Fig. 5, the commutation of the switches in the  $S_1$ - $S_2$  leg is initiated when current  $i_1 = i_P/2 + i_M$  is maximum, i.e., when  $i_1 = (I_O/n_{TR})/2 + I_M$ . Also, the commutation of the switches in the  $S_3$ - $S_4$  leg is initiated when current  $i_2 = i_P/2 - i_M$  is maximum, i.e., when  $i_2 = (I_O/n_{TR})/2 + I_M$ . Therefore, in the proposed circuit, all primary switches are commutated with the same magnitude current. However, the charging and discharging of the capacitances of switches  $S_1$  and  $S_2$  is done by the sum of the energy stored in the output filter inductor, which is proportional to  $[I_O/(2n_{TR})]^2$ , and the energy stored in the magnetizing inductance of coupled inductor  $L_C$ , which is proportional to  $(I_M)^2$ . On the other hand, the charging and discharging of the capacitances of switches  $S_3$  and  $S_4$  are done by the sum of the energy stored in the leakage inductance of the transformer and the energy stored in the magnetizing inductance of coupled inductor  $L_C.$  Therefore, switches in the  $S_1\mathchar`-S_2$  leg can achieve ZVS in a

wide range of input voltage and load current even without assistance from the energy stored in magnetizing inductance  $L_{\rm M}$ of coupled inductor  $L_{\rm C}$  since plenty of energy is available from filter inductor  $L_{\rm F}$ . However, ZVS of the switches in the  $S_3-S_4$ leg is entirely dependent on the energy stored in the magnetizing inductance of coupled inductor  $L_{\rm C}$  since, for optimal performance, it is desirable to minimize the leakage inductance of the transformer so that the secondary-side duty-cycle loss and the energy of the secondary-side parasitic ringing is also minimized. Generally, to achieve ZVS of all bridge switches in the entire input-voltage and load range, it is necessary to satisfy

$$\frac{1}{2}L_{M}I_{M}^{2} \ge CV_{IN}^{2} + \frac{1}{2}C_{LC}V_{IN}^{2} + \frac{1}{2}C_{TR}\left(\frac{V_{IN}}{2}\right)^{2} \quad (1)$$

where  $C = C_3 = C_4$  is the capacitance across primary switches  $S_3$  and  $S_4$ ,  $C_{LC}$  is the interwinding capacitance of coupled inductor  $L_C$ , and  $C_{TR}$  is the capacitance seen across the primary of transformer TR that includes interwinding capacitance of the transformer and any reflected capacitance of the secondary-side circuit. If capacitances  $C_{LC}$  and  $C_{TR}$  are neglected, (1) simplifies to

$$L_M I_M^2 \ge 2 C V_{IN}^2.$$

(2)

As can be seen from (2), if the value of inductor  $L_M$  is selected so that ZVS is achieved at no load and maximum input voltage  $V_{IN(max)}$ , ZVS is achieved in the entire load and input-voltage range.

The value of inductor  $L_M$  required to achieve ZVS at no load can be calculated by observing the waveform during time interval  $T_8-T_{10}$  in Fig. 5. Magnetizing current  $i_M$  changes linearly from maximum negative value  $I_M^- = -I_M$  to maximum positive value  $I_M^+ = I_M$ , i.e.,  $i_M$  changes for  $2I_M$ , due to a positive voltage of  $V_{IN}$  across the winding AB of inductor  $L_C$ . Since according to Fig. 5, the time interval  $T_8-T_{10}$  is approximately equal to  $(1-D)T_S/2$ , where D is duty cycle and  $T_S$  is a switching period,  $I_M$  can be calculated from

$$V_{IN} = L_{M} \frac{2I_{M}}{(1-D)\frac{T_{S}}{2}}$$

(3)

as

$$I_{\rm M} = \frac{(1-D)V_{\rm IN}}{4L_{\rm M}f_{\rm S}} \tag{4}$$

where  $f_S = 1/T_S$  is the switching frequency. Since at no load  $D \approx 0$  because the two bridge legs must be out of phase to reduce the volt-sec product across the primary winding, the ZVS condition at no load and high line from (2) and (4) is

$$L_{M} \left(\frac{V_{IN(max)}}{4L_{M}f_{S}}\right)^{2} \ge 2CV_{IN(max)}^{2}.$$

(5)

Finally, from (5), the value of  $L_{\rm M}$  required to maintain ZVS at no load and high line is

$$L_{\rm M} \le \frac{1}{32 {\rm Cf}_{\rm S}^2}.\tag{6}$$

As can be seen from Fig. 3, current  $i_M$  flowing through magnetizing inductance  $L_M$  introduces a current asymmetry in the two bridge legs, i.e.,  $i_1 = i_P/2 + i_M$  and  $i_2 = i_P/2 - i_M$ .

Fig. 6. Experimental 670 W: (a) conventional converter power stage and (b) proposed converter power stage with coupled inductor.

Therefore, in the proposed circuit, leg  $S_1-S_2$  always carries a higher current than the leg  $S_3-S_4$ , the difference being magnetizing current  $i_M$ . To simultaneously achieve ZVS at no load and minimize the bridge conduction loss in the proposed circuit in Fig. 2, it is necessary to select the maximum magnetizing inductance  $L_M$  determined from (6). Furthermore, if for such a selected magnetizing inductance, current  $i_2$  in the  $S_3-S_4$  leg is significantly lower than current  $i_1$  in the  $S_1-S_2$  leg, different

size switches can be selected for the two legs, which may reduce the cost of the implementation without sacrificing the circuit performance.

Finally, it should be noted that to achieve maximum efficiency improvement, the turns ratio of the transformer must be maximized. In fact, since the duty-cycle loss in the converter in Fig. 2 is negligible due to the minimized leakage inductance of the transformer, the converter can be designed with a larger turns ratio compared to a converter that uses the leakage inductance and/or external inductance to extend the ZVS range. Moreover, the minimized leakage inductance greatly reduces the secondary-side ringing between the leakage inductance of the transformer and the junction capacitance of the rectifier so that any residual parasitic ringing can be damped by a small snubber circuit as, for example, the RCD-snubber circuit shown in Fig. 6.

The control of the circuit in Fig. 2 is the same as the control of any other constant frequency FB ZVS converter. In fact, any of the integrated phase-shift controllers available on the market can be used implement the control of the proposed circuit. However, it should be noted that in the circuit in Fig. 2 the maximum output voltage is obtained when the bridge legs are operated in phase, which is the opposite from the behavior of the conventional FB ZVS converter shown in Fig. 1 that achieves the maximum output voltage when the bridge legs are switched out of phase. This difference in the control characteristic of the converter has a minor effect on the control-loop design since a simple control-signal inversion in the voltage control loop circumvents the problem.

It also should be noted that the proposed circuit in Fig. 2 can be implemented with any type of secondary-side rectifier. Specifically, it can also be implemented with a full-wave, full-bridge rectifier, or a current-doubler rectifier.

#### **IV. EXPERIMENTAL RESULTS**

The performance of the proposed circuit was verified on a 670-W experimental prototype operating at 116 kHz. The experimental converter was designed to operate from 400-V dc input and deliver 14 A from a 48-V output. The component values of the experimental circuit are shown in Fig. 6(b). The phase-shift control circuit was implemented using a UC3875 controller. For performance comparison purposes, an experimental prototype of the conventional FB ZVS converter shown in Fig. 6(a) was also built. The conventional FB ZVS converter was designed with an external inductance of 18  $\mu$ H in series with the primary winding of the transformer (25T:5T:5T) to achieve ZVS over a load range from 50% to 100%.

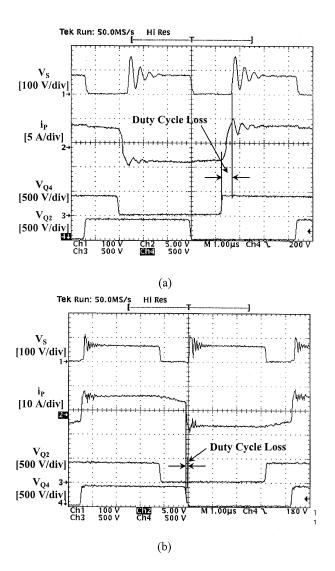

Fig. 7(a) and (b) show the oscillograms of key waveforms of the conventional FB ZVS converter and the proposed FB ZVS converter, respectively. As can be seen from Fig. 7(a), in the conventional FB ZVS converter the parasitic ringing caused by the external leakage inductance with the rectifier's junction capacitance is severe even with a snubber circuit which dissipates approximately 12 W. As shown in Fig. 6(a), snubber capacitance  $C_{snubber}$  is approximately 0.5 nF, since two capacitors (1 nF) in series. The snubber loss can be calculated as

$$P_{\text{snubber}} = C_{\text{snubber}} \times V_{\text{sec ondary}}^2 \times 2 \times f_{\text{S}}$$

$$= 0.5 \times 10^{-9} \times 320^2 \times 2 \times 116\,000 \cong 12\,[\text{W}] \quad (7)$$

Fig. 7. Measured key waveforms at  $P_{\rm O}=670$  W: (a) conventional FB ZVS converter and (b) proposed FB ZVS converter. From top to bottom: secondary voltage  $V_{\rm S}$ ; primary current  $i_{\rm P}$ ; drain-to-source voltage  $V_{\rm Q2}$  of  $Q_2$ ; drain-to-source voltage  $V_{\rm Q4}$  of  $Q_4$ . Time base:  $1\,\mu\,s/div.$

where  $V_{secondary}$  is the peak voltage across the secondary winding of transformer TR. Moreover, the duty cycle loss is approximately 0.5  $\mu$ s which is more than 18% of the secondary side duty cycle. As can be seen from the corresponding waveforms in Fig. 7(b), the proposed converter has a very small duty cycle loss (<0.1  $\mu$ s) as well as a very much reduced parasitic ringing because of a minimized leakage inductance of the transformer that is less than 3  $\mu$ H. The measured magnetizing inductance of coupled inductor L<sub>C</sub> is approximately 180  $\mu$ H.

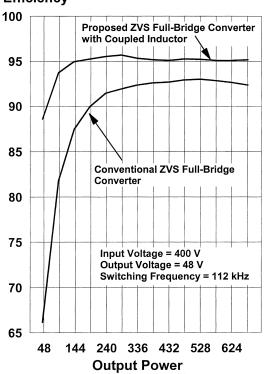

Fig. 8 shows the measured efficiencies of the conventional FB ZVS converter and the proposed FB ZVS converter as functions of output power. As can be seen from Fig. 8, the proposed converter shows a conversion efficiency improvement in the entire measured power range from 50 W to 670 W. Generally, the efficiency improvement is more pronounced at light loads where the conventional FB ZVS converter operates with hard switching. Specifically, at light loads, the efficiency improvement is more than 20%. At full load, the proposed circuit shows a efficiency improvement of approximately 3%, which translates into approximately 30% reduction of losses.

Fig. 8. Measured efficiencies of conventional FB ZVS converter and proposed FB ZVS converter as functions of output power.

## V. CONCLUSION

In this paper, a new isolated, constant-frequency, FB ZVS converter which employs a coupled inductor on the primary side to achieve ZVS in a wide range of load current and input voltage with reduced circulating energy and conduction losses has been described. Since this coupled inductor does not appear as a series inductance in the load current path, it does not cause a loss of duty cycle or severe voltage ringing across the output rectifiers. The operation and performance of the proposed circuit was verified on a 670-W (48-V/14-A) prototype. The measured efficiency improvement of the proposed circuit with respect to the conventional FB ZVS converter was 3% at full load and more than 20% at light loads. The ability of the proposed circuit to maintain a high efficiency at light loads makes the proposed converter particularly attractive in applications where a number of power converters connected in parallel share the load current so that each converter operates with a load which is a fraction of its full load.

### References

- O. D. Petterson and D. M. Divan, "Pseudo-resonant full bridge dc/dc converter," in *Proc. IEEE Power Electronics Spec. Conf.*, 1987, pp. 424–430.

- [2] R. A. Fisher, K. D. T. Ngo, and M. H. Kuo, "A 500 kHz, 250 W dc-dc converter with multiple outputs controlled by phase-shifted PWM and magnetic amplifiers," in *Proc. High Freq. Power Conv.*, May 1988, pp. 100–110.

- [3] L. H. Mweene, C. A. Wright, and M. F. Schlecht, "A 1 kW, 500 kHz front-end converter for a distributed power supply system," in *Proc. IEEE Appl. Power Electron. Conf. (APEC)*, 1989, pp. 423–432.

- [4] J. A. Sabaté, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zerovoltage-switched PWM converter," in *Proc. IEEE Appl. Power Electron.*

- Conf. (APEC), 1990, pp. 275–284.

[5] J. A. Sabaté, V. Vlatkovic, R. B. Ridley, and F. C. Lee, "High-voltage, high-power, ZVS, full-bridge PWM converter employing an active snubber," in *Proc. IEEE Appl. Power Electron. Conf. (APEC)*, 1991, pp. 158–163.

- [6] G. Hua, F. C. Lee, and M. M. Jovanović, "An improved full-bridge zerovoltage-switched PWM converter using a saturable inductor," in *Proc. IEEE Power Electron. Spec. Conf.*, 1991, pp. 189–194.

- [7] M. Nakaoka, S. Nagai, Y. J. Kim, Y. Ogino, and Y. Murakami, "The state-of-the art phase-shifted ZVS-PWM series & parallel resonant dc-dc power converters using internal parasitic circuit components and new digital control," in *Proc. IEEE PESC*'92, 1992, pp. 62–70.

- [8] R. Redl, L. Balogh, and D. W. Edwards, "Optimum ZVS full-bridge dc/dc converter with PWM phase-shift control: Analysis, design considerations, and experimental results," in *Proc. IEEE Appl. Power Electron. Conf. (APEC)*, 1994, pp. 159–165.

- [9] R. Ayyanar and N. Mohan, "Novel soft-switching dc-dc converter with full ZVS-range and reduced filter requirement—Part I: Regulated-output applications," *IEEE Trans. Power Electron.*, vol. 16, pp. 184–192, Mar. 2001.

- [10] P. K. Jain, W. Kang, H. Soin, and Y. Xi, "Analysis and design considerations of a load and line independent zero voltage switching full bridge DC/DC converter topology," *IEEE Trans. Power Electron.*, vol. 17, pp. 649–657, Sept. 2002.

**Yungtaek Jang** (S'92–M'95–SM'01) was born in Seoul, Korea. He received the B.S. degree from Yonsei University, Seoul, in 1982, and the M.S. and Ph.D. degrees from the University of Colorado, Boulder, in 1991 and 1995, respectively, all in electrical engineering.

From 1982 to 1988, he was a Design Engineer at Hyundai Engineering Co., Seoul. From 1995 to 1996, he was a Senior Engineer at Advanced Energy Industries, Inc., Fort Collins, CO. Since 1996, he has been a Senior Member of R&D Staff at the Power Elec-

tronics Laboratory, Delta Products Corporation, Research Triangle Park, NC (the U.S. subsidiary of Delta Electronics, Inc., Taiwan, R.O.C.). He holds 14 U.S. patents. His research interests include resonant power conversion, converter modeling, control techniques, and low harmonic rectification.

Dr. Jang received the IEEE TRANSACTIONS ON POWER ELECTRONICS Prize paper award for best paper published in 1996.

**Milan M. Jovanović** (F'01) was born in Belgrade, Serbia. He received the Dipl.Ing. degree in electrical engineering from the University of Belgrade.

Presently, he is the Vice President for Research and Development of Delta Products Corporation, Research Triangle Park, NC (the U.S. subsidiary of Delta Electronics, Inc., Taiwan, R.O.C.).

**Yu-Ming Chang** was born in Taiwan, R.O.C., on December 15, 1964. He received the M.A. and Ph.D. degrees from Cheng Kung University, Taiwan, in 1991 and 1998, respectively.

He is a Business Director of Telecom Power Business Unit, Delta Electronics Inc., Chungli, Taiwan. His interests include circuit topology innovation of power converters, control methodology, and packaging technologies.