## NANO EXPRESS Open Access

# A Novel Dopingless Fin-Shaped SiGe Channel TFET with Improved Performance

Shupeng Chen, Shulong Wang, Hongxia Liu, Tao Han, Haiwu Xie and Chen Chong

#### **Abstract**

In this paper, a dopingless fin-shaped SiGe channel TFET (DF-TFET) is proposed and studied. To form a high-efficiency dopingless line tunneling junction, a fin-shaped SiGe channel and a gate/source overlap are induced. Through these methods, the DF-TFET with high on-state current, switching ratio of 12 orders of magnitude and no obvious ambipolar effect can be obtained. High  $\kappa$  material stack gate dielectric is induced to improve the off-state leakage, interface characteristics and the reliability of DF-TFET. Moreover, by using the dopingless channel and fin structure, the difficulties of doping process and asymmetric gate overlap formation can be resolved. As a result, the structure of DF-TFET can possess good manufacture applicability and remarkably reduce footprint. The physical mechanism of device and the effect of parameters on performance are studied in this work. Finally, on-state current ( $l_{ON}$ ) of 58.8  $\mu$ A/ $\mu$ m, minimum subthreshold swing of 2.8 mV/dec (SS<sub>min</sub>), average subthreshold swing (SS<sub>avg</sub>) of 18.2 mV/dec can be obtained. With improved capacitance characteristics, cutoff frequency of 5.04 GHz and gain bandwidth product of 1.29 GHz can be obtained. With improved performance and robustness, DF-TFET can be a very attractive candidate for ultra-low-power applications.

Keywords: Tunnel FET, Dopingless, Fin-shaped channel, Line tunneling junction, Stack gate oxide

#### Introduction

With the scaling down of MOSFETs, the switching speed, high-frequency performance, density, cost and functionality of integrated circuits (ICs) are meet a great improvement [1]. But with the continuous progress of voltage scaling down, the unacceptable high-power consumption becomes a serious problem for modern ICs [1, 2]. Benefit from the band-to-band tunneling mechanism, tunnel FET (TFET) with steep SS and low-power consumption bring a new solution to this problem and attracted lots of attention [3–9]. But the applications of conventional silicon-based TFETs are limited by the considerably low on-state current  $(I_{\rm ON})$ , low switching ratio, severe ambipolar effect and large average subthreshold swing (SS) [1, 7]. To improve the performance of TFETs, applications of new structures and new materials on TFETs have been

proposed in recent years. For example, TFETs with tunneling rate enhanced layer are proposed in recent years [5, 10, 11]. With this layer, the effective length of tunneling path is reduced and results to an obvious tunneling rate enhancement. Moreover, TFETs with improved gate structure are studied by many research groups [12-20]. The concept of line tunneling is introduced in L-TFET [17–19]. As a result,  $SS_{avg}$  of 42.8 mV/decade and  $I_{ON}$ of  $10^{-6}$ A/µm can be achieved by L-TFET. To further improve the performance of TFETs, an improved TG-TFET with T-shaped overlap and dual source is reported [20, 21]. As a result, the  $I_{ON}$  of TG-TFET reaches 81  $\mu$ A/ μm. To further improve the device performance, high requirement on doping profile of the tunneling junction is required. Foundry engineers need to create a ultrasteep abrupt junction which has only several nanometers thick, and this is very difficult to achieve. In order to avoid this difficulty, the dopingless TFET (DL-TFET) on thin intrinsic semiconductor film using charge plasma concept is reported by research groups [22, 23]. In DL-TFET, the manufacture difficulty can be significantly

\*Correspondence: slwang@xidian.edu.cn; hxliu@mail.xidian.edu.cn School of Microelectronics, Key Laboratory of Wide Band-Gap Semiconductor Materials and Devices of Education, Xidian University, Xi'an 710071, China

© The Author(s) 2020. **Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 2 of 8

reduced by removing the ultra-steep abrupt junction. The performance degradation induced by random dopant fluctuations can be avoided. Moreover, the fabrication of the DL-TFET does not demand high thermal budgets for creating the source and drain, which opens up the possibility of realizing TFETs on other substrates such as single crystal silicon on glass. As a result, the SS of DL-TFET has been greatly improved. However, due to the low efficiency of point tunneling junction, the current of DL-TFET is not high enough, which is difficult to meet the ever-increasing requirements of modern circuit applications.

In this paper, a novel dopingless fin-shaped SiGe channel TFET (DF-TFET) is proposed and studied. To improve performance and robustness of the device, line tunneling junction and SiGe material are applied to DF-TFET. Meanwhile, gate metal work function is optimized to further improve the tunneling rate. Moreover, the dopingless channel reduced the manufacture process difficulty while the fin structure makes the asymmetric gate/backgate manufacture applicable. As a result, on-state current ( $I_{ON}$ ) of 58.8 $\mu$ A/ $\mu$ m, off-state leakage current ( $I_{OFF}$ ) near  $10^{-11} \mu A/\mu m$ , average subthreshold swing (SS<sub>avg</sub>) of 18.2 mV/dec and minimum subthreshold swing (SS<sub>min</sub>) of 2.8 mV/dec can be reached by DF-TFET. With relatively small gate capacitance  $(C_{gg})$  and gate to drain capacitance ( $C_{\rm gd}$ ), good analog/ $R\tilde{F}$  performance can be obtained. Finally, the cutoff frequency  $(f_T)$  reached 5.04 GHz and gain bandwidth product (GBW) reached 1.29 GHz.

The structures of this paper are as follows: "Device Structure and Simulation Method" section shows the TCAD simulation methods of this work. The structure and the parameter of DF-TFET are introduced. The differences and advantages of DF-TFET compared with DL-TFET and TG-TFET are illustrated. The mechanism, characteristic and analog/RF performance of DF-TFET are discussed in "Results and Discussion" section. A performance comparison between DF-TFET, DL-TFET and TG-TFET is carried out in this section. Moreover, the influence of the device parameters on performance and DF-TFET's typical RF parameters is studied in this section. In order to further understand the potential of DF-TFETs in ultra-low-power applications, comparisons of electrical characteristics among different TFETs and DF-TFETs under low voltage bias were carried out.

### **Device Structure and Simulation Method**

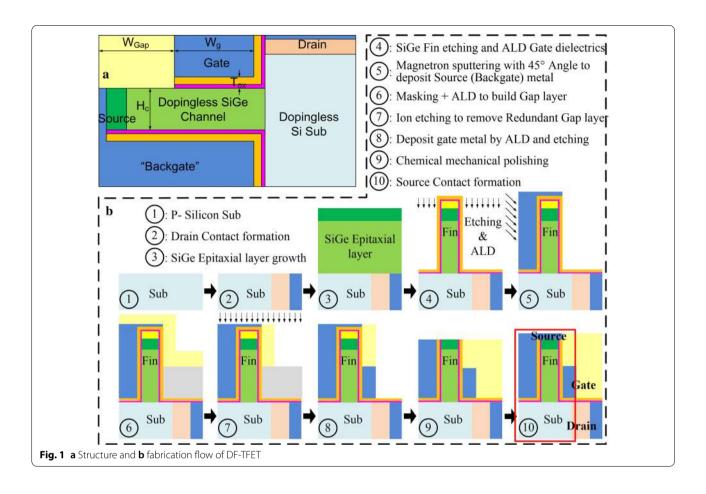

The proposed structure of DF-TFET is illustrated in Fig. 1a. To improve the device performance, line tunneling junction is applied to the dopingless fin-shaped SiGe channel by charge plasma concept [24, 25]. It is known that gate dielectric thickness can significantly

affect the tunneling current. This is because in the result of the WKB approximation [26], as shown in Eq. (1), the tunneling probability depends on effective screening length  $(\lambda)$ , effective carrier mass  $(m^*)$ , energy band gap  $(E_{\rm g})$  and effective screening energy window  $(\Delta \Phi)$ .

$$T_{\rm WKB} \approx \exp\left(-\frac{4\lambda\sqrt{2m^*}\sqrt{E_{\rm g}^3}}{3q\hbar(E_{\rm g} + \Delta\Phi)}\right)$$

(1)

Reducing the thickness of the gate dielectric or using a high  $\kappa$  dielectric will reduce  $\lambda$  and increase  $\Delta \Phi$ , which will cause a tunneling probability increase exponentially. Thus, using high  $\kappa$  dielectrics and reducing the dielectric thickness can significantly increase the on-state current of TFET. But the small dielectric thickness and interface quality issues of high  $\kappa$  dielectrics will cause serious reliability problems. Thus, a stack gate dielectric of 0.5 nm of Al<sub>2</sub>O<sub>3</sub> and 2.0 nm of HfO<sub>2</sub> is set to guarantee a good interface quality [27-29], which can significantly reduce the leakage current and improve the reliability of gate dielectric. The source electrode is located on the top of the fin structure. At the same time, it is also next to one side of the fin and works as a "backgate" to apply a zero bias. By using gate and source electrode with different metal work functions, a line tunneling junction can be formed in the dopingless fin-shaped SiGe channel by charge plasma concept. The band-to-band tunneling (BTBT) direction is perpendicular to the channel/ gate surface. This can help increase  $I_{ON}$  by improving the effective tunneling junction area.

High switching ratio  $(I_{\rm ON}/I_{\rm OFF})$  can be obtained due to the large on-state current  $(I_{\rm ON})$  and small off-state current  $(I_{\rm OFF})$  provided by the line tunneling junction. Furthermore, the application of a fin structure in DF-TFET can remarkably reduce the footprint compared to the planer line tunneling TFET [30, 31]. Figure 1b shows an available fabrication flow to form the structure of DF-TFET. Table 1 shows the main process parameters of DF-TFET. Finally, without the difficulty to make a steep and uniform abrupt p—n junction, good device performance and robustness can be achieved.

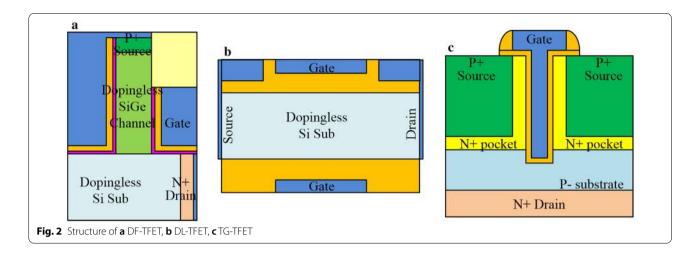

To better understand of the differences and advantages of DF-TFET, DL-TFET and TG-TFET, Fig. 2 shows the structure of these three devices. With line tunneling junction, L-TFET and TG-TFET expected to obtain high on-state current. But experimental results show that the actual performance of L-TFET is not as high as expected [18, 19]. One of the most important reasons is the difficulty on form a steep and uniform abrupt p—n junction with perfect interface characteristics. Based on the structure of L-TFET, TG-TFET makes

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 3 of 8

**Table 1 Main parameters of DF-TFET**

| DF-TFET                            |

|------------------------------------|

| 30 nm                              |

| 15 nm                              |

| 2.5 nm                             |

| 5 nm                               |

| 5.1 eV                             |

| $1 \times 10^{20}  \text{cm}^{-3}$ |

|                                    |

a great improvement on  $I_{\rm ON}$ . But TG-TFET is still facing the difficulty on forming a perfect abrupt p-n junction. Thus, to obtain the desirable good performance, a steep and uniform abrupt p-n junction which has only several nanometers thick should be obtained, but it is very difficult to realize in the manufacture process. By using a dopingless channel, DL-TFET can avoid this problem and bring better interface quality near tunneling junction. However, compared to line tunneling TFETs [16–21] with abrupt p-n junctions, simulation result shows that the  $I_{\rm ON}$  of DL-TFET is relatively low

[22, 23]. For further improvement, the DF-TFET is proposed and studied in this work.

Simulation of DF-TFET is carried out in Silvaco Atlas TCAD tools. Non-local BTBT model is introduced in this simulation to bring the energy band spatial variation into account, which can help to improve the accuracy of the BTBT tunneling process. Lombardi mobility model is considered to make the channel mobility accurate. Band-gap narrowing model is taken into account to fit the heavy doped ohmic contact regions, and Shockley–Read–Hall recombination model is taken into consideration in this paper, too.

#### **Results and Discussion**

# Mechanism and Comparison of DF-TFET, DL-TFET and TG-TFET

Figure 3a shows the transfer characteristics comparison of DF-TFET, DL-TFET and TG-TFET. Benefit from the line tunneling junction in the fin-shaped SiGe channel, DF-TFET reaches an on-state current ( $I_{\rm ON}$ ) of 58.8  $\mu$ A/  $\mu$ m and achieves a large switching ratio of over 12 orders of magnitude where no obvious ambipolar effect occurs. Furthermore, minimum subthreshold swing (SS<sub>min</sub>) of

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 4 of 8

2.8 mV/dec and average subthreshold swing (SS $_{\rm avg}$ ) of 18.2 mV/dec are obtained. As a result, DF-TFET has obvious improvement in  $I_{\rm ON}$  compared to DL-TFET and subthreshold swing compared to TG-TFET.  $I_{\rm ON}$  of DF-TFET is more than one order of magnitude larger than DL-TFET at  $V_{\rm DS}\!=\!V_{\rm GS}\!=\!1$  V. Figure 3b shows the energy band condition of DF-TFET and illustrates the formation

of tunneling window in fin-shaped channel. The red dotted line in the inset of Fig. 3b shows the position where the energy band curve is obtained.

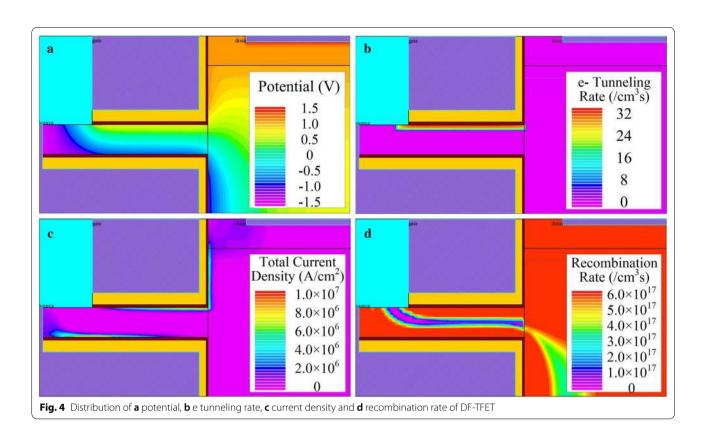

The distribution of important physical quantity in DF-TFET's tunneling process is shown in Fig. 4, which includes the distribution of (a) potential, (b) e tunneling rate, (c) total current density and (d) recombination rate in an on-state work condition. In Fig. 4a, a clear potential gradient perpendicular to the gate/channel interface can be observed. Thus, a huge potential difference is generated in fin-shaped channel and this will modulate the concentration of electrons and holes on both sides of fin channel. At the same time, a steep energy band bending can be formed in the fin-shaped channel. As a result, a line tunneling junction parallel to the gate/channel interface can be formed. Figure 4b shows the e-tunneling rate in the fin structure channel. The peak value of e-tunneling rate is uniformly distributed near the gate/channel interface and parallel to the surface. This proves that the line tunneling junction is parallel to the gate/channel interface. Figure 4c shows the current path in DF-TFET. The valence band electrons from the backgate/channel side are tunneling to the conduction band near the gate/ channel side. Under the influence of gate voltage and drain voltage, electrons move along the fin channel to the drain electrode. In this way, a tunneling current path is formed in DF-TFET. Figure 4d shows the recombination rate distribution in DF-TFET; this can illustrate the location of the tunneling junction more obviously. The purple strip in the SiGe fin channel can represent the location of the tunneling junction.

### DC Characteristics with Different Parameters and Analog/ RF Performance

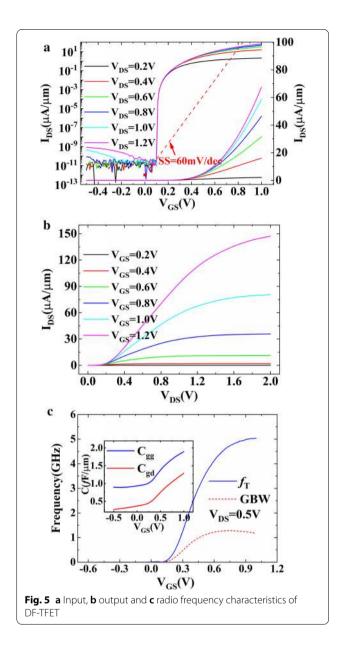

Figure 5a, b shows the input and output characteristics of DF-TFET under different biases. The increasing of

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 5 of 8

$V_{\rm DS}$  has little effect on subthreshold swing characteristics, but  $I_{\rm ON}$  will have a linear growth while  $V_{\rm DS}$  increases from 0.2 to 1.2 V (at  $V_{\rm GS}\!=\!1.0$  V). Figure 5c shows the cutoff frequency ( $f_{\rm T}$ ) and gain bandwidth product (GBW) calculated by Eqs. (2) and (3). Result shows that a cutoff frequency of 5.04 GHz and a gain bandwidth product of 1.29 GHz can be obtained.

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi C_{\rm gs} \sqrt{1 + 2C_{\rm gd}/C_{\rm gs}}} \approx \frac{g_{\rm m}}{2\pi \left(C_{\rm gs} + C_{\rm gd}\right)} = \frac{g_{\rm m}}{2\pi C_{\rm gg}}$$

(2)

$$GBW = g_{\rm m}/2\pi 10C_{\rm gd} \tag{3}$$

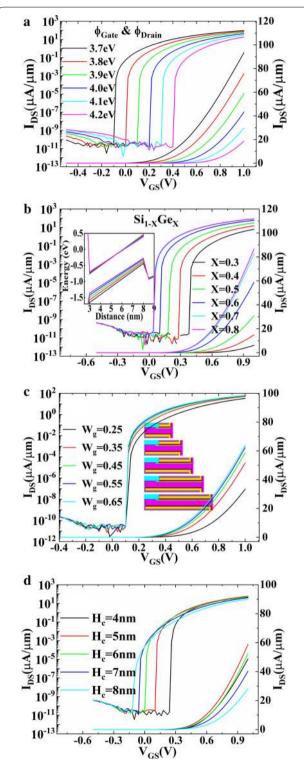

Figure 6a shows the effect of gate work function ( $\phi_{\rm Gate}$ ) and drain work function ( $\phi_{\rm Drain}$ ) on transfer characteristics of DF-TFET. With the increasing work function, the transfer characteristic curve shifts toward the positive direction. As the work function varies from 3.7 to 4.2 eV, the  $V_{\rm th}$  increases linearly from 0 to 0.5 V while the  $I_{\rm ON}$  decreases linearly from 93.4 to 18.6  $\mu$ A/ $\mu$ m. This makes it possible to adjust  $V_{\rm th}$  to apply to different application requirements. Figure 6b shows the effect of composition ratio X of  ${\rm Si}_{1-X}{\rm Ge}_X$ . The increase in germanium composition leads to the decreasing of energy band gap and the increasing of tunneling window, as shown in the

inset of Fig. 6b. Finally, results in the  $I_{\rm ON}$  increase and transfer characteristic curve translates toward the negative direction. However, when  $X\!>\!0.7$ , both the transfer characteristic curve and the  $I_{\rm ON}$  have little change with the increasing X. This is because the channel energy band structure becomes insensitive to X when  $X\!>\!0.7$ , as shown in Fig. 6b inset. Figure 6c, d shows the effect of gate length  $(W_{\rm g})$  and channel thickness  $(H_{\rm c})$  on transfer characteristics. The inset of Fig. 6c shows the dimensions of device channel under different  $W_{\rm g}$ . It is not difficult to observe from Fig. 6d that DF-TFET will suffer  $I_{\rm ON}$  decrease when  $H_{\rm c}$  becomes both too small and too large. Thus, a proper  $H_{\rm c}$  will benefit the device performance.

In order to understand the potential of DF-TFET in ultra-low-power applications, Table 2 shows a performance comparison of different TFETs with DF-TFET. Compared to TFETs with a traditional heavily doped p—n tunneling junction [6, 20, 32–35], DF-TFET has obvious advantages on SS and switching ratio. This is due to the characteristics of DF-TFET by using electrostatically doping. Compared to other dopingless TFETs [22, 23, 36, 37], DF-TFET has obvious advantages on I<sub>ON</sub>. This is because of the improved tunneling rate by using line tunneling junction and SiGe material. By combining the advantages of p—n tunneling junction and dopingless tunneling junction, DF-TFET can provide high operating

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 6 of 8

current and low static power consumption in ultra-low-power applications.

#### **Conclusion**

In this work, a novel DF-TFET is proposed and the electrical characteristics are analyzed by simulation method. The structure characteristic, physical mechanism, performance with different parameters and analog/RF performance of DF-TFET are discussed and studied. Benefit from the dopingless fin structure channel, stack gate dielectric, SiGe channel material and high-efficiency line tunneling junction, good performance in switching characteristics and analog/RF

**Fig. 6** Transfer characteristics with different **a** gate work function  $(\varphi_{\text{Gate}})$  and drain work function  $(\varphi_{\text{Drain}})$ , **b** SiGe composition ratio, **c** gate length  $(W_{\text{o}})$  and **d** channel thickness  $(H_{\text{c}})$

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 7 of 8

Table 2 Performance comparison of different TFETs with DF-TFET (at  $V_{GS} = V_{DS} = 0.5 \text{ V}$ )

| Device          | / <sub>ON</sub> (μΑ/μm) | Switching ratio      | SS <sub>avg</sub> (mV/dec) |

|-----------------|-------------------------|----------------------|----------------------------|

| V-TFET [32]     | 8                       | ~ 10 <sup>7</sup>    | 51                         |

| DS-TFET [33]    | 0.01                    | $5.3 \times 10^7$    | 64                         |

| SUTFET [6]      | 13.5                    | $4.4 \times 10^6$    | 25                         |

| TMG TFET [34]   | 10                      | $3.3 \times 10^{8}$  | 44                         |

| GS-TFET [35]    | 0.1                     | $5.9 \times 10^{11}$ | 40                         |

| TG-TFET [20]    | 0.6                     | $6 \times 10^{8}$    | 45                         |

| DL-TFET [22]    | 0.01                    | $1.1 \times 10^9$    | 51                         |

| ML-DL-TFET [23] | 0.1                     | ~ 10 <sup>13</sup>   | 19                         |

| DMD-DLTFET [36] | $5 \times 10^{-3}$      | ~ 10 <sup>9</sup>    | 43                         |

| H-DLTFET [37]   | 0.9                     | ~ 10 <sup>14</sup>   | 16 mV/de                   |

| This work       | 3.8                     | $1.4 \times 10^{11}$ | 18                         |

characteristics can be obtained. Moreover, by avoiding the formation of the abrupt p–n junction in manufacture process, uniform doping with high consistency and high robustness on process fluctuation can be achieved. Simulation result shows that,  $I_{\rm ON}$  of 58.8  $\rm \mu A/\mu m$ , switching ratio of 12 orders of magnitude, no obvious ambipolar effect, SS\_min of 2.8 mV/dec and  $f_{\rm T}$  of 5.04 GHz can be achieved by DF-TFET. With the large operating current, high switching ratio, steep SS, good reliability, stable fabrication process and good manufacturability, it can be expected as one of the promising candidates for the future low-power IC and sensitive sensor applications.

#### **Abbreviations**

DF-TFET: Dopingless fin-shaped SiGe channel TFET; ICs: Integrated circuits; TGTFET: T-shaped gate dual-source TFET; DL-TFET: Dopingless TFET;  $I_{ON}$ : On-state current;  $I_{OFF}$ : Off-state current;  $SS_{\min}$ : Minimum subthreshold swing;  $SS_{avg}$ : Average subthreshold swing;  $C_{gg}$ : Gate capacitance;  $C_{gd}$ : Gate to drain capacitance;  $f_{T}$ : Cutoff frequency; GBW: Gain bandwidth product;  $\lambda$ : Effective screening length; m\*: Effective carrier mass;  $E_{g}$ : Energy band gap;  $\Delta\Phi$ : Effective screening energy window;  $W_{g}$ : Length of gate;  $W_{Gap}$ : Length of gap;  $T_{ox}$ : Stack gate oxide thickness;  $H_{c}$ : Channel thickness;  $\Psi_{Gate}/\Psi_{Drain}$ : Gate and drain work function;  $V_{DS}$ : Drain to source voltage;  $V_{GS}$ : Gate to source voltage.

#### Acknowledgements

In particular, thank you for the discussion and help of Prof. Jamal Deen in the process of writing this manuscript.

#### Authors' contributions

SC puts forward the innovative results in this manuscript and completed the work of simulation and article writing. SW and HL support the completion of this work, and participation in help format modification and detail discussion. TH, HX and CC helped in format modification and detailed discussion. All authors read and approved the final manuscript.

#### Funding

This research is financially supported by the National Natural Science Foundation of China (Grant No. 61904136), the China Postdoctoral Science Foundation (Grant No. 2019M653551) and the Fundamental Research Program of Shaanxi (Grant No. 2019JQ-656).

#### Availability of data and materials

Not applicable (This manuscript is a purely theoretical study on analog/RF performance of TFET. The simulation data have been given in this manuscript, and it is not to be described here).

#### Competing interests

There are non-financial competing interests.

Received: 17 June 2020 Accepted: 6 October 2020 Published online: 17 October 2020

#### References

- lonescu AM, Riel H (2011) Tunnel field-effect transistors as energyefficient electronic switches. Nature 479(7373):329–337. https://doi. org/10.1038/nature10679

- Sakurai T (2004) Perspectives of low power VLSI's. IEICE Trans Electron 87:429–436

- Villalon A, Carval GL, Martinie S, Royer CL, Jaud MA, Cristoloveanu S (2014) Further insights in TFET operation. IEEE Trans Electron Devices 61(8):2893–2898. https://doi.org/10.1109/TED.2014.2325600

- Li W, Liu H, Wang S, Chen S (2017) Reduced Miller capacitance in U-shaped channel tunneling FET by Introducing heterogeneous gate dielectric. IEEE Electron Device Lett 38(3):403–406. https://doi. org/10.1109/LED.2017.2661318

- Li W, Liu H, Wang S, Chen S, Wang Q (2018) The optimization of spacer engineering for capacitor-less DRAM based on the dual-gate tunneling transistor. Nanoscale Res Lett 13(1):73. https://doi.org/10.1186/s1167 1-018-2483-8

- Chen S, Wang S, Liu H, Li W, Wang Q, Wang X (2017) Symmetric U-shaped gate tunnel field-effect transistor. IEEE Trans Electron Devices 64(3):1343– 1349. https://doi.org/10.1109/TED.2017.2647809

- Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

- Huang Q, Huang R, Zhan Z, Qiu Y, Jiang W, Wu C, Wang Y (2012) A novel Si tunnel FET with 36 mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration. In: Proceedings IEDM. IEEE, San Francisco, CA, USA, pp 8.5.1–8.5.4. https://doi. org/10.1109/IEDM.2012.6479005.

- Avci UE, Young IA (2013) Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length. In: Proceedings of IEDM. IEEE, Washington, DC, USA, pp 4.3.1–4.3.4. https://doi.org/10.1109/ IEDM.2013.6724559.

- Nagavarapu V, Jhaveri R, Woo JCS (2008) The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans Electron Devices 55(4):1013–1019. https://doi.org/10.1109/TED.2008.916711

- Abdi DB, Kumar MJ (2014) In-built N+ pocket p-n-p-n tunnel fieldeffect transistor. IEEE Electron Device Lett 35(12):1170–1172. https://doi. org/10.1109/LED.2014.2362926

- Choi W, Lee H (2016) Demonstration of hetero-gate-dielectric tunneling field-effect transistors (HG TFETs). Nanoscale Res Lett 3:13. https://doi. org/10.1186/s40580-016-0073-y

- Cao W, Yao CJ, Jiao GF, Huang D, Yu HY, Li MF (2011) Improvement in reliability of tunneling field-effect transistor With p-n-i-n structure. IEEE Trans Electron Devices 58(7):2122–2126. https://doi.org/10.1109/ TED.2011.2144987

- Toh EH, Wang GH, Samudra G, Yeo YC (2007) Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl Phys Lett 90(26):263507. https://doi. org/10.1063/1.2748366

- Huang R, Huang Q, Chen S et al (2014) High performance tunnel field-effect transistor by gate and source engineering. Nanotechnology 25(50):505201. https://doi.org/10.1088/0957-4484/25/50/505201

- Wang W, Wang PF, Zhang CM, Lin X, Liu XY, Sun QQ, Zhou P, Zhang DW (2014) Design of U-shape channel tunnel FETs with SiGe source regions. IEEE Trans Electron Devices 61(1):193–197. https://doi.org/10.1109/ TED.2013.2289075

Chen et al. Nanoscale Res Lett (2020) 15:202 Page 8 of 8

- Yang Z (2016) Tunnel field-effect transistor with an L-shaped gate. IEEE Electron Device Lett 37(7):839–842. https://doi.org/10.1109/ LED.2016.2574821

- Kim SW, Kim JH, Liu TK, Choi WY, Park B (2016) Demonstration of L-shaped tunnel field-effect transistors. IEEE Trans Electron Devices 63(4):1774– 1778. https://doi.org/10.1109/TED.2015.2472496

- Kim SW, Choi WY, Sun MC, Kim WH, Park BG (2012) Design guideline of Si-based L-shaped tunneling field-effect transistor. Jpn. J. Appl. Phys. 51(6s):06FE09. https://doi.org/10.1143/JJAP.51.06FE09

- Chen S, Liu H, Wang S, Li W, Wang X, Zhao L (2018) Analog/RF performance of T-shape gate dual-source tunnel field-effect transistor. Nanoscale Res Lett 13:321. https://doi.org/10.1186/s11671-018-2723-y

- Li W, Liu H, Wang S, Chen S, Yang N (2017) Design of high performance Si/SiGe heterojunction tunneling FETs with a T-shaped gate. Nanoscale Res Lett 12(1):198. https://doi.org/10.1186/s11671-017-1958-3

- Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 60(10):3285–3290. https://doi.org/10.1109/TED.2013.2276888

- Raad BR, Tirkey S, Sharma D, Kondekar P (2017) A New Design approach

of dopingless tunnel FET for enhancement of device characteristics.

IEEE Trans Electron Devices 64(4):1830–1836. https://doi.org/10.1109/ TED.2017.2672640

- Rajasekharan B, Hueting RJE, Salm C, van Hemert T, Wolters RAM, Schmitz J (2010) Fabrication and characterization of the charge-plasma diode. IEEE Electron Device Lett 31(6):528–530. https://doi.org/10.1109/ IED.2010.2045731

- Hueting RJE, Rajasekharan B, Salm C, Schmitz J (2008) The charge plasma P-N diode. IEEE Electron Device Lett 29(12):1367–1369. https://doi. org/10.1109/LED.2008.2006864

- Sze SM (1981) Physics of semiconductor devices. Wiley, Hoboken. https://doi.org/10.1016/s0026-2692(82)80036-0

- Ando T et al (2017) High mobility high-Ge-content SiGe PMOSFETs using Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stacks with in-situ O<sub>3</sub> treatment. IEEE Electron Device Lett 38(3):303–305. https://doi.org/10.1109/LED.2017.2654485

- 28. Yue Y, Hao Y, Zhang J (2008) AlGaN/GaN MOS-HEMT with stack gate  $H_tO_2/Al_2O_3$  structure grown by atomic layer deposition. In: 2008 IEEE

- compound semiconductor integrated circuits symposium, Monterey, CA, pp 1–4. https://doi.org/10.1109/CSICS.2008.59

- 29. Zhang R, Huang P, Lin J, Taoka N, Takenaka M, Takagi S (2013) High-mobility Ge p- and n-MOSFETs with 0.7-nm EOT using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/ Ge gate stacks fabricated by plasma postoxidation. IEEE Trans Electron Devices 60(3):927–934. https://doi.org/10.1109/TED.2013.2238942

- Verreck D, Verhulst AS, Kao K, Vandenberghe WG, De Meyer K, Groeseneken G (2013) Quantum mechanical performance predictions of p-n-i-n versus pocketed line tunnel field-effect transistors. IEEE Trans Electron Devices 60(7):2128–2134. https://doi.org/10.1109/TED.2013.2260237

- Lin J, Wang T, Lee W, Yeh C, Glass S, Zhao Q (2018) Characteristics of recessed-gate TFETs with line tunneling. IEEE Trans Electron Devices 65(2):769–775. https://doi.org/10.1109/TED.2017.2786215

- 32. Lee H, Park J, Shin C (2016) Study of random variation in germaniumsource vertical tunnel FET. IEEE Trans Electron Devices 63(5):1827–1834

- Bagga N, Kumar A, Dasgupta S (2017) Demonstration of a novel two source region tunnel FET. IEEE Trans Electron Devices 64(12):5256–5262

- Ko E, Lee H, Park J, Shin C (2016) Vertical tunnel FET: design optimization with triple metal-gate layers. IEEE Trans Electron Devices 63(12):5030–5035

- Sun M et al (2010) Scalable embedded Ge-junction vertical channel tunneling field-effect transistor for low-voltage operation. In: 2010 IEEE nanotechnology materials and devices conference, Monterey, CA, pp 286-290

- Sharma N, Chauhan SS (2017) Dual metal drain Ge-source dopingless TFET with enhanced turn-ON steep subthreshold swing and high ONcurrent. Flectron Lett 53(14):960–962

- Han T, Liu H, Chen S et al (2019) Design and investigation of the high performance doping-less TFET with Ge/Si<sub>0.6</sub>Ge<sub>0.4</sub>/Si heterojunction. Micromachines 10(6):424

#### **Publisher's Note**

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

# Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- ► Rigorous peer review

- ▶ Open access: articles freely available online

- ► High visibility within the field

- Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com