Received 11 June 2021; revised 1 July 2021; accepted 13 July 2021. Date of publication 15 July 2021; date of current version 27 July 2021. The review of this paper was arranged by Editor S. Ikeda.

Digital Object Identifier 10.1109/JEDS.2021.3097390

# A Novel SiC Asymmetric Cell Trench MOSFET With Split Gate and Integrated JBS Diode

# JINPING ZHANG (Member, IEEE)<sup>®</sup>, ZIXUN CHEN, YUANYUAN TU, XIAOCHUAN DENG (Member, IEEE)<sup>®</sup>, AND BO ZHANG (Senior Member, IEEE)<sup>®</sup>

State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu 610054, China CORRESPONDING AUTHOR: J. ZHANG (e-mail: jinpingzhang@uestc.edu.cn)

This work was supported in part by the National Key Research and Development Program of China under Grant 2018YFB0905702; in part by the National Natural Science Foundation of China under Grant 61404023; and in part by the China Postdoctoral Science Foundation under Grant 2020M682607.

**ABSTRACT** A novel high performance SiC asymmetric cell trench MOSFET with split gate (SG) and integrated junction barrier schottky (JBS) diode (SGS-ATMOS) is proposed for the first time. The shielding effect provided by the SG structure not only reduces the gate-drain capacitance ( $C_{gd}$ ) but also alleviates the electric field crowding in the dielectric layer at trench corner. The integrated trench JBS diode bypasses the PiN body diode while obtaining good double protection from the SG and p-type shielding region. Therefore, not only the MOSFET but also diode performance is significantly improved for the proposed structure. Numerical analysis results show that compared with the conventional asymmetric cell trench MOSFET (Con-ATMOS), the high frequency figure of merit (HFFOM<sup>1</sup>,  $R_{on} \cdot C_{gd}$ ) is reduced by 92.5% and the Baliga figure of merit (BFOM,  $BV^2/R_{on.sp}$ ) is increased by 57.2%, respectively. In addition, the forward conduction voltage drop ( $V_{\rm F}$ ), reverse recovery charge ( $Q_{\rm rr}$ ) and peak reverse recovery current  $(I_{\rm rrm})$  of the diode are reduced from 3.10V, 1.95 $\mu$ C/cm<sup>2</sup> and 68.0A for the Con-ATMOS to 1.56V,  $0.97\mu$ C/cm<sup>2</sup> and 35.9A for the proposed SGS-ATMOS, respectively. Compared with the Con-ATMOS, the turn-on loss ( $E_{on}$ ) and turn-off loss ( $E_{off}$ ) of the proposed device are reduced by 33.3% and 33.0%, respectively. The  $E_{\rm on}$  and  $E_{\rm off}$  of the proposed device are also 33.6% and 30.0% off compared with the Con-ATMOS with external JBS diode, respectively. The temperature characteristics of the SGS-ATMOS are also discussed and it is found that the proposed device exhibits good performance at high temperature.

**INDEX TERMS** 4H-SiC, trench MOSFET, asymmetric cell, split gate, junction barrier Schottky (JBS), figure of merit (FOM), turn-on loss, turn-off loss.

#### I. INTRODUCTION

Silicon carbide (SiC) based power semiconductor devices are very suitable for high voltage, high power and high temperature applications due to its excellent material performance, such as wide bandgap, large critical electric field strength and high thermal conductivity [1]–[6]. Compared with silicon insulated gate bipolar transistor (Si IGBT), SiC metaloxide-semiconductor field effect transistor (MOSFET) has faster switching speed and lower switching loss, which significantly improve electric power conversion efficiency and reduce size of passive components [7]–[10]. Although SiC planar gate MOSFET demonstrates good reliability performance [11], [12], trench MOSFET (TMOS) structure is still preferred since it has better device performance, which derived from large channel density and weakened junction field effect transistor (JFET) effect. However, for the conventional SiC TMOS, high electric field in the SiC drift region and large relative permittivity ( $\varepsilon$ ) ratio of SiC to SiO<sub>2</sub> lead to very high electric field in the trench gate oxide layer at the blocking state. The gate oxide layer will breakdown or degrade before the drain bias reaches avalanche breakdown voltage ( $BV_{av}$ ). 3MV/cm is commonly adopted as the maximum electric field in the gate oxide layer ( $E_{ox,max}$ ) for good long-time reliability. To reduce the electric field in the gate oxide layer, a heavily doped p-type shielding (p-SH) region under the trench bottom is introduced [13], [14]. However, the p-SH region brings about additional JFET region, which increases the specific on-state resistance  $(R_{on,sp})$ . So, a relative-heavily doped n-type current spreading layer (CSL) is inserted between the p-base and n drift region [15], [16], or it wraps the p-SH region [17]. It helps to spread current from the MOS channel into the drift region and weaken the JFET effect caused by the p-SH region. References [18] and [19] introduce a SiC double trench MOSFET (DTMOS) with a p-SH region only in the sidewall and bottom of a source trench. The DTMOS achieves a low  $R_{on,sp}$  as well as alleviates the electric field crowding in the gate trench oxide layer. However, it has large gate-drain capacitance  $(C_{gd})$  contributed by the bottom of the gate trench [20]. The DTMOS also shows a gate oxide rapture due to its instable avalanche robustness under unclamped inductive switching (UIS) stress [21]. In recent years, SiC asymmetric cell TMOS structures, such as the conventional asymmetric cell trench MOSFET (Con-ATMOS) [22], [23] and asymmetric cell tilt implanted trench MOSFET (ACTI-TMOS) [24], etc. have been proposed. The source-connected asymmetric p-SH region not only alleviates the electric field crowding at the trench bottom and corners in the gate oxide layer but also reduces the  $C_{gd}$  at the same time. Therefore, improved device performance and gate oxide reliability were achieved. However, for the SiC asymmetric cell TMOS structures, the gate trench bottom and side wall faced to the n drift region still introduce additional  $C_{\rm gd}$  and the electric field crowding at the trench bottom and corners in the gate oxide layer still limit the improvement of device performance and gate oxide reliability.

For the SiC MOSFET, the use of PiN body diode is usually avoided due to the large turn-on voltage and bipolar degradation [9], [25]. External anti-parallel SiC junction barrier schottky (JBS) diode is commonly used but it will increase volume, capacitance and cost of the SiC device. Additional connection wire between the SiC JBS diode and MOSFET also increases stray inductance and reduces reliability of the device. Therefore, integration of a JBS diode in the SiC MOSFET is a promising solution. Using a separate active region to integrate the JBS diode in the SiC MOSFET is a relatively easy way [26], [27]. However, it adds a relatively large chip area. To integrate the JBS diode in the MOSFET cell, a lot of efforts have been made in [28]-[33]. SiC TMOSs with an integrated JBS diode between two trench gates were demonstrated in References [30] and [31], respectively. Based on the conventional SiC TMOS with p-SH region, [32]-[34] report a SiC TMOS with an integrated JBS diode at the side wall of an additional source trench. In these SiC TMOS structures, however, the integrated JBS diode occupies additional chip area and impacts performance of the SiC MOSFET.

In this paper, a novel SiC asymmetric cell TMOS with a split gate (SG) and integrated JBS diode (SGS-ATMOS) is proposed for the first time. Compared with the Con-ATMOS, the proposed structure demonstrates excellent static and dynamic performance with suppressed electric field crowding

(b) Con-ATMOS

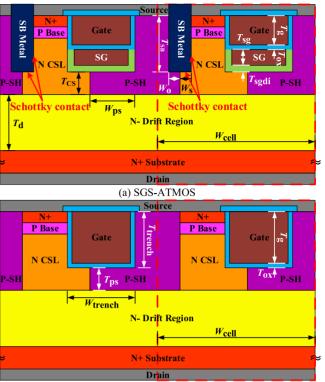

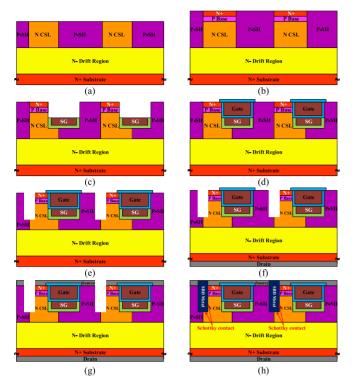

**FIGURE 1.** Schematic cross sectional view of the SiC devices: (a) proposed SGS-ATMOS and (b) Con-ATMOS.

at the trench corners. Meanwhile, the integrated trench JBS diode with double protection demonstrates excellent performance without occupation of additional chip area.

#### **II. DEVICE STRUCTURE AND MECHANISM**

Fig. 1 (a) and (b) show the schematic cross-sectional view of the proposed SiC SGS-ATMOS and Con-ATMOS, respectively. Both structures are asymmetric cell TMOS with a source-connected asymmetric p-SH region surrounding the sidewall and part of the trench bottom. The negative charges provided by the depletion region of the p-SH region alleviate the high electric field at trench bottom and corners in the trench gate dielectric layer. A relative-heavily doped n CSL under the p-base region and part of the trench are adopted in both structures to alleviate the JFET effect. Compared with the Con-ATMOS, the proposed SGS-ATMOS features a source-connected SG under the trench gate as well as a schottky barrier (SB) metal inserted between the p-SH region and n CSL. The source-connected SG decouples the interaction between the drain and gate. Therefore, the  $C_{\rm gd}$  as well as gate-drain charges  $(Q_{gd})$  are dramatically reduced, which improves the switching speed and reduces the switching loss. The SB metal forms schottky contact with the n CSL. An integrated trench JBS diode is introduced with good double protection from the p-SH region and trench SG structure. The double protection mechanism of the integrated trench JBS diode reduces the high-temperature leak current

TABLE 1. Main parameters used in the simulation.

| Parameter                                          | SGS-<br>ATMOS                       | Con-<br>ATMOS                         |

|----------------------------------------------------|-------------------------------------|---------------------------------------|

| Cell width, W <sub>cell</sub>                      | 2.5µm                               | 2.5µm                                 |

| Trench width, W <sub>trench</sub>                  | 1µm                                 | 1μm                                   |

| Trench depth, T <sub>trench</sub>                  | 1.15µm                              | 1.15µm                                |

| Gate depth, $T_{\rm g}$                            | 0.6µm                               | 1.1µm                                 |

| Gate oxide thickness, $T_{ox}$                     | 50nm                                | 50nm                                  |

| P-SH region thickness under trench, $T_{ps}$       | 0.4µm                               | 0.4µm                                 |

| P-SH region width under trench, $W_{ps}$           | 0.7µm                               | 0.7µm                                 |

| N- drift region thickness, $T_{d}$                 | 12µm                                | 12µm                                  |

| N- drift region concentration, $N_d$               | 8.2×1015 cm-3                       | 8.2×10 <sup>15</sup> cm <sup>-3</sup> |

| P-base width, $W_{\rm pb}$                         | 0.8µm                               | 1µm                                   |

| N CSL concentration, $N_{\rm CS}$                  | 2×10 <sup>16</sup> cm <sup>-3</sup> | 2×10 <sup>16</sup> cm <sup>-3</sup>   |

| N CSL thickness under trench, $T_{CS}$             | 0.4µm                               | 0.4µm                                 |

| Split gate thickness, $T_{sg}$                     | 0.4µm                               | /                                     |

| Split gate dielectric thickness, T <sub>sgdi</sub> | 100nm                               | /                                     |

| SB metal depth, $T_{\rm SB}$                       | 1.15µm                              | /                                     |

| Ohmic contact width of SB metal, $W_0$             | 0.2µm                               | /                                     |

| Schottky contact width of SB metal, $W_{\rm s}$    | 0.2µm                               | /                                     |

| Work function of the SB metal, $W_{\rm fs}$        | 5.1eV                               | /                                     |

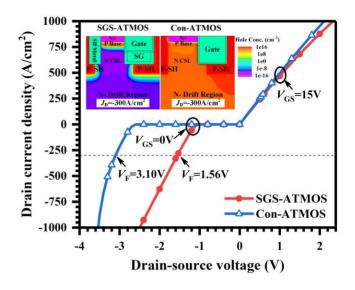

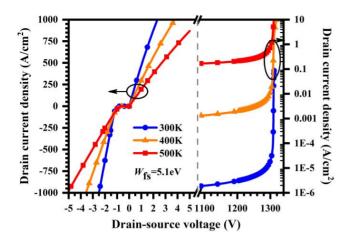

**FIGURE 2.** Forward and reverse conduction I-V characteristics for the SGS-ATMOS and Con-ATMOS, respectively. The inserted figures show the hole concentration distribution in the device surface in the diode conduction mode at  $J_{\rm D} = -300 {\rm A/cm}^2$ .

$(J_{lk})$  at the blocking state, which is similar to that in our previous work [30]. Since the integrated trench JBS diode are formed mainly at the sidewall of the SB metal, it does not occupy additional chip area and will not increase the cell width of the SiC MOSFET.

Silvaco TCAD is used to simulate the characteristics of the SiC ATMOSs [35]. To simplify the simulation, the cell marked within the red dash line for the two structures are simulated. Similar to our previous work in [3], [6], [21], [30] and [36], Fermi-Dirac statistics is used in the simulation and models, such as band gap narrowing (BGN), incomplete ionization, FLDMOB, CONWELL, SURFMOB, CONSRH, Auger and analytic models are considered. 4H-SiC material is used and the main device parameters used in the simulation are listed in the Table 1. The work function of the SB metal used to form schottky contact is 5.1eV. If not specified in the following discussion, the device active region used is 1cm<sup>2</sup>. To have a meaningful comparison, the device parameters not listed in the Table 1 are the same for the two structures.

## **III. RESULTS AND DISCUSSION**

Fig. 2 shows the forward and reverse conduction I-V characteristics for the two devices. The forward and reverse I-V curves are obtained with gate-source voltage ( $V_{GS}$ ) of 15V and 0V, respectively. SiO<sub>2</sub> is used as the gate and SG dielectric for the proposed SGS-ATMOS and Con-ATMOS. It can be seen that although the source-connected SG structure has a certain impact on the JFET resistance for the proposed device, the two devices still have comparable forward I-V characteristics. It also can be seen that contributed by the lower turn-on voltage of the integrated JBS diode, the forward conduction voltage drop ( $V_F$ ) for the diode of the proposed SGS-ATMOS is only 1.56V, which is about half of 3.10V for the diode of the Con-ATMOS at drain current density ( $J_D$ ) of  $-300A/cm^2$ . The inserted figures in the Fig. 2 show the surface hole concentration distribution in the diode conduction mode at  $J_D = -300A/cm^2$  for the proposed SGS-ATMOS and Con-ATMOS, respectively. It is found that compared with the Con-ATMOS, the hole concentration at the drift region for the proposed SGS-ATMOS is extreme low. It indicates that the integrated JBS diode successfully bypasses the conduction of the PiN body diode. As a result, the proposed device not only has a low  $V_F$ in the diode conduction mode but also suppress the bipolar degradation effect appears in the PiN body diode for the Con-ATMOS.

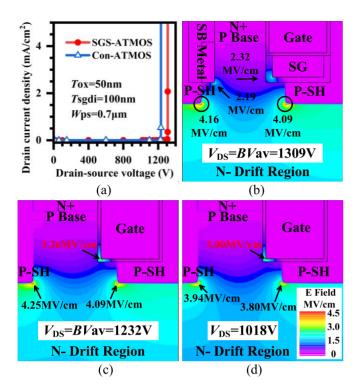

Fig. 3(a) shows the blocking I-V characteristics for the two devices with same P-SH region width under trench  $(W_{ps})$  of 0.7µm. It can be seen that the proposed SGS-ATMOS has a little bit higher  $BV_{av}$  than that of the Con-ATMOS. The BV<sub>av</sub> is 1309V and 1232V for the proposed SGS-ATMOS and Con-ATMOS, respectively. Fig. 3(b) and Fig. 3(c) show the electric field distribution at  $BV_{av}$  for the proposed SGS-ATMOS and Con-ATMOS, respectively. It can be seen that although the two devices have comparable  $BV_{av}$ , the  $E_{ox,max}$  for the Con-ATMOS is much higher than that of the proposed SGS-ATMOS. The  $E_{ox,max}$  at  $BV_{av}$ is 2.32MV/cm and 3.26MV/cm for the proposed SGS-ATMOS and Con-ATMOS, respectively. Considering good long-time reliability, the higher  $E_{ox,max}$  at  $BV_{av}$  for the Con-ATMOS shall induces gate oxide breakdown or degradation. Fig. 3(d) shows electric field distribution for the Con-ATMOS with  $E_{ox,max}=3MV/cm$ , where the  $V_{ds}$  is only 1018V. It can be concluded that since the SG with thicker  $T_{\text{sgdi}}$  for the proposed SGS-ATMOS relieves the electric

FIGURE 3. (a) Blocking I-V characteristics for the two devices, (b) electric field distribution for the SGS-ATMOS at  $BV_{av}$ , (c) electric field distribution for the Con-ATMOS at  $BV_{av}$  and (d) electric field distribution for the Con-ATMOS with  $E_{ox,max} = 3MV/cm$ , where the  $V_{DS}$  is only 1018V.

field crowding in the dielectric layer at the trench corner, the limiting factor of breakdown is shifted from the gate oxide breakdown for the Con-ATMOS to the avalanche breakdown for the proposed SGS-ATMOS. As a result, the breakdown voltage (*BV*) is increased from 1018V of the Con-ATMOS to 1309V of the proposed SGS-ATMOS. Considering Baliga's figure of merit (BFOM,  $BV^2/R_{on,sp}$ ), although the proposed SGS-ATMOS has a little bit higher  $R_{on,sp}$ , the BFOM is still increased from  $5.23 \times 10^8$  W/cm<sup>2</sup> of the Con-ATMOS to  $8.22 \times 10^8$  W/cm<sup>2</sup> of the proposed SGS-ATMOS. Compared with the Con-ATMOS, the BFOM for the proposed device is increased by 57.2% owing to the improved *BV*. The above results demonstrate that the proposed SGS-ATMOS has an improved static performance.

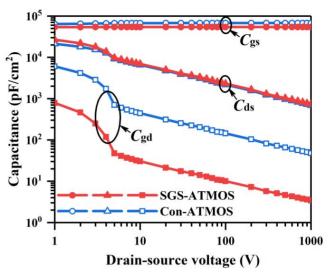

The device capacitance as a function of the drain-source voltage  $(V_{DS})$  is shown in the Fig. 4. It can be seen that the  $C_{gd}$  and gate-source capacitance  $(C_{gs})$  of the proposed SGS-ATMOS are smaller than those of the Con-ATMOS in the whole  $V_{DS}$  range. The  $C_{gd}$  and  $C_{gs}$  at the  $V_{DS}$  of 600V for the SGS-ATMOS are 4.31pF/cm<sup>2</sup> and 54.1nF/cm<sup>2</sup>, respectively. At the same condition, the  $C_{gd}$  and  $C_{gs}$  are 60.8pF/cm<sup>2</sup> and 67.4nF/cm<sup>2</sup> for the Con-ATMOS, respectively. Compared with the Con-ATMOS, the  $C_{gd}$  and  $C_{gs}$  are reduced by 92.9% and 19.7% for the proposed SGS-ATMOS, respectively. Further investigation results show that the dramatically reduced  $C_{gd}$  and  $C_{gs}$  are derived from the reduced gate depth as well as decoupled interaction

FIGURE 4. Device capacitance as a function of the drain-source voltage.

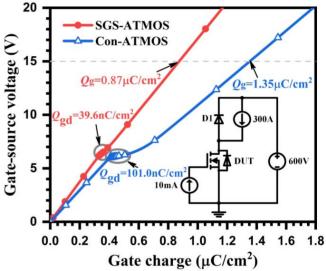

FIGURE 5. Gate charges versus gate-source voltage for the two devices.

between the gate and drain. It is contributed by the appearance of the source-connected SG structure. With the much smaller  $C_{\rm gd}$ , the proposed SGS-ATMOS demonstrates superior high frequency figure of merit (HFFOM<sup>1</sup>,  $R_{on} \cdot C_{gd}$ ). The  $R_{on} \cdot C_{gd}$  is reduced from 120.0m $\Omega$ ·pF for the Con-ATMOS to 9.0m $\Omega$ ·pF for the SGS-ATMOS. Compared with the Con-ATMOS, the HFFOM<sup>1</sup>  $(R_{on} \cdot C_{gd})$  for the proposed SGS-ATMOS is reduced by 92.5%. For the drain-source capacitance ( $C_{ds}$ ), the SGS-ATMOS has almost same  $C_{ds}$  as that of the Con-ATMOS. The obvious reduction of the  $C_{ds}$ and  $C_{\rm gd}$  at  $V_{\rm DS}$  of 2V-5V for the two devices is derived from the depletion of JFET region between the two p-SH regions. The gate charges  $(Q_g)$  versus the  $V_{GS}$  is also shown in Fig. 5. The inserted figure shows test circuit used in the simulation. It can be seen that the  $Q_{\rm g}$  and  $Q_{\rm gd}$  of the proposed SiC SGS-ATMOS are significantly reduced.

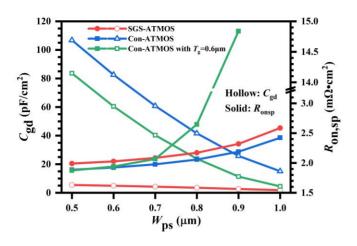

**FIGURE 6.** Influence of the  $W_{ps}$  on the  $C_{gd}$  and  $R_{on,sp}$ .

Compared with 101.0nC/cm<sup>2</sup> for the Con-ATMOS, the  $Q_{gd}$  for the SGS-ATMOS is only 39.6nC/cm<sup>2</sup>. Meanwhile, the total  $Q_g$  from V<sub>GS</sub> = 0V to 15V is only 0.87µC/cm<sup>2</sup> for the SGS-ATMOS. While at the same condition, the total  $Q_g$  is 1.35µC/cm<sup>2</sup> for the Con-ATMOS. When it comes to another HFFOM (HFFOM<sup>2</sup>,  $R_{on} \cdot Q_{gd}$ ), the  $R_{on} \cdot Q_{gd}$  is reduced from 200.0m $\Omega$ ·nC for the Con-ATMOS to 82.5m $\Omega$ ·nC for the SGS-ATMOS. Compared with the Con-ATMOS, the HFFOM<sup>2</sup> ( $R_{on} \cdot Q_{gd}$ ) for the proposed SGS-ATMOS is reduced by 58.8%.

Fig. 6 shows the influence of the  $W_{ps}$  on the  $C_{gd}$  and  $R_{\text{on,sp}}$  for the proposed SGS-ATMOS and Con-ATMOS, respectively. In order to have a meaningful comparison, the Con-ATMOS with a gate depth  $(T_g)$  of 0.6µm is also added in the figure. It can be seen that with the  $W_{ps}$  increases from 0.5 $\mu$ m to 1 $\mu$ m, the C<sub>gd</sub> decreases significantly for the two Con-ATMOSs owing to the enhanced shielding effect provided by the source-connected P-SH region. Compared to the Con-ATMOS, the Con-ATMOS with the  $T_{g} = 0.6 \mu m$ has lower  $C_{\rm gd}$ , which derived from the smaller  $T_{\rm g}$ . While for the proposed SGS-ATMOS, the  $C_{gd}$  decreases slightly with the  $W_{ps}$  increases from 0.5µm to 1µm since good shielding effect already provided by the SG structure in the whole range. With the  $W_{ps}=1\mu m$ , the  $C_{gd}$  at the  $V_{DS}$ of 600V is 1.88pF/cm<sup>2</sup>, 15.1pF/cm<sup>2</sup> and 4.50pF /cm<sup>2</sup> for the proposed SGS-ATMOS, Con-ATMOS and Con-ATMOS with the  $T_g = 0.6 \mu m$ , respectively. Compared to the two Con- ATMOSs, the proposed device shows much lower  $C_{\rm gd}$ in the whole range. It also can be found that with the  $W_{ps}$ increases from 0.5 $\mu$ m to 1 $\mu$ m, the  $R_{on,sp}$  increases for these three devices. For the Con-ATMOS with the  $T_g = 0.6 \mu m$ , the  $R_{on,sp}$  increases sharply after the  $W_{ps}$  larger than 0.7 $\mu$ m owing to the increased JFET effect. For the proposed SGS-ATMOS and Con-ATMOS, the increase of the  $R_{on,sp}$  shows similar trend. With the  $W_{ps} = 1 \mu m$ , the HFFOM<sup>1</sup> is reduced from 36.6m $\Omega$ ·pF for the Con-ATMOS to 4.9m $\Omega$ ·pF for the proposed SGS-ATMOS. With the much smaller  $C_{gd}$  and

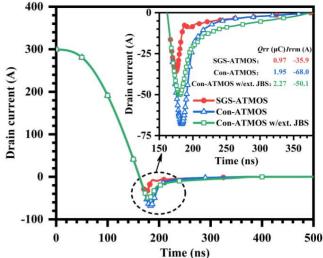

FIGURE 7. Reverse recovery waveforms for the diode of the SGS-ATMOS, Con-ATMOS and Con-ATMOS with external JBS diode.

comparable  $R_{\text{on,sp}}$ , the proposed SGS-ATMOS demonstrates superior high frequency figure of merit.

Fig. 7 shows reverse recovery waveforms for the diode of the SGS-ATMOS and Con-ATMOS, respectively. In order to have a meaningful comparison, the reverse recovery waveform for the Con-ATMOS with external anti-parallel JBS diode is also shown in the figure. The active area for the external JBS diode is also 1cm<sup>2</sup>. In the simulation, the forward conducting current ( $I_{\rm F}$ ) is 300A and the  $di_{\rm F}/dt$  is kept same for all the diodes. It can be seen that the integrated JBS diode for the proposed SGS-ATMOS exhibits the best reverse recovery performance among these three devices. Without injection of the minority carrier, the diode reverse recovery charge  $(Q_{\rm rr})$  and peak reverse recovery current ( $I_{rrm}$ ) are only 0.97 $\mu$ C/cm<sup>2</sup> and -35.9A for the proposed SGS-AMOS, which is 50.2% and 47.2% off compared with  $1.95\mu$ C/cm<sup>2</sup> and -68.0A for the Con-ATMOS, respectively. For the Con-ATMOS with external JBS diode, the  $Q_{\rm rr}$  and  $I_{\rm rrm}$  are 2.27 $\mu$ C/cm<sup>2</sup> and -50.1A, respectively. It can be found that compared with the proposed SGS-ATMOS, although the external JBS diode can suppress the conduction of the PiN body diode, the larger capacitance induced by the additional JBS diode increases the  $Q_{\rm rr}$  and  $I_{\rm rrm}$ .

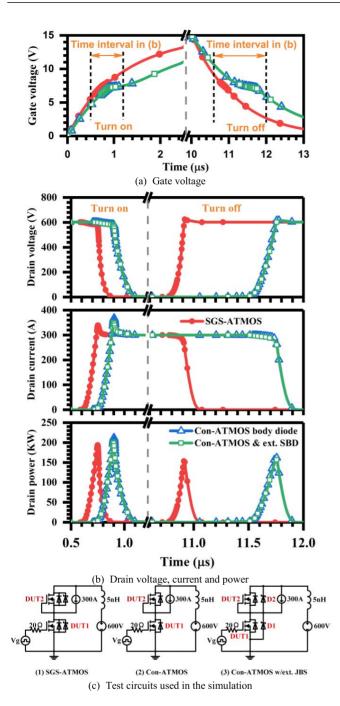

The gate and drain switching waveforms for the SGS-ATMOS, Con-ATMOS and Con-ATMOS with external JBS diode are shown in the Fig. 8 (a) and (b), respectively. The test circuits used in the simulation are shown in the Fig. 8(c). In each circuit, DUT1 and DUT2 are the same device and the active area for all the devices including external JBS diodes (D1 and D2) are  $1 \text{cm}^2$ . The gate voltage source (Vg) is turned on from 0V to 15V at  $t = 0\mu \text{s}$  and turned off from 15V to 0V at  $t = 10\mu \text{s}$ . It can be seen from the Fig. 8 (a) that the miller platform of the SGS-ATMOS is much shorter than that of the Con-ATMOS, which is aligned with the results indicated in the Fig. 5. It also can be seen

FIGURE 8. Switching waveforms and test circuits used in the simulation: (a) gate voltage, (b) drain voltage, current and power and (c) test circuits.

from Fig. 8 (a) and (b) that the switching speed of the SGS-ATMOS is much faster than those of the Con-ATMOS and Con-ATMOS with external JBS diode, which results in a much smaller switching loss. The turn-on loss ( $E_{on}$ ) and turn-off loss ( $E_{off}$ ) of the SGS-ATMOS are 16.4mJ/cm<sup>2</sup> and 17.7mJ/cm<sup>2</sup>, respectively. The  $E_{on}$  and  $E_{off}$  are reduced by 33.3% and 33.0% when compared with 24.6mJ/cm<sup>2</sup> and 26.4mJ/cm<sup>2</sup> for the Con-ATMOS, respectively. Meanwhile, the  $E_{on}$  and  $E_{off}$  of the SGS-ATMOS are also 33.6% and 30.0% off compared with 24.7mJ/cm<sup>2</sup> and 25.3mJ/cm<sup>2</sup> for

#### TABLE 2. Comparison of performance for the two devices.

| Parameter                                                                       | SGS-<br>ATMOS        | Con-<br>ATMOS        |

|---------------------------------------------------------------------------------|----------------------|----------------------|

| Specific on-state resistance, $R_{\text{on,sp}}$ (m $\Omega$ •cm <sup>2</sup> ) | 2.08                 | 1.98                 |

| Diode forward conduction voltage drop, $V_{\rm F}$ (V)                          | 1.56                 | 3.10                 |

| Breakdown voltage, $BV(V)$                                                      | 1309                 | 1018                 |

| Maximum electric field in oxide, E <sub>ox,max</sub> (MV/cm)                    | 2.32                 | 3.00                 |

| BFOM, $BV^2/R_{on,sp}$ (W/cm <sup>2</sup> )                                     | $8.22 \times 10^{8}$ | 5.23×10 <sup>8</sup> |

| Gate-drain capacitance, $C_{\rm gd,sp}$ (pF/cm <sup>2</sup> )                   | 4.31                 | 60.8                 |

| Gate-source capacitance, $C_{\rm gs,sp}$ (nF/cm <sup>2</sup> )                  | 54.1                 | 67.4                 |

| HFFOM <sup>1</sup> , $R_{on} \bullet C_{gd}$ (m $\Omega \bullet pF$ )           | 9.0                  | 120.0                |

| Gate-drain charges, $Q_{gd}$ (nC/cm <sup>2</sup> )                              | 39.6                 | 101.0                |

| Total gate charges, $Q_{\rm g}$ ( $\mu$ C/cm <sup>2</sup> )                     | 0.87                 | 1.35                 |

| HFFOM <sup>2</sup> , $R_{on} \bullet Q_{gd}$ (m $\Omega \bullet nC$ )           | 82.5                 | 200.0                |

\* $R_{on,sp}$  is obtained at  $V_{GS}$ =15V and  $J_D$ =300A/cm<sup>2</sup> and  $V_F$  is obtained at  $V_{GS}$ =0V and  $J_D$ =-300A/cm<sup>2</sup>.

| Parameter                                                         | SGS-<br>ATMO<br>S | Con-<br>ATM<br>OS | Con-<br>ATMOS<br>w/ext. JBS |

|-------------------------------------------------------------------|-------------------|-------------------|-----------------------------|

| Peak reverse recovery current, $I_{\rm rrm}$ (A)                  | -35.9             | -68.0             | -50.1                       |

| Reverse recovery charge, $Q_{\rm rr}$ ( $\mu$ C/cm <sup>2</sup> ) | 0.97              | 1.95              | 2.27                        |

| Turn on loss, $E_{\rm on}$ (mJ/cm <sup>2</sup> )                  | 16.4              | 24.6              | 24.7                        |

| Turn off loss, $E_{\rm off}$ (mJ/cm <sup>2</sup> )                | 17.7              | 26.4              | 25.3                        |

the Con-ATMOS with external JBS diode, respectively. In addition, other than the smaller  $E_{\rm on}$  and  $E_{\rm off}$ , the turnon and turn-off delay time are also much shorter for the proposed SiC SGS-ATMOS. Furthermore, the smaller  $Q_{\rm g}$  for the proposed SGS-ATMOS also makes it easier to be driven, which reduces the requirement for the gate driver.

Tables 2 and 3 summarize the simulation results for the SGS-ATMOS and Con-ATMOS. The reverse recovery and switching performance for the Con-ATMOS with external anti-parallel JBS diode are also listed in the Table 3. The results indicate that the proposed SGS-ATMOS has superior performance when compared with the Con-ATMOS with and without external anti-parallel JBS diode.

The impact of the temperature (T) on the static I-V characteristics of the SGS-ATMOS are shown in Fig. 9. It can be seen that with increase of the temperature, the forward and reverse conduction I-V characteristics are degraded due to reduction of the mobility at higher temperature. The  $R_{on,sp}$ increases from 2.08m $\Omega$ ·cm<sup>2</sup> at T = 300K to 3.38m $\Omega$ ·cm<sup>2</sup> and  $5.21 \text{m}\Omega \cdot \text{cm}^2$  at T = 400 K and T = 500 K, respectively. The  $V_{\rm F}$  of the integrated JBS diode increases from 1.56V at T = 300K to 1.81V and 2.20V at T = 400K and T = 500K, respectively. Although the positive temperature coefficient of  $R_{on,sp}$  and  $V_F$  increases the conduction loss at high temperature, it can avoid forming local current filament in applications due to the negative feedback mechanism of heat and electricity, which makes the SGS-ATMOS reliable and suitable for parallel usage [37]. The  $J_{lk}$  in the blocking state increases on orders of magnitude when the

FIGURE 9. Impact of temperature on the static I-V characteristics of the SGS-ATMOS.

temperature increases from 300K to 500K. However, the increase of the  $J_{lk}$  is still acceptable since good double protection is formed for the integrated trench JBS diode. Further investigation results show that the  $E_{ox,max}$  of the device is below 3MV/cm at different temperature and indicates the breakdown of the device is still avalanche breakdown.

To investigate the impact of the SG on the SGS-ATMOS, the relative permittivity ( $\varepsilon_{sgdi}$ ) and thickness ( $T_{sgdi}$ ) of the SG dielectric are varied to see how the device performance changes. In the discussion, the trench depth, gate depth as well as gate oxide thickness keep no change. The dependence of the device performance, such as capacitance ( $C_{gs}$ ,  $C_{ds}$  and  $C_{\rm gd}$ ),  $R_{\rm on,sp}$  and HFFOM<sup>1</sup> ( $R_{\rm on} \cdot C_{\rm gd}$ ) on the  $\varepsilon_{\rm sgdi}$  with the  $T_{\text{sgdi}} = 100$ nm is shown in Fig. 10(a). It can be seen that with the  $\varepsilon_{\text{sgdi}}$  increases, the  $C_{\text{gd}}$  and  $R_{\text{on}}$   $C_{\text{gd}}$  decrease significantly while the  $C_{gs}$ ,  $C_{ds}$  and  $R_{on,sp}$  increase slightly. The  $C_{\rm gd}$  and HFFOM<sup>1</sup> ( $R_{\rm on} \cdot C_{\rm gd}$ ) are reduced from 4.31pF/cm<sup>2</sup> and 9.00m $\Omega$ ·pF to 1.81pF/cm<sup>2</sup> and 3.85 m $\Omega$ ·pF when the  $\varepsilon_{\text{sgdi}}$  increases from 3.9 to 24, respectively. The decrease of the  $C_{\rm gd}$  and HFFOM<sup>1</sup> ( $R_{\rm on} \cdot C_{\rm gd}$ ) are induced by the enhanced shielding effect provided by the SG. Fig. 10(b) shows the impact of the  $T_{sgdi}$  on the device performance, such as capacitance ( $C_{gs}$ ,  $C_{ds}$  and  $C_{gd}$ ),  $R_{on,sp}$  and HFFOM<sup>1</sup> ( $R_{on} \cdot C_{gd}$ ) with the  $\varepsilon_{\rm sgdi} = 3.9$ . It can be seen that the  $C_{\rm gs}$ ,  $C_{\rm ds}$  and  $R_{\text{on,sp}}$  decrease while the  $C_{\text{gd}}$  and  $R_{\text{on}} \cdot C_{\text{gd}}$  increase as the  $T_{\text{sgdi}}$  increasing. The changing trends are all opposite to that shown in Fig. 10(a). The  $C_{\rm gd}$  increases from 4.31pF/cm<sup>2</sup> to 9.92pF/cm<sup>2</sup> when the  $T_{sgdi}$  increases from 100nm to 300nm. The increase of the  $C_{gd}$  is induced by the weakened shielding effect provided by the SG with the thicker  $T_{sgdi}$ . However, the  $C_{gs}$  decreases 14.7% when  $T_{sgdi}$  increases from 100nm to 300nm. The reduction of the  $C_{\rm gs}$  comes from the reduced overlap area between the gate and SG. The slightly reduced  $R_{on,sp}$  comes from the enhanced impact of the gate on the JFET region when the  $T_{sgdi}$  increases from 100nm to 300nm, which increases the accumulation of the electron near the trench in the forward conduction state at the  $V_{\rm GS}$  of 15V. It is found that adoption of the high-k

FIGURE 10. Impact of the  $\varepsilon_{sgdi}$  and  $T_{sgdi}$  on the device performance (a)  $\varepsilon_{sgdi}$  and (b)  $T_{sgdi}$ .

material or making the SG dielectric thinner is benefit for the reduction of the  $C_{gd}$  as well as HFFOM<sup>1</sup> ( $R_{on} \cdot C_{gd}$ ), which is benefit to the improvement of the dynamic performance.

A brief fabrication process flow for the SiC SGS-ATMOS is proposed in Fig. 11. A 4H-SiC epitaxial material with nepitaxial layer on n+ substrate is used as a starting material. Similar to the Con-ATMOS, the CSL, P base, N+ source and P-SH layer are formed via epitaxial growth and ion implantation, respectively. Compared with the Con-ATMOS, additional process steps are used to form the SG and schottky contact. The SG forming process for the SiC SGS-ATMOS is similar to that used for the Si SG-TMOS in our previous work [38], [39]. The SG is connected to source at the both ends of the trench strip via un-etched SG poly and metal via. Considering the lower temperature required to form schottky contact between the SB metal and n CSL, the SB metal is deposited and annealed after the formation of the backside and front side ohmic metals. The schottky contact process is similar to that used in [32]-[34] for 4H-SiC TMOS with an integrated JBS diode at the side wall of an additional source trench. Therefore, the additional process steps for the SG and schottky contact are fully compatible with the process flow of the SiC Con-ATMOS.

FIGURE 11. Proposed brief fabrication process flow for the 4H-SiC SGS-ATMOS. (a) epitaxial growth of the CSL and then formation of the first part of the P-SH layer via ion implantation, (b) epitaxial growth of the P base and N+ source layer successively and then formation of the second part of the P-SH layer via ion implantation, (c) etching the gate trench and then forming the SG (The SG is connected to source at the both ends of the trench strip via un-etched SG poly and metal via. The connection is not demonstrated in the figure), (d) forming the gate and isolation dielectric layer, (e) etching the SB metal trench, (f) forming the back side ohmic metal layer, (g) forming the front side ohmic metal layer and (h) forming the SB metal layer and then the top metal layer.

### **IV. CONCLUSION**

A novel SiC SGS-ATMOS with SG and integrated trench JBS diode is proposed and analyzed in this paper. Compared with the SiC Con-ATMOS, the proposed SGS-ATMOS demonstrates excellent static and dynamic performance in both MOSFET and diode modes. The simulation results show that the BFOM for the proposed SGS-ATMOS and Con-ATMOS with same parameters are  $8.22 \times 10^8$  W/cm<sup>2</sup> and  $5.23 \times 10^8$  W/cm<sup>2</sup>, respectively. Compared with the Con-ATMOS, the BFOM for the proposed device is improved by 57.2%. Meanwhile, compared with the Con-ATMOS, the  $C_{\rm gd}$ ,  $C_{\rm gs}$ ,  $Q_{\rm gd}$  and  $Q_{\rm g}$  are significantly reduced since the source-connected SG reduces the gate depth as well as decouples the interaction between the drain and gate. Compared with the Con-ATMOS, the HFFOM<sup>1</sup> ( $R_{on} \cdot C_{gd}$ ) and HFFOM<sup>2</sup> ( $R_{on} \cdot Q_{gd}$ ) for the proposed SGS- ATMOS are reduced by 92.5% and 58.8%, respectively. Contributed by the integrated trench JBS diode, the  $V_{\rm F}$ ,  $Q_{\rm rr}$  and  $I_{\rm rrm}$  of the diode are reduced from 3.10V,  $1.95\mu$ C/cm<sup>2</sup> and -68.0A for the Con-ATMOS to 1.56V,  $0.97\mu$ C/cm<sup>2</sup> and -35.9A for the proposed SGS-ATMOS at the  $J_D$  of -300A/cm<sup>2</sup>, respectively. The  $E_{on}$  and  $E_{off}$  of the SGS-ATMOS are 16.4mJ/cm<sup>2</sup> and 17.7mJ/cm<sup>2</sup>, which are 33.3% and 33.0% off compared with 24.6mJ/cm<sup>2</sup> and 26.4mJ/cm<sup>2</sup> for the Con-ATMOS, respectively. Meanwhile, the  $E_{on}$  and  $E_{off}$  of the SGS-ATMOS are also 33.6% and 30.0% off compared with 24.7mJ/cm<sup>2</sup> and 25.3mJ/cm<sup>2</sup> for the Con-ATMOS with external JBS diode, respectively. The temperature characteristics for the SGS-ATMOS are discussed and it is found that the proposed device exhibits good performance in high temperature and suitable for parallel usage. Finally, the dependence of the device performance on the SG dielectric parameters are also discussed for the SGS-ATMOS, which presents a further improvement direction for the proposed device.

### REFERENCES

- T. Kimoto, "Material science and device physics in SiC technology for high-voltage power devices," *Jpn. J. Appl. Phys.*, vol. 54, no. 4, pp. 1–27, Apr. 2015, doi: 10.7567/JJAP.54.040103.

- [2] J. Zhang, X. Luo, B. Zhang, and Z. Li, "Improved double-recessed 4H-SiC MESFETs structure with recessed source/drain drift region," *Microelectron. Eng.*, vol. 84, no. 12, pp. 2888–2891, Dec. 2007, doi: 10.1016/j.mee.2007.02.014.

- [3] J. Zhang, B. Zhang, and Z. Li, "Asymmetric 3D trigate 4H-SiC MESFETs with a recessed drain drift region," *Semicond. Sci. Technol.*, vol. 24, no. 4, pp. 1–5, Feb. 2009, doi: 10.1088/0268-1242/24/4/045001.

- [4] X. Deng et al., "A multiple-ring-modulated JTE Technique for 4H-SiC power device with improved JTE-dose window," *IEEE Trans. Electron Devices*, vol. 64, no. 12, pp. 5042–5047, Dec. 2017, doi: 10.1109/TED.2017.2761995.

- [5] X. Deng *et al.*, "Multizone gradient-modulated guard ring technique for ultrahigh voltage 4H-SiC devices with increased tolerances to implantation dose and surface charges," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 3, pp. 1505–1512, Sep. 2019, doi: 10.1109/JESTPE.2019.2910610.

- [6] X. Deng *et al.*, "High voltage SiC JBS diodes with multiple zone junction termination extension using single etching step," *Mater. Sci. Forum*, vols. 778–780, pp. 808–811, Feb. 2014, doi: 10.4028/www.scientific.net/MSF.778-780.808.

- [7] X. Li *et al.*, "Impact of termination region on switching loss for SiC MOSFET," *IEEE Trans. Electron Devices*, vol. 66, no. 2, pp. 1026–1031, Feb. 2019, doi: 10.1109/TED.2018.2888995.

- [8] X. Li et al., "A SiC power MOSFET loss model suitable for high-frequency applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8268–8276, Oct. 2017, doi: 10.1109/TIE.2017.2703910.

- [9] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications. Singapore: Wiley, 2014, pp. 150–165.

- [10] Y. Yonezawa, "Recent progress in high to ultra-high-voltage SiC power devices: Development and application," in *Proc. Int. Power Electron. Conf. (IPEC-Niigata-ECCE Asia)*, Niigata, Japan, 2018, pp. 3603–3606, doi: 10.23919/IPEC.2018.8507668.

- [11] S.-H. Ryu et al., "10-kV, 123-mΩ cm<sup>2</sup> 4H-SiC power DMOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 556–558, Aug. 2004, doi: 10.1109/LED.2004.832122.

- [12] P. M. Shenoy and B. J. Baliga, "The planar 6H-SiC ACCUFET: A new high-voltage power MOSFET structure," *IEEE Electron Device Lett.*, vol. 18, no. 12, pp. 589–591, Dec. 1997, doi: 10.1109/55.644080.

- [13] Y. Sui, T. Tsuji, and J. A. Cooper, "On-state characteristics of SiC power UMOSFETs on 115-μm drift layers," *IEEE Electron Device Lett.*, vol. 26, no. 4, pp. 255–257, Apr. 2005, doi: 10.1109/LED.2005.845495.

- [14] S. Harada, M. Kato, T. Kojima, K. Ariyoshi, Y. Tanaka, and H. Okumura, "Determination of optimum structure of 4H-SiC trench MOSFET," in *Proc. 24th Int. Symp. Power Semicond. Devices ICs*, Bruges, Belgium, 2012, pp. 253–256, doi: 10.1109/ISPSD.2012.6229071.

- [15] J. Tan, J. A. Cooper, and M. R. Melloch, "High-voltage accumulationlayer UMOSFET's in 4H-SiC," *IEEE Electron Device Lett.*, vol. 19, no. 12, pp. 487–489, Dec. 1998, doi: 10.1109/55.735755.

- [16] Q. Zhang, M. Gomez, C. Bui, and E. Hanna, "1600V 4H-SiC UMOSFETs with dual buffer layers," in *Proc. 17th Int. Symp. Power Semicond. Devices ICs*, Santa Barbara, CA, USA, 2005, pp. 211–214, doi: 10.1109/ISPSD.2005.1487988.

- [17] Y. Wang, K. Tian, Y. Hao, C.-H. Yu, and Y.-J. Liu, "An optimized structure of 4H-SiC U-shaped trench gate MOSFET," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2774–2778, Sep. 2015, doi: 10.1109/TED.2015.2449972.

- [18] Y. Nakano, R. Nakamura, H. Sakairi, S. Mitani, and T. Nakamura, "690V, 1.00 mΩcm<sup>2</sup> 4H-SiC double-trench MOSFETs," in *Proc. Int. Conf. Silicon Carbide Related Mater.*, vols. 717–720, May 2012, pp. 1069–1072. [Online]. Available: www.scientific.net/MSF.717-720.1069

- [19] T. Nakamura *et al.*, "High performance SiC trench devices with ultralow ron," in *Proc. Int. Electron Devices Meeting*, Washington, DC, USA, 2011, pp. 1–3, doi: 10.1109/IEDM.2011.6131619.

- [20] B. J. Baliga, Fundamentals of Power Semiconductor Devices. New York, NY, USA: Springer, 2008, pp. 14–447.

- [21] X. Deng *et al.*, "Investigation and failure mode of asymmetric and double trench SiC MOSFETs under avalanche conditions," *IEEE Trans. Power Electron.*, vol. 35, no. 8, pp. 8524–8531, Aug. 2020, doi: 10.1109/TPEL.2020.2967497.

- [22] D. Peters et al., "The new CoolSiC<sup>TM</sup> trench MOSFET technology for low gate oxide stress and high performance," in Proc. PCIM Eur. Int. Exhibit. Conf. Power Electron. Intell. Motion Renew. Energy Energy Manage., Nuremberg, Germany, 2017, pp. 1–7.

- [23] R. Siemieniec *et al.*, "A SiC trench MOSFET concept offering improved channel mobility and high reliability," in *Proc. 19th Eur. Conf. Power Electron. Appl. (EPE ECCE Europe)*, Warsaw, Poland, 2017, pp. 1–13, doi: 10.23919/EPE17ECCEEurope.2017.8098928.

- [24] W. Ni et al., "Study of asymmetric cell structure tilt implanted 4H-SiC trench MOSFET," *IEEE Electron Device Lett.*, vol. 40, no. 5, pp. 698–701, May 2019, doi: 10.1109/LED.2019.2908253.

- [25] M. Furukawa et al., "Improved reliability of 1.2kV SiC MOSFET by preventing the intrinsic body diode operation," in Proc. PCIM Eur. Digit. Days Int. Exhibit. Conf. Power Electron. Intell. Motion Renew. Energy Energy Manage., 2020, pp. 1–5.

- [26] K. Kawahara *et al.*, "6.5 kV schottky-barrier-diode-embedded SiC-MOSFET for compact full-unipolar module," in *Proc. 29th Int. Symp. Power Semicond. Devices IC's (ISPSD)*, Sapporo, Japan, 2017, pp. 41–44, doi: 10.23919/ISPSD.2017.7988888.

- [27] T. Tominaga et al., "Superior switching characteristics of SiC-MOSFET embedding SBD," in Proc. 31st Int. Symp. Power Semicond. Devices ICs (ISPSD), Shanghai, China, 2019, pp. 27–30, doi: 10.1109/ISPSD.2019.8757664.

- [28] H. Jiang *et al.*, "SiC MOSFET with built-in SBD for reduction of reverse recovery charge and switching loss in 10-kV applications," in *Proc. 29th Int. Symp. Power Semicond. Devices IC's (ISPSD)*, Sapporo, Japan, 2017, pp. 49–52, doi: 10.23919/ISPSD.2017.7988890.

- [29] H. Jiang, J. Wei, X. Dai, M. Ke, C. Zheng, and I. Deviny, "Silicon carbide split-gate MOSFET with merged Schottky barrier diode and reduced switching loss," in *Proc. 28th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Prague, Czech Republic, 2016, pp. 59–62, doi: 10.1109/ISPSD.2016.7520777.

- [30] X. Li et al., "SiC trench MOSFET with integrated selfassembled three-level protection Schottky barrier diode," *IEEE Trans. Electron Devices*, vol. 65, no. 1, pp. 347–351, Jan. 2018, doi: 10.1109/TED.2017.2767904.

- [31] T. Dai *et al.*, "4H-SiC trench MOSFET with integrated fast recovery MPS diode," *Electron. Lett.*, vol. 54, no. 3, pp. 167–169, Feb. 2018, doi: 10.1049/el.2017.3198.

- [32] Y. Kobayashi *et al.*, "Body PiN diode inactivation with low on-resistance achieved by a 1.2 kV-class 4H-SiC SWITCH-MOS," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2017, pp. 1–4, doi: 10.1109/IEDM.2017.8268356.

[33] R. Aiba *et al.*, "Experimental demonstration on superior switching

- [33] R. Aiba *et al.*, "Experimental demonstration on superior switching characteristics of 1.2 kV SiC SWITCH-MOS," in *Proc. 31st Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Shanghai, China, 2019, pp. 23–26, doi: 10.1109/ISPSD.2019.8757628.

- [34] R. Aiba, K. Matsui, M. Baba, S. Harada, H. Yano, and N. Iwamuro, "Demonstration of superior electrical characteristics for 1.2 kV SiC Schottky barrier diode-wall integrated trench MOSFET with higher Schottky barrier height metal," *IEEE Electron Device Lett.*, vol. 41, no. 12, pp. 1810–1813, Dec. 2020, doi: 10.1109/LED.2020.3031598.

- [35] ATLAS User's Manual: Device Simulation Software, Silvaco Inc., Santa Clara, CA, USA, 2015.

- [36] X. Deng, X. Xu, X. Li, X. Li, Y. Wen, and W. Chen, "A novel SiC MOSFET embedding low barrier diode with enhanced third quadrant and switching performance," *IEEE Electron Device Lett.*, vol. 41, no. 10, pp. 1472–1475, Oct. 2020, doi: 10.1109/LED.2020.3017650.

- [37] G. Wang, J. Mookken, J. Rice, and M. Schupbach, "Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications," in *Proc. IEEE Appl. Power Electron. Conf. Exposit. (APEC)*, Fort Worth, TX, USA, 2014, pp. 1478–1483, doi: 10.1109/APEC.2014.6803502.

- [38] Z. Wang *et al.*, "Shield gate trench MOSFET with narrow gate architecture and low-k dielectric layer," *IEEE Electron Device Lett.*, vol. 41, no. 5, pp. 749–752, May 2020, doi: 10.1109/LED.2020.2981484.

- [39] R. Wang, X. Li, M. Qiao, X. Zhou, T. Wang, and B. Zhang, "Total ionizing dose effects in 30-V split-gate trench VDMOS," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 9, pp. 2009–2014, Sep. 2020, doi: 10.1109/TNS.2020.2965286.