# A Novel Soft-Switched PWM Inverter for AC Motor Drives

Shaotang Chen, Student Member, IEEE, and Thomas A. Lipo, Fellow, IEEE

Abstract—A novel soft-switched inverter topology is derived from the passively clamped quasi-resonant link (PCQRL) circuit. By introducing magnetic coupling between the two resonant inductors, the number of auxiliary switches can be reduced from two to one, and only a single magnetic core is required for the resonant dc link. An analysis of this novel PCQRL topology with coupled inductors is presented to reveal the various soft-switching characteristics. In comparison with the conventional passively clamped, continuously resonant dc link inverter, this soft-switched inverter can reduce voltage stresses from more than 2 per unit (pu) to 1.1–1.3 pu. It can also provide soft-switched pulse-width modulated (PWM) operation. Simulation and experiment are performed to backup the analysis.

#### I. INTRODUCTION

THE EMERGENCE of soft-switched topologies for power conversion has brought new perspectives to high-performance inverter design. In particular, the resonant dc link converters [1]–[4], which promise to be the next generation of industrial drives, have received considerable research interest. A more recent trend seems to have evolved from continuously resonant to quasi-resonant strategies owing to the various benefits regarding resonant link design and control, device rating requirements, and compatibility to pulsewidth modulated (PWM) and other conventional drive control techniques [5]–[12].

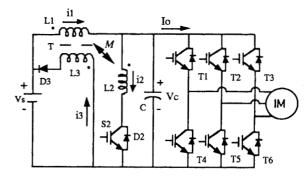

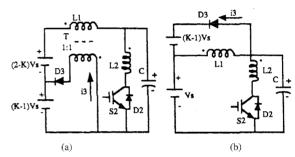

A new type of soft-switched voltage source inverter—the passively clamped quasi-resonant link (PCQRL) inverter—had been proposed in [13]. The PCQRL topology has the advantages of low clamp factor, simple resonance control, guaranteed zero link voltage conditions, and PWM capabilities. However, the penalties are the relatively high device count associated with the auxiliary switched inductor circuit and the high reverse voltage requirement for the clamp diode. A solution to the drawback of large device count is the introduction of magnetic coupling between the two resonant inductors by making them share the same magnetic core, as shown in Fig. 1. With magnetic coupling the current in the auxiliary inductor  $L_2$  can reverse during the resonant transient, which makes it possible to use only one switch to control the operation of the auxiliary circuit. Thus, the device count for the auxiliary switched inductor circuit is reduced from two switches and one separate inductor to only one switch and an additional coil in the main resonant inductor/transformer. Other advantages include the feedback of resonant energy

Manuscript received December 28, 1994; revised February 22, 1996. The authors are with the Department of Electrical and Computer Engineering, University of Wisconsin-Madison, Madison, WI 53706-1691 USA. Publisher Item Identifier S 0885-8993(96)05161-7.

Fig. 1. Passively clamped quasi-resonant dc link inverter with coupled inductors.

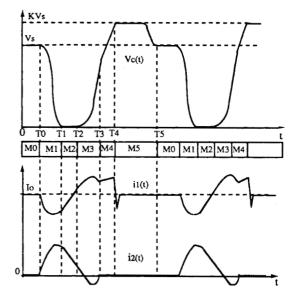

Fig. 2. Resonant link waveforms.

through magnetic coupling back to the dc bus. Thus, the stresses of clamping will be further relieved.

The operation and the control requirement of the new quasi-resonant inverter with coupled inductive feedback is presented in this paper. A detailed analysis of the topology is also performed to reveal the characteristics of the inverter. Simulation and experiment are performed to backup the theory.

# II. OPERATION PRINCIPLES AND ANALYSIS

The operation of the link can be explained by referring to Figs. 1 and 2. Initially, the auxiliary switch  $S_2$  is off and the

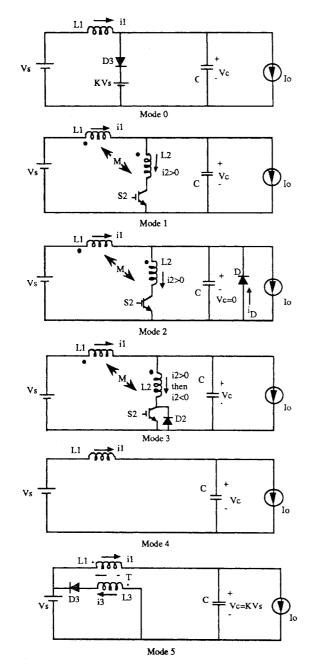

Fig. 3. Equivalent circuit for mode analysis.

auxiliary circuit is disconnected from the inverter main power circuit. Once powered-up, the resonance between inductor  $L_1$  and capacitor C drives the capacitor voltage up toward  $2V_s$  until it is clamped at  $KV_s$ . Since the clamp factor, K, is less than 2 per unit (pu), the resonance between  $L_1$  and C will limit the capacitor voltage,  $V_c$ , between  $(2-K)V_s$  and  $KV_s$ , which will gradually damp toward  $V_s$  due to resonant losses. Thus, the capacitor voltage will be maintained near  $V_s$  as long as the auxiliary circuit is not switched on. This state is so called the pseudo steady-state mode  $O(M_0)$ . Assume at time  $T_0$ , a PWM switching command for the switching of the inverter poles is given. To initiate a resonant transient, the auxiliary

switch  $S_2$  is first turned on in a zero current-switching manner. With  $S_2$  on, the resonance between  $L_1, L_2$ , and C causes the capacitor to discharge and pulls down the link voltage toward a negative value. The process is called mode 1  $(M_1)$ . When capacitor voltage reaches zero, the antiparallel diodes in the inverter legs conduct and the link voltage is clamped at zero-voltage condition or mode 2  $(M_2)$ . The zero-voltage condition can be maintained for a short period of time determined by the link parameters. During mode 2, the inverter poles can then perform the commanded switching at zero-voltage condition. In the mean time, the magnetic coupling between inductors  $L_1$  and  $L_2$  causes the current in the antiparallel diodes to decrease.

Once the current in the antiparallel diodes becomes zero, the zero-voltage condition is removed, and the link resonance between  $L_1, L_2$  and C regains control and automatically charges up the capacitor voltage. This process is indicated as mode 3  $(M_3)$ . In mode 3, owing to the magnetic coupling, inductor current  $i_2$  will reverse its direction and diode  $D_2$ becomes conducting. The switch  $S_2$  is then turned off in a zero-voltage switching manner. Mode 3 ends when current  $i_2$ decreases to zero and diode  $D_2$  turns off. This result means that the auxiliary circuit is automatically disconnected from the main power circuit at the end of mode 3. In mode 4, the resonance between  $L_1$  and C keeps driving the link voltage up to the clamp voltage  $KV_s$ . At this moment, clamp period  $(M_5)$  starts to feedback excessive resonant energy to the dc source through the clamp diode  $D_3$ . After mode 5, link returns to pseudo steady-state mode 0. The same resonant cycle will repeat if another PWM command is given.

An analysis of the link operation can be performed based on the equivalent circuits shown in Fig. 3. The main results are given as follows:

Mode 0) Pseudo Steady-State ( $S_2$  off and  $D_2$  off;  $D_3$  off): The link states are approximated by

$$v_c(t) = V_s \tag{1}$$

$$i_1(t) = I_0 \tag{2}$$

$$i_2(t) = 0. (3)$$

Mode 1) Link Voltage Ramps Down ( $S_2$  on and  $D_2$  off;  $D_3$  off): The resonant transient is initiated and link resonance between  $L_1, L_2$ , and C occurs. Based on the equivalent circuit in Fig. 3(b), the link current and voltage can be derived as

$$v_{c}(t) = \frac{V_{S}}{L_{1} + L_{2} + 2M} [(L_{2} + M) + (L_{1} + M)\cos\omega_{1}(t - T_{0})]$$

$$i_{1}(t) = I_{o} + \frac{V_{S}}{\omega_{1}(L_{1} + L_{2} + 2M)}$$

$$\cdot \left[\omega_{1}(t - T_{0}) - \frac{(L_{1} + M)(L_{2} + M)}{L_{1}L_{2} - M^{2}} \sin\omega_{1}(t - T_{0})\right]$$

$$i_{2}(t) = \frac{V_{S}}{\omega_{1}(L_{1} + L_{2} + 2M)}$$

$$\cdot \left[\omega_{1}(t - T_{0}) + \frac{(L_{1} + M)^{2}}{L_{1}L_{2} - M^{2}} \sin\omega_{1}(t - T_{0})\right]$$

$$(6)$$

where

$$\omega_1 = \frac{1}{\sqrt{L_{12}C}}$$

$$L_{12} = \frac{L_1L_2 - M^2}{L_1 + L_2 + 2M}$$

and

$$M = k\sqrt{L_1 L_2} \qquad (k \neq 1) \tag{7}$$

with k being the coupling coefficient.

Mode 2) Zero Link Voltage Condition ( $S_2$  on and  $D_2$  off;  $D_3$  off; antiparallel diodes on):

$$v_c(t) = 0 (8)$$

$$i_1(t) = i_1(T_1) + \frac{L_2 V_s}{L_1 L_2 - M^2} (t - T_1)$$

(9)

$$i_2(t) = i_2(T_1) - \frac{MV_s}{L_1L_2 - M^2}(t - T_1).$$

(10)

The total current in the antiparallel diodes is

$$i_d(t) = -\frac{(M+L_2)V_s}{L_1L_2 - M^2}(t - T_1) + \frac{\sqrt{(L_1 + L_2 + 2M)(L_1 - L_2)}}{L_1L_2 - M^2} \frac{V_s}{\omega_1}.$$

(11)

Setting (11) equal to zero gives the duration of mode 2

$$\Delta T_2 = \frac{1}{\omega_1} \sqrt{\left(\frac{L_1 + M}{L_2 + M}\right)^2 - 1}.$$

(12)

The clamp diode  $D_3$  will suffer from the highest reverse voltage, which is

$$V_{d3} = \left(1 + \frac{1}{K - 1}\right)V_s = \frac{K}{K - 1}V_s. \tag{13}$$

Mode 3) Link Ramps Up—Stage 1 ( $S_2$  on then off, and  $D_2$  off then on;  $D_3$  off): Resonance caused by  $L_1, L_2$  and C charges link capacitor C.

$$v_c(t) = \frac{(L_2 + M)}{L_1 + L_2 + 2M} V_s [1 - \cos \omega_1 (t - T_2)]$$

$$i_1(t) = i_1(T_2) + \frac{V_s}{\omega_1 (L_1 + L_2 + 2M)}$$

(14)

$$\omega_1(L_1 + L_2 + 2M)$$

$$\cdot \left[\omega_1(t - T_2) + \frac{(L_2 + M)^2}{(L_1 L_2 - M^2)} \sin \omega_1(t - T_2)\right] \quad (15)$$

$$\begin{split} i_2(t) &= i_2(T_2) + \frac{V_s}{\omega_1(L_1 + L_2 + 2M)} \\ &\cdot [\omega_1(t - T_2) - \frac{(M + L_1)(M + L_2)}{L_1L_2 - M^2} \sin \omega_1(t - T_2)]. \end{split}$$

Note that  $i_2(t)$  will become negative if a proper value of M and thus k is chosen. Usually, a value of k equal to 0.75–0.95 will be able to ensure that  $i_2(t)$  reverses its direction. It should be pointed out that the above analysis assumes the link load current  $I_o$  is constant even after the inverter switches change states. In reality, however,  $I_o$  may varies after switching. The actual waveforms of  $V_c, i_1$  and  $i_2$  will not necessarily follow (14)–(16). A simulation is usually performed to study the influence of dc link load current change, as will be discussed in Section IV.

Mode 4) Link Ramps Up—Stage 2 ( $S_2$  off and  $D_2$  off, and  $D_3$  off): Resonance of  $L_1$  and C keeps charging capacitor C. Thus

$$v_{c}(t) = V_{s} - (V_{s} - v_{c}(T_{3})) \cos \omega_{2}(t - T_{3})$$

$$+ \frac{\omega_{1}(L_{2} + M)}{\omega_{2}(L_{1} + L_{2} + 2M)} V_{s} \sin \omega_{1}(T_{3} - T_{2})$$

$$\cdot \sin \omega_{2}(t - T_{3}) \qquad (17)$$

$$i_{1}(t) = I_{o} + \frac{V_{s} - v_{c}(T_{3})}{Z} \sin \omega_{2}(t - T_{3})$$

$$+ \frac{(L_{2} + M)}{(L_{1} + L_{2} + 2M)} \frac{V_{s}}{Z} \sin \omega_{1}(T_{3} - T_{2})$$

$$\cdot \cos \omega_{2}(t - T_{3}) \qquad (18)$$

where

$$\omega_2 = \frac{1}{\sqrt{L_1 C}}$$

and

$$Z = \sqrt{\frac{L_1}{C}}.$$

Mode 5) Clamp Action ( $S_2$  and  $D_2$  off;  $D_3$  on): Clamp action occurs when link voltage reaches  $KV_8$

$$V_c(t) = KV_S \tag{19}$$

$$i_1(t) = I_o. (20)$$

## III. LINK DESIGN AND CONTROL SCHEME

The design of the PCQRL topology with coupled inductors as shown in Fig. 1 first involves the selection of parameters  $L_1, L_2, C$ , and k or M to satisfy desired link waveform specifications such as dv/dt, di/dt, clamp factor K, peak currents in  $L_1$  and  $L_2$ , and the period of zero voltage. Given a desired clamp factor K, the turn ratio of the clamp transformer is readily determined to be equal to 1/(K-1). By choosing a coupling coefficient k between  $L_1$  and  $L_2$  equal to 0.75-0.95 and a link capacitor C equal to 60-100 nF, the values of  $L_1$  and  $L_2(< L_1)$  are then estimated based on the dv/dt parameters. Usually, a simulation or calculation based on (1)-(20) is required to adjust the link parameters and to verify that the design specifications are met.

For a prototype inverter design, a 320-V dc bus is used. A set of parameters has been chosen as  $L_1=28.89~\mu\mathrm{H}, L_2=11.8~\mu\mathrm{H}, C=80~\mathrm{nF},$  and k=0.9. The turn ratio between  $L_1$  and  $L_3$  is designed as 1:5 to realize a desirable voltage clamp factor K=1.2. The magnetic coupling between  $L_1$  and  $L_2$  is achieved by making  $L_2$  share the same magnetic core with  $L_1$  and  $L_3$ .

To ensure voltage clamping at  $KV_s$ , the leakage inductance between  $L_1$  and  $L_3$  has to be minimized. Thus, the two windings of  $L_1$  and  $L_3$  are made using a coaxial structure as discussed in [14]. The coaxial winding transformer structure gives a measured leakage inductance as low as 80 nH.

In comparison with all other resonant link inverters, the new topology appears to provide the simplest control requirement to realize soft-switched PWM modulation. Only a minimal revision to an ordinary PWM control scheme is required.

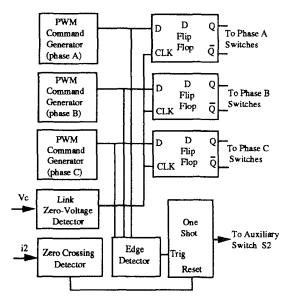

Fig. 4. Control circuit diagram for soft-switched PWM modulation.

In Fig. 4, the block diagram for soft-switched PWM control of the inverter is included. The PWM command generator could be a space vector or a sine-triangle PWM. The state changes of PWM modulation commands are first detected by the edge detector, which generates a turn-on signal to the auxiliary switch  $S_2$  to initiate a resonant transient. When the link voltage reaches zero, the zero-voltage detector outputs a signal to clock-in PWM commands to the inverter switches. It synchronizes the command with the zero link instant so that the inverter only switches at zero-voltage conditions. In the mean while, the zero crossing detector senses the current reversal in inductor  $L_2$  to output a turn-off signal to switch  $S_2$ .

As is evident from control circuit shown in Fig. 4, the operation of the link relies on a link zero-voltage detector to indicate soft-switching instants and a current sensor to measure the current reversal in the auxiliary switch  $S_2$ . Therefore, more complicated control is required in comparison with hard switching.

## IV. SIMULATION AND EXPERIMENTAL RESULTS

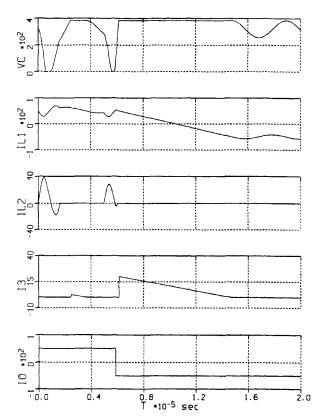

A simulation based on above link parameters in the prototype design was performed to verify the analysis and to reveal the link performance at various load conditions. At t=0, the initial current in  $L_1,i_1$ , and the dc link load current,  $I_o$ , are both equal to 50 A. The initial capacitor voltage was set to 320 V. The auxiliary switch  $S_2$  is turned on at t=0. The simulated link voltage and current waveforms are shown in Fig. 5. It can be observed that link voltage  $V_c$  begins to ramp down. The fall time for the link voltage is about 800 ns. The zero link voltage condition, which is utilized for soft switching of inverter poles, is maintained for about 400 ns before the link voltage automatically again rises. The rise time for the link voltage is more than 1.5  $\mu$ s. It is important to mention that these waveform dv/dt parameters are very desirable for better utilization of the IGBT switching characteristics. The

Fig. 5. Simulated link waveforms with dc link current reversal.

link voltage produces a dv/dt of about 500 V/ $\mu$ s, a desirable value often recommended by the industry.

The worst operating condition for resonant link is when a reversal of dc link current,  $I_o$ , happens during mode 3. A link current reversal from positive 50 A to negative 50 A, as shown in Fig. 5, is simulated. It is seen that the rising edge dv/dt becomes much larger due to capacitor charge-up by the reversed link current. However, the current in auxiliary switch,  $i_2$ , is not, in fact, affected. Most of the energy is fed back through the clamp winding to the dc source. This is an advantage over the active clamp resonant link where the possibility of link load current reversal causes the clamp switch to be rated at a much high rating.

Due to the quasi-resonant or the so-called resonant transition property, all these waveforms suggest a small resonant duty cycle and small peak resonant currents. It is apparent that the resonant energy circulating inside this quasi-resonant converter will be considerably smaller than the conventional continuous resonant dc link converters.

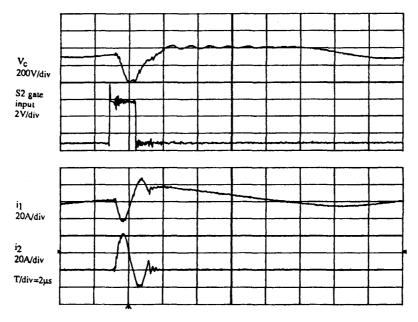

Based on the above link parameters, the novel quasiresonant inverter topology of Fig. 1 with a 320-V dc bus was constructed. The dc bus voltage was provided by a three-phase rectifier in the experiment. The auxiliary switch,  $S_2$ , is turned on whenever a resonant transient is required for zero-voltage switching, while its turn-off is based on the current reversal in inductor  $L_2$ . Fig. 6 records the capacitor voltage  $V_c$ , switch  $S_2$  gate driver input signal, and inductor  $L_1$  and  $L_2$  currents. The experimental measurement of link waveforms shows good

Fig. 6. Measured resonant link waveforms. DC bus voltage = 341.7 V.

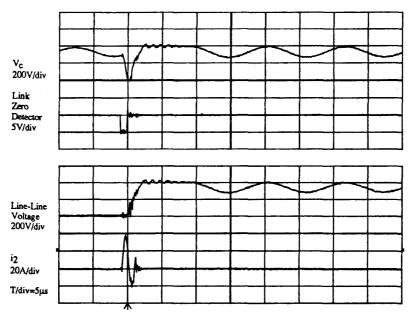

Fig. 7. Zero-voltage switching of inverter switches. DC bus voltage = 341.7 V.

agreement with simulation results. In particular, the clamp factor K achieved is seen to be well confined below 1.25, which is very close to the designed specification of 1.2.

The soft switching characteristic of the inverter can be seen from Fig. 7, which shows the resonant link voltage  $V_c$ , link zero-voltage detector output, and line to line voltage and inductor  $L_2$  current. A link zero-voltage detector circuit is used to detect the instant when capacitor voltage  $V_c$  reaches zero. The zero-voltage condition is indicated by the rising edge of the detector output. This zero-voltage conditions are employed to initiate the soft switching of the six inverter switches. The experimental measurement of the inverter output line to line voltage in Fig. 7 shows that the line to line voltage

changes are clearly in synchronization with the link zero-voltage conditions. Therefore, zero turn-on losses are realized in the inverter.

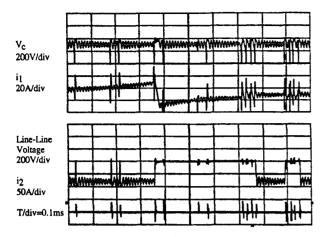

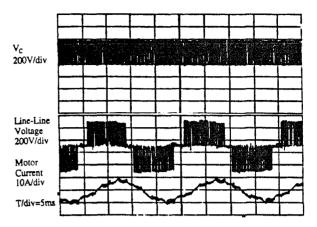

To demonstrate its PWM operation, a three-phase sine-triangle PWM command generator was implemented as in Fig. 4 to control the six inverter switches. The triangle carrier or the inverter switching frequency is 5 KHz. The output of the soft-switched inverter is connected directly to a three-phase, 240-V induction motor rated at 3 horse power. Fig. 8 plots the PWM link waveforms when the motor is operating under zero mechanical load. The curves shows that the inverter behaves satisfactorily over all operation conditions of a typical motor—inverter drive system.

Fig. 8. Pulse-width modulated link waveforms with a motor load. DC bus voltage = 320~V.

As can be observed from Figs. 7 and 8, after the clamping or during mode 0, there exists a lot of ripple from  $KV_s$  to  $(2-K)V_s$  in the link voltage waveform, although the average voltage is equal to  $V_s$ . The ripple is actually caused by the resonance between  $L_1$  and C. This is why mode 0 is called pseudo steady-state. However, in comparison with continuous resonant dc Link inverters where the ripple goes from  $2V_s$  to zero, its influence is much less in the PCQRL inverters because K is very close to one.

The motor line to line voltage and phase current, together with the link voltage, are also shown in Fig. 9. It is seen that there is some distortion in the motor current. One reason for the distortion is accounted by the distortion present in the reference signals of the sine and triangle waveforms of the present controller. Another reason, however, has to be attributed to the minimum link pulse requirement in the resonant inverter. In fact, every time after  $S_2$  is turned on and a resonant transient is initiated, it can not be turned on again in less than a certain minimum period. In the experimental design, a 10-µs minimum pulse limitation has been imposed. Due to the pulse limitation, those state changes in the PWM command that occur less than 10  $\mu$ s after a previous change is made will be ignored by the control circuit. Some modification to the sine-triangle PWM is needed to prevent consecutive state changes that are less than a minimum pulse period apart. Another solution to the problem is to use space vector PWM modulation, which would incorporate the minimum pulse requirement. Research on these aspects of quasiresonant converter control is continuing.

## V. RELATED TOPOLOGIES

The problem with high reverse voltage in the clamp diode can be elegantly solved in the case of battery source operation such as in electric vehicle drives. In fact, with a battery source, the clamp diode can be connected to a low voltage battery group with a voltage equal to  $(K-1)V_s$ , as shown in Fig. 10(a), where K is the desired link clamp factor. In this case, the turn ratio of the clamp transformer, T, can be designed to be 1:1 instead of the original 1:1/(K-1). Therefore, the maximum reverse voltage of clamp diode

Fig. 9. Motor line to line voltage and phase current. DC bus voltage = 320 V

Fig. 10. Different clamps for battery power sources (a) with 1:1 clamp transformer and (b) with diode clamp

becomes only  $2V_s$  instead of the previous value  $(1+1/(K-1))V_s$ .

Another even more simplified structure, which is also of considerable practical interest, can be derived by connecting the clamp diode directly to a separate low voltage dc source, as shown in Fig. 10(b). To implement this diode-clamped quasi-resonant link, the low voltage dc source shown can be a separate low-voltage battery in the case of electric vehicles. In the case of a diode bridge rectifier, a capacitor and a dc-to-dc regulator to maintain its voltage could be a practical solution as the cost and switching losses for such a low-power dc-to-dc converter may be less than those of the passive clamp transformer.

## VI. CONCLUSION

The PCQRL inverter is able to provide an optimal structure for soft switching with low device ratings, simple topology, easy link implementation, and control. The PCQRL topology yields the smallest device count by introducing magnetically coupled inductors in a single core. A simplification that does not require a complicated clamp transformer is also offered for practical implementation. The operation principles and link resonance control of the novel PCQRL inverter with coupled inductors are investigated. Link waveforms and operation modes are analyzed to reveal various soft switching characteristics. Successful operation of this novel PCQRL inverter with coupled inductors was demonstrated both in simulation and in an experimental implementation.

#### REFERENCES

- [1] D. M. Divan, "The resonant dc link inverter-A new concept in static power conversion," in *IEEE-IAS Annual Conf. Rec.*, 1986, pp. 648–656. Y. Murai and T. A. Lipo, "High frequency series resonant dc link power

- conversion," in *IEEE-IAS Annual Conf. Rec.*, 1988, pp. 772–779.

[3] D. M. Divan and G. Skibinski, "Zero switching loss inverters for high

- power applications," in *IEEE-IAS Annual Conf. Rec.*, 1987, pp. 627–634.

[4] A. Mertens and D. M. Divan, "A high frequency resonant dc link inverter

- using IGBTs," in IPEC, Tokyo, Japan, 1990, pp. 152-160. [5] W. McMurray, "Resonant snubbers with auxiliary switches," in IEEE-

- IAS Annual Conf. Rec., 1989, pp. 829-834. [6] R. W. DeDoncker, and P. J. Lyons, "The auxiliary resonant commutated

- pole converter," in IEEE-IAS Annual Conf. Rec., 1990, pp. 1228-1235. [7] J. He and N. Mohan, "Parallel resonant dc link circuit—A novel zero switching loss topology with minimum voltage stresses," in IEEE-PESC Conf. Rec., 1989, pp. 1006-1012.

- [8] J. G. Cho, H. S. Kim, and G. H. Cho, "Novel soft switching PWM converter using a new parallel resonant dc-link," in IEEE-PESC Conf. Rec., 1991, pp. 241–247

- R. W. DeDoncker and J. P. Lyons, "The auxiliary quasi-resonant dc link inverter," in IEEE-PESC Conf. Rec., 1991, pp. 248-253.

- [10] G. Skibinski, "The design and implementation of a passive clamp resonant dc link inverter for high power application," Ph.D. thesis, Univ. of Wisconsin-Madison, 1992.

- [11] L. Malesani, P. Tenti, P. Tamasin, and V. Toigo, "High efficiency quasi resonant dc link converter for full-range PWM," in IEEE-APEC Conf. Rec., 1992, pp. 472–478.

[12] J. W. Choi and S. K. Sul, "Resonant link bidirectional power converter

- without electrolytic capacitor," in IEEE-PESC Conf. Rec., 1993, pp. 293-299.

- [13] S. Chen and T. A. Lipo "A passively clamped quasi resonant dc link inverter," in IAS Ann. Conf. Rec., 1994, vol. 2, pp. 841-848.

- [14] M. S. Rauls, D. W. Novotny, and D. M. Divan, "Design considerations for high frequency co-axial winding power transformers," in IEEE-IAS Ann. Conf. Rec., 1991, pp. 946-952.

Shaotang Chen (S'93) received the B.Eng. and the M.Eng. degrees from the Central China University of Science and Technology, Wuhan, China, in 1983 and 1986, respectively. He received the M.S. and Ph.D. degrees from the University of Wisconsin, Madison, in 1993 and 1995, respectively.

He was with the Central China University of Science and Technology, Wuhan, China, from 1986 to 1991. He is currently with the Research and Development Center, General Motors, Warren, MI. His research interests are in control of electric

machines, electric machine drives, and power electronics.

Thomas A. Lipo (M'64-SM'71-F'87) is a native of Milwaukee, WI.

From 1969 to 1979 he was an Electrical Engineer in the Power Electronics Laboratory of Corporate Research and Development of the General Electric Company, Schenectady, NY. He became Professor of Electrical Engineering at Purdue University in 1979, and in 1981 he joined the University of Wisconsin in the same capacity, where he is presently the W. W. Grainger Professor for Power Electronics and Electrical Machines.

He has received the Outstanding Achievement Award from the IEEE Industry Applications Society, the William E. Newell Award of the IEEE Power Electronics Society, and the 1995 Nicola Tesla IEEE Field Award from the IEEE Power Engineering Society for his work. Over the past 30 years he has served IEEE in numerous capacities, including President of the Industrial Applications Society.