# A Physical Alpha-Power Law MOSFET Model

Keith A. Bowman, Blanca L. Austin, John C. Eble<sup>\*</sup>, Xinghai Tang, and James D. Meindl

Georgia Institute of Technology Atlanta, GA 30332-0269 Phone: (404) 894-9910 FAX: (404) 894-0462 \*Compaq Corporation Shrewsbury, MA 01545 E-mail: gt6078a@prism.gatech.edu

# Abstract<sup>†</sup>

A new compact physics-based Alpha-Power Law MOSFET Model is introduced to enable projections of low power circuit performance for future generations of technology by linking the simple mathematical expressions of the original Alpha-Power Law Model with their physical origins. The new model, verified by HSPICE simulations and measured data, includes: 1) a subthreshold region of operation for evaluating the on/off current trade-off that becomes a dominant low power design issue as technology scales, 2) the effects of vertical and lateral high field mobility degradation and velocity saturation, and 3) threshold voltage roll-off. Model projections for MOSFET CV/I indicate a 2Xperformance opportunity compared to NTRS extrapolations for the 250, 180, and 150nm generations subject to maximum leakage current estimates of the roadmap. NTRS and model calculations converge at the 70nm technology generation, which exhibits pronounced on/off current interdependence for low power gigascale integration (GSI).

## **1. Introduction**

The Alpha-Power Law MOSFET Model [1] is the most widely utilized compact drain current model due to its simple mathematical form and high degree of accuracy. The model has been used to derive many expressions for evaluating circuit performance. However, due to its empirical nature, the parameters of the model are measured values, which largely precludes projections of circuit performance for future generations of technology. Moreover, the model does not describe the subthreshold region and therefore on/off drain current trade-offs cannot be thoroughly analyzed. The Low Power Transregional

MOSFET Model [2] describes all regions of operation (subthreshold, triode, and saturation). The drain current equations are rigorously derived and provide insight into the physical basis of MOSFET behavior. Therefore, the Low Power Transregional Model is an advantageous choice for predicting performance of future technology generations and in particular for analyzing on/off drain current trade-offs. The disadvantage of the Low Power Transregional Model is its relatively complex drain current equations. Coupling the Alpha-Power Law and Low Power Transregional models enables a new compact physicsbased Alpha-Power Law MOSFET Model. Salient features of this new model include: 1) extension into the subthreshold region of operation, 2) the effects of vertical and lateral high field mobility degradation and velocity saturation, and 3) threshold voltage roll-off. Therefore, the new Physical Alpha-Power Law Model enables compact projections and physical insight into future circuit performance for low power GSI.

#### 2. Model Derivation

The new *Physical* Alpha-Power Law Model is derived by coupling the simple empirical Alpha-Power Law MOSFET Model [1] and the more complex physics-based Low Power Transregional MOSFET Model [2]. The derivation of the new model begins by equating the saturation drain current of the Alpha-Power Law Model [1], (1), and the Low Power Transregional Model [2], (2).

$$I_{D0} \left| \frac{V_{GS} - V_T}{V_{DD} - V_T} \right|_{\alpha}^{\alpha} = I_{D_{SAT}}$$

(1)

where  $I_{D0}$  (5) is a modified drive current that includes an effective mobility dependence on  $V_{GS}$ . Neglecting the small weak inversion contribution and performing a three term binomial expansion of the bulk charge terms in  $I_{D_{SAT}}$ ,

the Low Power Transregional Model's saturation drain current [2] may be simplified as

$$I_{D_{SAT}} \approx \frac{\partial W}{L_{C}} V_{DS_{SAT}} V_{DS_{SAT}} V_{T} - \frac{\partial \eta}{2} V_{DS_{SAT}}$$

(2)

where (W/L) is the channel width-to-length ratio,  $C_{OX}$  is the gate oxide capacitance per unit area,  $\mu_{eff}$  is the effective mobility including vertical [3] and lateral [4] high field degradation effects given as

$$\mu_{\text{eff}} = \frac{\mu_0}{\left[1 + \theta \right] V_{\text{GS}} - V_{\text{T}} \left[ \left[1 + V_{\text{DS}_{\text{SAT}}} \right] \right] E_{\text{C}} L \left[ \right]}, \quad (3)$$

<sup>&</sup>lt;sup>†</sup>This work is supported by the Semiconductor Research Corporation (Contract: SJ-374) and the Defense Advanced Research Project Agency (Contract: F3361595C1623).

and the saturation voltage is

$$V_{\text{DS}_{\text{SAT}}} = \mathsf{E}_{\text{C}}\mathsf{L}\sqrt{1 + \frac{2}{\mathsf{E}_{\text{C}}\mathsf{L}}}\sqrt{1 + \frac{2}{\mathsf{E}_{\text{C}}\mathsf{L}}}\sqrt{1 - 1}. \quad (4)$$

(Note: Figure 2 defines all parameters used in (2)-(4).) Combining (1) and (2) for  $V_{GS}=V_{DD}$

$$I_{D0} = \iint W / L \bigcup C_{OX} \mu_{eff} V_{D0} \left[ V_{DD} - V_{T} - \iint \eta / 2 \bigcup V_{D0} \right]$$

(5)

where

$$V_{D0} = V_{DS_{SAT}} \Big|_{V_{GS} = V_{DD}} .$$

(6)

From (1)

$$\left[ \frac{V_{GS} - V_{T}}{V_{DD} - V_{T}} \right]_{\alpha}^{\alpha} = I_{D_{SAT}} / I_{D0} .$$

(7)

Substituting (2) and (5) into (7) gives

$$\frac{1}{2} \frac{V_{GS} - V_{T}}{V_{DD} - V_{T}} \left\| \right\|^{\alpha} = \frac{V_{DS_{SAT}} \left[ V_{GS} - V_{T} - \frac{1}{2} \eta / 2 \left[ V_{DS_{SAT}} \right] \right]}{V_{D0} \left[ V_{DD} - V_{T} - \frac{1}{2} \eta / 2 \left[ V_{D0} \right] \right]} .$$

(8)

Solving for the exponent  $\alpha$  in (8),

$$\alpha|_{V_{GS}} = \frac{\ln \left[ V_{DS_{SAT}} \left[ V_{GS} - V_{T} - \frac{\eta}{2} \sqrt{2} V_{DS_{SAT}} \right] \right]}{\ln \left[ V_{DD} \left[ V_{DD} - V_{T} - \frac{\eta}{2} \sqrt{2} \right] V_{DO} \right]} \right]}.$$

(9)

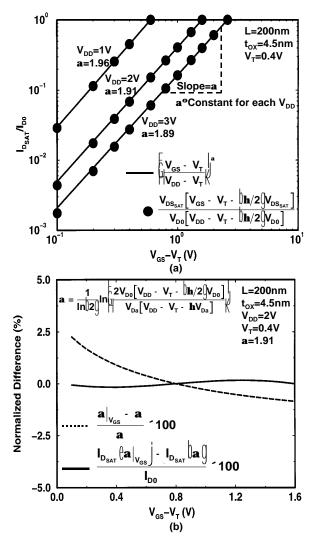

Equation (9) expresses the parameter  $\alpha$  as a function of V<sub>GS</sub>. Given V<sub>T</sub>=0.4V and V<sub>DD</sub>=1, 2, and 3V for  $\alpha$ =1.96, 1.91, and 1.89, respectively, Figure 1(a) plots both sides of (8) as  $\log(I_{D_{SaT}}/I_{D0})$  versus  $\log(V_{GS}-V_T)$  to demonstrate the power law relationship of  $I_{D_{\text{SAT}}}$  with respect to  $V_{\text{GS}}\text{-}V_{\text{T}}.$ Figure 1(a) exhibits excellent agreement between the Alpha-Power Law and Low Power Transregional saturation drain current models for a constant value of  $\alpha$ . Applying L' Hospital's Rule to (9) verifies that the expression has a removable singularity at the point  $V_{GS}=V_{DD}$ . Therefore from Figure 1(a), (9) will provide an accurate solution to  $\alpha$ for any value of  $V_{\text{GS}}$  between  $V_{\text{T}}$  and  $V_{\text{DD}}$  (region of saturation assuming  $V_{DS}=V_{DD}$ ). A simplified and accurate expression of  $\alpha$  is determined by selecting  $V_{\text{GS}}$  equal to the middle value between the end points  $(V_{DD}, V_T)$  such that  $V_{GS} = [V_{DD} + V_T]/2$ . Substituting  $V_{GS} = [V_{DD} + V_T]/2$ into (9) gives

$$\alpha = \alpha \Big|_{V_{DD} + V_{T} / 1 / 2} = \frac{1}{\ln |2|} \ln \left| \frac{2V_{D0} V_{DD} - V_{T} - \frac{1}{2} \eta / 2(V_{D0})}{V_{Da} V_{DD} - V_{T} - \eta V_{Da}} \right|$$

(10)

where

$$V_{Da} = V_{DS_{SAT}} \Big|_{V_{GS} = \bigcup V_{DD} + V_T \bigcup 2} .$$

(11)

For added verification of (10), Figure 1(b) plots the percent difference between  $\alpha|_{V_{GS}}$  (9) and  $\alpha$  (10) normalized by  $\alpha$  versus V<sub>GS</sub>-V<sub>T</sub>. The parameter  $\alpha|_{V_{GS}}$  varies less than

Figure 1. Validation of  $\alpha$ 's constant behavior against V<sub>GS</sub>. (a) log( $I_{D_{SAT}}/I_{D0}$ ) versus log(V<sub>GS</sub>-V<sub>T</sub>) demonstrates the power law relationship of  $I_{D_{SAT}}$ , equation (8), against V<sub>GS</sub>-V<sub>T</sub> for V<sub>DD</sub>=1, 2, and 3V. (b) Percent normalized difference versus V<sub>GS</sub>-V<sub>T</sub> indicates that  $\alpha|_{V_{GS}}$ , equation (9), varies less than 3% from  $\alpha$ , equation (10), and the effect of this difference on  $I_{D_{SAT}}$ , equation (1), is less than 1%.

3% from the constant value of  $\alpha$ . The effect of this difference between  $\alpha|_{V_{GS}}$  (9) and  $\alpha$  (10) is observed in Figure 1(b) by plotting the percent difference of  $I_{D_{SAT}} \frac{1}{2} \alpha|_{V_{GS}}$  and  $I_{D_{SAT}} \frac{1}{2} \alpha_{Q}^{0}$  from (1) normalized by  $I_{D0}$ . Figure 1(b) indicates less than a 1% variation for  $I_{D_{SAT}}$  using  $\alpha|_{V_{GS}}$  compared to the  $\alpha$  calculated in (10).

$$\begin{split} I_{D} &= \begin{cases} I_{D_{SUB}} \quad \left| V_{GS} \leq V_{T} + \eta / \beta : \text{ subthreshold region} \right| \\ I_{D} &= \begin{cases} I_{D_{SW}} \quad \left| V_{DS} \geq V_{DS_{SAT}} : \text{ triode region} \right| \\ I_{D_{SAT}} \quad \left| V_{DS} \geq V_{DS_{SAT}} : \text{ saturation region} \right| \\ I_{D_{SUB}} &= \left| W / L \int_{0} C_{OX} \frac{\eta}{\beta^{2}} \left[ 1 - exp \right] - \beta V_{DS} \int_{0}^{1} exp \int_{0}^{1} \beta / \eta \int_{0}^{1} V_{GS} - V_{T} - \eta / \beta \right] \\ I_{D_{TRI}} &= \left| W / L \int_{\overline{1 + \theta} V_{GS} - V_{T}} \int_{\overline{1 + \theta} V_{GS} - V_{T}} \int_{\overline{1 + \theta} V_{GS} - V_{T}} \int_{\overline{1 + \theta} V_{DS} / \overline{1 + V_{DS}} / \overline{1 + V_{DS$$

A feature of the *Physical* Alpha-Power Law Model is that the dependence of carrier velocity on V<sub>GS</sub> is jointly described by I<sub>D0</sub>, (5), (3), (4) and (6), as well as  $\alpha$  (10). This yields improved accuracy of the model for V<sub>GS</sub> near V<sub>T</sub> compared to the original Alpha-Power Law Model [1] that describes carrier velocity as a function of V<sub>GS</sub> solely through  $\alpha$ . Therefore, the values of  $\alpha$  calculated by the *Physical* Alpha-Power Law Model are slightly larger than the measured  $\alpha$  values of the original Alpha-Power Law Model [1] for short channel MOSFETs.

For further insight into the  $\alpha$  parameter, analyses of the long channel MOSFET with negligible carrier velocity saturation ( $E_CL>>V_{DD}-V_T$ ) and the short channel MOSFET with severe carrier velocity saturation ( $E_CL<<V_{DD}-V_T$ ) are performed. In the long channel case, the saturation voltage (4) may be simplified by performing a two term binomial expansion such that

$$V_{DS_{saT}}\Big|_{E_{c}L >> V_{GS} - V_{T}} \approx \int 1/\eta \bigoplus_{u} V_{GS} - V_{T} \bigcup_{u}.$$

(12)

Substituting (12) into (10) gives

$$\alpha \Big|_{\mathsf{E}_{\mathsf{C}}\mathsf{L} >> \mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{T}}} \approx \frac{\mathsf{ln}[\mathcal{A}]}{\mathsf{ln}[\mathcal{A}]} = 2.$$

(13)

Thus, for long channel MOSFETs with negligible carrier velocity saturation the exponent  $\alpha$  converges to the value for the classical Shockley square-law MOSFET model [5]. For the short channel MOSFET with V<sub>GS</sub> sufficiently larger than V<sub>T</sub>, the saturation voltage (4) may be simplified as

$$V_{\text{DS}_{\text{SAT}}}\Big|_{\text{E}_{\text{C}}\text{L} << \text{V}_{\text{GS}} - \text{V}_{\text{T}}} \approx \sqrt{D2\text{E}_{\text{C}}\text{L}/\eta \bigcup_{\cup} \text{V}_{\text{GS}} - \text{V}_{\text{T}}}\bigcup_{\cup}.$$

(14)

Substituting (14) into (10) gives

$$\alpha|_{\mathsf{E}_{\mathsf{C}}\mathsf{L} << \mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{T}}} \approx \frac{1}{\mathsf{In}[2]} \mathsf{In}[2]^{3/2} = 3/2 \;. \tag{15}$$

Substituting (14) and (15) as well as (5), (3), (4) and (6) into the expression for saturation drain current (1) gives

$$I_{D_{SAT}}\Big|_{E_{C}L << V_{DD} - V_{T}} \approx WC_{OX} \Big| V_{GS} - V_{T} \bigcup_{u} s_{at}, \qquad (16)$$

where  $v_{sat}$  is the saturation velocity. Thus, for the short channel MOSFET with severe carrier velocity saturation the drain current in the saturation region approaches a linear dependence of  $V_{GS}$ - $V_T$  [1].

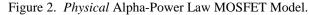

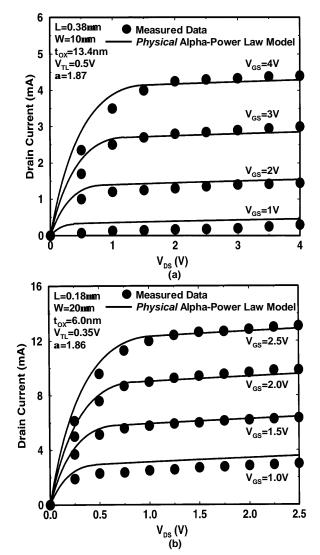

The equations for the triode and subthreshold regions of operation are simplified versions of the Low Power Transregional MOSFET Model [2] such that the complete Physical Alpha-Power Law MOSFET Model is defined in Figure 2. To ensure accurate modeling of sub-micron MOSFETs, a threshold voltage roll-off term [6] is included in the  $V_T$  formula. Figure 3 compares the newly derived model against Level 3 HSPICE simulations [7] for the  $0.25\mu m$  (L=0.20 $\mu m$ ) technology generation in the (a) superthreshold region ( $I_D$  versus  $V_{DS}$ ) and (b) subthreshold region ( $I_D$  versus  $V_{GS}$ ). Excellent agreement is demonstrated between the Physical Alpha-Power Law Model and HSPICE simulations. A crucial element of the Physical Alpha-Power Law Model is the subthreshold analysis, which was neglected in the original Alpha-Power

Figure 3. Verification of the *Physical* Alpha-Power Law Model against HSPICE Simulations [7] for (a)  $I_D$  versus  $V_{DS}$  and (b)  $I_D$  versus  $V_{GS}$ .

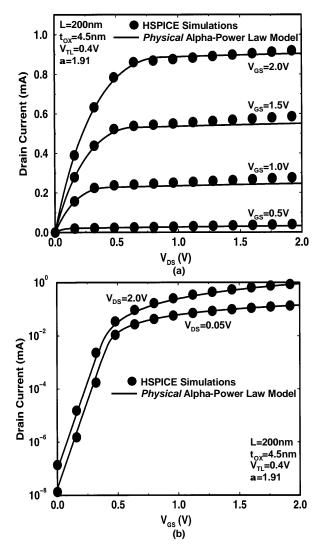

Law Model [1]. Inclusion of the subthreshold region of operation provides key insight into the on/off current tradeoff for future technology generations. Figure 4 demonstrates that the model is in good agreement with measured data for submicron technology generations: (a) L=0.38 $\mu$ m [8] and (b) L=0.18 $\mu$ m [9]. Therefore, the new *Physical* Alpha-Power Law Model retains the simplicity of the original Alpha-Power Law Model while providing a physical basis for the model parameters that enables circuit performance projections for future generations of technology including on/off current interdependence for low power GSI.

# 3. Projections using the *Physical* Alpha-Power Law Model

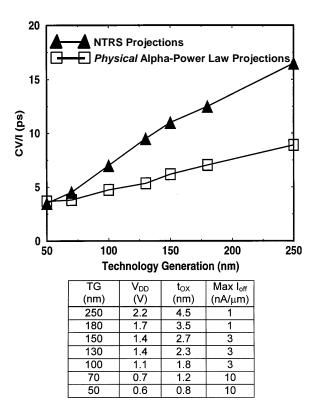

Figure 5 compares the MOSFET delay metric CV/I as projected by the newly derived *Physical* Alpha-Power Law

Figure 4. Verification of the *Physical* Alpha-Power Law Model against measured data for (a)  $L=0.38\mu m$  [8] and (b)  $L=0.18\mu m$  [9].

Model against the NTRS roadmap [10]. Values for feature size, oxide thickness, and supply voltage are chosen in the range of parameters projected by the roadmap. For the model projections, the threshold voltage is calculated by equating the subthreshold drain current per unit width to the maximum off current (Max  $I_{off}$ ) specified by the roadmap. Figure 5 indicates a 2X-performance advantage for the first three generations compared to the NTRS calculations, subject to the maximum allowable leakage current. As technology scales, the extrapolations of the NTRS converge to the calculations predicted by the *Physical* Alpha-Power Law Model thus indicating a significant on/off current interdependence.

### 4. Conclusion

The complete *Physical* Alpha-Power Law MOSFET Model is derived to describe all regions of operation

Figure 5. Comparison of the *Physical* Alpha-Power Law and NTRS Projections for CV/I versus Technology Generation (TG). The model calculates  $V_T$  by equating  $(I_{D_{SUB}}/W)$  to the maximum off current (Max  $I_{off}$ ) determined in the roadmap.

(subthreshold, triode, and saturation) while providing a simple mathematical expression for calculations of circuit performance yet retaining a physical insight of model parameters. Validated against HSPICE and measured data, the model includes the effects of 1) vertical and lateral high field mobility degradation and velocity saturation, and 2) threshold voltage roll-off. The Physical Alpha-Power Law MOSFET Model describes the entire range of velocity saturation from the long channel MOSFET with negligible velocity saturation to the short channel MOSFET with severe velocity saturation. Model projections for MOSFET delay indicate a 2X-performance opportunity compared to the roadmap extrapolations for the 250, 180, and 150nm generations subject to the maximum leakage current estimated by the roadmap. The NTRS and model calculations converge at a technology generation of 70nm, which indicates a significant on/off current interdependence for low power GSI.

## 5. References

- T. Sakurai and A R. Newton, "Alpha-Power Law MOSFET Model and its Applications to CMOS Inverter Delay and Other Formulas," *IEEE J. of Solid State Circuits*, Vol. 25, No. 2, pp. 584-594, Apr. 1990.

- [2] B. Austin, K. Bowman, Xinghai Tang, and J. D. Meindl, "A Low Power Transregional MOSFET Model for Complete Power-Delay Analysis of CMOS Gigascale Integration (GSI)," *Proc. of the 11<sup>th</sup> Annual IEEE Intl. ASIC Conf.*, pp. 125-129, Sept. 1998.

- [3] S. L. Garverick and C. G. Sodini, "A Simple Model for Scaled MOS Transistors that Includes Field-Dependent Mobility," *IEEE J. Solid-State Circuits*, Vol. SC-22, No. 1, pp. 111-114, Feb. 1987.

- [4] B. T. Murphy, "Unified Field-Effect Transistor Theory Including Velocity Saturation," *IEEE J. Solid-State Circuits*, Vol. SC-15, pp. 325-327, June 1980.

- [5] W. Shockley, "A unipolar field effect transistor," *Proc. IRE*, Vol. 40, pp. 1365-1376, Nov. 1952.

- [6] A. Agrawal, V. K. De, and James D. Meindl, "Opportunities for Scaling FET's for Gigascale Integration (GSI)," *Proc. of the 23<sup>rd</sup> ESSDERC*, pp. 919-926, Sept. 1993.

- [7] HSPICE User's Manual, Meta-Software, Inc., Mar. 1995.

- [8] R. A. Chapman, C. C. Wei, D. A. Bell, S. Aur, G. A. Brown, and R. A. Haken, "0.5 Micron CMOS for High Performance at 3.3V," *IEEE IEDM Tech. Dig.*, pp. 52-55, 1988.

- [9] M. Bohr, S. U. Ahmed, L. Brigham, R. Chau, R. Gasser, R. Green, W. Hargrove, E. Lee, R. Natter, S. Thompson, K. Weldon, and S. Yang, "A High Performance 0.35µm Logic Technology for 3.3V and 2.5V Operation," *IEEE IEDM Tech. Dig.*, pp. 273-276, 1994.

- [10] Semiconductor Industry Association, "NTRS," 1997.