August 27, 2013 Penang, Malaysia

## A Possibility of Crystalline Indium-Gallium-Zinc-Oxide

#### asQED symposium 2013 (5th Asia Symposium on Quality Electronic Design)

Shunpei Yamazaki Semiconductor Energy Laboratory Co.,LTD., 398 Hase, Atsugi-shi, Kanagawa, Japan

## **Table of Contents**

- 1. Overview

- 2. Introduction

- 3. What is CAAC (C-Axis Aligned Crystal)?

- 4. Electrical Characteristics of CAAC-IGZO FET

- 5. Applications of Display and VLSI

- 6. Comparison of OS FET to MRAM & NAND Flash Memory

7. Conclusion

## [1] Overview

- 1. N. Kimizuka and T. Mohri, *J. Solid State Chem.*, **60**, 382 (1985).

- 2. N. Kimizuka, M. Isobe, and M. Nakamura, J. Solid State Chem., 116, 170 (1995).

- 3. C. Chen, K-C. Cheng, E. Chagarov, and J. Kanicki, Jpn. J. Appl. Phys., 50, 091102(2011).

- 4. S.Yamazaki, presented at International Workshop "Private Sector Academia Interaction", organized with KVA (2011).

http://www.icsu.org/events/ICSU%20Events/international-workshop-private-sector-academia-interaction

- 5. S. Yamazaki, J. Koyama, Y. Yamamoto, and K. Okamoto, *SID Symposium Digest*, **43**, 183 (2012).

- H. Inoue, T. Matsuzaki, S. Nagatsuka, Y. Okazaki, T. Sasaki, K. Noda, D. Matsubayashi, T. Ishizu, T. Onuki, A. Isobe, Y. Shionoiri, K. Kato, T. Okuda, J. Koyama, and S. Yamazaki, *IEEE J. Solid-State Circuits*, **47**, 2258 (2012).

- 7. J. Koezuka K. Okazaki, T. Hirohashi, M. Takahashi, S. Adachi, M Tsubuku, S. Yamazaki,

Y. Kanzaki, H. Matsukizono, S. Kaneko, S. Mori, and T. Matsuo, *SID Symposium Digest*, 44, 723 (2013).

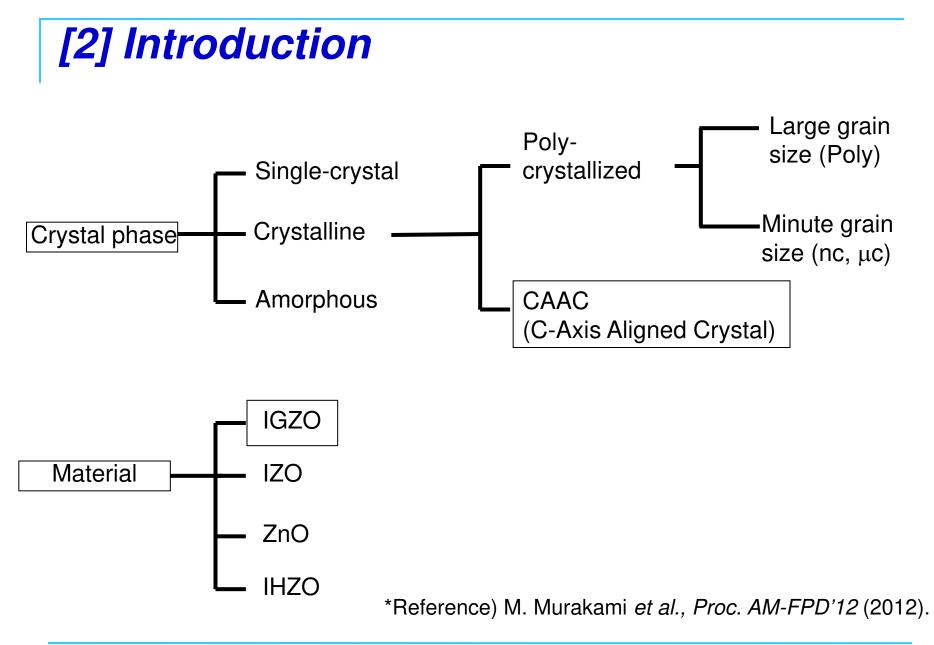

\*Reference) M. Murakami et al., Proc. AM-FPD'12 (2012).

## Commercial Production of Displays Using CAAC-IGZO FET Has Begun for the First Time in the World

#### docomo NEXT series Reference: http://www.sharp.co.jp/products/sh02e/ AQUOS PHONE ZETA SH-02E

Smart phones using CAAC-IGZO FET manufactured by NTT DOCOMO, INC. and

Sharp Corporation went on sale on Nov, 2012.

#### LCD1296 (OS) The smart phone "AQUOS PHONE ZETA SH-02E" manufactured by Sharp, Corp. LCD Module : 4.9 inches SHARP QM3417DP

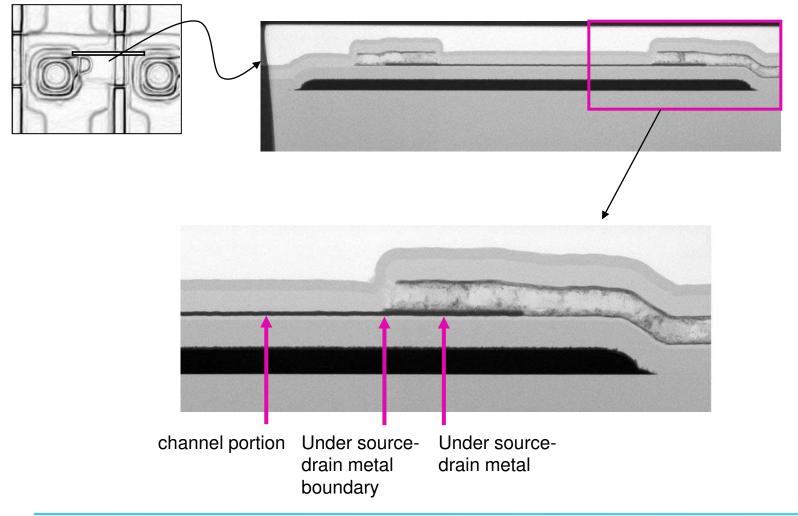

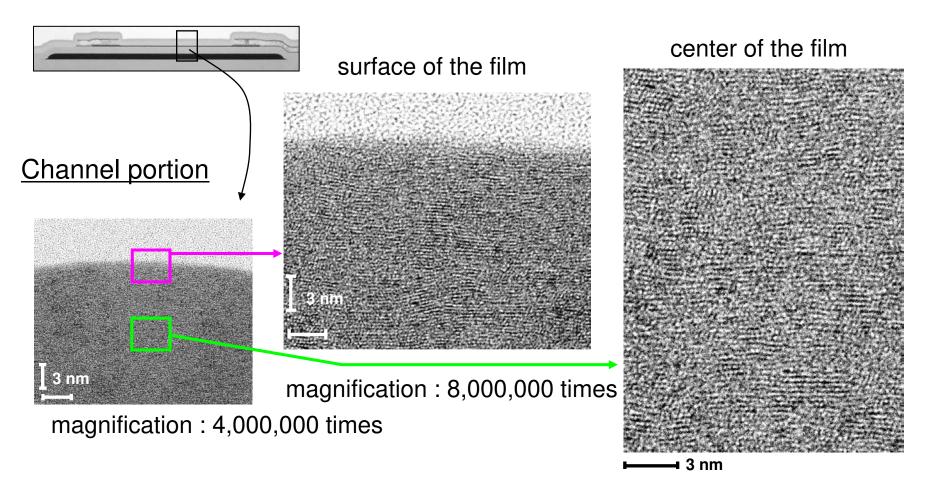

#### AQUOS PHONE ZETA SH-02E Cross-sectional TEM Image Analysis of CAAC-IGZO

## [3]What is CAAC (C-Axis Aligned Crystal)?

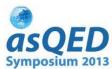

Fig. (a) shows a diffraction image of XRD (out-of-plane) on the crystalline IGZO (called CAAC hereinafter). A peak (009) is observed at around  $31^{\circ}$ .

Since the CAAC-IGZO has a periodic structure in Fig.(b), it has a peak in (009) in the image by XRD (out of plain).

\*Reference) S.Yamazaki et al., SID Symposium Digest, 43, 183 (2012).

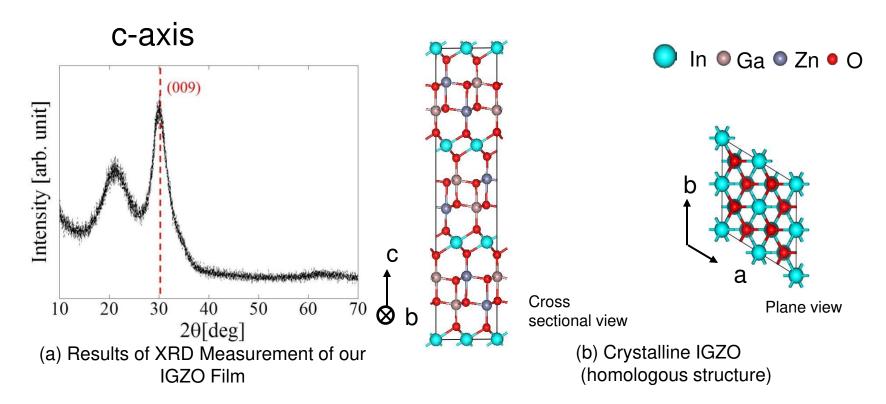

## X-Ray Diffraction (XRD) in a-b Plane

#### **Results of In-plane XRD Measurement**

- Fig. (a) shows XRD spectra of IGZO formed over a quartz substrate with a thickness of 300 nm by an in-plane method.

- Clear diffraction peaks are observed at every 60  $^\circ\,$  in the single-crystal IGZO having c-plane surface in Fig. (b).

- On the other hand, the CAAC-IGZO shows no diffraction peak as clear as those in the single-crystal IGZO even by rotating a sample at a 360-degree in Fig. (a), i.e. there is no symmetry in the (110) plane and no orientation in the a-b plane.

\*Reference) S.Yamazaki et al., SID Symposium Digest, 43, 183 (2012).

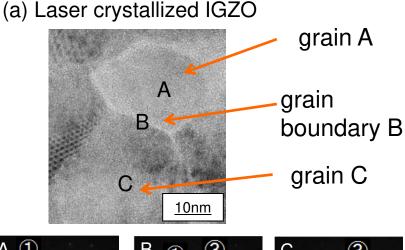

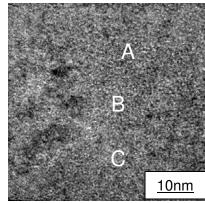

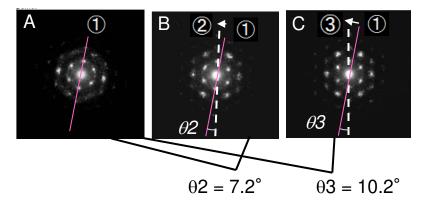

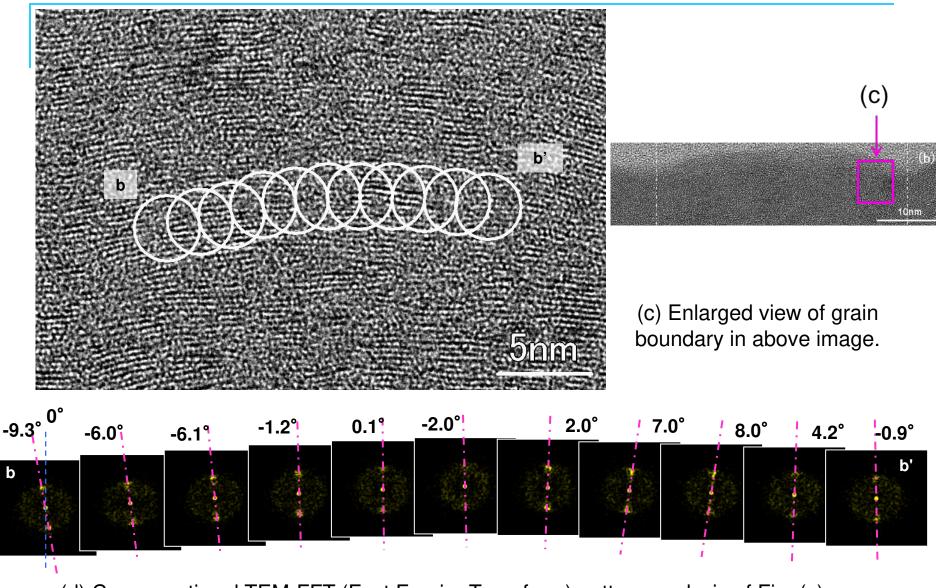

### Grain Boundary of IGZO vs. Grain region of CAAC-IGZO

> A-(1) and B-(1) have the same angle. B-(3) and C-(3) have the same angle.

B: The same diffraction angle is observed in both A and C

#### (b) CAAC (no clear grain boundary)

B: Observed diffraction angle rotates between and C

(d) Cross-sectional TEM-FFT (Fast Fourier Transform) pattern analysis of Fig. (c)

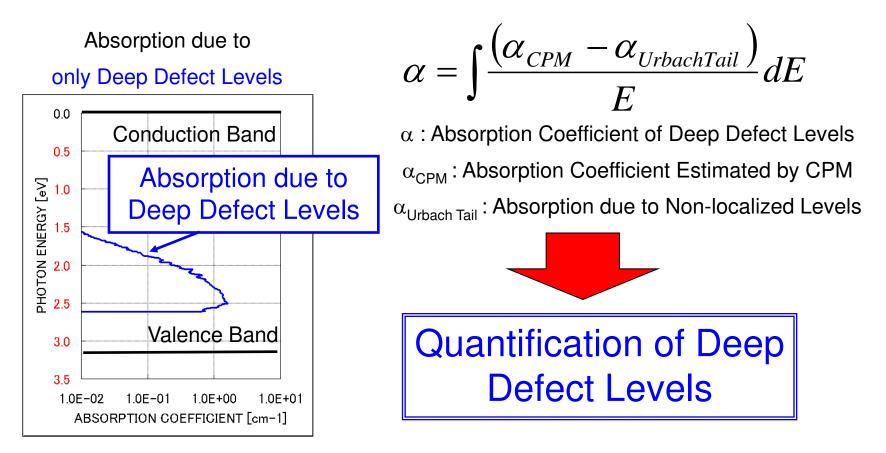

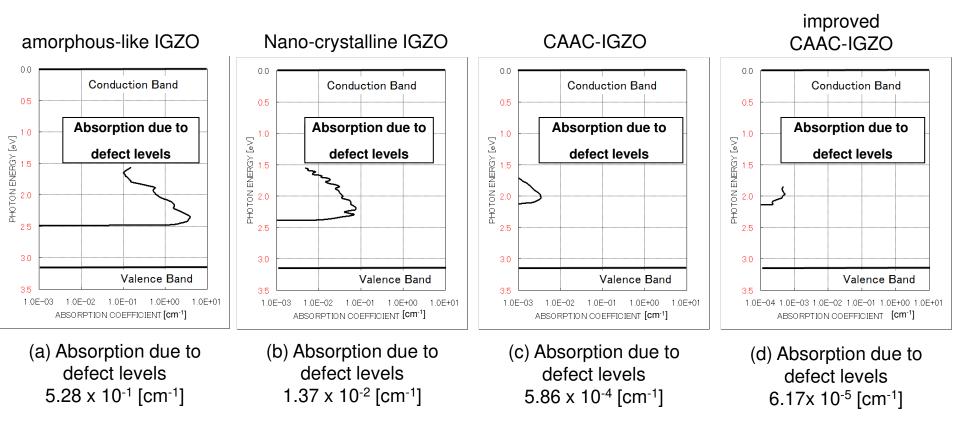

## Evaluation of Deep Defect Levels in IGZO

The absorption due to deep defect levels was quantified.

\*Reference) M.Tsubuku et al., SID Symposium Digest, 44, 166 (2013).

## Evaluation of Deep Defect Levels in IGZO

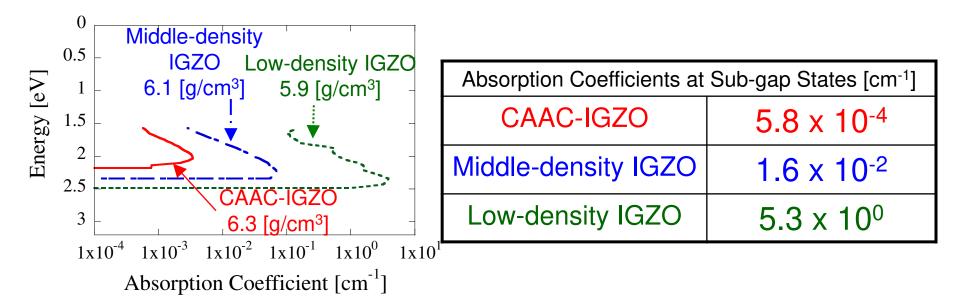

Absorption due to deep defect levels in low-density IGZO, middledensity IGZO and CAAC-IGZO were quantified.

### Deep defect levels exist at low density

### in CAAC-IGZO.

\*Reference) M.Tsubuku et al., SID Symposium Digest, 44, 166 (2013).

## Comparison of Deep Level DOS (density of states) by CPM

DOS can be reduced to 1/10000 of those of the amorphous-like IGZO which is necessary for LSI.

Therefore, what is found is: (1)CAAC-IGZO does not have a clear grain boundary. (2)Grains do exist but they are connected with each. (3)CAAC-IGZO is an oxide semiconductor film for the lowest DOS (density of states) compared with nc or amorphous-like IGZO.

That is, we think, this CAAC-IGZO has <u>new crystal morphology</u>. Since CAAC-IGZO does not have a clear grain boundary, any kind of photo-mask patterns can be formed over a large glass substrate in homogeneous or 10-100 nano-meter scale VLSI pattern.

Now, we will examine

"The electrical characteristics of CAAC-IGZO FET".

## [4] Electrical Characteristics of CAAC-IGZO FET

- 1. Variation in Characteristics of CAAC-IGZO Transistors

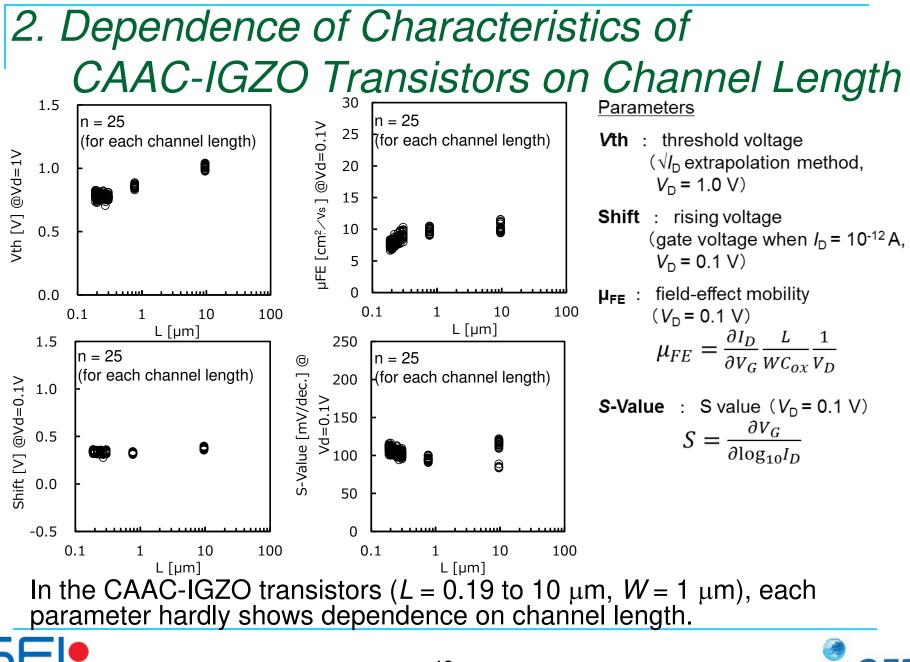

- 2. Dependence of Characteristics of CAAC-IGZO Transistors on Channel Length

- 3. Temperature Characteristics of CAAC-IGZO Transistors

- 4. Off-state Current

- 5. Drain Withstand Voltage of CAAC-IGZO Transistors

- 6. Reliability Measurement Results

- 7. Summary of Features of CAAC-IGZO

#### 1. Variation in Characteristics of CAAC-IGZO Transistors The graph below shows characteristics of 25 CAAC-IGZO transistors in a 5-inch substrate. 5 inch $L = 0.19 \ \mu m, W = 1.0 \ \mu m, T_{OX} = 20 \ nm$ 1E-02 50 X X X X X n = 251E-03 X × X X X 1E-04 40 $V_{\rm D} = 1.0 \, {\rm V}$ 5 inch 1E-05 × × X × × 30 1E-06 × × X X X μFE [cm²/Vs] ≤1E-07 X X $V_{\rm D} = 0.1 \,\,{\rm V}$ X X X 20 면 1E-08 1E-09 Vth (Ave) :0.79 V 1E-10 10 within the second *V* th (3σ) :63 mV 1E-11 S-value (Ave) : 109 mV/dec. 1E-12 $\mathbf{0}$ μ (Ave) $: 7.7 \text{ cm}^2/\text{Vs}$ 2 3 -3 -2 1

Vg [V] The CAAC-IGZO transistors have excellent uniformity and small S values.

NDUCTOR ENERGY LABORATO

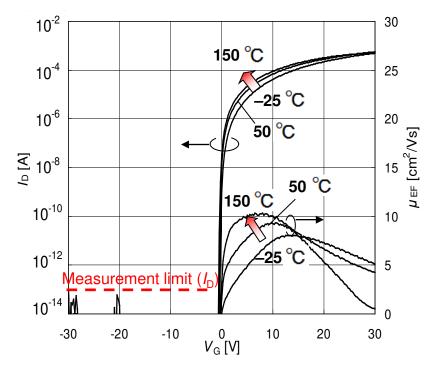

## 3. Temperature Characteristics of CAAC-IGZO Transistors

$(L = 3.0 \ \mu\text{m}, W = 20 \ \mu\text{m}, T_{OX} = 130 \ \text{nm}, V_D = 10 \ \text{V}, T = -25 \ ^{\circ}\text{C}, 50 \ ^{\circ}\text{C}, 150 \ ^{\circ}\text{C})$

Even when temperature is increased, Id-Vg characteristics rises at almost the same positions, which proves the CAAC-IGZO transistor has a favorable characteristics.

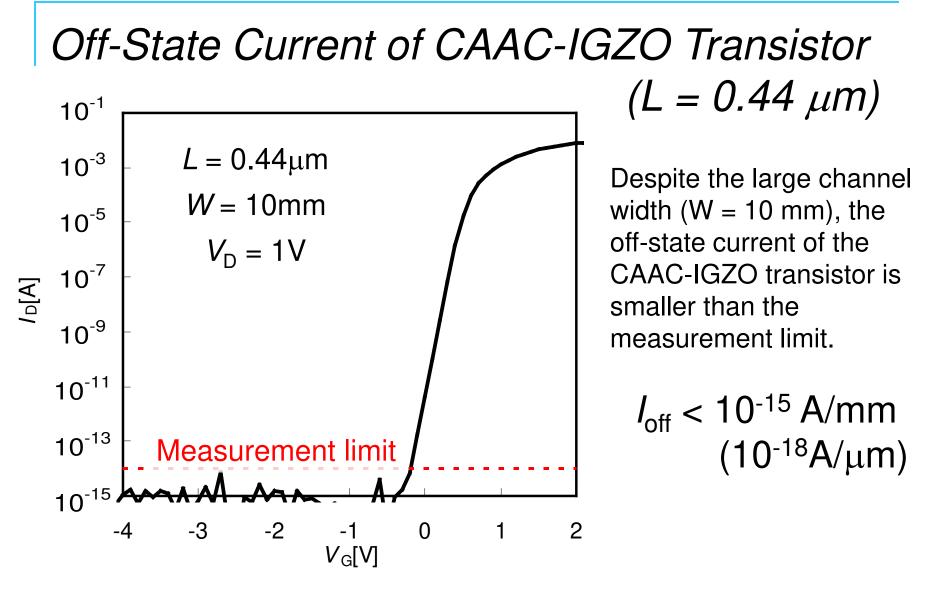

The off-state current is smaller than the measurement limit regardless of temperature.

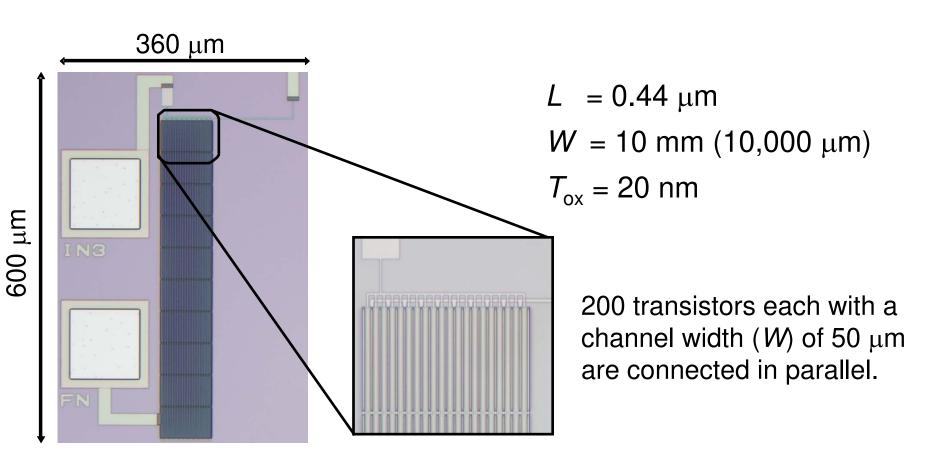

Micrograph of CAAC-IGZO transistor with a channel width (*W*) of 10 mm.

$A I_{\rm D} V_{\rm G}$  characteristics of a CAAC-IGZO transistor ( $L = 0.44 \ \mu m$ ,  $W = 10 \ mm$ ).

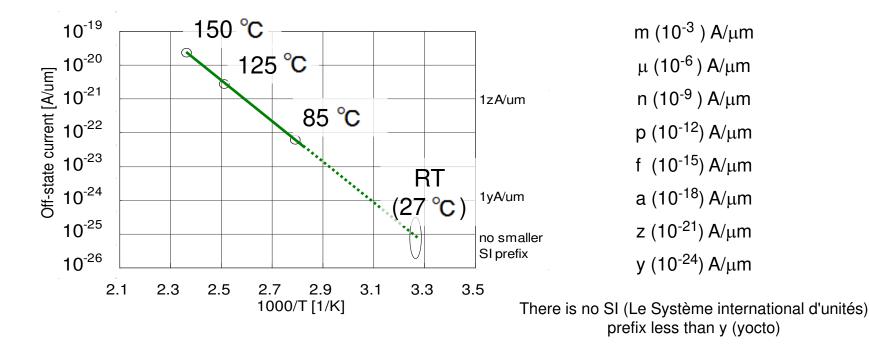

## Arrhenius Plot of Off-State Current (L = 0.49 μm)

Because of large Eg of 3.2eV, off-state current is smaller than the level of  $yA/\mu m = 10^{-24}A/\mu m$  (RT).

$L = 0.49 \ \mu\text{m}, \ W = 10 \ \text{mm}, \ T_{OX} = 20 \ \text{nm}, \ I_{off} = \text{Id}@Vg = -3V$

\*Reference) S. Yamazaki, *ECS Trans.*, 54.**85** (2013).

Symposiun

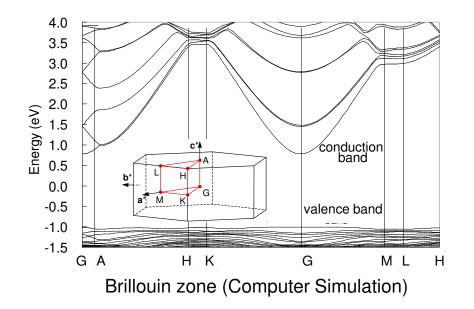

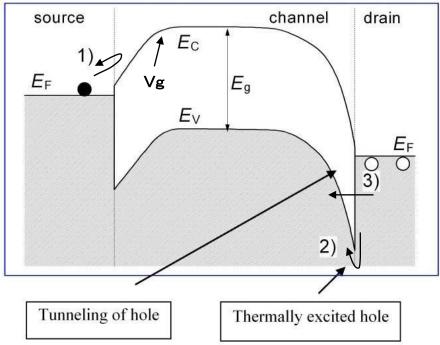

### Mechanism of Small Off-State Current

-Brillouin Zone and Effective Mass of Holes in IGZO FET in Off-State -

Effective mass calculated by the computer simulation

| Effective mass of electron m <sub>e</sub> */m <sub>e</sub> | 0.25(a*),0.25(b*),0.23(c*) |

|------------------------------------------------------------|----------------------------|

| Effective mass of hole<br>m <sub>h</sub> */m <sub>e</sub>  | 21(a*),41(b*),11(c*)       |

We found a significantly large effective mass of holes of 11 to 41 in IGZO FET, which is 100 times as large as that of 0.25 in Silicon FET.

That is, holes are unlikely to move around within IGZO.

\*Reference) M. Murakami, et al., Ext. Abstr. Solid States Devices and Materials, 320 (2012).

### Band Diagram of IGZO FET in Off-State

Band diagram of IGZO FET in off-state :

- 1) Since Vg is reverse biased, no electrons flows from source.

- In the reverse bias state, holes which are minority carriers from drain has a large effective mass; therefore, the current due to holes hardly flows. Tunneling current and thermally excited holes are both negligible.

- 3) As a result, the off-state current is extremely small.

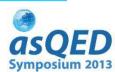

## 5. Drain Withstand Voltage of CAAC-IGZO Transistors

Unlike in the Si transistors, avalanche breakdown does not occur in the CAAC-IGZO transistors.

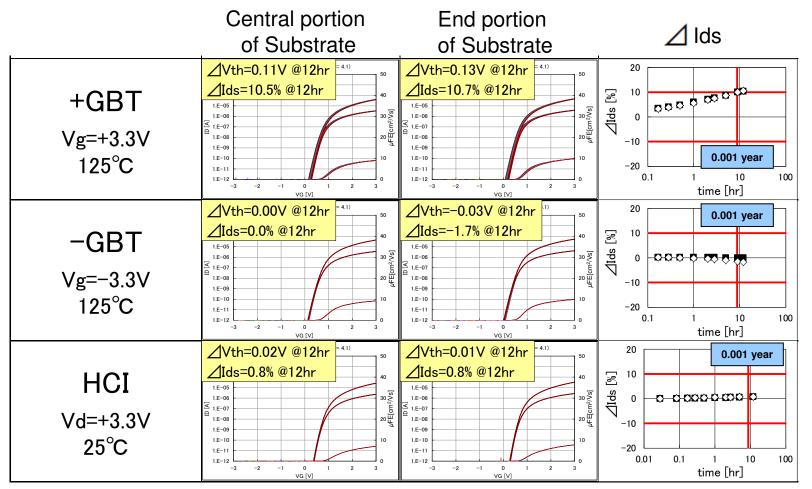

### 6. Reliability Measurement Results

#### B (Bias)-T (Temperature Treatment) and Hot carrier injection

$L = 0.8 \mu m, W = 10 \mu m, T_{ox} = 20 nm$

Central portion of Substrate  $\diamondsuit$  End portion of Substrate

## Reliability Measurement Results

$\Delta$  Ids (\*)Deterioration rate of Ids with 3.0V of Vd and 3.0V of Vg

| +GBT              | ⊿ lds<br>at 0.001 year                                    | Central portion: 10.0 %<br>at 0.001 year |                       | Central portion: () |

|-------------------|-----------------------------------------------------------|------------------------------------------|-----------------------|---------------------|

| Vg=+3.3V<br>125°C | (*) Target specification: $\leq 10\%$ at 0.001 year       | End portion: 9.9 %<br>at 0.001 year      | measurement<br>result | End portion:        |

| -GBT              | ⊿ lds<br>at 0.001 year                                    | Central portion: 0.0 %<br>at 0.001 year  |                       | Central portion: 🔿  |

| Vg=-3.3V<br>125°C | (*) Target<br>specification:<br>$\leq 10\%$ at 0.001 year | End portion: -1.5 %<br>at 0.001 year     | measurement<br>result | End portion:        |

| HCI               | ⊿ lds<br>at 0.001 year                                    | Central portion: 0.9 %<br>at 0.001 year  |                       | Central portion: 〇  |

| Vd=+3.3V<br>25°C  | (*) Target<br>specification:<br>$\leq 10\%$ at 0.001 year | End portion: 0.9 %<br>at 0.001 year      | measurement<br>result | End portion:        |

## 7. Summary of Features of CAAC-IGZO

|                                                                | CAAC-IGZO (intrinsic)                | Si (intrinsic)                      | Difference        |

|----------------------------------------------------------------|--------------------------------------|-------------------------------------|-------------------|

| • Eg→wide                                                      | 2.8 to 3.2 eV                        | 1.1 eV                              |                   |

| <ul> <li>Minority carrier (hole)</li> </ul>                    | < 10 <sup>-9</sup> cm <sup>-3</sup>  | 10 <sup>11</sup> cm <sup>-3</sup>   | 10 <sup>20</sup>  |

| <ul> <li>Majority carrier (electron)</li> </ul>                | Injection from only source           |                                     |                   |

| <ul> <li>Avalanche breakdown</li> </ul>                        | non                                  | occurs                              |                   |

| <ul> <li>Debye Length</li> </ul>                               | > 1 m                                | $\mu m$ order                       | > 10 <sup>8</sup> |

| <ul> <li>Reliability</li> </ul>                                | high (same level of Si LSI)          |                                     |                   |

| <ul> <li>Off-state current</li> </ul>                          | yA/µm order (at 85 °C)               | pA/μm order                         |                   |

| <ul> <li>Small S value,<br/>close to an ideal value</li> </ul> | 60 to 120 mV/dec.                    |                                     |                   |

| <ul> <li>On/off ratio</li> </ul>                               | > 10 <sup>17</sup> ~10 <sup>20</sup> | 10 <sup>6</sup> to 10 <sup>10</sup> |                   |

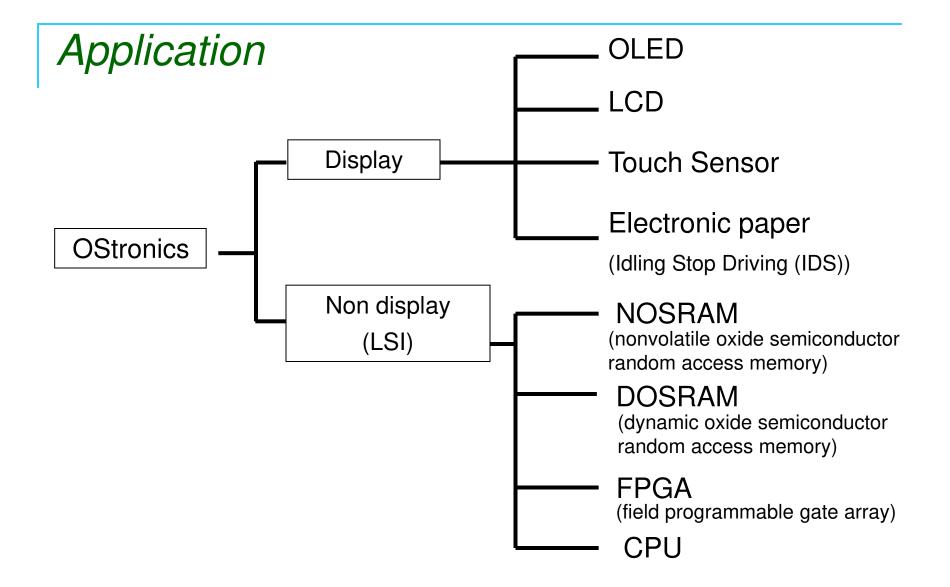

## [5] Applications of Display and VLSI

### 13.5-Inch 4K OS-FET OLED Display

Specifications

| -                    |                             |

|----------------------|-----------------------------|

| Screen Diagonal      | 13.5-inch                   |

| Driving Method       | Active Matrix               |

| Resolution           | 3840 x RGB x 2160<br>(QFHD) |

| Pixel Density        | 326 dpi                     |

| Aperture Ratio       | 55.8%                       |

| Pixel<br>Arrangement | RGB Stripe                  |

| Source Driver        | Chip on Film                |

| Gate Driver          | Integrated                  |

| Number of<br>OS-FETs | 1.25 x 10 <sup>8</sup>      |

### 3.4-Inch High-Definition Flexible OLED Display

#### Specifications

| Screen Diagonal      | 3.4-inch                         |  |

|----------------------|----------------------------------|--|

| Driving Method       | Active Matrix                    |  |

| Resolution           | 960 x RGB x 540 (qHD)            |  |

| Pixel Density        | 326 dpi                          |  |

| Aperture Ratio       | 40%                              |  |

| Pixel Arrangement    | RGB Stripe                       |  |

| Coloring Method      | White OLED with Color<br>Filters |  |

| Source Driver        | Integrated                       |  |

| Gate Driver          | Integrated                       |  |

| Number of<br>OS-FETs | 1.67 x 10 <sup>6</sup>           |  |

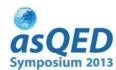

### NOSRAM cell structure

\*Reference) H. Inoue et al., IEEE J. Solid-St. Circ.,47 (2012).

Symposi

### NOSRAM

#### Specifications

| Memory Capacitance   | 1 Mbit                             |  |

|----------------------|------------------------------------|--|

| Technology           | Si-FET:0.8 μm                      |  |

| (Channel length)     | CAAC-IGZO FET : 0.8 $\mu$ m        |  |

| Die size             | 4.9 mm x 6.4 mm                    |  |

| Cell size            | 4.4 μm x 2.8 μm                    |  |

| Organization         | 1024 bit/page x 1024 pages         |  |

| Power supply voltage | VDD / VH / VL = 3 V / 4.5 V / -1 V |  |

| Write Time           | 150 ns/page                        |  |

| Read Time            | 900 ns/page                        |  |

| Retention Time       | > 60 days (at 85 °C )              |  |

| Number of FETs (Si)  | 1,190,000                          |  |

| Number of FETs (OS)  | 1,050,000                          |  |

\*Reference)

H. Inoue et al., JSSC, 47 (2012) 2258.

S. Yamazaki et al., Proc. SID'12 Dig. (2012) pp. 183-186.

S. Nagatsuka et al., in 5th IEEE Int. Memory Workshop (2013).

### FPGA (Field Programmable Gate Array)

| Core Size of MC-DRPLD                   | 2.6 x 4.4 mm    |

|-----------------------------------------|-----------------|

| Number of the PLEs                      | 20              |

| Number of the User I/O pins             | 20              |

| Configuration Memories                  | 7,520 bits      |

| Look-Up Table inputs                    | 4               |

| Power Supply Voltage                    | 2.5-3.3 V       |

| Channel Length: CMOS FET /<br>CAAC-IGZO | 0.5 μm / 1.0 μm |

| Number of FETs (OS)                     | 9,040           |

| Number of FETs (Si)                     | 45,411          |

\*Reference)

Y. Okamoto et al., UCSIC and TFT poster session (2013).

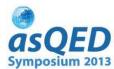

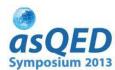

## 8-Bit Normally Off CPU

#### Specifications

| Architecture           | 8bit CISC             |  |  |

|------------------------|-----------------------|--|--|

| Technology             | Si-FET: 0.5 μm        |  |  |

| (Channel length)       | CAAC-IGZO-FET: 0.8 μm |  |  |

| Die size               | 8.4 mm x 12.0 mm      |  |  |

| Core size              | 4.5 mm x 3.4 mm       |  |  |

| Clock frequency        | 25 MHz                |  |  |

| Power supply voltage   | 2 V                   |  |  |

| Number of FETs<br>(OS) | 255                   |  |  |

| Number of FETs<br>(Si) | 42,500                |  |  |

\*Reference)

T. Ohmaru *et al., Ext. Abstr. Solid States Device and Materials* (2012) pp. 1144-1145. H. Kobayashi *et al., COOL Chips XVI* (2013).

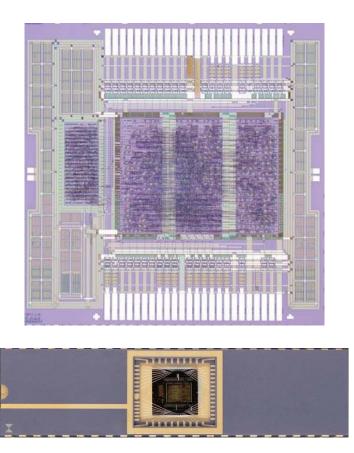

## 32-Bit Normally Off CPU

\*Reference) N. Sjokvist *et al.*,"Zero Area Overhead State Retention Flip Flop Utilizing Crystalline In-Ga-Zn Oxide Thin Film Transistor with Simple Power Control Implemented in a 32-bit CPU", to be published in SSDM 2013 Session M-6-4.

#### Specifications

| Technology           | Si          | 0.35 μm (GI: 10nm) |  |

|----------------------|-------------|--------------------|--|

| Technology           | IGZO        | 0.8 μm (GI: 20nm)  |  |

| Number of FETs (OS)  | 51,410      |                    |  |

| Number of FETs (Si)  | 372,000     |                    |  |

| Clock frequency      | 15MHz       |                    |  |

| Power supply voltage | Si          | 2.5 V              |  |

|                      | IGZO        | 3.5 V              |  |

| ISA                  | 32-bit RISC |                    |  |

| Pipeline             | 3 stages    |                    |  |

| IOPAD                | 256         |                    |  |

#### Cache

| Organization       | Unified I and D cache |

|--------------------|-----------------------|

| Block size         | 1 word ( = 4 bytes)   |

| Hit time           | 1 clock cycle         |

| Size               | 2KB                   |

| Block placement    | 2-way                 |

| Replacement policy | LRU                   |

| Write strategy     | Write back            |

## [6]Comparison of OS FET to MRAM &

#### NAND Flash Memory

|                              | OS Memory                                                  | STT-MRAM                                   | NAND Flash memory                    |

|------------------------------|------------------------------------------------------------|--------------------------------------------|--------------------------------------|

| Non-volatility               | Utilizes small off-state<br>current                        | Utilizes spins                             | Charge retention of<br>floating gate |

| Materials                    | OS material                                                | Magnetic rare earthes                      | Si                                   |

| Driving method               | Voltage-driving (4-pin)                                    | Current-driving (2-pin)                    | Voltage-driving (4-pin)              |

| Power consumption            | On/off control of FET                                      | Spin-directions charge of<br>magnetic body | Charge injection to<br>floating gate |

| Writing energy               | <u>4fJ/bit</u><br>(Charging/discharging of<br>capacitance) | 90fJ/bit<br>(Joule heat)                   | 1.4nJ/bit<br>(Injecting charge)      |

| Writing degradation          | <u>No</u>                                                  | Yes                                        | Yes                                  |

| Cell size                    | 11F <sup>2</sup> ~                                         | 8F <sup>2</sup> ~                          | <u>4F<sup>2</sup> ~</u>              |

| Multivalued                  | Possible                                                   | Difficult                                  | Possible                             |

| 3D conversion                | Possible                                                   | Difficult                                  | Possible                             |

| Magnetic-field<br>resistance | high                                                       | low,<br>magnetic-field interference*       | high                                 |

| Circuit diagram              |                                                            |                                            |                                      |

\*magnetic-field interference ; voltage driving 4 terminal electric network

## [7] Conclusion

- 1. We believe CAAC-IGZO has "new crystal morphology".

- 2. This is because IGZO does not have a clear grain boundary.

- 3. Reliability of CAAC-IGZO is acceptable for VLSI spec.

- 4. IGZO semiconductor has an extremely low off-state current. Then, by integrating CMOS of the Si semiconductor, we attained an ideal switch (off-state current is completely stopped).

- 5. Application forms of CAAC-IGZO are, for example, CPU, Non-volatile memory (NOSRAM) without fatigue, and FPGA.

- 6. We believe CAAC-IGZO technology can achieve new innovation in VLSI industry.

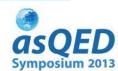

## Recent Topics Id-Vg Characteristics of CAAC-OS FET (L/W = 40nm/40nm)

# Thank you for your attention.

- We express great appreciation to Dr. Noboru Kimizuka, the first to synthesize IGZO in the world.

- His research outcome now grows to industry by CAAC-IGZO discovery.

- We believe 40nm channel length FET using CAAC-IGZO shall open the door to the high definition 3D VLSI.

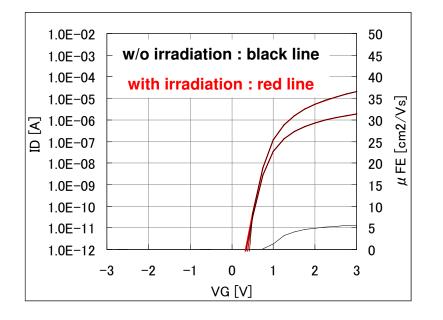

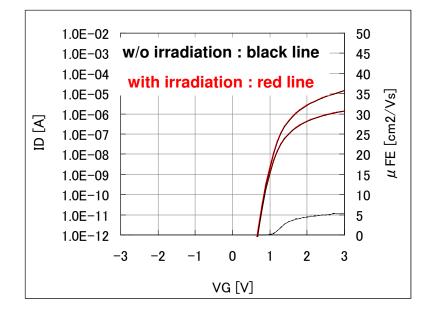

### Influence of Light Irradiation

#### Id-Vg characteristics under light irradiation

#### Monochromic UV light

The photon flux :  $7 \times 10^{15} \text{ cm}^{-2}\text{s}^{-1}$ Wavelength of Light : 350 nm White LED

Illumination Intensity : 40000lx

$L = 1 \mu m, W = 10 \mu m, T_{ox} = 20 nm$

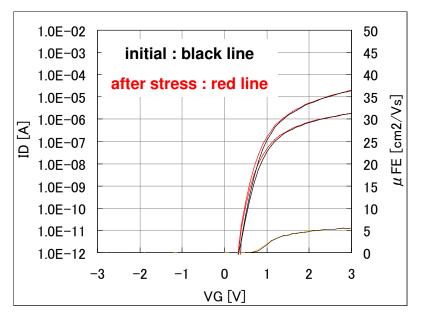

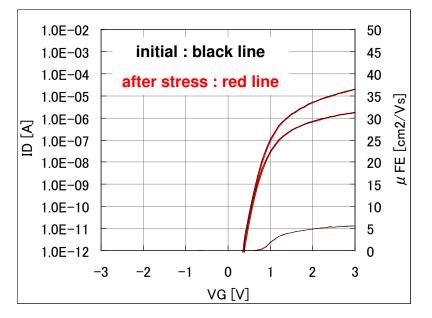

### Negative-Bias Photodegradation

Degradation under negative bias temperature illumination stress (NBTIS)

#### Monochromic UV light

Gate Bias Stress : -3.3V Stress temperature : 40 °C Stress Time : 1hr The photon flux : 7 x 10<sup>15</sup> cm<sup>-2</sup>s<sup>-1</sup> Wavelength of Light : 350 nm White LED

Gate Bias Stress : -3.3V Stress temperature : 40 °C Stress Time : 1hr Illumination Intensity : 40000lx

$L = 1 \mu m, W = 10 \mu m, T_{ox} = 20 nm$