### A Pseudo-Synchronous Implementation Flow for WCHB QDI Asynchronous Circuits

**Yvain Thonnart, Edith Beigné, Pascal Vivet** CEA-LETI, Minatec, Grenoble, France

Async'2012, May 8<sup>th</sup> 2012 DTU, Copenhagen, Denmark

### Asynchronous circuits

#### with synchronous CAD tools?

#### A handcrafted piece of art

- Entangled uneven loops

- Requires minute attention to detail

- Very valuable for specific needs

- But very expensive design time

- A powerful heavy machinery

- Backed-up by big EDA companies

- Obsessed about clocks

- Scared of loops

#### Pseudo-synchronous implementation

- "Mass-produced"

- Much cheaper design time

- Can run fast, nevertheless!

Trick the chain link model

#### Yvain Thonnart – ASYNC'12 Symposium, Copenhagen, Denmark | May 8th 2012 2 © CEA. All rights reserved

### Outline

- Asynchronous circuits with synchronous CAD tools ?

- Pseudo-synchronous models for C-elements

- Pseudo-synchronous circuit implementation

- Benchmarking against asynchronous implementation

- Real-world implementations

- Conclusion & perspectives

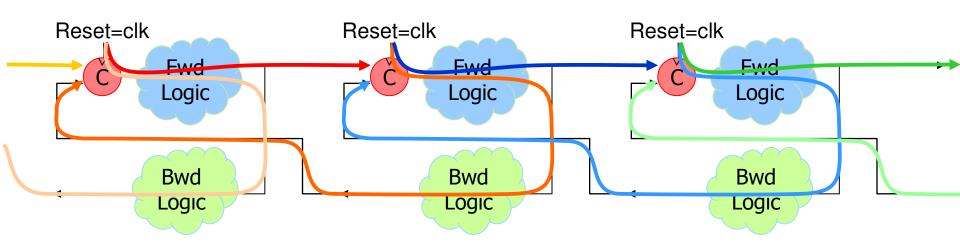

#### **DIMS WHCB pipeline** combinational loops & optimization Reset Reset Reset Fwd Fwd Fwd Logic LOGIC Logic Bwd Bwd Bwd Logic LOGIC LOGIC

- Performance is given by the loops cycle times

- Design optimization needs to constrain those loops

- Synchronous CAD tools can't handle them

- → need to cut the loops in the timing graph & constrain loop segments

- Where to cut for a systematic approach

- in the WCHB C-elements: the ones gathering forward and backward data (they must be Resetted)

#### **Asynchronous Implementation: cost & flaws**

#### Resulting timing constraints:

- For each WCHB C-element in the cell library, disable timing arcs to cut the loops

- set\_disable\_timing 'C\_element' –from 'in' –to 'out'

- For each path segment between two WCHB C-elements, specify a target maximum delay

- set\_max\_delay from 'C/elt/inst1/out' to 'C/elt/inst2/in' 0.5ns

- Limitation: The WCHB C-elements themselves are not optimized

- Minimal or no drive adaptation of cells depending on cell load

- No consideration on signal slope on path end

- Cells can be moved back and forth during placement

- Synchronous CAD tools do not manage asynchronous path ends correctly

#### Use pseudo-synchronous models for WCHB C-elements

- to cut timing loops without disabling timing arcs

- to improve tool control over path ends

# Pseudo-synchronous circuit timing paths

- Loops are cut naturally at pseudo-synchronous C-elts

- No need to disable a timing arc

- Creates 2 kinds of paths in WCHB pipeline:

- forward paths

et 2

backward paths

How to derive pseudo synchronous models ?

How to constrain resulting paths ?

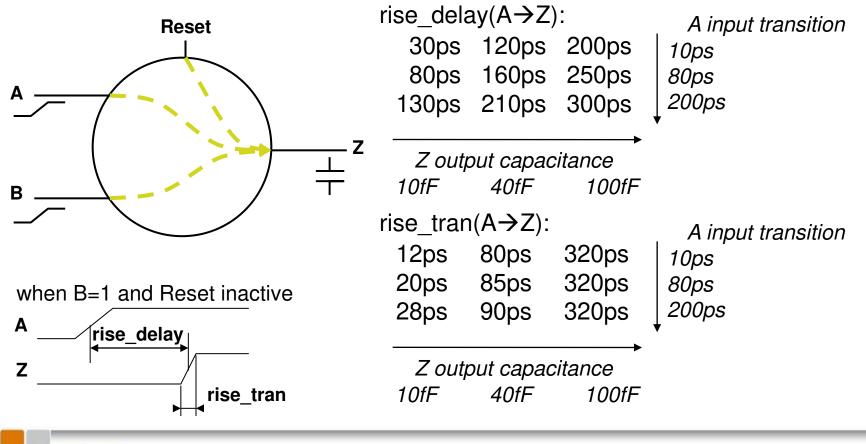

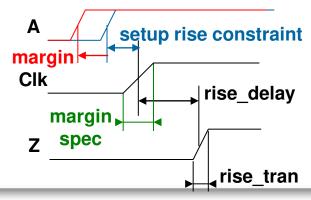

### **Asynchronous** .lib characterization

- Ilib files in Liberty format to model cell timing arcs

- As a function of input transition times and output capacitance

- 4 values per arc : rise delay, fall delay, rise transition, fall transition

leti

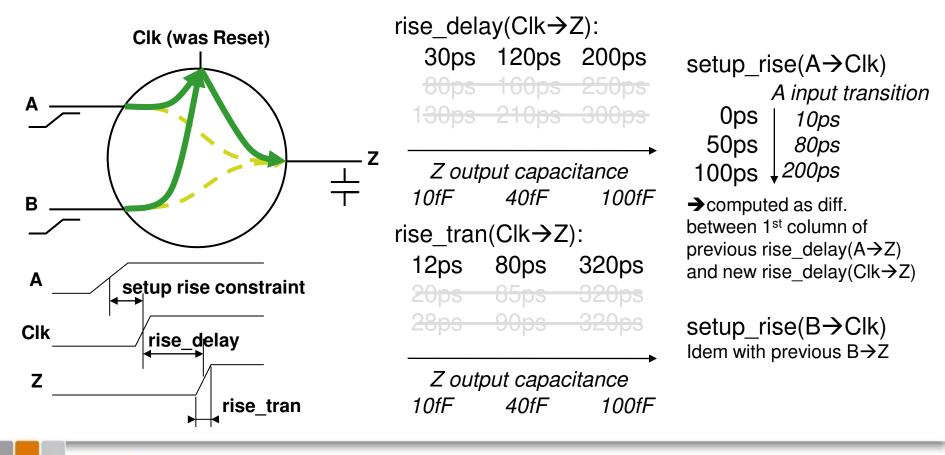

### **Pseudo-synchronous**.lib derivation

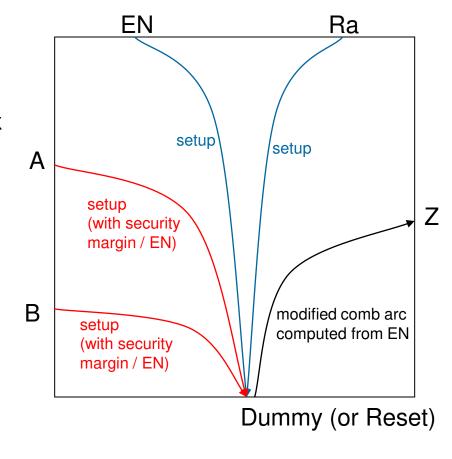

#### C-element is modeled like a synchronous flip-flop

- Reset pin is used as a dummy clock input

- New arc uses first row of  $A \rightarrow Z$  arc, old arcs are turned to setup checks

#### Vvain Thonnart – ASYNC'12 Symposium, Copenhagen, Denmark | May 8th 2012 | 8 © CEA. All rights reserved

# Simple pseudo-synchronous constraint

- Declaring a clock on the reset signal constrains all paths to a given "dummy" period

- Actual asynchronous cycle time given by biggest sum of 2 fwd + 2bwd delays on the loops (for token+bubble)

- →as bad as 4x dummy target period

- →often less (2x-3x) as no hold fixing is done

- Dummy clock period limitation:

- Logic depth can be different on each path

- Relaxes all paths to worst path length

eti & li

- Actual throughput not optimal when forward and backward logic are not balanced (on most critical local loop)

- Actual forward latency can be really sub-optimal (given by sum of fwd delays)

- What about over-constraining the design ?

- Negative slack is not a big deal for implementation, circuit is QDI after all !

- But over-constrained paths will distract the optimization kernels...

# Refined pseudo-synchronous timing constraints

Use dummy clock declaration to identify paths, not to constrain design with a given period

- Declare clock to break loops, with any period (e.g. Ons)

- Override delays on all paths with reg2reg set\_max\_delay constraints set\_max\_delay 0.23ns –from C/elt/inst1 –to C/elt/inst2 (no pins given → preserve all arcs inferred by clock declaration)

- Resulting constraints very similar to asynchronous ones, but with no timing arc disabled

- → Better control on timing paths for optimization tools

- Leverage on all existing asynchronous STA methods to predict performance

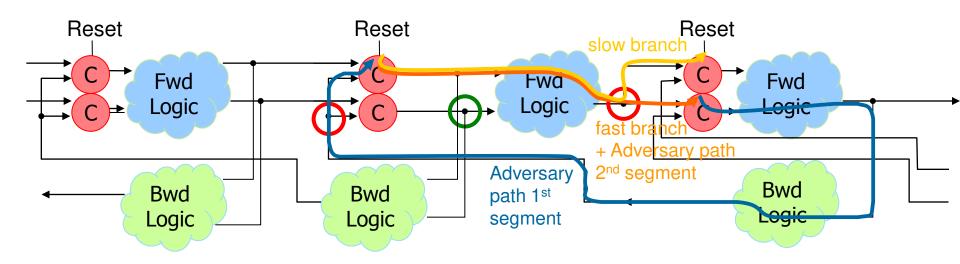

# WHCB isochronic forks handling

- Green fork needs no isochronic assumption

- Both branches are acknowledged by protocol (C-element on point of reconvergence)

- Red forks should be isochronic (or relaxed)

- Only one of the branches is acknowledged (reconvergence on a combinational gate)

BUT

- they always occur at path ends (previous logic is shared)

- Shortest adversary path goes through 2 C-elements and at least 1 inverting bwd logic

- Constraining paths through the fork for shortest possible delays (with refined 'set\_max\_delay' constraints) also balances any buffer tree needed at the fork

- Adversary path isochronic hypothesis is easily met

#### leti&li/t

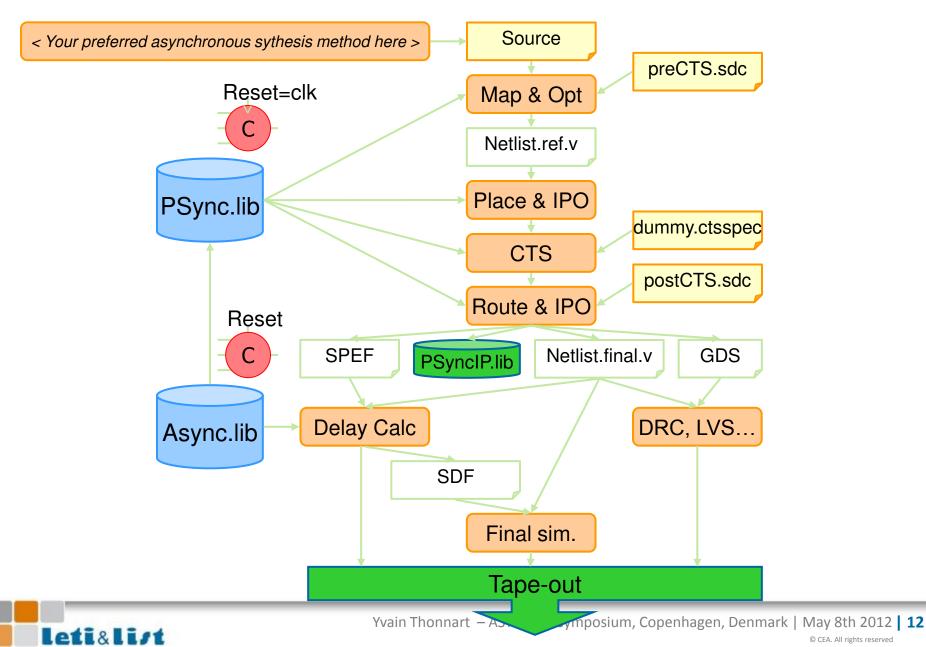

### **Pseudo-synchronous implementation flow**

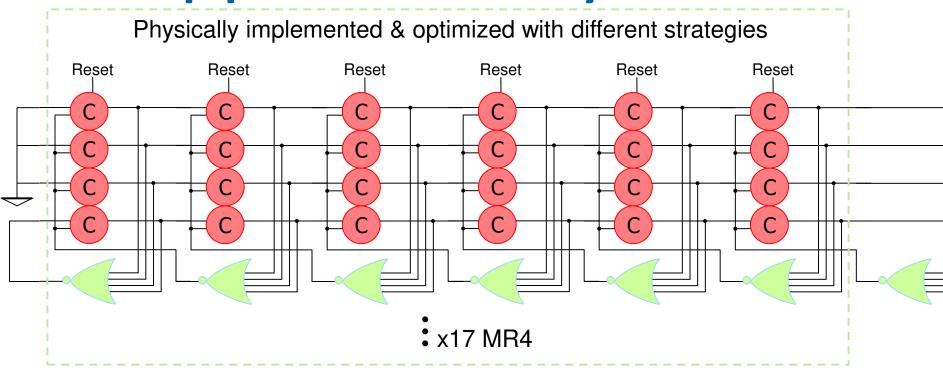

# Linear pipeline case study

- Instantiated 4x to inject the 4 different input values on each MR4

- Implemented down to layout with Cadence SoC Encounter

- STMicro 65nm LP technology

- Very narrow floorplan 20µm\*600µm to model a long NoC link

#### Yvain Thonnart – ASYNC'12 Symposium, Copenhagen, Denmark | May 8th 2012 | 13 © CEA. All rights reserved

# **Timing constraints strategies**

#### Asynchronous modeling

combinational loops broken at *C-elements inputs.*

- zero-delay target:

- 'set\_max\_delay 0' on all paths

- zero slack:

- iterations on place-and-route flow adjusting per path 'set\_max\_delay' values until implementation reports final slack of Ops.

- -40ps slack:

- same as above, but stop iterating as soon as final negative slack is lesser than 40ps.

#### Pseudo-synchronous modeling

- zero-delay target:

- 'create\_clock Reset -period 0'

- simple:

- 'create\_clock Reset -period N' with iterations until N cannot be reduced with a final slack of Ops.

#### zero slack:

- 'create\_clock Reset -period 0', plus iterations on per path

'set\_max\_delay' values until implementation reports a final slack of Ops.

- -20ps slack:

- same as above, with a 20ps target.

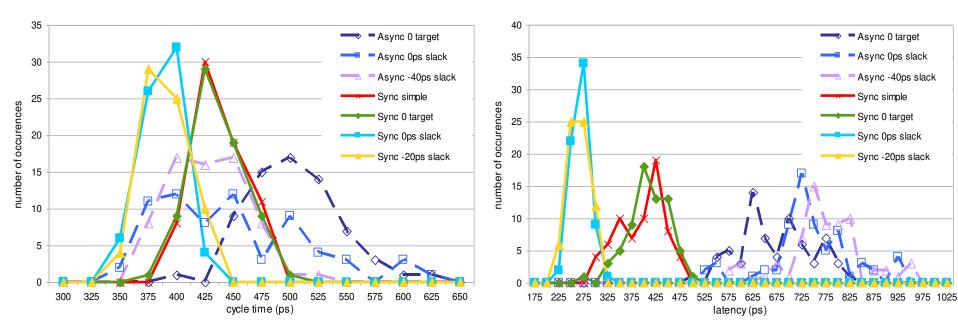

# Benchmarking results @tt65\_1.2V\_25C

- With asynchronous modeling, disabling timing arcs to break loops at C-elements degrades performance

- Simple and 0 target synchronous are comparable in performance

- Less iterations for 0 target, but slightly bigger area

eti 2

Ad-hoc synchronous constraints give best results

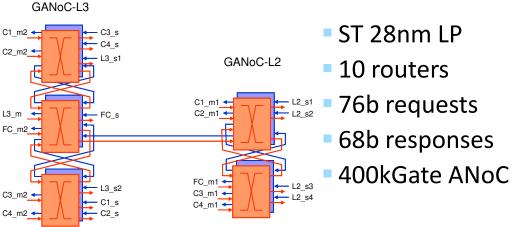

# **ANoC implementations**

- ANoC router made of 6 kinds of WCHB processes

- 3 per input stage, 3 per output stage

- Generic data path size

- Any possible combination of input stages and output stages

- 60 "generic" 'set\_max\_delay' constraints cover all possible arrangements of processes in NoC topology

- 60 values to refine for zero-slack strategies

- Recent implementation in 3 chips with industrial partnership in 2011/2012

- 2D-mesh based, in STMicro 65nm LP

- Req-Resp Master-Slave based in STMicro 32nm and 28nm LP

- ST 65nm LP

- 16 routers

- 2 channels

- 34b datapath

- 1MGate ANoC

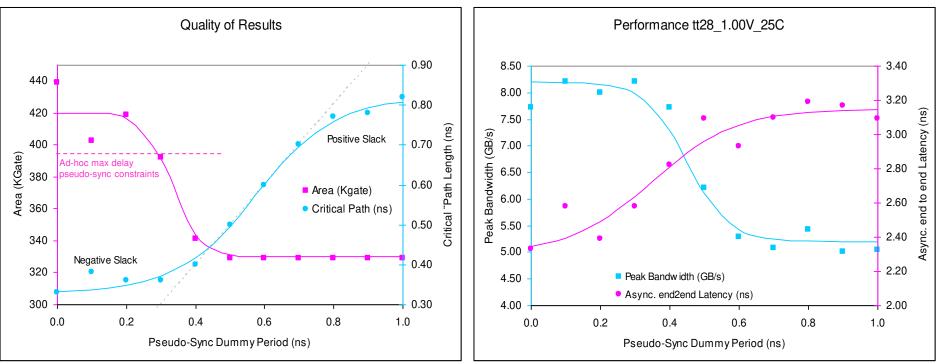

# 28nm P2012\_CO ANoC synthesis results

- According to dummy period:

- Area increase up to +30%

- cycle time & latency reduction up to -30%

- Ad-hoc pseudo-sync. constraints allow for:

- reproducible best performance @ 1280Mflit/s

- with reasonable area increase by ~20% compared to under-constrained design

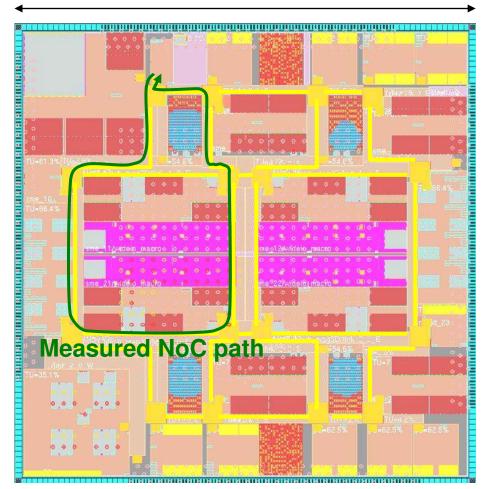

# **MAG3D** implementation results

- Technology

- STMicroelectronics cmos 65nm low-power process

- Implementation strategy

- Pseudo-synchronous hard-macro for routers

- Mixed integration on top

- Synchronous DfT

- Pseudo-synchronous ANoC links

- P&R Runtime ~ 17h

- ANoC Area

- IM Gate

- Performance

- @tt65\_1.2V\_25C

- 7 routers path

- ~10 mm links

- Average throughput: 850 Mflit/s

- Average latency: 9.81ns

#### ~8.5mm

#### leti&li/t

### Conclusion

Asynchronous circuits turned synchronous (not really...)

- For the designs → a bit more performance

- DIMS WCHB circuits are not as bad as you would think, aren't they ?

- For the designers → a systematic approach for loop breaking and design constraints

- Large asynchronous designs within easy reach

- For the community a "benevolent" betrayal

- Don't banish me, please...

- For the industry

→ a comfortable well-known CAD environment

- Energy-efficient off-the-shelf soft IPs

- OK, they are actually asynchronous, but only if they ask...

- But will it work for more than ANoC or DIMS WCHB ?

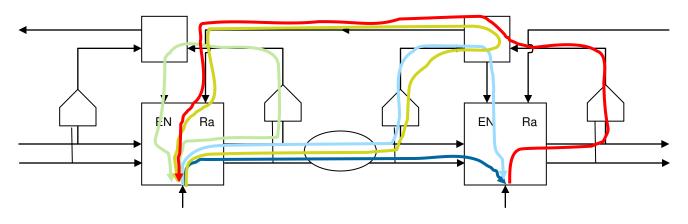

# Pseudo-synchronous timing paths in QDI (PCHB/PCFB/RSPCHB...) pipelines

- Up to 5 types of pseudo-synchronous paths instead of 2

- (+ WCHB like paths for state variable in PCFB)

- Not necessarily balanced in delays → ad-hoc constraints to be considered, dummy period could be insufficient

- When no Reset input is present on the cells, create and rely on an "internal pin" for dummy clock

- pin(dummy) {direction : "internal"; [...]} in .lib file

- create\_clock –name 'dummy\_clk' [\$all\_dummy\_pins\_in\_design] in .sdc file

- Blue paths form an isochronic fork for "bubbles"

- Need special handling to guarantee data deactivation before EN re-activation

#### leti&li/t

# timing arcs diversion and timing margin

Alternatives for relative delay constraint on isochronic fork

specify 'set\_data\_check'

- reduce max delay constraints separately on both paths to guarantee there is no positive slack

- Add security margin to data arcs

- Compatible with simple dummy clk period constraint

- Specify margin thanks to dummy clk transition time

LABORATOIRE D'ÉLECTRONIQUE ET DE TECHNOLOGIES DE L'INFORMATION

LABORATOIRE D'INTÉGRATION DES SYSTÈMES ET DES TECHNOLOGIES

#### Many thanks to

- My co-authors for their 9-year contribution & support

- The reviewers for their inspiring feedback

- The audience for your questions ?