# A Regulated Charge Pump With Small Ripple Voltage and Fast Start-Up

Jae-Youl Lee, Member, IEEE, Sung-Eun Kim, Student Member, IEEE, Seong-Jun Song, Student Member, IEEE, Jin-Kyung Kim, Student Member, IEEE, Sunyoung Kim, Student Member, IEEE, and Hoi-Jun Yoo, Senior Member, IEEE

Abstract—A regulated charge pump circuit is realized in a 3.3-V 0.13- $\mu m$  CMOS technology. The charge pump exploits an automatic pumping control scheme to provide small ripple output voltage and fast start-up by decoupling output ripple and start-up time.

The automatic pumping control scheme is composed of two schemes, an automatic pumping current control scheme and an automatic pumping frequency control scheme. The former automatically adjusts the size of pumping driver to reduce ripple voltage according to output voltage. The latter changes the pumping period by controlling a voltage-controlled oscillator (VCO). The output frequency of the VCO varies from 400 kHz to 600 kHz by controlling the input bias voltage of the VCO.

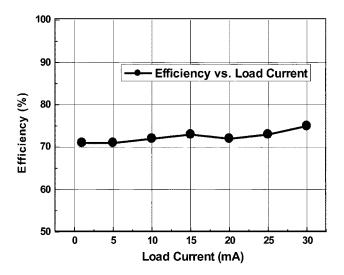

The prototype chip delivers regulated 4.5-V output voltage from a supply voltage of 3.3 V with a flying capacitor of 330 nF, while providing 30 mA of load current. The area is 0.25 mm² and the measured output ripple voltage is less than 33.8 mV with a  $2 \cdot \mu F$  load capacitor. The power efficiency is greater than 70% at the range of load current from 1 to 30 mA. An analytical model for ripple voltage and recovery time is proposed demonstrating a reasonable agreement with SPICE simulation results.

*Index Terms*—Automatic pumping control, large load current, regulated charge pump, small ripple voltage.

## I. INTRODUCTION

N MANY semiconductor devices, such as DRAM, EEPROM, and switched-capacitor transformers, charge pumps are frequently used to provide voltage higher than a power supply because high voltage level in a charge pump is generated by transferring charge to a capacitive load, without any amplifiers or regular transformers [1]. Many charge pump approaches have focused on the design of the Dickson charge pump, such as [2]–[4], since the conventional applications have required a high voltage with only limited current drive capability. However recent applications like USB-OTG (On-The-Go) not only require a high voltage level, but also require high current drive capability [5].

According to [6], output voltage of the charge pump decreases as load current increases. The dependence prevents the charge pump from generating high voltage with high

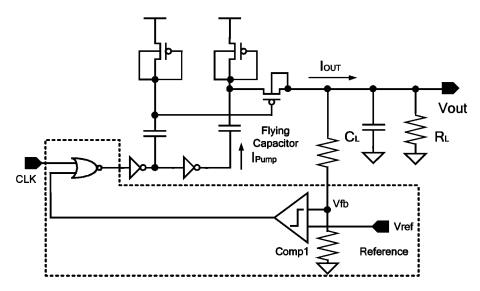

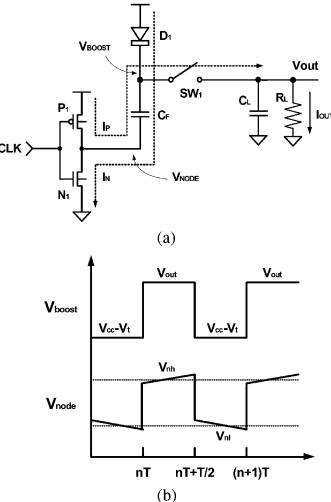

load current. To reduce the dependence, the regulated charge pump was proposed [7]. This charge pump generates constant output voltage regardless of load current by employing a clock blocking scheme blocking an input clock signal when the output voltage is higher than the required voltage. Fig. 1 shows a conceptual schematic of this charge pump. Using this scheme, constant output voltage with large load current of the charge pump can be achieved. However, large ripple voltage is incurred due to the clock blocking, especially in case of the large load current.

This paper describes a new regulated charge pump incorporating an automatic pumping control scheme to reduce ripple voltage while delivering large load current. The proposed regulated charge pump generates approximately 4.5-V output voltage and 33.8-mV ripple voltage with 30-mA load current.

In Section II, the steady state and dynamic analysis of the conventional regulated charge pump are described to develop the output ripple voltage generation processes and output voltage recovery time. In Section III, a new charge pump is proposed to reduce ripple voltage and decrease the recovery time of the output voltage. To verify the function of the proposed charge pump, the charge pump is analyzed by dynamics with state equations. Experimental results are provided and discussed in Section IV. Finally, conclusions are presented in Section V.

## II. CONVENTIONAL REGULATED CHARGE PUMP

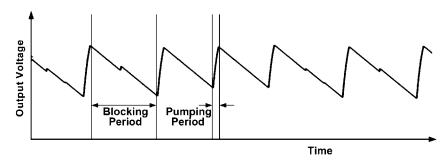

In the conventional regulated charge pump, the clock blocking scheme is adopted to isolate the output voltage level from the value of a load resistor, which determines the load current. Although its average output voltage has a constant value regardless of load resistor, large output ripple voltage is generated during the pumping and blocking periods.

The operation of clock blocking is shown in Fig. 2. The output load capacitor is charged only during pumping period and discharged through the load resistor continuously. If the pumping period is much shorter than the blocking period, output ripple voltage at the load capacitor during the pumping period [4] is determined by

$$\Delta V_{\text{out}} = \frac{i_{\text{pump}}}{C_{\text{load}} \cdot f} \tag{1}$$

where  $i_{\mathrm{pump}}$  is the pumping current into the flying capacitor during the pumping and blocking periods which is equal to  $i_{\mathrm{out}}$  in a steady state,  $C_{\mathrm{load}}$  is the output load capacitance, and f is the switching frequency between the pumping and blocking periods.

Manuscript received December 26, 2004; revised October 4, 2005.

J.-Y. Lee is with the Advanced DDI Design Team, System LSI Division, Samsung Electronics, Yongin 449-711, Korea (e-mail: jaeyoul.lee@kaist.ac.kr).

S.-E. Kim and J. K. Kim are with the Basic Research Laboratory, Electronics and Telecommunications Research Institute, Daejeon 305-700, Korea.

S.-J. Song, S. Kim, and H.-J. Yoo are with the Division of Electrical Engineering, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea. Digital Object Identifier 10.1109/JSSC.2005.862340

Fig. 1. Conceptual schematic of a conventional regulated charge pump.

Fig. 2. Operation of a regulated charge pump.

To reduce output ripple voltage, voltage variation during the pumping and blocking periods should be minimized. During the pumping period, it is clear that either small pumping current or large output load capacitor or high switching frequency is required to achieve small ripple voltage. However, in practice, changing the load capacitor value is difficult when this value is given in a specification, and reducing the charge pumping ability may lose load current supplying capability. Therefore, in order to reduce the output ripple, control of the pumping current and switching frequency, according to the load current, is required.

During the blocking period, turning off the operation of the charge pump causes a relatively large voltage drop. Therefore, another novel scheme rather than the blocking scheme is required.

It is important to decrease the rise time for the robustness of the output voltage. If the charge pump has a fast rise time in a power-up state, fast recovery time is also shown after the output voltage drops abruptly. Using dynamic analysis of charge pump, rise time  $T_r$  [3], output voltage raises to the required voltage level, is derived as

$$T_r = \frac{\ln\left[1 - \frac{V_{\text{out}} - V_{\text{gain}}}{V_{\text{gain}}}\right]}{\ln\beta}$$

(2)

$$\beta = \frac{1}{1 + \frac{C_{\text{flying}}}{C_{\text{load}}}} \tag{3}$$

where  $V_{\rm gain}$  is the maximum gained voltage at the flying capacitor, and (2) is expressed by the number of clock cycles. Large  $V_{\rm gain}$  is essential in reducing the rise time. However, it creates large ripple voltage in a steady state, because it increases the charge at load capacitor during the pumping period. Therefore, in a dynamic state,  $V_{\rm gain}$  during the pumping period should be maximized for fast rise time, and in a steady state, minimized for small ripple voltage.

## III. PROPOSED REGULATED CHARGE PUMP

# A. Automatic Pumping Current Control Scheme

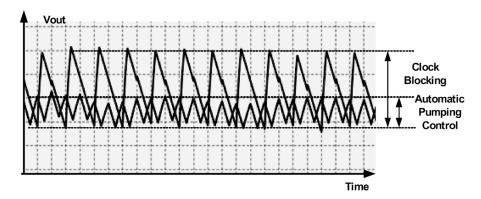

The proposed charge pump exploits the automatic pumping current control scheme; it changes pumping current according to the magnitude of the output voltage. At the low output voltage, the proposed charge pump uses large pumping current to rapidly increase output voltage. On the other hand, at the high output voltage, it reduces boosting power by turning off some of pumping drivers. Fig. 3 shows the reduction of output ripple voltage in the automatic pumping current control scheme, compared to the clock blocking scheme. In case of the conventional regulated charge pump, the output voltage is independent of the load resistance and has large ripple voltage because it always pumps the flying capacitor with full power. However the proposed charge pump using the automatic pumping current control scheme create a small ripple voltage with output voltage independent of load resistance.

Fig. 3. Reduction of output ripple voltage in automatic pumping control.

Fig. 4. Proposed charge pump.

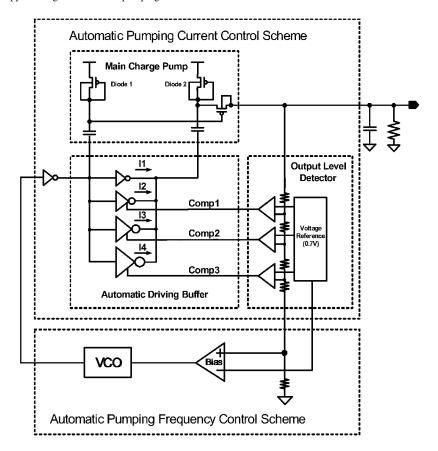

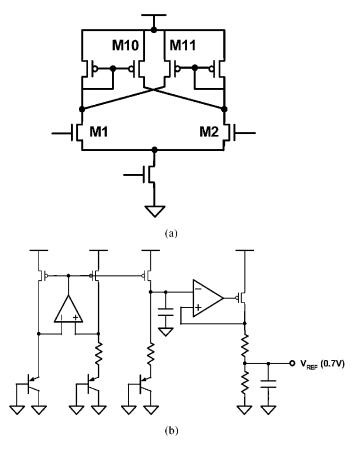

The automatic pumping current control scheme is realized by three functional blocks; a main charge pump (MCP), an output level detector (OLD), and an automatic driver (ADR), as shown in Fig. 4. The operation of the MCP is to charge the load capacitor. The OLD senses the output voltage level and generates control signals for the ADR. By using resistor chain, scaled values of output voltage are compared to the reference voltage of 0.7 V in each comparator. The voltage reference and the comparator are shown in Fig. 5(a) and (b), respectively.

The bandgap reference voltage generator generates an output voltage of 1.2 V and the reference voltage of 0.7 V is generated using a voltage divider. It adopts a self-biased cascade structure [8] to reduce the effect of supply voltage variations and can effectively remove switching noise. The comparator has two feedback paths: the negative feedback of M1 and M2, and the

positive feedback of M10 and M11 to accomplish hysteresis. It detects output voltage levels of 4.5, 4.8, and 5 V.

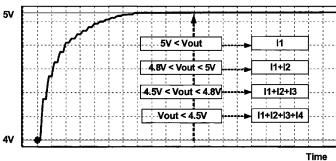

The ADR optimizes the pumping current by adjusting the number of buffers using the output value of the OLD, since the pumping current in (1) determines the ripple voltage. The operation of the ADR according to output voltage is shown in Fig. 6. When output voltage is low, the ADR provides full pumping current  $(I_1+I_2+I_3+I_4)$  to the flying capacitor and as output voltage rises, the pumping current delivered to the flying capacitor is stepwise reduced down to  $I_1$ .

## B. Automatic Pumping Frequency Control Scheme

To further reduce output ripple voltage, the proposed charge pump also exploits the automatic pumping frequency control scheme that has been developed in previous works [9], [10].

Fig. 5. (a) Comparator. (b) Voltage reference.

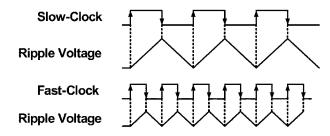

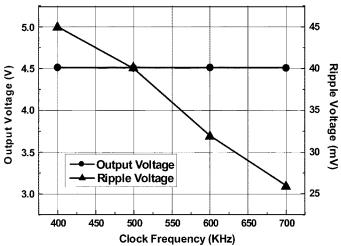

In (1), the switching frequency of the charge pump is related to the output ripple voltage. The switching frequency is equal to the pumping clock frequency because the proposed charge pump repeats the current pumping on every clock cycle, while the conventional charge pump with the clock blocking scheme continues to charge the load capacitor during the pumping period and stops during the blocking period. This switching frequency is larger than the pumping clock frequency. Fig. 7 shows the relationship between the output ripple voltage and the clock frequency. As (1) implies, the ripple voltage is inversely proportional to the switching frequency. The block diagram for the automatic pumping frequency control is shown in Fig. 4. A voltage-controlled oscillator (VCO) generates a clock signal, linearly determining the switching frequency. After the output voltage is detected, a bias block compares the voltage divided by resistors with the reference voltage and linearly converts that to the control voltage of the VCO. The operating clock frequency of the charge pump changes from 400 kHz to 600 kHz as output voltage rises.

# C. Analysis of Proposed Charge Pump

To reduce the output ripple voltage and the recovery time after the drop in output voltage, a  $V_{\rm gain}$  at each cycle is controlled according to output voltage. To analyze the proposed charge pump, the following assumptions are made:

1) The diode has constant forward bias voltage drop  $(V_t)$  when the diode is on.

Fig. 6. Simulation result of the proposed charge pump.

Fig. 7. Relationship between clock frequency and ripple voltage in the proposed charge pump.

Parasitic capacitance is negligibly small compared with the charge pump capacitance.

The pumping current  $i_{\mathrm{pump}}$  of the proposed charge pump is expressed as

$$i_{\text{pump}} = \sum_{j=1}^{n} i_j \quad (n = 1, 2, 3, 4)$$

(4)

where  $i_j$  is the pumping current delivered by each buffer in the ADR, and n is the index number of operating buffers which are operated by the output value of the OLD. The ripple voltage is obtained from (1) as

$$\Delta V_{\text{out}} = \frac{\sum_{j=1}^{n} i_j}{C_{\text{load}} \cdot f} = \frac{i_{\text{out}}}{C_{\text{load}} \cdot f}.$$

(5)

The pumping current is equal to that of the load resistor in a steady state. As load current increases, the output voltage level decreases, and the number of operating buffers increases.

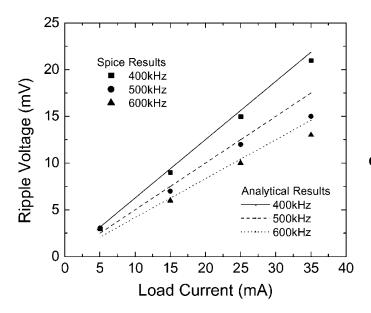

Fig. 8 shows the dependence of the ripple voltage on the load current and the switching frequency under the condition of  $V_{cc}=3.3~{\rm V}$  and  $C_L=2~\mu{\rm F}$ . The output ripple voltage is proportional to the load current and inversely proportional to the pumping clock frequency.

It is important to guarantee the fast recovery of the output voltage after the output voltage drops abruptly. In order to model the recovery time, Thevenin equivalent circuit for this charge pump is derived from a large signal model in a steady state and then the time constant of output node is calculated from the output resistance and capacitance of the equivalent circuit. Fig. 9(a) shows the operation of the proposed charge pump in steady state. The currents  $I_p$  and  $I_n$  flow through  $P_1$  and  $N_1$  in the pumping period and the blocking period, respectively. If the resistances of  $D_1$  and  $SW_1$  are sufficiently smaller than the

Fig. 8. Comparison of the analytical result with the SPICE simulation for the ripple voltage.

those of  $P_1$  and  $N_1$ ,  $V_{boost}$  is  $V_{out}$  or  $V_{cc} - V_t$  and  $V_{node}$  changes linearly as shown in Fig. 9(b) since  $P_1$  and  $N_1$  operate in triode region. The current  $I_p$  and  $I_n$  can be obtained from the current equation of MOSFET in a triode region as

$$I_{p}\left[nT, nT + \frac{T}{2}\right]$$

$$\approx \mu_{p}C_{ox}\frac{W_{p}}{L_{p}}\left\{(V_{cc} - V_{thp})(V_{cc} - V_{nh})\right.$$

$$\left. - \frac{(V_{cc} - V_{nh})^{2}}{2}\right\}$$

$$I_{n}\left[nT + \frac{T}{2}, (n+1)T\right]$$

$$\approx \mu_{n}C_{ox}\frac{W_{n}}{L_{n}}\left\{(V_{cc} - V_{thn})V_{nl} - \frac{V_{nl}^{2}}{2}\right\}$$

(7)

where  $V_{nh}$  and  $V_{nl}$  are the averages of  $V_{node}$  in the pumping period and the blocking period, respectively.

In a steady state, the output current is equal to the currents supplied by  $P_1$  and  $N_1$  for half cycle time ( $I_{\rm out}=I_p/2=I_n/2$ ) because the  $V_{\rm node}$  does not change according to clock cycle, and assuming  $V_{cc}-V_{thp}\gg V_{cc}-V_{nh}$  and  $V_{cc}-V_{thn}\gg V_{nl}$

$$V_{nl} = \frac{\mu_p}{\mu_n} \cdot \frac{W_p L_n}{L_p W_n} \cdot \frac{V_{cc} - V_{thp}}{V_{cc} - V_{thn}} (V_{cc} - V_{nh})$$

(9)

$$dV_{nl} = -\frac{\mu_p}{\mu_n} \cdot \frac{W_p L_n}{L_p W_n} \cdot \frac{V_{cc} - V_{thp}}{V_{cc} - V_{thn}} dV_{nh}. \tag{10}$$

According to the charge conservation law, the total charge stored in the circuit at time nT + T/4 is equal to the sum of

Fig. 9. (a) Operation of the proposed charge pump. (b) Timing diagram of  $V_{\rm boost}$  and  $V_{\rm node}.$

the charge flowing into load resistance for T/2 and the charges stored in the capacitors  $C_f$  and  $C_1$  at time nT + T3/4.

$$(V_{\text{out}} - V_{nh})C_f + V_{\text{out}}C_l$$

$$= (V_{cc} - V_t - V_{\text{nl}})C_f + V_{\text{out}}C_l + I_{\text{out}}\frac{T}{2}$$

$$dV_{\text{out}} = dV_{nh} - dV_{\text{nl}}$$

$$(12)$$

From (10) and (12)

$$dV_{\text{out}} = \left(1 + \frac{\mu_p}{\mu_n} \cdot \frac{W_p L_n}{L_n W_n} \cdot \frac{V_{cc} - V_{thp}}{V_{cc} - V_{thn}}\right) dV_{nh}. \tag{13}$$

By differentiating (6) and using (13)

$$dI_p \approx -\frac{\mu_p C_{\text{ox}} \frac{W_p}{L_p} (V_{cc} - V_{thp})}{1 + \frac{\mu_p}{\mu_n} \cdot \frac{W_p L_n}{L_p W_n} \cdot \frac{V_{cc} - V_{thp}}{V_{cc} - V_{thn}}} dV_{\text{out}}.$$

(14)

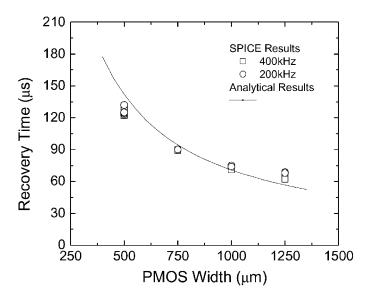

Fig. 10. Comparison of the analytical result with SPICE simulation for recovery time.

From (14), the relationship between the variations of  $V_{\rm out}$  and  $I_{\rm out}$  is expressed as

$$\frac{dV_{\text{out}}}{dI_{\text{out}}} \equiv R_{\text{rec}} \approx -\frac{2\left(1 + \frac{\mu_p}{\mu_n} \cdot \frac{W_p L_n}{L_p W_n} \cdot \frac{V_{cc} - V_{thp}}{V_{cc} - V_{thp}}\right)}{\mu_p C_{\text{ox}} \frac{W_p}{L_p} (V_{cc} - V_{thp})}.$$

(15)

$R_{\rm rec}$  represents the equivalent output series resistance of the proposed charge pump and is dependent on the electrical characteristics, the dimensions of transistors and the gate voltage. The recovery time that gets back up to 63% of  $\Delta V_{\rm out}$  is the time constant  $tR_{\rm rec}C_L$ .

Fig. 10 shows the comparison of the analytical result with the SPICE simulation for the recovery time as a function of the size of driver buffer under the condition of  $\Delta V_{\rm out}=0.4~{\rm V}\sim 2.4~{\rm V}$  and  $C_L=2~\mu{\rm F}$ . The analytical data have been in good agreement with the SPICE simulation results. Fig. 10 indicates that the recovery time does not depend on the switching frequency and  $\Delta V_{\rm out}$ , and is inversely proportional to the width of the pMOS  $(P_1)$ . Therefore, the recovery time of the proposed charge pump compared to the conventional charge pump decreases by stepwise increasing the size of the driving buffer when the output voltage reduces below the specified voltages.

### IV. EXPERIMENTAL RESULTS

The approach of the proposed charge pump is focused on producing small output ripple voltage while delivering large load current. To validate the results of our schemes, the proposed charge pump was fabricated using 3.3-V 0.13- $\mu$ m CMOS technology as the power supply circuit in an USB-OTG transceiver. The microphotograph is shown in Fig. 11. Its active area is 0.25 mm<sup>2</sup> except for a 330-nF external flying capacitor. On the bottom right side, the pumping MOS diodes are designed as large as possible to supply enough load current. The output stage of the proposed charge pump is composed of a variable load resistor and a 2- $\mu$ F load capacitor mounted on a test PCB.

Fig. 11. Microphotograph of proposed charge pump.

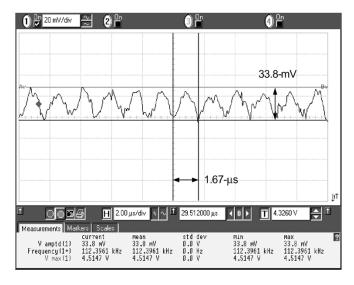

Fig. 12. Measurement results of output voltage.

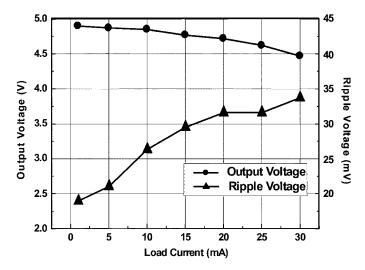

Fig. 12 shows that the output ripple voltage is 33.8 mV with the automatic pumping control scheme when the load current is 30 mA and the output voltage is 4.5 V. The rise time and fall time of the output voltage are equal to each other since the pumping operation is performed on every clock cycle and the clock duty cycle is 50%. In the conventional charge pump, these times are different because the charge pump stops pumping operations until the output voltage drops lower than the required output voltage level.

Fig. 13 shows the measured output and the ripple voltage versus the load current. A set of measurements has been performed by changing the value of the variable load resistor connected to the output. As load current increases, output voltage gradually drops to 4.5 V and output ripple voltage changes from

Fig. 13. Measurement results of output and ripple voltage as a function of load current.

Fig. 14. Measurement results of power efficiency.

18 mV to 33.8 mV. The ripple voltage is proportional to load current. However, the difference between the measured ripple voltage and the SPICE simulation result shown in Fig. 8 increases as the load current increases because the simulation result does not include the noise caused by parasitic components. The leakage current was through the pMOS used as SW1 in Fig. 9(a). This can also increase ripple voltage.

Power efficiency of a charge pump [11] is shown as

$$Eff_{power} = \frac{I_{out}V_{out}}{I_{power}V_{power}} \times 100.$$

(16)

The corresponding result is higher than 70% regardless of load current, as shown in Fig. 14. When the load current becomes smaller, the dynamic power loss caused by switching large transistors does not change and the ratio of the power loss over the output power increases. As a result, the power efficiency degrades as load current decreases.

To verify the effect of the pumping clock frequency on the output voltage and the output ripple voltage, the VCO is turned off and an external clock is applied as a pumping clock. Fig. 15 shows that the pumping clock frequency does not influence the

Fig. 15. Measurement results of output and ripple voltage as a function of clock frequency.

TABLE I PERFORMANCE SUMMARY OF THE PROPOSED CHARGE PUMP

| Supply Voltage | 3.3-V                  |

|----------------|------------------------|

| Pumping        | 400-kHz~ 600-kHz       |

| Frequency      |                        |

| Output Voltage | 4.5-V~5-V              |

| Ripple Voltage | 33.8-mV (with 2µF load |

|                | capacitor)             |

| Efficiency     | 70%~75%                |

| Area           | $0.25 \text{ mm}^2$    |

| Technology     | 3.3-V 0.13-µm CMOS     |

|                | technology             |

output voltage and the output ripple voltage is inversely proportional to the pumping clock frequency at a load current of 30 mA. In a steady state, output ripple voltage shows a linear triangle wave as shown in Fig. 12. Although clock frequency is changed, output voltage increase during a positive clock phase equals to the decrease during a negative clock phase. Therefore, the output voltage is not affected by frequency change.

Table I summarizes the performance characteristics of the proposed charge pump.

## V. CONCLUSION

A new regulated charge pump with low output ripple voltage and high load current drive capability is proposed enhancing tolerance of the output voltage variation. This proposed charge pump adopts the automatic pumping current control scheme and automatic pumping frequency scheme. The analysis of the charge pump is carried out to model the ripple voltage and the recovery time. The proposed charge pump is implemented using a 3.3-V 0.13- $\mu$ m CMOS technology. The test chip generates 4.5-V output from a 3.3-V supply with supplying up to 30 mA of load current. Its ripple voltage is less than 33.8 mV with a 2- $\mu$ F load capacitor. The power efficiency is higher than 70% at the range of load current from 1 mA to 30 mA. The proposed charge pump is used as the power supply circuit in the USB-OTG transceiver.

#### ACKNOWLEDGMENT

The authors would like to thank Samsung Electronics Corporation for the test chip and test PCB fabrication.

#### REFERENCES

- [1] J. A. Starzyk, Y.-W. Jan, and F. Qui, "A DC-DC charge pump design based on voltage doublers," *IEEE Trans. Circuits Syst. I: Fundam. Theory Appl.*, vol. 48, no. 3, pp. 350–359, Mar. 2001.

- [2] J. F. Dickson, "On-chip high-voltage generation in nMOS integrated circuits using an improved voltage multiplier technique," *IEEE J. Solid-State Circuits*, vol. SC-11, pp. 374–378, Jun. 1976.

- [3] T. Tanzawa and T. Tanaka, "A dynamic analysis of the Dickson charge pump," *IEEE J. Solid-State Circuits*, vol. 32, no. 8, pp. 1231–1240, Aug. 1907

- [4] G. Di Cataldo and G. Palumbo, "Design of an Nth order Dickson voltage multiplier," *IEEE Trans. Circuits Syst. I: Fundam. Theory Appl.*, vol. 43, pp. 414–418, May 1996.

- [5] S.-E. Kim, S.-J. Song, J. K. Kim, S. Kim, J.-Y. Lee, and H.-J. Yoo, "A small ripple regulated charge pump with automatic pumping control schemes," in *Proc. 30th Eur. Solid-State Circuits Conf.*, Sep. 2004, pp. 383–386.

- [6] T. Ogawa, S. Hatanaka, and K. Taniguchi, "An on-chip high-efficiency DC-DC converter with a compact timing edge control circuit," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2002, pp. 278–279.

- [7] T. Tanzawa and S. Atsumi, "Optimization of word-line booster circuits for low-voltage flash memories," *IEEE J. Solid-State Circuits*, vol. 34, no. 8, pp. 1091–1098, Aug. 1999.

- [8] B. Razavi, Design of Analog CMOS Integrated Circuits. New York: McGraw-Hill, 2001.

- [9] K. H. Aw, "Inconsistency in power down current caused by voltage control oscillator (VCO) of EPROM wordline charge pump," in *Proc.* 6th Int. Symp. Physical and Failure Analysis of Integrated Circuits, Jul. 1997, pp. 187–190.

- [10] J. Soldera, A. V. Boas, and A. Olmos, "A low ripple fully integrated charge pump regulator," in *Proc. 16th Symp. Integrated Circuits and Sys*tems Design, Sep. 2003, pp. 177–180.

- [11] R. Pelliconi, I. David, B. Andrea, P. Macro, and R. P. Luigi, "Power efficient charge pump in deep submicron standard CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 1068–1071, Jun. 2003.

**Seong-Jun Song** (S'01) received the B.S. (*summa cum laude*) and M.S. degrees in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2001 and 2004, respectively. He is currently working toward the Ph.D. degree in electrical engineering and computer science at KAIST.

Since 2001, he has been a Research Assistant at KAIST, where he worked on developing high-speed optical interface integrated circuits using submicron CMOS technology, phase-locked loops and clock and

data recovery circuits for high-speed data communications, and radio-frequency CMOS integrated circuits for wireless communications. His current research interests include ultra-low-power wearable/implantable biomedical microsystems and energy-efficient communication systems for body area and sensor networks.

**Jin Kyung Kim** was born in Anyang, Korea, in 1977. She received the B.S. and M.S. degrees in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2002 and 2004, respectively.

She then joined the Basic Research Laboratory of Electronics and Telecommunications Research Institute (ETRI), Daejeon. Since then, she has been engaged in the research and development of MEMS switch driver and intrabody communication system.

Sunyoung Kim (S'03) received the B.S. degree in electrical engineering from Yonsei University, Seoul, in 2002, and the M.S. degree in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2005. She is currently working toward the Ph.D. degree in electrical engineering and computer science at KAIST.

Her research includes low-voltage low-power sigma-delta modulators and mixed-signal integrated circuits. Her current research interests are related

to low-power biomedical microsystems and consumer applications including digital hearing aids.

Jae-Youl Lee (M'00) received the B.S. degree in metallurgical engineering from Hanyang University, Seoul, Korea, in 1992, and the M.S. and Ph.D. degrees in materials science and engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1994 and 1999, respectively.

From 1999 to 2003, he was with a DRAM design group at Hynix Semiconductor and designed a family of SDRAMs. In 2003, he was a visiting Professor with KAIST. He joined Samsung Electronics, Korea,

and has been involved in the development of high-speed serial interface from 2004.

Hoi-Jun Yoo (M'95–SM'05) graduated from the Electronic Department of Seoul National University, Seoul, Korea, in 1983, and received the M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, in 1985 and 1988, respectively. His Ph.D. work concerned the fabrication process for GaAs vertical optoelectronic integrated circuits.

From 1988 to 1990, he was with Bell Communications Research, Red Bank, NJ, where he invented the two-dimensional phase-locked VCSEL array,

the front-surface-emitting laser, and the high-speed lateral HBT. In 1991, he became Manager of a DRAM design group at Hyundai Electronics and designed a family of fast-1M DRAMs and synchronous DRAMs, including 256M SDRAM. From 1995 to 1997, he was a faculty member with Kangwon National University. In 1998, he joined the faculty of the Department of Electrical Engineering at KAIST, and led a project team on RAM Processors (RAMP). In 2001, he founded a national research center, System Integration and IP Authoring Research Center (SIPAC), funded by Korean government to promote worldwide IP authoring and its SOC application. Currently, he serves as the Project Manager for IT SoC and Post-PC in Korea Ministry of Information and Communication. His current interests are SOC design, IP authoring, high-speed and low-power memory circuits and architectures, design of embedded memory logic, optoelectronic integrated circuits, and novel devices and circuits. He is the author of the books DRAM Design (Seoul, Korea: Hongleung, 1996; in Korean) and High Performance DRAM (Seoul, Korea: Sigma, 1999; in Korean).

Dr. Yoo received the Electronic Industrial Association of Korea Award for his contribution to DRAM technology in 1994 and the Korea Semiconductor Industry Association Award in 2002.

**Sung-Eun Kim** (S'04) was born in Busan, Korea, in 1978. He received the B.S. degree in electrical and computer engineering from Hanyang University, Seoul, Korea, in 2002, and the M.S. degree in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2004.

He subsequently joined the Basic Research Laboratory of Electronics and Telecommunications Research Institute (ETRI), Daejeon. Since then, he has been engaged in the research and development

of MEMS switch driver and intrabody communication system.