Open access • Proceedings Article • DOI:10.1109/PES.2010.5589968

# A sequential AC/DC power flow algorithm for networks containing Multi-terminal VSC HVDC systems — Source link ☑

Jef Beerten, Stijn Cole, Ronnie Belmans

Institutions: Katholieke Universiteit Leuven

Published on: 25 Jul 2010 - Power and Energy Society General Meeting

Topics: Forward converter, High-voltage direct current, Power-flow study, AC power and Voltage source

# Related papers:

- Generalized Steady-State VSC MTDC Model for Sequential AC/DC Power Flow Algorithms

- Multi-terminal VSC HVDC for the European supergrid: Obstacles

- A Multi-Option Unified Power Flow Approach for Hybrid AC/DC Grids Incorporating Multi-Terminal VSC-HVDC

- Minimization of steady-state losses in meshed networks using VSC HVDC

- Impact of DC Line Voltage Drops on Power Flow of MTDC Using Droop Control

J. Beerten, S. Cole, and R. Belmans, "A sequential AC/DC power flow algorithm for networks containing multi-terminal VSC HVDC systems," *Proc. IEEE PES General Meeting PES GM* 2010, Minneapolis, USA, Jul. 25–29, 2010, 7 pages.

Digital Object Identifier: <u>10.1109/PES.2010.5589968</u>

URL:

http://ieeexplore.ieee.org/xpl/articleDetails.jsp?tp=&arnumber=5589968

© 2010 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works.

1

# A Sequential AC/DC Power Flow Algorithm for Networks Containing Multi-terminal VSC HVDC Systems

Jef Beerten, Student Member, IEEE, Stijn Cole, Student Member, IEEE, and Ronnie Belmans, Fellow, IEEE

Abstract—In this paper, a sequential AC/DC power flow algorithm is proposed to solve networks containing Multi-terminal Voltage Source Converter High Voltage Direct Current (VSC MTDC) systems. In VSC HVDC technology, the converter losses add up to a significant fraction of the overall system losses. However, they are often neglected or not taken into account in a proper manner in VSC HVDC power flows. The algorithm put forward in this paper takes the converter losses into account using a generalized converter loss model. The converter steady state equations are derived in their most general format, with the AC network power injections as controlled quantities. It is shown that correctly defining the power setpoints with respect to the system bus instead of the converter bus, as is often done to simplify calculations, requires additional iterative calculations. The DC system modelling method proposed in this paper does not impose any restriction on the HVDC grid topology. A VSC MTDC power flow solver is incorporated into MATPOWER to show the validity of the proposed algorithm.

Index Terms—HVDC transmission, HVDC converters, load flow analysis, VSC HVDC.

#### I. INTRODUCTION

N recent years, the power engineering world is showing a growing interest in power transmission based on High Voltage Direct Current (HVDC) technology in Multi-Terminal (MTDC) configurations. This interest is explained by an ever growing need for transmission capacity. Suggestions have been made to construct a whole new overlaying DC 'supergrid', in order to connect the growing share of renewables, which is often located far away from the load centers. The DC grid could be even offshore, connecting various offshore wind farms and other renewable energy sources [1], [2].

It is unclear whether the supergrid will ever see the light of day. Its precursors however, have been built and are in operation since long time: The two multi-terminal HVDC systems Hydro Québec - New England and the Sardiniamainland Italy link, commissioned in respectively 1992 and 1989. The application of MTDC was preceded by many studies since 1980, dealing with various aspects of MTDC. One of the more prominent topics was the solution of the power flow problem of the integrated AC/DC grid [3]–[7].

Jef Beerten is funded by a research grant from the Research Foundation – Flanders (FWO).

The authors are with the Department of Electrical Engineering (ESAT), Division ELECTA, Katholieke Universiteit Leuven, Kasteelpark Arenberg 10, bus 2445, 3001 Leuven-Heverlee, Belgium (e-mail: jef.beerten@esat.kuleuven.be, stijn.cole@esat.kuleuven.be, ronnie.belmans@esat.kuleuven.be).

The inherent technical specifics of the Current Source Converter (CSC) technology, on which the conventional HVDC systems are based, make that multi-terminal operation is impractical if more than three converters are involved, thus impeding an application of the technology in large scale, meshed DC grids: It is for instance difficult to reverse power flow in parallel operation and complex insulation and accurate grounding schemes are needed in series configuration.

Voltage Source Converters (VSC) HVDC have much better prospects for multi-terminal operation: The DC side behaves as a current source, rendering power flow reversal a trivial task. Unfortunately, because the operating principles of VSCs are so different from those of CSCs, the power flow algorithms developed for CSC MTDC cannot be directly used for its VSC counterpart. The general philosophy, however, remains the same. The solution methods are usually subdivided in sequential and unified methods. In sequential methods, the AC and DC equations are solved sequentially (e.g. in [6], [8]); in unified methods, the AC and DC system are solved together (e.g. in [7]). In this paper, the sequential approach is applied to the general AC/VSC MTDC system. The advantage of the sequential approach is that it is possible to incorporate a MTDC system into existing AC based power flow software, while in the unified approach the whole program implementation needs to be changed in order to solve the AC and DC system together.

It is not the first time that a sequential method for VSC MTDC power flow is developed. However, most of the methods presented in literature are not general enough: In [9] an approximate solution is obtained by neglecting converter losses and losses in the phase reactor, whereas in [10], converter losses are neglected, DC variables are not accessible and the power flow setpoints are defined at the converter bus instead of the system bus. This simplifies the calculations, but is not in accordance with current practice in actual VSC HVDC systems. The major contribution of this paper is the development of a general and detailed VSC MTDC power flow calculation, using the full power flow equations, including converter losses, and defining the power setpoints with respect to the system bus. The generalized modelling approach used for the DC network does not impose any restrictions on the topology or configuration of the DC network. Furthermore, it is shown how the VSC MTDC sequential power flow method can be implemented in an existing AC power flow package.

The remainder of the paper is organized as follows: The second section describes the modelling of the converter stations,

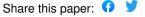

Fig. 1. VSC HVDC converter station.

including phase reactors, operating modes, and with special care for the converter losses, often neglected in VSC HVDC power flow. The third section discusses the DC grid power flow model and its efficient solution, proposed previously in our paper [11]. A fourth section addresses the interaction between the AC and the DC grid. It is shown in this section that defining the power setpoints with respect to the system bus requires additional iterative calculations. Finally, simulation results are discussed in the fifth section. The results are obtained by combining the proposed methodology with the open source Matlab toolbox, MATPOWER [12].

#### II. VSC CONVERTER STATIONS

In a VSC MTDC network, the VSC converter stations form the links between the AC and the DC networks. In this section, the modelling of the converter stations is discussed. A first part addresses the converter power flow equations and the assumptions used in the analysis. The second part discusses the different control modes. The inclusion of the converter losses into the power flow algorithm are treated in the third part of this section.

# A. Converter station model

In VSC transmission, a voltage waveform is synthesized by the converter station, either by a two-level or multilevel Pulse Width Modulation (PWM) technique, commercially available as HVDC Light [13] or by using a multimodular converter (MMC) approach, commercially available as HVDC PLUS [14]. When the output wave forms are synthesized using PWM, the converter station includes low pass filter equipment to block the flow of higher order harmonics into the AC transmission system. In the MMC technology the sine output waves are directly built up by the inverter outputs without using a PWM technique, resulting in the absence of filtering requirements. Fig. 1 shows a VSC HVDC converter station with the phase reactors, transformer and low pass filters (displayed in gray).

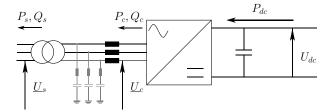

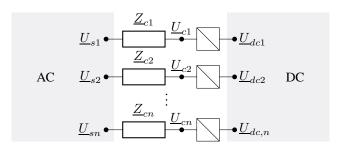

Regarding the power flow algorithms, a converter stations can be modelled as a controllable voltage source behind a complex impedance, which includes both the phase reactor and the transformer. Since the filtering requirements are heavily dependent on the technology considered, the filters are not taken into account in this paper. Fig. 2 shows a single phase equivalent diagram of n converter stations connected to different busses in the AC network.

The converter equations reduce to these of an impedance with a controllable voltage at the converter side. With  $\underline{U}_s$  =

Fig. 2. Equivalent single phase power flow model for multiple converter stations connected to the AC grid.

$U_s \angle \delta_s$  and  $\underline{U}_c = U_c \angle \delta_c$  respectively the AC bus voltage and the converter voltage and  $\underline{Z}_c = G_c + \jmath B_c$  the complex equivalent impedance, the equations for the power injected into the AC grid are given by

$$P_s = -U_s^2 G_c + U_s U_c [G_c \cos(\delta_s - \delta_c) + B_c \sin(\delta_s - \delta_c)](1)$$

$$Q_s = U_s^2 B_c + U_s U_c [G_c \sin(\delta_s - \delta_c) - B_c \cos(\delta_s - \delta_c)](2)$$

The power flowing to the AC network at the converter end can be written as

$$P_c = U_c^2 G_c - U_s U_c [G_c \cos(\delta_s - \delta_c) - B_c \sin(\delta_s - \delta_c)] (3)$$

$$Q_c = -U_c^2 B_c + U_s U_c [G_c \sin(\delta_s - \delta_c) + B_c \cos(\delta_s - \delta_c)] (4)$$

#### B. Converter control modes

Contrary to the LCC technology, which suffers from a high reactive power demand due to the firing delays and the commutation process, the VSC technology is able to control the reactive power flow at each converter station independently from the active power output to the AC grid (constant Q-control). There is also a possibility for the converters to control the AC bus voltage magnitude  $U_s$  by adopting its reactive power output to keep up the system voltage in a way similar to a synchronous generator (constant V-control).

When the two-terminal VSC HVDC concept is extended to a multi-terminal configuration, all but one converter control their active power injection into (or withdrawn from) the AC grid (constant P-control). One converter station will adopt its active power injection to control its DC bus voltage  $U_{dc}$ . In this way, this converter can be regarded as a "DC slack converter". The converter stations can therefore be in PQ- or PV-control, with an exception being made for the converter connected to the DC slack bus. The actual value of the active power injection of this converter is not known prior to the power flow as this quantity depends on the losses in the DC network and in the converter station, as will be shown in the next section.

#### C. Converter station losses

Apart from the losses in the phase reactor, which are taken into account by the equivalent phase impedance  $\underline{Z}_c$ , the other

TABLE I PER UNIT CONVERTER LOSS COEFFICIENTS

|           | a      | b     | c     |                  |  |

|-----------|--------|-------|-------|------------------|--|

| rectifier | 11.033 | 3.464 | 4.400 | $\times 10^{-3}$ |  |

| inverter  | 11.055 | 3.404 | 6.667 | X 10             |  |

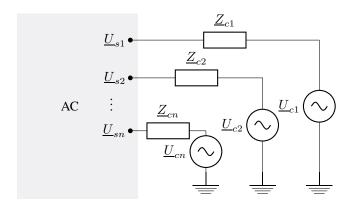

Fig. 3. Equivalent single phase power flow model of a 4-bus DC network.

converter losses are taken into account using a generalized converter station loss model for a typical VSC HVDC link with a rating of 600 MW and a DC voltage of  $\pm 300 kV$  [15]. In this loss model, the converter station losses are written as a function of the reactor current magnitude  $I_c$  and thus of the active and reactive power exchanged with the AC system. The overall converter losses  $P_{loss}$  can be split up into three aggregated loss components, further discussed in [16]: No load losses and losses linearly and quadratically depending on the reactor current:

$$P_{loss} = a + b \cdot I_c + c \cdot I_c^2, \tag{5}$$

$$P_{loss} = a + b \cdot I_c + c \cdot I_c^2,$$

with  $I_c = \frac{\sqrt{Pc^2 + Qc^2}}{\sqrt{3}U_c}.$

$$(5)$$

The per unit coefficients a, b and c in Tab. I are based on the data provided in [15] and are used in the sequential AC/DC power flow algorithm.

# III. DC GRID MODEL

The DC grid model used in this paper and presented in [11], is similar to the AC network models used in a conventional AC power flow. In a steady state analysis, the overall flow pattern is dictated by the line resistances and the DC voltage magnitude differences between the DC busses. Fig. 3 shows an equivalent steady state model of a 4-bus DC grid, which can be implemented using a pure resistance network.

The current injected at a DC node i can thus be written as the current flowing to the other n-1 nodes in the network

$$I_{dc,i} = \sum_{\substack{j=1\\j\neq i}}^{n} Y_{dc,ij} \cdot (U_{dc,i} - U_{dc,j}). \tag{7}$$

Combining all currents injected in the DC network by the VSC converters results in

$$I_{dc} = Y_{dc} U_{dc},$$

(8)

Fig. 4. Schematic overview of the sequential power flow approach

with  $I_{dc} = [I_{dc,1}, I_{dc,2} \dots I_{dc,n}]^T$  the DC current vector,  $U_{dc} = [U_{dc,1}, U_{dc,2} \dots U_{dc,n}]^T$  the DC voltage vector and  $Y_{dc}$ the DC bus matrix. Assuming a bipolar DC grid, the active power injected in node i can be written as

$$P_{dc,i}=2U_{dc,i}I_{dc,i}, \quad \forall i \le n. \tag{9}$$

The current injections  $I_{dc}$  are not known prior to the power flow solution for the DC grid, whereas the active power injections  $P_{dc}$  are known as a results of the AC power flow for all busses except for the DC slack bus. Combining (8) and (9) results in a system of non-linear equations:

$$0 = \mathsf{Y}_{\mathsf{dc}} U_{dc} - \left[ \frac{P_{dc,i}}{2U_{dc,i}} \right]. \tag{10}$$

As one DC bus controls its DC voltage and the others control their active power injection, the problem has to be rearranged. To simplify notation, but without loss of generality, we assume the last converter to be the DC slack bus. The vector of the unknowns can be written as

$$\boldsymbol{X} = \begin{bmatrix} \boldsymbol{X_1} \\ \boldsymbol{X_2} \end{bmatrix} = \begin{bmatrix} U_{dc,1} \\ \vdots \\ U_{dc,(n-1)} \\ P_{dc,n} \end{bmatrix}. \tag{11}$$

The DC bus admittance matrix is partitioned as follows:

$$Y_{dc} = \begin{bmatrix} Y_{11} & Y_{12} \\ \hline Y_{21} & y_{22} \end{bmatrix}$$

(12)

The matrix  $Y_{11}$  is of dimension (n-1) x (n-1),  $Y_{12}$  is a column vector of length n-1,  $Y_{21}$  a row vector of length n-1, and  $y_{22}$  a scalar.

This leads to a system of equations that can be solved by an iterative Newton method:

$$\begin{cases} 0 = \mathsf{Y}_{11}X_1 + Y_{12} \cdot u_{dcref} - P_{dc,i}/(2X_{1i}) \\ 0 = Y_{21}X_1 + y_{22} \cdot u_{dcref} - X_2/(2u_{dcref}) \end{cases}$$

(13)

#### IV. AC/DC POWER FLOW

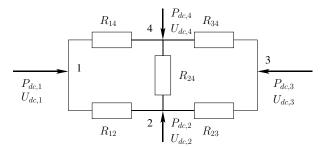

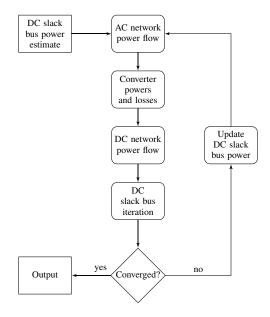

The models derived in the previous section are now combined in a sequential AC/DC power flow algorithm. Fig. 4 shows a generalized MTDC network based on VSC technology with n terminals. In the sequential approach, the DC grid variables are used as inputs to solve the AC equations and vice versa, which allows an easy integration of DC grids into existing AC power flow programs.

Fig. 5. Sequential flow chart of the sequential VSC AC/DC power flow algorithm.

Fig. 5 shows the flow chart of the sequential power flow algorithm. As discussed in the previous section, the DC network as well as the AC network each have to be solved iteratively. Due to the converter loss inclusion, an extra internal iteration is needed to calculate the DC slack bus active power injection  $P_{s,n}$  when the DC power injection is known as a result of the DC network power flow. Apart from these internal iterations, an external iteration is needed to ensure that the overall solution converges while the overall power flow solution changes due to the updates of the DC slack bus power injection. In this section, the different parts of the sequential power flow shown in Fig. 5 will be subsequently addressed.

# A. AC network power flow

The power flow equations for bus i in an AC grid with m nodes can be written as

$$P_{i}(\boldsymbol{U}, \boldsymbol{\delta}) = U_{i} \sum_{j=1}^{m} U_{j} \left[ G_{ij} \cos(\delta_{i} - \delta_{j}) + B_{ij} \sin(\delta_{i} - \delta_{j}) \right],$$

(14)

$$Q_i(\boldsymbol{U}, \boldsymbol{\delta}) = U_i \sum_{j=1}^m U_j \left[ G_{ij} \sin(\delta_i - \delta_j) - B_{ij} \cos(\delta_i - \delta_j) \right].$$

(15)

The non-linear set of power flow equations for all AC busses can be solved using a standard Newton-Raphson based power flow:

$$\begin{bmatrix} \left(\frac{\partial \mathbf{P}}{\partial \boldsymbol{\delta}}\right)^{(k)} & \left(\mathbf{U}\frac{\partial \mathbf{P}}{\partial \mathbf{U}}\right)^{(k)} \\ \left(\frac{\partial \mathbf{Q}}{\partial \boldsymbol{\delta}}\right)^{(k)} & \left(\mathbf{U}\frac{\partial \mathbf{Q}}{\partial \mathbf{U}}\right)^{(k)} \end{bmatrix} \begin{bmatrix} \mathbf{\Delta}\boldsymbol{\delta}^{(k)} \\ \mathbf{\Delta}\underline{\mathbf{U}}^{(k)} \end{bmatrix} = \begin{bmatrix} \mathbf{\Delta}\mathbf{P}^{(k)} \\ \mathbf{\Delta}\mathbf{Q}^{(k)} \end{bmatrix}$$

(16)

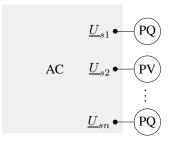

In the sequential algorithms, the converter stations are included in the AC network calculations as shown in Fig. 6. To include the VSC stations, the power mismatches  $\Delta P^{(k)}$  and  $\Delta Q^{(k)}$  in (16) are extended to include the power injections by the converter stations into the AC network. If the converter is in

Fig. 6. AC network power flow with converter stations treated as constant negative loads and voltage controlled busses.

a constant Q-control mode, the reactive output is added to the power mismatches as a negative load:

$$\Delta Q_i^{(k)} = Q_i^{gen} - (Q_i^{dem} - Q_{s,i}) - Q_i(U^{(k)}, \delta^{(k)}).$$

(17)

If the converter is used in a constant V-control, the station can be treated in a way similar to a voltage controlling AC generator, with an unknown reactive power injection. This is implemented by changing the AC bus from a PQ-node into a PV-node with a dummy generator to calculate the reactive power input.

For every converter station, except for the DC slack converter, the active power injection  $P_s$  into the AC grid is known. The active power mismatches are extended as

$$\Delta P_i^{(k)} = P_i^{gen} - (P_i^{dem} - P_{s,i}) - P_i(U^{(k)}, \boldsymbol{\delta}^{(k)}).$$

(18)

For the DC slack converter, the active power injection itself is a result of the power flow solution and therefore unknown. As an initial estimate, the converter stations, phase reactors and the DC network are assumed to be lossless. With the  $n^{th}$  converter station operating as the DC slack converter,

$$P_{s,n}^{(0)} = -\sum_{j=1}^{n-1} P_{s,j}.$$

(19)

For the  $k^{th}$  iteration, the solution from the previous iteration cycle is used as an estimate for  $P_{s,n}^{(k)}$ .

# B. Converter calculation and DC network power flow

Once the AC grid voltages  $\underline{U}_s$  and power injections  $P_s$  and  $Q_s$  are known as a result of the AC power flow, the voltages  $\underline{U}_c$  at the converter side can be found by first calculating the converter currents  $\underline{I}_c$

$$\underline{I}_{c,i} = \frac{P_{s,i} - jQ_{s,i}}{U_{s,i}^*}, \ \forall i < n.$$

(20)

Using this expression for  $\underline{I}_{c,i}$  to calculate the complex voltage drop over the converter impedance  $\underline{Z}_{c,i}$ , the voltage at the converter side can be written as

$$\underline{U}_{c,i} = \underline{U}_{s,i} - \underline{Z}_{c,i} \cdot \frac{P_{s,i} - \jmath Q_{s,i}}{U_{s,i}^*}, \ \forall i < n.$$

(21)

The converter powers at the converter side  $P_c$  and  $Q_c$  are thereafter calculated using (3) - (4). After calculating the converter power losses  $P_{loss}$  using (5), the DC grid power inputs are known. The DC network voltages  $U_{dc}$  and DC slack bus power  $P_{dc,n}$  result from iteratively solving (13).

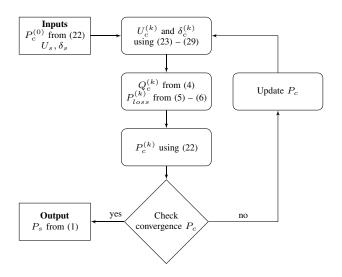

Fig. 7. DC Slack bus iteration flow chart.

#### C. DC slack bus iteration

After calculating the DC network, the active power  $P_{s,n}$ injected into the AC grid by the DC slack bus converter has to be solved iteratively since the converter losses depend on the converter current magnitude  $I_{c,n}$ , which is yet unknown. The procedure put forward in this paper uses the previous AC grid state to calculate the DC slack bus active power injection  $P_{s,n}$ . The voltage at the grid side of the DC slack bus converter  $\underline{U}_{s,n}$  is kept constant (both in magnitude and in phase angle) to calculate  $P_{s,n}$  since it is the solution for the iteration cycle under consideration. Also  $Q_{s,n}$ , the reactive power injected into the grid by the DC slack bus converter is kept constant during the DC slack bus iteration, due to the strong relation between reactive power and voltage magnitude, which is kept constant at the grid side for this iteration cycle.

The iteration to calculate the DC slack bus power injection into the AC grid is depicted in Fig. 7. The subscript nto indicate the slack bus has been omitted to simplify the notation. To start the iteration, an initial estimate is needed for the converter side active power injection. Using the power injection resulting from the DC power flow and an estimation of the converter losses  $P_{loss,n}^{(0)}$  deducted from the results of the AC network power flow in the overall iteration cycle, an initial value is given by

$$P_{c,n}^{(k)} = P_{dc,n} - P_{loss,n}^{(k)}. (22)$$

By convention, the power flow direction is chosen to be positive when power is flowing to the AC network bus. In the calculation of the DC slack bus active power injection, a Newton-Raphson iteration is used to calculate  $U_c^{(k)}$  and  $\delta_c^{(k)}$ using (2) - (3):

$$\begin{bmatrix} \begin{pmatrix} \frac{\partial P_c}{\partial \delta_c} \end{pmatrix}^{(j)} & \begin{pmatrix} U_c \frac{\partial P_c}{\partial U_c} \end{pmatrix}^{(j)} \\ \begin{pmatrix} \frac{\partial Q_s}{\partial \delta_c} \end{pmatrix}^{(j)} & \begin{pmatrix} U_c \frac{\partial Q_s}{\partial U_c} \end{pmatrix}^{(j)} \end{bmatrix} \begin{bmatrix} \Delta \delta_c^{(j)} \\ \frac{\Delta U_c}{U_c} \end{bmatrix} = \begin{bmatrix} \Delta P_c^{(j)} \\ \Delta Q_s^{(j)} \end{bmatrix}. \quad (23)$$

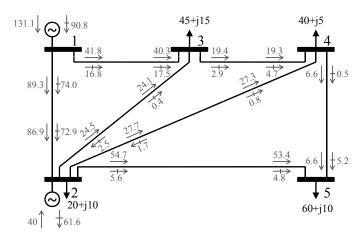

Fig. 8. Line powers of the 5-bus test network without the VSC MTDC system. **Legend**:  $\rightarrow$  Active power (MW) and  $\rightarrow$  Reactive power (MVAr).

TABLE II AC BUS VOLTAGES WITHOUT AND WITH A VSC MTDC SYSTEM

| bus | type  | Without  | MTDC           | With MTDC |                |  |

|-----|-------|----------|----------------|-----------|----------------|--|

|     |       | U (p.u.) | $\delta$ (deg) | U (p.u.)  | $\delta$ (deg) |  |

| 1   | slack | 1.060    | 0.00           | 1.060     | 0.00           |  |

| 2   | PV    | 1.000    | -2.06          | 1.000     | -2.39          |  |

| 3   | PQ    | 0.987    | -4.64          | 1.000     | -3.90          |  |

| 4   | PQ    | 0.984    | -4.96          | 0.996     | -4.27          |  |

| 5   | PQ    | 0.972    | -5.77          | 0.991     | -4.15          |  |

The elements of this Jacobian matrix are given by

$$\left(\frac{\partial P_c}{\partial \delta_c}\right)^{(j)} = -Q_c^{(j)} - U_c^{(j)^2} B_c, \tag{24}$$

$$\left(U_c \frac{\partial P_c}{\partial U_c}\right)^{(j)} = P_c^{(j)} + U_c^{(j)^2} G_c, \tag{25}$$

$$\left(\frac{\partial Q_s}{\partial \delta_c}\right)^{(j)} = -P_s^{(j)} - U_s^2 G_c, \tag{26}$$

$$\left(U_c \frac{\partial Q_s}{\partial U_c}\right)^{(j)} = Q_s^{(j)} - U_s^2 B_c, \tag{27}$$

with values for  $P_s,Q_s,P_c$  and  $Q_c$  from (1) – (4). The power mismatches  $\Delta P_c^{(j)}$  and  $\Delta Q_s^{(j)}$  can be written as

$$\Delta P_c^{(j)} = P_c^{(k)} - P_c(U_c, U_c^{(j)}), \tag{28}$$

$$\Delta P_c^{(j)} = P_c^{(k)} - P_c(\underline{U}_s, \underline{U}_c^{(j)}), \qquad (28)$$

$$\Delta Q_s^{(j)} = Q_s - Q_s(\underline{U}_s, \underline{U}_c^{(j)}). \qquad (29)$$

In these equations, the superscript j refers to the inner NR iteration, whereas the superscript k refers to the outer DC slack bus iteration.

After a convergence of  $P_{c,n}$ , the active power injected into the AC network  $P_{s,n}$  is calculated (Fig. 7) and thereafter checked for convergence in the overall iteration loop (Fig. 5).

#### V. SIMULATION RESULTS

In order to demonstrate the effectiveness of the proposed sequential algorithm, the sequential AC/VSC MTDC power flow algorithm has been integrated with the AC power flow program MATPOWER [12], an open-source Matlab toolbox. The input data format is similar to the format used for AC

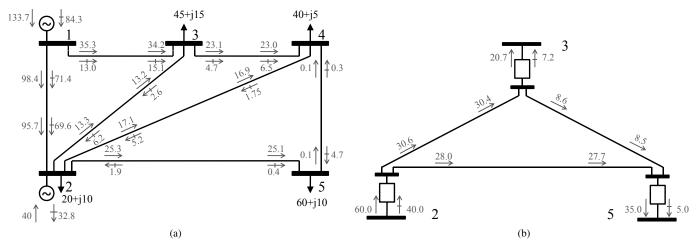

Fig. 9. Power flow solution with a VSC MTDC system between busses 2, 3 and 5: (a) Line powers in the 5-bus test network, (b) Line powers and AC grid injections of the 3-bus VSC MTDC system. Legend:  $\rightarrow$  Active power (MW) and  $\rightarrow$  Reactive power (MVAr).

TABLE III POWER FLOW SOLUTION WITH A VSC MTDC SYSTEM - CONVERTER STATIONS

| bus | Control mode | Converter Voltage |                  | Bus injection |              | Reactor loss |          | Converter loss  | DC Power      | DC Voltage        |

|-----|--------------|-------------------|------------------|---------------|--------------|--------------|----------|-----------------|---------------|-------------------|

|     |              | $U_c$ (p.u.)      | $\delta_c~(deg)$ | $P_s$ (MW)    | $Q_s$ (MVAr) | P(MW)        | Q (MVAr) | $P_{loss}$ (MW) | $P_{dc}$ (MW) | $U_{dc}$ $(p.u.)$ |

| 2   | P - Q        | 0.984             | -3.760           | -60.00        | -40.00       | 0.05         | 2.08     | 1.36            | -58.59        | 1.008             |

| 3   | Slack - V    | 1.003             | -3.431           | 20.68         | 7.17         | 0.00         | 0.19     | 1.15            | 21.84         | 1.000             |

| 5   | P - Q        | 0.993             | -3.340           | 35.00         | 5.00         | 0.01         | 0.51     | 1.19            | 36.21         | 0.998             |

power flows. A general DC grid can therefore be simulated, with an arbitrary number of terminals and topology. Simulations were carried out on a 5-bus test network based on [17], [18] with a 3-terminal MTDC network and on the IEEE 300-bus network with a 10-terminal MTDC network. The results from the 5-bus network are included in this paper and are discussed in this section.

Fig. 8 shows the line powers of the power flow solution without a MTDC network. The bus voltages of this solution are given in Tab. II. The MTDC network is connected between busses 2, 3 and 5. The converter at bus 3 is chosen as DC slack converter, thereby controlling the voltage on the DC network. The DC slack converter is also used to control the voltage at bus 3, whereas the other converters are directly controlling their reactive power injections (constant Q-mode). Data on the converter station phase reactors and line resistances were obtained from [13]. The results of the sequential algorithm are shown in Figs. 9a and 9b. The AC bus voltages are given in Tab. II. Since the converter station at bus 3 is working in a voltage controlling mode, the reactive power injection is adapted in order to keep  $U_{s,3}$  equal to 1.0 p.u.. The results on the converter stations are included in Tab. III. From this table, it is clear that the constant power losses take the largest share in the converter station losses. This is due to the fact that a base power of 100 MW is used for the MTDC connection whereas the MTDC loading is kept relatively low.

## VI. CONCLUSION

The sequential AC/DC power flow algorithm presented in this paper effectively solves AC networks containing VSC MTDC systems. The proposed solution method is general and offers the ability to include an arbitrary DC system into existing AC networks. There are no limits on the number of converters or on the topology of the DC grid. The algorithm is also accurate: Converter losses are represented by a generalized loss model based on a second order function of the reactor current and the full power flow equations are used for the AC side of the converter. Furthermore, the power setpoints are defined with respect to the system voltage, which necessitates an additional iterative procedure for the DC slack bus converter. The method has been implemented in MATPOWER, and properly tested. Numerical simulations show the validity of the algorithm to include an arbitrary VSC MTDC system into an AC network.

#### REFERENCES

- [1] S. Gordon, "Supergrid to the rescue," *Power Engineer*, vol. 20, no. 5, pp. 30–33, Oct.-Nov. 2006.

- [2] W. Lu and B.-T. Ooi, "Optimal acquisition and aggregation of offshore wind power by multiterminal voltage-source HVDC," *IEEE Trans. Power Del.*, vol. 18, no. 1, pp. 201–206, 2003.

- [3] C. M. Ong and A. Hamzei-nejad, "A general-purpose multiterminal DC load-flow," *IEEE Trans. Power App. Syst.*, vol. PAS-100, no. 7, pp. 3166– 3174, Jul. 1981.

- [4] H. Fudeh and C. M. Ong, "A simple and efficient AC-DC load-flow method for multiterminal DC systems," *IEEE Trans. Power App. Syst.*, vol. PAS-100, no. 11, pp. 4389–4396, Nov. 1981.

- [5] T. Smed, G. Andersson, G. B. Sheble, and L. L. Grigsby, "A new approach to AC/DC power flow," *IEEE Trans. Power Syst.*, vol. 6, no. 3, pp. 1238–1244, Aug. 1991.

- [6] M. E. El-Hawary and S. T. Ibrahim, "A new approach to AC-DC load flow analysis," *Electric Power Systems Research*, vol. 33, no. 3, pp. 193 – 200, 1995.

- [7] M. El-Marsafawy and R. Mathur, "A new, fast technique for load-flow solution of integrated multi-terminal AC/DC systems," *IEEE Trans. Power App. Syst.*, vol. 99, no. 1, p. 10, Jan./Feb. 1980.

- [8] U. Arifoglu, "The power flow algorithm for balanced and unbalanced bipolar multiterminal ac-dc systems," *Electric Power Systems Research*, vol. 64, no. 3, pp. 239 – 246, 2003.

- [9] Q. Chen, G.-Q. Tang, and W. X., "AC-DC power flow algorithm for multi-terminal VSC-HVDC systems," *Electric power automation equipment*, vol. 25, no. 6, p. 6, 2005.

- [10] L. Gengyin, Z. Ming, H. Jie, L. Guangkai, and L. Haifeng, "Power flow calculation of power systems incorporating VSC-HVDC," in *Proc. International Conference on Power System Technology PowerCon* 2004, vol. 2, Nov. 21–24, 2004, pp. 1562–1566.

- [11] S. Cole, J. Beerten, and R. Belmans, "Generalized dynamic VSC MTDC model for power system stability studies," *IEEE Trans. Power Syst.*, submitted for publication.

- [12] MATPOWER website. [Online]. Available: http://www.pserc.cornell.edu/matpower/

- [13] P. Haugland, "It's time to connect technical description of HVDC Light technology," ABB, Tech. Rep., March 2008.

- [14] M. Davies, M. Dommaschk, J. Dorn, J. Lang, D. Retzmann, and D. Soerangr, "HVDC PLUS basics and principle of operation," Siemens, Tech. Rep., 2008.

- [15] G. Daelemans, K. Srivastava, M. Reza, S. Cole, and R. Belmans, "Minimization of steady-state losses in meshed networks using VSC HVDC," in *Proc. IEEE PES General Meeting '09*, Calgary, Canada, Jul. 26–30 2009.

- [16] G. Daelemans, "VSC HVDC in meshed networks," Master's thesis, Katholieke Universiteit Leuven, Leuven, 2008.

- [17] S. G. W. and A. H. El-Abaid, Computer Methods in Power System Analysis. Kogakusha, Japan: McGraw-Hill, 1968.

- [18] E. Acha, C. R. Fuerte-Esquivel, H. Ambriz-Pérez, and C. Angeles-Camacho, FACTS: Modelling and Simulation in Power Networks. West-Sussex, England: John Wiley & Sons, 2004.

Jef Beerten (S'07) was born in Belgium in 1985. He received the M.Sc. degree in electrical engineering from the Katholieke Universiteit Leuven (K.U.Leuven), Leuven, Belgium, in 2008, where he is currently working towards the Ph.D. degree. He is a Research Assistant with the division ESAT-ELECTA division of K.U.Leuven. His research interests include power system control, integration of renewables and multiterminal HVDC in particular.

Mr. Beerten holds a Ph.D. fellowship from the Research Foundation Flanders (FWO).

Stijn Cole (S'06) received the M.Sc. degree in electrical engineering in 2005 from the Katholieke Universiteit Leuven (K.U.Leuven), Belgium. Since 2005 he is working as a research assistant at K.U.Leuven. He is a member of ELECTA, the Electrical Energy research group, of the department of Electrical Engineering of the K.U.Leuven, where he is working towards a Ph.D. His fields of interest include power systems, grid of the future, and HVDC.

Ronnie Belmans (S'77-M'84-SM'89-F'05) received the M.Sc. degree in electrical engineering in 1979 and the Ph.D. degree in 1984, both from the K.U.Leuven, Belgium, the Special Doctorate in 1989 and the Habilitierung in 1993, both from the RWTH, Aachen, Germany. Currently, he is a full professor with the K.U.Leuven, teaching electric power and energy systems. His research interests include techno-economic aspects of power systems, power quality and distributed generation. He is also guest professor at Imperial College of Science, Medicine

and Technology, London-UK. Since June 2002 he is chairman of the board of directors of ELIA, the Belgian transmission grid operator.