# A Simple, Accurate Capacitance–Voltage Model of Undoped Silicon Nanowire **MOSFETs**

Shihuan Lin, Xing Zhou, Guan Huei See, Guojun Zhu, Chengqing Wei, Junbin Zhang, and Zuhui Chen

School of Electrical & Electronic Engineering, Nanyang Technological University Nanyang Avenue, Singapore 639798, exzhou@ntu.edu.sg

# ABSTRACT

This paper presents a simple, accurate charge and capacitance model for undoped cylindrical gate-allaround (GAA) silicon-nanowire (SiNW) MOSFETs. The charge and capacitance model is derived from our surface-potential-based current model in which major non-ideal effects, such as velocity saturation, mobility degradation, channel-length modulation, and draininduced barrier lowering, are included. Based on proper approximations, simple charge and capacitance expressions are obtained and the validity is confirmed by comparison with numerical simulations.

Keywords: nanowire, MOSFET, compact model, C-V modeling.

### **1 INTRODUCTION**

The Gate-All-Around (GAA), or surrounding-gate, MOSFET is one of the most promising structures beyond bulk CMOS. Since early investigations on GAA/SOI devices [1], most recent experiments have demonstrated GAA silicon-nanowire (SiNW) structures with controlled diameters on the order of 3~6 nm using conventional CMOS technology [2]. Theoretically, GAA MOSFETs provide better gate electrostatic control capability than planar and double-gate (DG) counterparts. For long-channel GAA SiNW MOSFETs, much work has been devoted to modeling I-V characterization [3,4,5] and also C-V characterization [6,7,8].

In short-channel devices, non-ideal effects play an important role in device characterization, which need to be included in the model.

In the proposed model, a simple, accurate charge and capacitance model for short-channel undoped GAA SiNW MOSFETs is developed based on our surface-potentialbased current model [9]. The model is valid in all operation regimes including linear, saturation, volume inversion, strong inversion, and the "accumulation" regimes. The comparison between numerical simulations and the proposed model shows good agreement. The proposed model is suitable for circuit simulation and is extended to short-channel devices.

#### MODEL EQUATION 2

A charge-sheet approximation current expression for a

long-channel undoped GAA SiNW MOSFETs is written as:

$$I_{ds} = 2\pi R \mu Q_{sc} (y) \frac{dv_c}{dy}$$

$$\approx -\mu \frac{2\pi R}{L} \int Q_{sc} (y) d\phi_s + \mu v_{th} \frac{2\pi R}{L} \int dQ_{sc} (y)$$

$$= \mu \frac{2\pi R C_{as}}{L} \Big[ (V_{gf} + v_{th}) \cdot \Delta \phi - \Delta \phi \cdot \overline{\phi} \Big]$$

(1)

where

$$\Delta \phi = \phi_s \left( L \right) - \phi_s \left( 0 \right) \tag{2a}$$

and

$$\overline{\phi_s} = \frac{\phi_s(0) + \phi_s(L)}{2}.$$

(2b)

$\phi_s(0)$  and  $\phi_s(L)$  are the surface potentials at the source and drain, respectively,  $C_{ox}$  is the cylindrical capacitor of the gate oxide,  $V_{gf} \equiv V_{gs} - V_{FB}$  is the flatband-shifted gate voltage where  $V_{FB}$  is the flatband voltage,  $v_{th} = kT/q$  is the thermal voltage, R is the radius of SiNW,  $\mu$  is the mobility of electrons.

The expression of *y* is obtained from (1):

$$y = \frac{2\pi R\mu}{I_{ds}} \int_{V_s} Q_{sc}(y) dV_c$$

$$= \frac{L}{\left[ \left( V_{gf} + 2v_{th} \right) - \overline{\phi_s} \right] \Delta \phi} \left[ \left( V_{gf} + 2v_{th} \right) - \overline{\phi_s} \right] \Delta \phi$$

(3a)

where

where

$$dV_{C} = \left(1 + v_{th} \frac{2V_{gf} - 2\phi_{s} + C_{R}}{\left(V_{gf} - \phi_{s} + C_{R}\right)\left(V_{gf} - \phi_{s}\right)}\right) d\phi_{s}$$

To simplify it, we take the second-order Taylor expansions of y at  $\overline{\phi}$ :

$$y \approx \frac{L}{2} \left( 1 + \frac{\Delta \phi}{4H} \right) + \frac{L}{\Delta \phi} \left( \phi_s - \overline{\phi_s} \right) + \frac{L}{\Delta \phi H} \frac{\left( \phi_s - \phi_s \right)^2}{2}$$

(3b)

$$= \frac{L}{2} \left( 1 + \frac{\Delta \phi}{4H} \right) + \frac{L}{\Delta \phi} \left( u - \frac{u^2}{2H} \right)$$

where

$$H = \left[ \left( V_{gf} + 2v_{th} \right) - \overline{\phi_s} \right]$$

and

$$u = \phi_s - \overline{\phi_s} .$$

Total shored charge of each terminal node is easily obtained by taking integral of the distributed charge densities over the active gate region:

$$Q_G = 2\pi R \int_0^L Q_G(y) dy$$

<sup>(4)</sup>

$$Q_{SC} = 2\pi R \int_{0}^{L} Q_{SC}(y) dy$$

<sup>(5)</sup>

and  $Q_G = Q_{SC}$  from the charge neutrality.

Combining (3) and (4), we obtain the expression for the total gate charge in equilibrium:

$$Q_{G} = 2\pi R \int_{0}^{\mu} Q_{G}(y) dy$$

$$= 2\pi R C_{ox} L \left[ \left( V_{gf} - \overline{\phi_{s}} \right) + \frac{\Delta \phi^{2}}{12H} \right]$$

(6)

To obtain the source and drain terminal charges, the total inversion charge needs to be partitioned into source and drain portions. The Ward-Dutton method [10] is used in the proposed model:

$$Q_{D} = 2\pi R \int_{0}^{L} \frac{y}{L} Q_{i}(y) dy$$

$$= \pi R C_{ox} \cdot \left[ -\frac{L}{H^{2}} \frac{\Delta \phi^{3}}{80} - \frac{-y_{m} \Delta \phi^{2} + \Delta \phi \cdot L \left( V_{gf} - \overline{\phi_{s}} \right)}{6H} \right] \quad (7)$$

$$Q_{s} = 2\pi R \int_{0}^{L} \left( 1 + \frac{V_{gf} - \overline{\phi_{s}}}{2H} \right) + 2y_{m} \left( V_{gf} - \overline{\phi_{s}} \right) \right]$$

$$Q_{s} = 2\pi R \int_{0}^{L} \left( 1 - \frac{y}{L} \right) Q_{i}(y) dy \quad (8)$$

$$= Q_{c} - Q_{0}$$

where

$$y_m = \frac{L}{2} \left( 1 + \frac{\Delta \phi}{4H} \right). \tag{8a}$$

From (6)-(8), all terminal-node charges can be analytically calculated based on the surface-potential solution at the source and drain ends. In [9], the surfacepotential solution valid for all operation regions is shown. Therefore, the charge expressions (6), (7) and (8) are valid in all operation regimes involving linear, saturation, subthreshold, and strong inversion.

In short-channel devices, non-ideal effects such as mobility degradation, velocity saturation, velocity overshoot (VO), series resistance, channel-length modulation (CLM), and drain-induced barrier lowering (DIBL) are important and must be considered. The current expression for short-channel GAA SiNWs is obtained by including all the above non-ideal effects:

$$I_{ds} = \mu_{eff} \frac{2\pi RC_{ox}}{L} \Big[ \Big( V_{gf} + 2v_{th} \Big) V_{ds,eff} - V_{ds,eff} \cdot \overline{\phi_s} \Big]$$

(9)

where

$$\mu_{eff} = \frac{\mu_{eff\,0}}{1 + R_{sd} \frac{2\pi R}{L} \mu_{eff\,0} C_{ox} \left[ \left( V_{gf} + 2v_{th} \right) - \overline{\phi_s} \right]} \tag{10a}$$

$$\mu_{eff\,0} = \frac{\mu_s}{\left(1 + \left(\frac{\delta_L V_{ds}}{E_{satn}L}\right)^2\right)^{1/2}}$$

$$V_{ds,eff} = V_{d,eff} - V_{s,eff} \tag{11}$$

(10b)

$$V_{d,eff} = \mathcal{G}\left(V_d, V_{d,sat}, \delta_s\right) \tag{12a}$$

$$V_{s,eff} = \mathcal{G}(V_s, V_{s,sat}, \delta_s).$$

(12b)

$E_{satn}$  is the effective saturation electrical field after including the CLM/VO,  $\mu_s$  is vertical-field-dependent mobility,  $R_{sd}$  is the series resistance,  $V_{d,sat}$  and  $V_{s,sat}$  are the saturation voltages for source and drain, respectively,  $\delta_L$  is a fitting parameter,  $\delta_s$  is a smoothing parameter, and  $\mathcal{G}(\cdot)$  is the smoothing function.

The drain current is given by:

$$I_{ds} \approx \frac{\mu_s 2\pi R C_{ox} \left[ \left( V_{gf} + 2v_{th} \right) - \overline{\phi_s} \right] \Delta \phi}{L + \frac{\delta_L \Delta \phi}{E_{sam}} + R_{sd} \mu_s 2\pi R C_{ox} \left[ \left( V_{gf} + 2v_{th} \right) - \overline{\phi_s} \right]}.$$

(13)

Combining (3a) and (13), the *y* expression becomes

$$y \approx \frac{L}{2} \left( 1 + \frac{\Delta \phi}{4H^*} \right) + \frac{L}{\Delta \phi} \left( u - \frac{u^2}{2H^*} \right)$$

(14)

where

$$H^* = \frac{\left[\left(V_{gf} + 2v_{ih}\right) - \overline{\phi_s}\right]}{1 + \frac{\delta_L \Delta \phi}{LE_{sam}} + \frac{R_{sd} \mu_s 2\pi R C_{ox} \left[\left(V_{gf} + 2v_{ih}\right) - \overline{\phi_s}\right]}{L}}.$$

(14a)

The total terminal charges are:

$$Q_{G} = 2\pi R C_{ox} L \left[ \left( V_{gf} - \overline{\phi_{s}} \right) + \frac{\Delta \phi^{2}}{12H^{*}} \right]$$

(15)

$$Q_{D} = \pi R C_{ox} \begin{bmatrix} -\frac{L}{H^{*2}} \frac{\Delta \phi^{3}}{80} - \frac{-y_{m} \Delta \phi^{2} + \Delta \phi \cdot L \left( V_{gf} - \overline{\phi_{s}} \right)}{6H^{*}} \\ -\frac{\Delta \phi L}{6} \left( 1 + \frac{\left( V_{gf} - \overline{\phi_{s}} \right)}{2H^{*}} \right) + 2y_{m} \left( V_{gf} - \overline{\phi_{s}} \right) \end{bmatrix}$$

(16)

$$Q_{s} = Q_{G} - Q_{D} \cdot$$

(17)

$$s = Q_G - Q_D$$

The nonreciprocal capacitances are obtained as [11]:

$$C_{ij} = \delta_{ij} \frac{\partial Q_i}{\partial V_j} \quad \delta_{ij} = \begin{cases} 1, i = j \\ -1, i \neq j \end{cases}$$

(18)

#### 3 **RESULTS AND DISCUSSION**

To validate our model for long-channel devices, Medici numerical simulations of an undoped cylindrical GAA MOSFET are performed, with channel length  $L = 10 \ \mu m$ , R = 10 nm,  $T_{ox}$  = 2 nm, and a constant mobility  $\mu$  = 300  $cm^2/V-s$ .

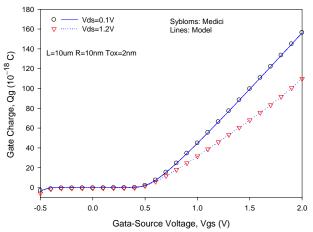

Fig. 1 shows the comparison of total gate terminal charge between Medici and the model in linear and saturation regimes for the long-channel device. The relative error is below 0.1% in strong-inversion regime. Similar behavior to bulk MOSFETs is observed [6], the terminal gate charge follows a logarithm increase in the subthrehold regime and linear increase in the strong-inversion regime.

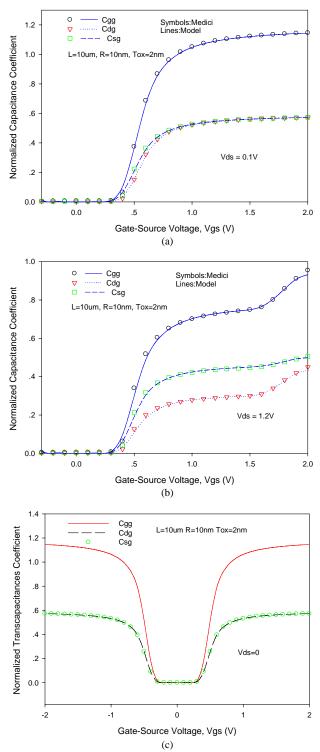

Fig. 2 shows the gate-related transcapacitances  $C_{gg}$ ,  $C_{gs}$ and  $C_{gd}$  versus  $V_{gs}$  from the model in linear and saturation regimes compared with Medici result. Excellent agreement can be observed. Similar to bulk MOSFETs,  $C_{gs}$  and  $C_{gd}$ approach different values when  $V_{ds} \neq 0$ .  $C_{gs}$ ,  $C_{gd}$ , and  $C_{gg}$ versus  $V_{gs}$  for  $V_{ds} = 0$  are shown in Fig. 2(c). When  $V_{ds} = 0$ , in all operation regimes,  $C_{gs}$  is exactly equal to  $C_{gd}$ . In undoped body devices due to lack of depletion charge, the  $C_{gg}$  is symmetric about the axis  $V_{gs} = V_{FB}$ .

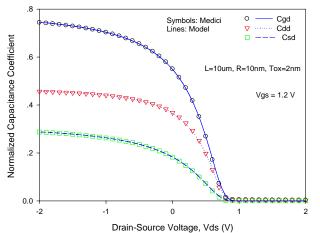

Fig. 3 shows the comparison of nonreciprocal drainrelated transpacitances between Medici and model. Again, excellent agreement is shown with smooth transition across all regimes. It is observed at high  $V_{ds}$ , the three transcapacitances approach zero, due to the surface potential being saturated in the high  $V_{ds}$  region.

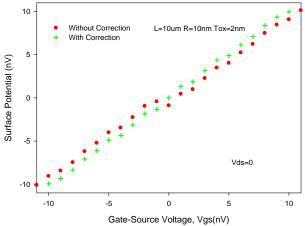

It is well known that exactly at  $V_{gs} = V_{FB}$ , there is a singularity in the one-carrier surface potential solution due to ignoring holes [12]. This singularity will result in  $C_{gg}$  discontinuity at  $V_{gs} = V_{FB}$  which may be detrimental in transient analyses. In the proposed model,  $\phi_s$  is approximated by  $\phi_s - \phi_{s_{a}fb}$  where  $\phi_{s_{a}fb}$  is the surface potential at flat band. Fig. 4 shows the surface potential versus  $V_{gs}$  with and without the correction. It shows that with the correction, the singularity problem is solved.

# 4 CONCLUSION

In conclusion, a simple, accurate charge model is developed for undoped cylindrical gate-all-around (GAA) silicon-nanowire MOSFETs. The model is firstly derived for long-channel devices, followed by extending to shortchannel devices by including non-ideal effects. The singularity problem at flat band is also solved by a simple correction.

Fig. 1. Terminal gate charge versus gate-source voltage for different  $V_{ds}$  with  $L = 10 \ \mu\text{m}$ ,  $R = 10 \ \text{nm}$ , and  $T_{ox} = 2 \ \text{nm}$ .

Fig 2. Normalized gate transcapacitance coefficients in (a) linear, (b) saturation, and (c)  $V_{ds} = 0$ . The normalization constant is 1/(LR).

Fig. 3. Normalized drain-related transcapacitance coefficients with  $V_{gs} = 1.2$  V. The normalization constant is 1/(LR).

Fig. 4. Surface potential with/without flat-band correction.

*Acknowledgment:* This work was supported in part by Nanyang Technological University under Grant RGM30/03 and in part by Semiconductor Research Corporation under Grant 2004-VJ-1166G.

## REFERENCES

- J. P. Colinge, M. H. Gao, A. Romano, H. Maes, and C. Claeys, "Silicon-on-insulator gate-all-around device," in *IEDM Tech. Dig.*, 1990, pp. 595–599.

- [2] N. Singh, F. Y. Lim, et al., "Ultra-narrow silicon nanowire gate-all-around CMOS devices: impact of diameter, channel-orientation and low temperature on device performance," in *IEDM Tech. Dig.*, 2006, pp. 547–550.

- [3] J. He, X. Zhang, G. Zhang, M. Chan, and Y. Y. Wang, "A carrier-based analytic DCIV model for long channel undoped cylindrical surrounding-gate MOSFETs," *Solid-State Electron.*, vol. 50, no. 3, pp. 416–421, Mar. 2006.

- [4] B. Iniguez, et al., "Explicit continuous model for longchannel undoped surrounding gate MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no.8, pp. 1868–1873, 2005.

- [5] T. K. Chiang, "New current-voltage model for surrounding-gate metal-oxide-semiconductor field effect transistors," *Jpn. J. Appl. Phys.*, vol. 44, pp. 6446-6451, Sept. 2005.

- [6] J. He, B. Wei, Y. D. Tao, S. Q. Yang and X. Tang, "Analytic carrier-based charge and capacitance model for long-channel undoped surrounding-gate MOSFETs," *IEEE Trans. Electron Devices*, vol. 54, no. 6, Jun. 2007.

- [7] O. Moldovan, B. Iniguez, D. Jimenez, and J. Roig, "Analytical charge and capacitance model of undoped cylindrical surrouding-gate MOSFETs," *IEEE Trans. Electron Devices*, vol. 54, no. 1, Jan. 2007.

- [8] H. X. Lu, B. Yu, and Y. Taur, "A unified charge model for symmetric double-gate and surrounding-gate MOSFETs," *Solid-State Electron.*, vol. 52, no. 1, pp. 67-72, Jan. 2008

- [9] S. H. Lin, X. Zhou, G. H. See1, Z. M. Zhu, G. H. Lim, C. Q. Wei, G. J. Zhu, Z. H., Yao, X. F. Wang, M. Yee, L. N. Zhao, Z. F. Hou, L. K. Ang, T. S. Lee, W. Chandra, "A Rigorous Surface-Potential-Based I-V Model for Undoped Cylindrical Nanowire MOSFETs," in *Proc. of the 7th International Conference on Nanotechnology (IEEE-Nano2007)*, Hong Kong, Aug. 2007, pp. 889-892.

- [10] S. Y. Oh, D. E. Ward, and R. W. Dutton, "Transient analysis of MOS transistor," *IEEE J. Solid-State Circuits*, vol. SSC-15, no. 4, pp. 636-643, Aug. 1980

- [11] D. E. Ward and R. W. Dutton, "A charge-oriented model for MOS transistor capacitances," *IEEE J. Solid-State Circuits*, vol. SSC-13, no. 5, pp. 703-708, Oct. 1978.

- [12] X. Zhou, Z. M. Zhu, S. C. Rustagi, G. H. See, G. J. Zhu, S. H. Lin, C. Q. Wei, and G. H. Lim, "Rigorous surface-potential solution for undoped symmetric double-gate MOSFETs considering both electrons and holes at quasi nonequilibrium," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 616-623, Feb. 2008.