Received November 2, 2019, accepted November 17, 2019, date of publication December 27, 2019, date of current version January 10, 2020.

Digital Object Identifier 10.1109/ACCESS.2019.2962706

# A Single DC Source Nine-Level Switched-Capacitor Boost Inverter Topology With Reduced Switch Count

MARIF DAULA SIDDIQUE<sup>®1,2</sup>, (Student Member, IEEE),

SAAD MEKHILEF<sup>®1,3</sup>, (Senior Member, IEEE),

NORAISYAH MOHAMED SHAH<sup>®1</sup>, (Member, IEEE),

N. SANDEEP<sup>®4</sup>, (Student Member, IEEE),

JAGABAR SATHIK MOHAMED ALI<sup>®5</sup>, (Senior Member, IEEE),

ATIF IQBAL<sup>®2</sup>, (Senior Member, IEEE),

MAHROUS AHMED<sup>®6,7</sup>, (Senior Member, IEEE),

SHERIF S. M. GHONEIM<sup>®6,8</sup>, (Senior Member, IEEE),

MOSLEH M. AL-HARTHI<sup>®6</sup>, BASEM ALAMRI<sup>®6</sup>, FARHAN A. SALEM<sup>®6</sup>,

AND MOHAMED ORABI<sup>®7</sup>, (Senior Member, IEEE)

<sup>1</sup>Power Electronics and Renewable Energy Research Laboratory, Department of Electrical Engineering, University of Malaya, Kuala Lumpur 50603, Malaysia

<sup>2</sup>Department of Electrical Engineering, Qatar University, Doha, Qatar

Corresponding author: Saad Mekhilef (saad@um.edu.my)

This work was supported in part by the Scientific Research Deanship, Taif University, Saudi Arabia, under Grant 1-439 - 6072.

**ABSTRACT** This paper presents a new boost inverter topology with nine level output voltage waveform using a single dc source and two switched capacitors. The capacitor voltages are self-balancing and thus is devoid of any sensors and auxiliary circuitry. The output voltage is twice higher than the input voltage, which eliminates the need for an input dc boost converter especially when the inverter is powered from a renewable source. The merits of the proposed topology in terms of the number of devices and cost are highlighted by comparing the recent and conventional inverter topologies. In addition to this, the total voltage stress of the proposed topology is lower and have a maximum efficiency of 98.25%. The operation and dynamic performance of the proposed topology have been simulated using PLECS software and are validated using an experimental setup considering a different dynamic operation.

**INDEX TERMS** Multilevel inverter, nine-level inverter, step-up inverter, switched capacitor, reduce switch count.

#### I. INTRODUCTION

Multilevel inverters (MLIs) have emerged and evolved as a perfect solution for the medium and high voltage/power applications where high-quality dc-ac power conversion is needed. The classical topologies for the MLIs are neutral point clamped (NPC), flying capacitor (FC) and cascade

The associate editor coordinating the review of this manuscript and approving it for publication was Firuz Zare.

H-bridge (CHB). These topologies are widely researched and are well established in industrial applications. However, for a higher number of output levels, the increased in the number components required for NPC and FC becomes quixotic. Similarly, for CHB, the higher number of isolated dc voltage sources for a higher number of levels limits its applications [1]–[5].

One category of the MLI topologies has been based on the multiple isolated dc voltage sources. In this category,

<sup>&</sup>lt;sup>3</sup>School of Software and Electrical Engineering, Faculty of Science, Engineering, and Technology, Swinburne University of Technology, Melbourne, VIC 3122, Australia

<sup>&</sup>lt;sup>4</sup>Department of Electrical and Electronics Engineering, National Institute of Technology Karnataka, Surathkal 575025, India

<sup>&</sup>lt;sup>5</sup>Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai 603203, India

<sup>&</sup>lt;sup>6</sup>Electrical Engineering Department, College of Engineering, Taif University, Taif 21974, Saudi Arabia

<sup>&</sup>lt;sup>7</sup>APEARC, Faculty of Engineering, Aswan University, Aswan 81542, Egypt

<sup>&</sup>lt;sup>8</sup>Electrical Department, Faculty of Industrial Education, Suez Canal University, Suez 43527, Egypt

the topologies have been classified as symmetrical and asymmetrical configured topologies. In symmetrically configured topologies, the dc voltage sources have the same magnitude. In asymmetrically configured topologies, the dc voltage sources have different magnitude resulting in a higher number of levels with a lower number of switches as well as dc voltage sources. In both types of topologies, the need for a higher number of isolated dc voltage sources limits their applications [6]–[9].

In order to reduce the number of dc voltage sources, the use of topologies with switched capacitor (SC) units have been recommended. The SC unit has been used with different arrangements resulting in different output voltage levels. One topology based on capacitors has been proposed in [10] and named as packed E-cell (PEC) topology. With two dc voltage sources and two capacitors, a nine-level output voltage waveform can be achieved, however, the topology lacks the boosting of the input voltage. Similar to [10], nine-level MLI topologies with two dc voltage sources and two capacitors have been proposed in [11], [12]. The authors in [13] proposed two new topologies with two dc voltage source along with two capacitors. Both topologies generate nine levels of the voltage across the load. However, both topologies use H-bridge for the polarity change, which requires switches with a higher voltage rating. The topologies also lack boosting ability. A K-type topology has been proposed in [14] in which two dc voltage sources along with two capacitors have been used for 13 levels at the output. However, the rating of both capacitors is different. In addition, both capacitors need to discharge for the last three levels, which results in a nonsteady response in the capacitor voltage and unequal voltage steps across the load.

Most of the SC-based topologies use single dc voltage source and the SC units are used to create different dc-link voltages for the multilevel output across the load. Some of the topologies with SC units have a distinctive feature of boosting the output voltage, i.e., the peak of the output voltage is higher than the input supply. The SC-based MLI topology based on H-bridge has been proposed in [15], and [16] in which SC is connected through H-bridges for charging and discharging purposes. Several H-bridge with SC can be connected for a higher number of levels, which increases the number of switches.

A new seven-level boost inverter topology has been proposed in [17] with triple voltage gain. A hybrid switched-capacitor based nine-level MLI topology has been proposed in [18], however, the boosting feature is absent from the topology of [18]. Few more seven-level boost inverter topologies have been proposed in [19]–[25], however, the higher number of components have always been the major concern about these topologies. Furthermore, the topologies proposed in [21], [22], [24], [25] have a lower value of boosting factor.

Based on the twice boosting gain, several nine-level MLI topologies have input. In [26], a single-stage nine-level topology has been proposed. The topology uses 12 switches for nine levels across the load with twice of voltage gain.

An improvement in terms of switches from [26] has been made in [27], which uses 11 switches to achieve nine levels. In [28], a new nine-level boost topology based on SC has been proposed to which the capacitors are charged in the first two levels and then discharged to give the boost feature in the next two states of the output voltage. Furthermore, for the topologies [29]–[38] the switch count for nine levels has been on the higher side. Considering these facts, this paper attempts to synthesize a nine-level voltage using the SC technique to reduce the component count. The main features of the proposed MLI are:

- i. A single dc source is used.

- ii. Self-voltage balancing is achieved across the capacitors.

- iii. The output voltage is twice the input voltage.

- iv. Low voltage stress across the switches.

- v. The capacitor voltages are independent of the load power factor and modulation index.

The circuit topology and its working will be discussed in Section II. A detailed comparison has been carried out in terms of quantitative and cost analysis and has been resented in Section III. Sections IV gives a detailed explanation of the proposed topology with several simulations and experimental results and the conclusion of the paper has been presented in Section V.

# **II. PROPOSED TOPOLOGY**

## A. CONFIGURATION OF THE PROPOSED TOPOLOGY

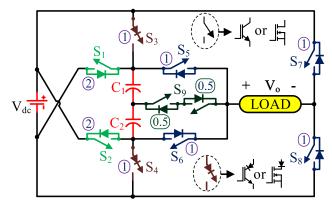

The configuration of the proposed single-phase SCMLI topology is shown in Fig. 1 along with the maximum voltage stress across each switch as a factor of input dc voltage source, i.e.  $V_{dc}$ . The assembly of the proposed topology consists of ten switches. The switches can be either IGBT or MOSFET based on the frequency of operation, voltage, and power rating of the converter. Two capacitors  $C_1$  and  $C_2$  are used to split the dc supply voltage into halves. By systematic and sequential turning ON/OFF of the switches, the capacitor voltages are maintained at half of the supply voltage, i.e.,  $V_{dc}/2$ . The proposed topology generates nine levels across the load with a twice voltage boosting factor. The switching

FIGURE 1. Proposed nine level inverter topology.

TABLE 1. Switching states of the proposed topology.

| $S_1$ | $S_2$ | $S_3$ | S <sub>4</sub> | $S_5$ | S <sub>6</sub> | $S_7$ | $S_8$ | S <sub>9</sub> | Vo               | $V_{C1}$ | $V_{C2}$ |

|-------|-------|-------|----------------|-------|----------------|-------|-------|----------------|------------------|----------|----------|

| 0     | 0     | 1     | 1              | 0     | 1              | 0     | 1     | 0              | 0                | С        | С        |

| 0     | 0     | 1     | 1              | 0     | 0              | 0     | 1     | 1              | $V_{dc}/2$       | С        | C        |

| 0     | 0     | 1     | 1              | 1     | 0              | 0     | 1     | 0              | $V_{dc}$         | C        | C        |

| 0     | 1     | 0     | 0              | 0     | 0              | 0     | 1     | 1              | $3V_{dc}/2$      | _        | D        |

| 0     | 1     | 0     | 0              | 1     | 0              | 0     | 1     | 0              | $2V_{dc}$        | D        | D        |

| 0     | 0     | 1     | 1              | 1     | 0              | 1     | 0     | 0              | 0                | C        | C        |

| 0     | 0     | 1     | 1              | 0     | 0              | 1     | 0     | 1              | $-V_{dc}/2$      | C        | C        |

| 0     | 0     | 1     | 1              | 0     | 1              | 1     | 0     | 0              | -V <sub>dc</sub> | С        | C        |

| 1     | 0     | 0     | 0              | 0     | 0              | 1     | 0     | 1              | $-3V_{dc}/2$     | D        | _        |

| 1     | 0     | 0     | 0              | 0     | 1              | 1     | 0     | 0              | $-2V_{dc}$       | D        | D        |

Notations: 0 = OFF state of the switch, 1 = ON state of the switch, -= no change in capacitor voltage, C = charging of capacitor, D = discharging of capacitor

table for the proposed topology along with the variation of capacitor voltages  $V_{C1}$  and  $V_{C2}$  are given in Table 1.

#### **B. DESCRIPTION OF VOLTAGE LEVELS**

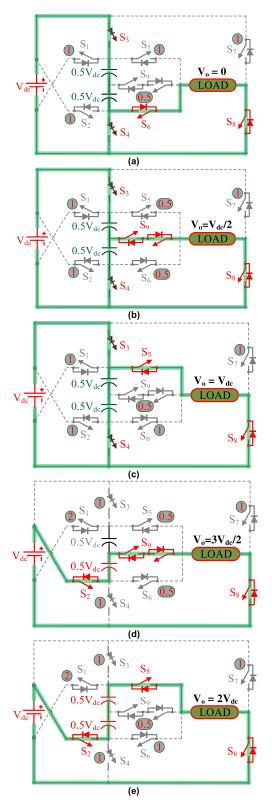

With the proposed topology, nine levels are generated across the load. In this section, all five levels in the positive half cycle are described with the blocking voltages of all the nonconducting switches and shown in Fig. 2 (a)-(e).

- (i) State i (Zero voltage state): In this voltage state, as shown in Fig. 2 (a), the capacitors  $C_1$  and  $C_2$  are made to charge to their peak voltage by connecting them directly across the dc voltage source. This is achieved by turning ON the switches  $S_3$  and  $S_4$ . By turning ON the switches  $S_5$  and  $S_7$ , the load terminals are shorted and a path is provided for the flow of current in case of an inductive load.

- (ii) State ii  $(+V_{dc}/2)$ : As shown in Fig. 2 (b), the first voltage state equal to  $V_{dc}/2$  appears across the load by turning ON the switches  $S_8$  and  $S_9$  and turning OFF switches  $S_5$  and  $S_7$ . In this state, the capacitor voltage  $V_{C1}$  and  $V_{C2}$  are maintained at  $V_{dc}/2$ . The capacitor voltage  $V_{C1}$ , equal to  $V_{dc}/2$ , is subtracted from dc voltage source  $V_{dc}$ .

- (iii) State iii ( $+V_{dc}$ ): In this voltage state, the full source voltage appears across the load by turning ON switch  $S_5$  and turning OFF switch  $S_9$  as shown in Fig. 2 (c). Both capacitor voltages are further maintained at  $V_{dc}/2$ . The energy is stored in both capacitors until this voltage state.

- (iv) State iv  $(+3V_{dc}/2)$ : In this voltage state, the switches  $S_3$  and  $S_4$  are turned OFF and energy stored in capacitor  $C_2$  is used to create the third voltage state. The voltage  $V_{C2}$  is

- (v) added to the dc voltage source  $V_{dc}$  by turning ON switch  $S_2$ . The state of capacitor  $C_1$  remains unchanged and the voltage is held at  $V_{dc}/2$ . This voltage state is shown in Fig. 2 (d).

- (vi) State v ( $+2V_{dc}$ ): The energies stored in both capacitors are released in this voltage state and the voltages of both capacitors are added to the dc voltage source. This boosting of dc voltage source results in  $2V_{dc}$  across the load as shown in Fig. 2 (e).

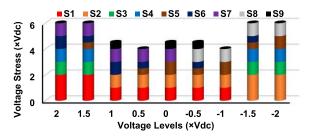

Fig. 3 summarizes the voltage stress across all the switches for each level at the output. The switches  $S_1$  and  $S_2$  are

**FIGURE 2.** Positive voltage states of the proposed nine level topology with (a)  $V_0=0$ , (b)  $V_0=V_{dc}/2$ , (c)  $V_0=V_{dc}$ , (d)  $V_0=3V_{dc}/2$ , and (e)  $V_0=2V_{dc}$ .

cross-connected between the dc voltage source and capacitors to obtain the boost feature. These switches need to block the  $2V_{dc}$  due to the cross-connection. The switches  $S_3$  and

FIGURE 3. Voltage stress across all switches during all voltage levels.

$S_4$  are connected in series with diodes in order to prevent the conduction of switches  $S_3$  and  $S_4$  in the boost mode of operation. The switches  $S_3$  to  $S_8$  are needed to block the supply voltage  $V_{dc}$  and the bidirectional switch  $S_9$  needs to block half of the supply voltage.

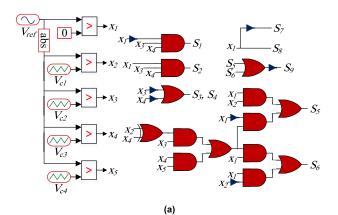

#### C. MODULATION TECHNIQUE

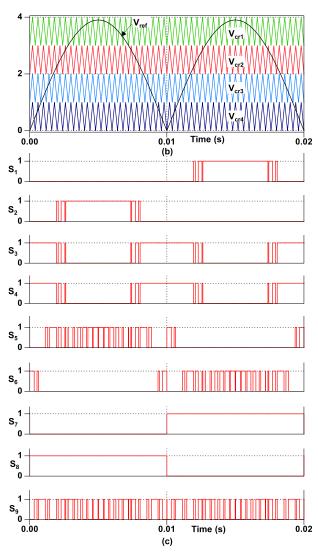

For the proposed topology, phase disposition pulse width modulation (PD-PWM) technique has been used. In PD-PWM, four carrier signals with the same magnitude and high frequency have been compared with the sinusoidal reference signal V<sub>ref</sub> having a frequency of output voltage. The comparison results in the gate pulses for the switched according to Table 1. The logic for the proposed nine-level topology has been derived using Table 1 and has been implemented using the logic gates as shown in Fig. 4 (a). Based on the logic as shown in Fig. 4 (a), the different signals are shown in Fig. 4 (b) and (c). Fig 4 (b) depicts the four carrier signals  $V_{cr1}$  to  $V_{cr4}$ , each having a magnitude of  $V_{cr}$  along with the reference voltage V<sub>ref</sub>. The gate signals produced with the comparison and the switching logic has been depicted in Fig. 4 (c). The modulation index for the PWM shown in Fig. 4 (b) can be obtained as

$$MI = \frac{V_{ref}}{4V_{cr}} \tag{1}$$

In order to show a better performance of the PD-PWM, different modulation techniques have been applied to the proposed nine-level topology. Apart from PD-PWM, phase opposition disposition PWM (POD-PWM), alternate phase opposition disposition PWM (APOD-PWM) and nearest level control PWM (NLC-PWM) techniques have been used for the comparison. With a carrier frequency of 2.5kHz and input voltage source,  $V_{\rm dc}=100 {\rm V}$ , Table 2 gives the comparison of different modulation techniques with the different factors. The PD-PWM gives the lower THD and higher output voltage compare to all other modulation techniques.

#### D. CAPACITOR VOLTAGE BALANCING

The self-voltage balancing of the capacitors  $C_1$  and  $C_2$  is one of the essential features of the proposed topology. Both voltages must be balanced with the voltage equal to half of the input voltage. From Table 1, the capacitor  $C_1$  and  $C_2$  have the same behavior in terms of charging and discharging pattern over a fundamental cycle. The capacitors  $C_1$  and

FIGURE 4. PD-PWM technique with (a) logic for the gate pulse generation, (b) carrier and reference signal and (c) generated gate pulses for all switches.

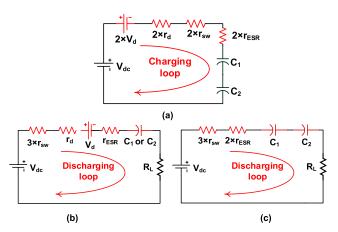

$C_2$  get charged during the voltage levels of zero,  $\pm V_{dc}/2$ , and  $\pm V_{dc}$ . The equivalent circuit during the charging od the capacitors is depicted in Fig. 5 (a). In the charing loop, the parasitic resistance of diodes, switches and equivalent series resistance (ESR) of capacitors are present. The lower

| TABLE 2. C | omparison of | different | PWM | techniques. |

|------------|--------------|-----------|-----|-------------|

|------------|--------------|-----------|-----|-------------|

| Load           | Modulation |           |                 | V               | T         |                 |                 |                  |           |

|----------------|------------|-----------|-----------------|-----------------|-----------|-----------------|-----------------|------------------|-----------|

| Load           | Techniques | $V_{THD}$ | 3 <sup>rd</sup> | 5 <sup>th</sup> | $I_{THD}$ | 3 <sup>rd</sup> | 5 <sup>th</sup> | V <sub>rms</sub> | $I_{rms}$ |

| Hu             | PD-PWM     | 9.57      | 0.98            | 0.37            | 0.72      | 0.49            | 0.12            | 139.7            | 5.5       |

| =50n           | POD-PWM    | 9.89      | 1.14            | 0.39            | 0.75      | 0.54            | 0.13            | 139.1            | 5.37      |

| R=20Ω , L=50mH | APOD-PWM   | 9.71      | 1.06            | 0.37            | 0.74      | 0.52            | 0.12            | 139.5            | 5.43      |

| R=2            | NLC-PWM    | 9.82      | 1.36            | 0.67            | 0.97      | 0.57            | 0.22            | 139.3            | 5.35      |

FIGURE 5. Equivalent circuit for the proposed nine level inverter for (a) charging of capacitors, (b) discharging of capacitor during voltage level of  $\pm 3 V_{dc}/2$  and (c) discharging of capacitors during the voltage voltage of  $\pm 2 V_{dc}$  [V<sub>d</sub> = Forward voltage drop of diode, r<sub>d</sub> = forward resistance of diode, r<sub>sw</sub> = forward resistance of switch and r<sub>ESR</sub> = ESR of capacitor].

value of these elements results in a meager value of time constant RC in the charing loop. By neglecting the voltage drops of the switches and diodes, the capacitor voltages will be half of the input voltage, i.e.,

$$V_{C1} = V_{C2} = \frac{V_{dc}}{2} \tag{2}$$

The capacitors get discharged by connecting them in series with the input source during the boost mode of operation, i.e., during the voltage levels of  $\pm 3 V_{dc}/2$ , and  $\pm 2 V_{dc}$  as shown in Fig. 5 (b) and (c) respectively. the fully charged capacitors start to discharge and their voltage drops from  $V_{dc}/2$ . However, during the discharging of capacitors as shown in Fig. 5 (b) and (c), the time constant RC is very much high compared to the charging of the capacitors. This results in the slow discharging of the capacitors. When the next charging state comes, the voltage across the capacitors again rises to  $V_{dc}/2$ . Therefore, over a complete fundamental cycle, both capacitors charge and discharge for several duration, and each capacitor voltage can be maintained at the  $V_{dc}/2$  with some ripple voltage.

## **III. COMPARATIVE STUDY**

To show the merits of the proposed nine-level topology, a comparison has been carried out in terms of different component counts, total voltage stress, and gain of different topologies. Table 3 gives a quantitative comparison between the proposed topology and recently introduced SC-based topologies. The proposed topology requires ten switches for the nine-level generation, which is lower than the topologies proposed in [26], [27], [30], [33], and [35]. Furthermore, the proposed topology uses only two capacitors for the gain of two. However, the topologies proposed in [22] and [24] gives a voltage gain of 1.5 by using three capacitors. Another noticeable benefit of the proposed topology has been in terms of reduced voltage stress. The TSV<sub>pu</sub> for the proposed topology has a lower value compared to topologies of [28], [30], [33], [34], and [36].

Apart from the quantitative analysis, a cost comparison of the proposed topology is given in Table 4. The rating of components has been selected based on the structure of the topologies. From Table 4, the proposed topology gives the minimum cost among all the topologies under consideration. The lower cost, along with the lower number of components gives an additional edge of the proposed topology for low and medium voltage applications as compared to other nine-level topologies with a single dc input voltage source. The reduced switch count implies reduced conduction losses. In theory, the maximum switch blocking voltage dictates the switching losses in addition to switching frequency. Furthermore, two of the total switches operate at the fundamental switching frequency. These factors supplement the fact of reduced switching losses. All these factors help in concluding that the proposed MLI has improved efficiency in comparison to similar counterpart topologies

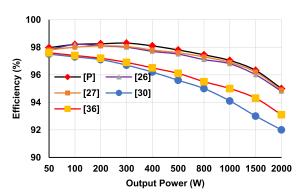

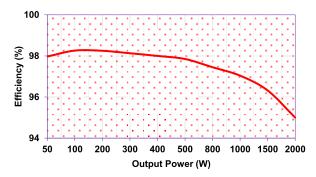

For a power electronic converter, efficiency has been one of the leading performance parameters. The efficiency of a converter depends on the losses of the converter. With power electronic switches, conduction and switching losses contribute to the overall losses in addition to the ripple losses of the switched capacitor unit. The conduction losses occur due to the power loss of the equivalent resistance of switch or diode. PLECS software has been used for the accurate estimation of efficiency through thermal modeling. Fig. 6 illustrates the curves of efficiencies with output power for different similar topologies. As can be seen from these curves that the proposed topology along with topologies of [26] and [27] has almost similar curves. However, the proposed topology has a slightly higher value of efficiency compared to all other topologies. The topologies proposed in [30] and [36] have lower efficiencies due to their higher number of components and the number of capacitors.

#### **IV. RESULTS AND DISCUSSION**

In this section, different simulation and experimental results have been illustrated and discussed in detail. The PD-PWM technique as shown in Fig. 4 has been used to demonstrate the performance of the proposed nine-level topology. For the simulation, two capacitors with  $2200\mu F$  have been used. The rating of the capacitor has been chosen based on the following

TABLE 3. Quantitative comparison of the proposed topology with other topologies.

| Topology             | N <sub>L</sub> | Nsw | N <sub>d</sub> | N <sub>dc</sub> | Ncap | Variety of capacitor | TSV <sub>pu</sub> | Gain | Voltage Boosting | Negative Level |

|----------------------|----------------|-----|----------------|-----------------|------|----------------------|-------------------|------|------------------|----------------|

| [10], [11], and [12] | 9              | 8   | 0              | 2               | 2    | 1                    | 4.5               | 1    | No               | Inherent       |

| [15], and [16]       | 7              | 16  | 0              | 1               | 2    | 1                    | 5.3               | 3    | Yes              | Inherent       |

| [17]                 | 7              | 12  | 0              | 1               | 2    | 1                    | 5.3               | 3    | Yes              | Inherent       |

| [22]                 | 7              | 10  | 0              | 1               | 3    | 2                    | 5.3               | 1.5  | Yes              | Inherent       |

| [24]                 | 7              | 9   | 1              | 1               | 3    | 2                    | 5.3               | 1.5  | Yes              | Inherent       |

| [26]                 | 9              | 12  | 0              | 1               | 2    | 1                    | 5.5               | 2    | Yes              | Inherent       |

| [27]                 | 9              | 11  | 0              | 1               | 2    | 1                    | 5                 | 2    | Yes              | Inherent       |

| [28]                 | 9              | 10  | 1              | 1               | 2    | 1                    | 7.5               | 2    | Yes              | Inherent       |

| [30]                 | 9              | 17  | 0              | 1               | 4    | 1                    | 7.25              | 1    | No               | Inherent       |

| [33]                 | 9              | 12  | 0              | 1               | 3    | 2                    | 6                 | 4    | Yes              | Inherent       |

| [34]                 | 9              | 9   | 0              | 1               | 2    | 2                    | 6.25              | 4    | Yes              | H-Bridge       |

| [35]                 | 9              | 12  | 0              | 2               | 1    | 1                    | 5                 | 1    | No               | Inherent       |

| [36]                 | 9              | 8   | 3              | 1               | 3    | 2                    | 6.5               | 4    | Yes              | Inherent       |

| [P]                  | 9              | 10  | 0              | 1               | 2    | 1                    | 5.5               | 2    | Yes              | Inherent       |

$N_L$ =number of levels,  $N_{sw}$ = number of switches,  $N_d$ =number of diodes (including antiparallel and series connected to a MOSFET),  $N_{dc}$ =number of dc voltage sources,  $N_{cap}$ = Number of capacitors,  $TSV_{pu}$ = Total standing voltage (in per unit), [P] = Proposed

TABLE 4. Cost comparison between proposed topology and recently introduced topologies with single source nine level configuration.

| C               | Part Number     | D-4:          | Unit       | Topology |       |       |         |         |         |        |      |

|-----------------|-----------------|---------------|------------|----------|-------|-------|---------|---------|---------|--------|------|

| Component       |                 | Rating        | Price (\$) | [26]     | [27]  | [28]  | [30]    | [33]    | [34]    | [36]   | [P]  |

| MOSFET*         | IRFP9140NPBF    | 100V, 23A     | 2.2        | 2        | 2     | 2     | -       | -       | -       | 2      | 2    |

|                 | IRFP240PBF      | 200V, 20A     | 2.68       | 10       | 9     | 2     | 7       | 4       | 2       | 3      | 6    |

|                 | AUIRFSL6535     | 300V, 19A     | 3.32       | -        | -     | 2     | -       | -       | -       | -      | -    |

|                 | IRFP350PBF      | 400V, 16A     | 3.48       | -        | -     | 4     | 7       | 6       | 3       | -      | 2    |

|                 | IXFH15N80       | 800V, 20A     | 13.492     | -        | _     | -     | 2       | 2       | 4       | 4      | -    |

| Diode*          | V20PWM10HM3/I   | 100V, 20A     | 1.11       | _        | -     | -     | -       | -       | 1       | 2      | -    |

|                 | 20ETF64PBF      | 200V, 20A     | 1.81       | -        | -     | 1     | -       | -       | -       | -      | -    |

| Capacitor#      | 23A252F100BB1H1 | 100V, 2500 μF | 14.23      | 2        | 2     | 2     | 4       | 1       | 1       | 2      | 2    |

|                 | 23M252F200BH1H1 | 200V, 2500 μF | 23.61      | -        | -     | -     | -       | 2       | 1       | -      | -    |

| Total Cost (\$) | )               |               |            | 56.99    | 56.98 | 60.59 | 127.024 | 120.034 | 108.718 | 97.088 | 55.9 |

\*www.digikey.com, #www.galco.com

equation:

$$C_1 = C_2 = \frac{I_{pk}}{(\Delta V_C \times f_o)} \tag{3}$$

where,  $I_{pk}$ ,  $\Delta V_C$ , and  $f_o$  are the peak load current, capacitor voltage ripple, and frequency of the output voltage, respectively [27]. The different parameters used for the validation of the proposed topology has been given in Table 5.

## A. SIMULATION RESULTS

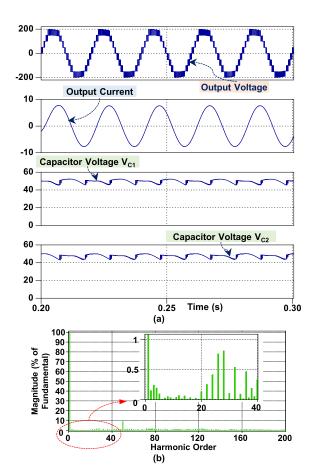

The proposed nine-level topology has been simulated using PLECS software. Fig. 7 shows the different simulated

waveforms for the proposed topology. The ac output voltage has a peak of 200V, which has been fed to a series-connected the resistive-inductive load (Z = 50mH + 20  $\Omega$ ), results in an output current of a peak value of 7.5A. The voltage across both capacitors varies around 50V with a minimum and maximum value of 45V and 51V, respectively. Furthermore, the FFT of the output voltage has also been shown in Fig. 7 (b), which has a THD of 9.41% with the elimination of all lower-order harmonics.

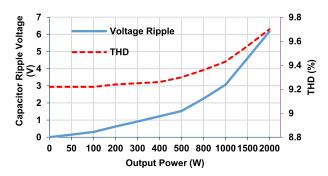

Some of the performance parameters have also been shown for the proposed topology. Fig. 8 shows the variation of capacitor ripple voltage along with THD. The capacitor ripple

FIGURE 6. Efficiency comparison of different topologies.

**TABLE 5.** Simulation and experimental parameters.

| Parameter            | Simulation                                                  | Experimental                                                |

|----------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| Input voltage source | 100V                                                        | 100V                                                        |

| Output frequency     | 50Hz                                                        | 50Hz                                                        |

| Carrier frequency    | 2.5 kHz                                                     | 2.5 kHz                                                     |

| Capacitor            | 2200 μF                                                     | 2200 μF                                                     |

| Load Parameters      | Different<br>combinations of<br>resistive-inductive<br>load | Different<br>combinations of<br>resistive-inductive<br>load |

TABLE 6. Power loss distribution of the proposed topology with  $P_0 = 800W$ .

| Power Loss of            | $P_{sw}(W)$ | $P_{c}(W)$ | $P_{loss}(W)$ |

|--------------------------|-------------|------------|---------------|

| Switch S <sub>1</sub>    | 0.0256      | 0.826      | 0.8516        |

| Switch S <sub>2</sub>    | 0.0256      | 0.826      | 0.8516        |

| Switch S <sub>3</sub>    | 0.0541      | 3.838      | 3.8921        |

| Switch S <sub>4</sub>    | 0.0612      | 3.848      | 3.9092        |

| Switch S <sub>5</sub>    | 0.0506      | 0.649      | 0.6996        |

| Switch S <sub>6</sub>    | 0.0537      | 0.652      | 0.7057        |

| Switch S <sub>7</sub>    | 0.041       | 1.018      | 1.059         |

| Switch S <sub>8</sub>    | 0.044       | 1.015      | 1.059         |

| Switch S <sub>9</sub>    | 0.0579      | 1.487      | 1.5449        |

| Total switch losses      | 0.4137      | 14.159     | 14.5727       |

| Capacitor C <sub>1</sub> |             |            | 3.15          |

| Capacitor C <sub>2</sub> |             |            | 3.17          |

voltage increases as the output power increase. The increase in capacitor ripple voltage slightly deteriorates the output voltage waveform and this change results in a slight increase in the THD. At no load, the THD has a value of 9.2% which increases to 9.7% at an output power of 2kW.

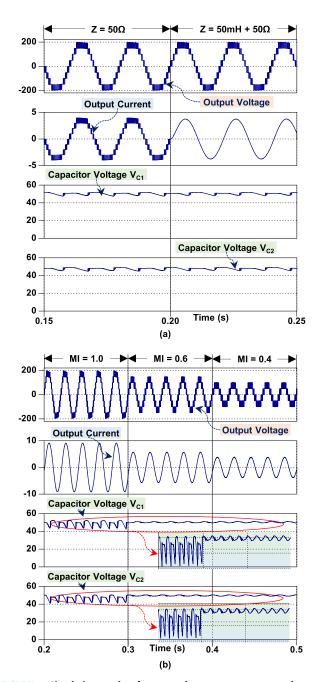

Furthermore, the performance of the proposed topology has been tested with a dynamic change of load and modulation index (MI). Fig. 9 (a) illustrates the output voltage, current and capacitor voltages with a load change of

**FIGURE 7.** Simulation results of (a) output voltage, output current and capacitor voltage with  $Z = 50 \text{mH} + 20 \Omega$  and (b) FFT of output voltage.

FIGURE 8. Variation of capacitor ripple voltage along with THD.

purely resistive load of  $Z=50~\Omega$  to a series-connected resistive-inductive load with  $Z=50 \mathrm{mH}+50~\Omega$ . With the change of load type, both capacitor voltages are balanced and it shows that the load type does not affect the balancing of capacitor voltages. In addition, a dynamic change of modulation index has been illustrated in Fig. 9 (b). The MI has been changed from 1.0 to 0.6 and from 0.6 to 0.4. With a modulation index of 0.6, the number of levels is reduced to seven and with a modulation index of 0.4, the number of levels becomes 5. However, both capacitor voltages remain balanced.

**FIGURE 9.** Simulation results of output voltage, output current and capacitor voltage with (a) change of load from Z = 50  $\Omega$  to Z = 50mH + 50  $\Omega$  and (b) change of modulation index with Z = 20mH + 20  $\Omega$ .

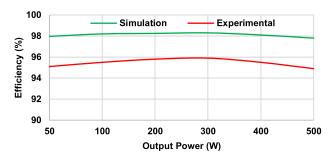

In addition, the efficiency of the proposed topology against the output power has been shown in Fig. 10. The maximum efficiency of the proposed topology has been estimated as 98.25% at the output power of 200W. At the output power of 2kW, the efficiency of the proposed topology comes out to be 95%. The proposed topology gives adequate efficiency at a higher power rating. Furthermore, the power loss distribution among different switches and capacitors for a power rating of 800W has been given in VI. The switch pair S<sub>3</sub>

FIGURE 10. Efficiency vs output power curve of the proposed topology.

and  $S_4$  have the maximum power loss as both switches are involved in the charging and discharging of capacitors. With 800W output power, the total losses of the converter become 20.9W. This results in the efficiency of the proposed topology as 97.5%.

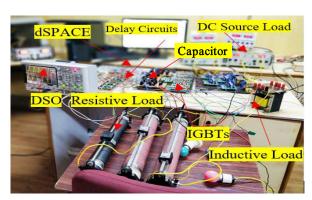

### B. EXPERIMENTAL RESULTS

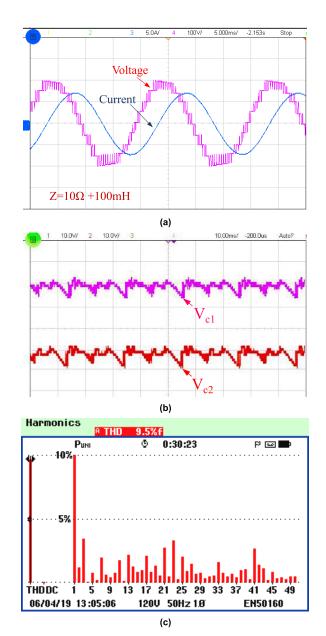

To verify the feasibility of the proposed nine-level topology, a laboratory prototype was developed to carry out the experimental work. The switching frequency of 2.5 kHz has been selected for the PD-PWM with a dead time of  $2\mu$ s provided by the delay circuit. The gate pulses have been generated using dSPACE. The experimental setup has been shown in Fig. 11. For the experimental results, the magnitude of the dc input voltage source was fixed to 100V. Fig. 12 (a) shows the output voltage and current waveform for series-connected resistive-inductive load with  $R=10\Omega$  and L=100mH. One of the main features of the proposed topology has been the twice voltage gain and this has been confirmed by the output voltage, which has a 200V peak resulting from a 100V dc input voltage. In addition, both capacitor voltages are depicted in Fig. 12 (b). Both capacitor voltages, i.e., V<sub>c1</sub> and V<sub>c2</sub> are well balanced and are equal to half of the dc voltage source, i.e., 50V as shown in Fig. 12 (b). Fig. 12 (c) depicts the FFT spectrum of the output voltage with a THD value of 9.5% which is analogous to the simulation value of THD.

FIGURE 11. Experimental setup for the proposed nine level topology.

FIGURE 12. Experimental results of (a) output voltage, output current waveform [v = 100v/div, i = 5A/div] (b) capacitor voltages [ $V_{c1} = V_{c2} = 10V/\text{div}$ ] and (c) FFT of output voltage with  $Z = 100\text{mH} + 10~\Omega$ .

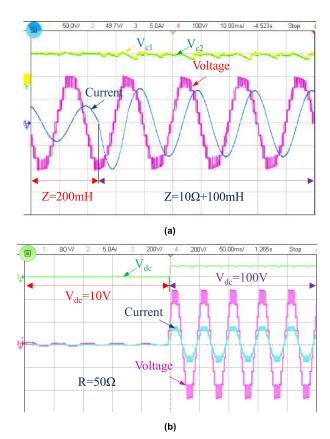

Moreover, a change in the type of load has also been considered during the experimental results. Fig. 13 (a) shows the waveforms as the load changes from resistive-inductive load to a purely inductive load. Furthermore, the proposed topology has been tested with a step-change in input dc voltage while feeding the resistive load. The input dc voltage  $V_{\rm dc}$  is changed to 100V from 10V and the corresponding voltage and current waveforms are shown in Fig. 13 (b). All these results prove the suitability and feasibility of the proposed nine-level boost inverter topology for varying operating conditions.

Fig. 14 shows the variation of efficiency of the proposed topology with simulation and hardware results. As the

FIGURE 13. Experimental results for the proposed nine level MLI with (a) change of load from purely inductive to resistive-inductive load  $[\nu=100v/{\rm div},\,i=5{\rm A/div},\,V_{\rm c1}=V_{\rm c2}=50V/{\rm div}]$  and (b) step change in input dc voltage source from 10V to 100V  $[\nu=80V/{\rm div},\,i=5{\rm A/div},\,V_{\rm dc}=200V/{\rm div}.]$

FIGURE 14. Simulation and experimental efficiency of the proposed topology.

maximum efficiency of the proposed topology in simulation is 98.25%, however, with the experimental setup, the measured efficiency is about 96%.

# **V. CONCLUSION**

A new single-phase nine-level MLI topology has been proposed in this paper. The proposed nine-level boost inverter topology has been based on switched capacitors with a reduced number of switches. A detailed comparative study highlights the proposed topology potential in terms of reduced requirements of components for the same number of voltage levels. The cost comparison supplements the lower

price of the proposed topology with a single dc voltage source for nine-level and proves it to be cost-beneficial. The efficiency comparison also gives the additional edge of the proposed topology compare to other topologies. The reduction in the number of components, cost, and higher efficiency makes the proposed topology suitable for low and medium voltage applications. The workability of the proposed topology has been proved by the different results with various loading conditions. The different simulation and hardware results verify the improved performance of the proposed topology.

#### **REFERENCES**

- H. Akagi, "Multilevel converters: Fundamental circuits and systems," Proc. IEEE, vol. 105, no. 11, pp. 2048–2065, Nov. 2017.

- [2] L. Franquelo, J. Rodriguez, J. Leon, S. Kouro, R. Portillo, and M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

- [3] J. I. Leon, S. Vazquez, and L. G. Franquelo, "Multilevel converters: Control and modulation techniques for their operation and industrial applications," *Proc. IEEE*, vol. 105, no. 11, pp. 2066–2081, Nov. 2017.

- [4] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A new multilevel inverter topology with reduce switch count," *IEEE Access*, vol. 7, pp. 58584–58594, 2019.

- [5] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters-state of the art, challenges, and requirements in industrial applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

- [6] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 135–151, Jan. 2016.

- [7] M. D. Siddique, S. Mekhilef, N. M. Shah, and M. A. Memon, "Optimal design of a new cascaded multilevel inverter topology with reduced switch count," *IEEE Access*, vol. 7, pp. 24498–24510, 2019.

- [8] M. Vijeh, M. Rezanejad, E. Samadaei, and K. Bertilsson, "A general review of multilevel inverters based on main submodules: Structural point of view," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9479–9502, Oct. 2019.

- [9] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, M. Tayyab, and M. K. Ansari, "Low switching frequency based asymmetrical multilevel inverter topology with reduced switch count," *IEEE Access*, vol. 7, pp. 86374–86383, 2019.

- [10] M. Sharifzadeh and K. Al-Haddad, "Packed E-cell (PEC) converter topology operation and experimental validation," *IEEE Access*, vol. 7, pp. 93049–93061, 2019.

- [11] D. Niu, F. Gao, P. Wang, K. Zhou, F. Qin, and Z. Ma, "A nine-level T-type packed U-cell inverter," *IEEE Trans. Power Electron.*, vol. 35, no. 2, pp. 1171–1175, Feb. 2020.

- [12] P. Bhatnagar, R. Agrawal, N. K. Dewangan, S. K. Jain, and K. K. Gupta, "Switched-capacitors 9-level module (SC9LM) with reduced device count for multilevel DC to AC power conversion," *IET Electr. Power Appl.*, vol. 13, no. 10, pp. 1544–1552, Oct. 2019.

- [13] S. R. Raman, Y. C. Fong, Y. Ye, and K. W. E. Cheng, "Family of multiport switched-capacitor multilevel inverters for high-frequency AC power distribution," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4407–4422, May 2019.

- [14] E. Samadaei, M. Kaviani, and K. Bertilsson, "A 13-levels module (K-type) with two DC sources for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 66, no. 7, pp. 5186–5196, Jul. 2019.

- [15] S. S. Lee, "A single-phase single-source 7-level inverter with triple voltage boosting gain," *IEEE Access*, vol. 6, pp. 30005–30011, 2018.

- [16] X. Sun, B. Wang, Y. Zhou, W. Wang, H. Du, and Z. Lu, "A single DC source cascaded seven-level inverter integrating switched-capacitor techniques," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7184–7194, Nov. 2016.

- [17] M. D. Siddique, S. Mekhilef, N. M. Shah, J. S. M. Ali, and F. Blaabjerg, "A new switched capacitor 7L inverter with triple voltage gain and low voltage stress," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, to be published, doi: 10.1109/TCSII.2019.2932480.

- [18] N. Sandeep and U. R. Yaragatti, "Operation and control of an improved hybrid nine-level inverter," *IEEE Trans. Ind. Appl.*, vol. 53, no. 6, pp. 5676–5686, Nov. 2017.

- [19] Y. P. Siwakoti, A. Mahajan, D. J. Rogers, and F. Blaabjerg, "A novel seven-level active neutral-point-clamped converter with reduced active switching devices and DC-link voltage," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 10492–10508, Nov. 2019.

- [20] H. Yu, B. Chen, W. Yao, and Z. Lu, "Hybrid seven-level converter based on T-type converter and H-bridge cascaded under SPWM and SVM," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 689–702, Jan. 2018.

- [21] M. J. Sathik, K. Bhatnagar, N. Sandeep, and F. Blaabjerg, "An improved seven-level PUC inverter topology with voltage boosting," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 1, pp. 127–131, Jan. 2020, doi: 10.1109/tcsii.2019.2902908.

- [22] J. Liu, X. Zhu, and J. Zeng, "A seven-level inverter with self-balancing and low voltage stress," *IEEE J. Emerg. Sel. Topics Power Electron.*, to be published, doi: 10.1109/JESTPE.2018.2879890.

- [23] J. Zeng, W. Lin, and J. Liu, "Switched-capacitor-based active-neutral-point-clamped seven-level inverter with natural balance and boost ability," *IEEE Access*, vol. 7, pp. 126889–126896, 2019.

- [24] J. Liu, J. Wu, and J. Zeng, "Symmetric/asymmetric hybrid multilevel inverters integrating switched-capacitor techniques," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 6, no. 3, pp. 1616–1626, Sep. 2018.

- [25] S. S. Lee and K.-B. Lee, "Dual-T-type seven-level boost active-neutral-point-clamped inverter," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6031–6035, Jul. 2019.

- [26] S. S. Lee, "Single-stage switched-capacitor module (S<sup>3</sup>CM) topology for cascaded multilevel inverter," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 8204–8207, Oct. 2018.

- [27] J. S. M. Ali and V. Krishnasamy, "Compact switched capacitor multi-level inverter (CSCMLI) with self-voltage balancing and boosting ability," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4009–4013, May 2019.

- [28] R. Barzegarkhoo, M. Moradzadeh, E. Zamiri, H. M. Kojabadi, and F. Blaabjerg, "A new boost switched-capacitor multilevel converter with reduced circuit devices," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 6738–6754, Aug. 2018.

- [29] A. Taghvaie, J. Adabi, and M. Rezanejad, "A multilevel inverter structure based on a combination of switched-capacitors and DC sources," *IEEE Trans. Ind. Informat.*, vol. 13, no. 5, pp. 2162–2171, Oct. 2017.

- [30] M. Khenar, A. Taghvaie, J. Adabi, and M. Rezanejad, "Multi-level inverter with combined T-type and cross-connected modules," *IET Power Elec*tron., vol. 11, no. 8, pp. 1407–1415, Jul. 2018.

- [31] A. Taghvaie, J. Adabi, and M. Rezanejad, "Circuit topology and operation of a step-up multilevel inverter with a single DC source," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 6643–6652, Nov. 2016.

- [32] N. Sandeep, J. S. M. Ali, U. R. Yaragatti, and K. Vijayakumar, "A self-balancing five-level boosting inverter with reduced components," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6020–6024, Jul. 2019.

- [33] Y. Nakagawa and H. Koizumi, "A boost-type nine-level switched capacitor inverter," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6522–6532, Jul. 2019.

- [34] B.-B. Ngo, M.-K. Nguyen, J.-H. Kim, and F. Zare, "Single-phase multi-level inverter based on switched-capacitor structure," *IET Power Electron.*, vol. 11, no. 11, pp. 1858–1865, Sep. 2018.

- [35] N. Sandeep and U. R. Yaragatti, "A switched-capacitor-based multilevel inverter topology with reduced components," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5538–5542, Jul. 2018.

- [36] J. Liu, J. Wu, J. Zeng, and H. Guo, "A novel nine-level inverter employing one voltage source and reduced components as high-frequency AC power source," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2939–2947, Apr. 2017.

- [37] R. M. Sekar, D. N. Jayakumar, K. Mylsamy, U. Subramaniam, and S. Padmanaban, "Single phase nine level inverter using single DC source supported by capacitor voltage balancing algorithm," *IET Power Electron.*, vol. 11, no. 14, pp. 2319–2329, Nov. 2018.

- [38] M. Saeedian, M. E. Adabi, S. M. Hosseini, J. Adabi, and E. Pouresmaeil, "A novel step-up single source multilevel inverter: Topology, operating principle, and modulation," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3269–3282, Apr. 2019.

MARIF DAULA SIDDIQUE (Student Member, IEEE) was born in Chhapra, India, in 1992. He received the B.Tech. and M.Tech. degrees in electrical engineering from Aligarh Muslim University (AMU), in 2014 and 2016, respectively. He is currently pursuing the Ph.D. degree with the Power Electronics and Renewable Energy Research Laboratory (PEARL), Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia. He is currently a Visiting

Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar. His research interests include step-up power electronics converters (dc/ac and dc/dc), multilevel inverter topologies and their control, and grid-tied applications of power electronic converters with solar photovoltaic systems. He is serving as a regular Reviewer for several journals including the IEEE Transactions on Power Electronics, *IET Power Electronics*, and IEEE Access.

**SAAD MEKHILEF** (Senior Member, IEEE) received the B.Eng. degree in electrical engineering from the University of Sétif, Sétif, Algeria, in 1995, and the master's degree in engineering science and the Ph.D. degree in electrical engineering from the University of Malaya, Kuala Lumpur, Malaysia, in 1998 and 2003, respectively. He is currently a Professor and the Director of the Power Electronics and Renewable Energy Research Laboratory, Department of Electrical Engineering,

University of Malaya. He is also currently the Dean of the Faculty of Engineering, University of Malaya. He is also a Distinguished Adjunct Professor with the School of Software and Electrical Engineering, Faculty of Science, Engineering and Technology, Swinburne University of Technology, VIC, Australia. He has authored or coauthored more than 450 publications in international journals and conference proceedings. His current research interests include power converter topologies, control of power converters, renewable energy, and energy efficiency.

NORAISYAH MOHAMED SHAH (Member, IEEE) received the B.Eng. degree from the University of Malaya, in 1999, the M.Eng. degree from Oita University, Japan, in 2003, and the Ph.D. degree from George Mason University, Fairfax, VA, USA, in 2014. She is currently a Senior Lecturer with the Department of Electrical Engineering, University of Malaya. Her current research interests include signal processing and renewable energy.

in 1991. He received the B.E. degree in electrical and electronics engineering from the BMS College of Engineering, Bengaluru, the M.Tech. degree in power electronics and drives from the Visvesvaraya National Institute of Technology Nagpur, Nagpur, India, and the Ph.D. degree in electrical and electronics engineering from the National Institute of Technology Karnataka, Surathkal, India, in 2012, 2014, and

N. SANDEEP was born in Bengaluru, India,

2018 respectively.

His research interests include multilevel inverters and grid-tied renewables. He was a recipient of the Best Poster Prize Award from the 18th IEEE National Power Systems Conference 2014 at IIT Guwahati, Guwahati, India. He is serving as a regular Reviewer for several journals including the IEEE Transactions on Industrial Electronics, the IEEE Transactions on Power Electronics, and the IET Power Electronics.

JAGABAR SATHIK MOHAMED ALI (Senior Member, IEEE) was born in Thanjavur, India, in 1979. He received the B.E. degree in electronics and communication engineering from Madurai Kamarajar University, Madurai, India, in 2002, and the M.E. and Ph.D. degrees from the Faculty of Electrical Engineering, Anna University, Chennai, India, in 2004 and 2016, respectively. He is currently an Associate Professor with the Department of Electrical and Electronics Engineering, SRM

Institute of Science and Technology (formerly SRM University), Chennai. He is consultant of various power electronics companies for the design of power electronics converters. He has authored more than 20 articles publications in international journals and conference proceedings. His current research interests include multilevel inverters, grid-connected inverters, and power electronics converters and its applications in renewable energy systems.

ATIF IQBAL (Senior Member, IEEE) received the B.Sc. (Gold Medal) and M.Sc. (power system and drives) degrees in engineering from the Aligarh Muslim University (AMU), Aligarh, India, in 1991 and 1996, respectively, and the Ph.D. degree from Liverpool John Moores University, Liverpool, U.K., in 2006. He received the Ph.D. degree in the U.K. He is an Associate Professor of electrical engineering with Qatar University. He is also a former Full Professor of electrical engineering with

AMU, Aligarh. He has been employed as a Lecturer with the Department of Electrical Engineering, AMU, Aligarh, since 1991, where he served as a Full Professor, until August 2016. He was a recipient of the Outstanding Faculty Merit Award AY and the Research Excellence Award at Qatar University, Doha, Qatar, from 2014 to 2015, and the Maulana Tufail Ahmad Gold Medal for standing first at the B.Sc. engineering exams with AMU. He has received best research articles including the IEEE ICIT 2013, IET-SEISCON 2013, and SIGMA 2018. He has published widely his research findings related to power electronics and renewable energy sources in international journals and conferences. He has authored/coauthored more than 300 research articles, one book, and three chapters in two other books. He is a Fellow the IET U.K., and IE, India. He has supervised several large research and development projects. His research interests include modeling and simulation of power electronic converters, control of multi-phase motor drives and renewable energy sources, solar photovoltaic systems, and metaheuristic algorithms. He is an Associate Editor of the IEEE Transaction on Industry Application and the Editor-in-Chief of the Journal of Electrical Engineering (i'manager).

MAHROUS AHMED received the B.S. and M.Sc. degrees in electrical engineering from Assiut University, Assiut, Egypt, in 1996 and 2000, respectively, and the Ph.D. degree in electrical engineering from the University of Malaya, Kuala Lumpur, Malaysia, in 2007. Since 2007, he has been an Assistant Professor with the Aswan Faculty of Engineering, Aswan University, Aswan, Egypt. In 2014, he became an associate professor. He is currently an Associate Professor with the

Faculty of Engineering, Taif University, Saudi Arabia. He has awarded more than 10 research funded projects in the field of power electronics applications. He has published more than 70 articles in an international sited journals and conferences. His research interests include power conversion techniques and power electronics applications.

**SHERIF S. M. GHONEIM** received the B.Sc. and M.Sc. degrees from the Faculty of Engineering, Zagazig University, Egypt, in 1994 and 2000, respectively, and the Ph.D. degree in electrical power and machines from the Faculty of Engineering, Cairo University, in 2008. Since 1996, he has been a Teaching Staff with the Faculty of Industrial Education, Suez Canal University, Egypt. He is currently a Guest Researcher with the Institute of Energy Transport and Storage (ETS), University of

Duisburg–Essen, Germany. He is currently an Assistant Professor with the Electrical Engineering Department, Faculty of Engineering, Taif University. His research interests include grounding systems, dissolved gases analysis, breakdown in SF6 gas, and artificial intelligent technique applications.

MOSLEH M. AL-HARTHI was born in Taif, Saudi Arabia, in October 15, 1966. He received the B.Sc. degree in electronics technology and engineering from Indiana State University, Terre Haute, USA, in 1996, the M.S. degree in electronics technology and engineering from Indiana State University, in 1997, and the Ph.D. degree in electrical engineering from Arkansas University, Fayetteville, USA. He was an Assistant Professor with the College of Technology, Jeddah, Saudi Arabia, from

2001 to 2009. He is currently a Professor with the Electrical Engineering Department, Taif University, Saudi Arabia, where he is currently with the Dean of the College of Engineering. His research interests include control engineering, electronics, and signal processing.

**BASEM ALAMRI** received the B.Sc. degree (Hons.) in electrical engineering from KFUPM, the M.Sc. degree (Hons.) in electrical power systems from King Abdulaziz University, Jeddah, Saudi Arabia, the M.Sc. degree in sustainable electrical power from Brunel University, London, U.K., in 2007 and 2008, respectively, and the Ph.D. degree in electrical power engineering from Brunel University, London, in 2017. He is currently an Assistant Professor of electrical engineering with

the College of Engineering, Taif University. His research interests include power systems, power quality, power filter design, and smart grids with a particular emphasis on the integration of renewable energy sources with power grids. He is a member of many international and local professional organizations. He is also a Certified Energy Auditor and a Certified Energy Manager of the Association of Energy Engineers (AEE), USA. He has received many awards and prizes including a certificate from Advance Electronics Company (AEC) in recognition of outstanding academic achievement during the B.Sc. degree with KFUPM. He also received the National Grid (NG) Prize and the Power Grid Operator in the U.K., for being the top distinction student of the M.Sc. degree of the SEP Program with Bunel University, London, U.K.

**FARHAN A. SALEM** was born in Jordan. He received the M.Sc. degree in mechatronics of production systems from Moscow State Academy of instrument making and information technology, Moscow, in 1996 and the Ph.D. degree in production and manufacturing/mechanical and physicotechnical processing machines and tools from the University of Russia, Moscow, in July 2000. He is currently an Associate Professor of the Industrial Engineering Program with the Department of

Mechanical Engineering, Taif University.

MOHAMED ORABI (Senior Member, IEEE) received the Ph.D. degree from Kyushu University, Fukuoka, Japan, in 2004. He is currently a Professor with Aswan University, Aswan, Egypt. He is the Founder and the Director of the Aswan Power Electronics Application Research Center, Aswan University. He was with Enpirion Inc., and Altera Corp., from June 2011 to July 2014. He has published about 200 articles in international conference proceedings and journals. His

research interests include dc—dc and PFC converters, integrated power management, nonlinear circuits, and inverter design for renewable energy applications. He received the 2002 Excellent Student Award of the IEEE Fukuoka Section and the Best Young Research Award from the IEICE Society, Japan, in 2004. He also received the SVU Encouragement Award, in 2009, and the National Encouragement Award, in 2010. He is an Associate Editor of *IET Power Electronics* and a Guest Editor of the IEEE Journal of Emerging and Selected Topics in Power Electronics.

• • •