# A Smart IGBT Gate Driver IC with Temperature Compensated Collector Current Sensing

by

Jingxuan Chen

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy

Edward S. Rogers Sr. Department of Electrical & Computer Engineering University of Toronto

© Copyright by Jingxuan Chen 2018

# A Smart IGBT Gate Driver IC with Temperature Compensated Collector Current Sensing

Jingxuan Chen

Doctor of Philosophy

Edward S. Rogers Sr. Department of Electrical & Computer Engineering University of Toronto

2018

#### Abstract

Precision current measurement is a critical function that must be incorporated into modern high voltage and high current power systems. Conventional IGBT current sensing methods usually employ discrete sensors such as lossy shunt resistors and involve accessing the high voltage collector load of the IGBT. This would normally present difficulties for integration. In this thesis, an IGBT collector current sensing technique which only utilizes the low voltage signal at the gate terminal is presented. This technique is based on the unique Miller plateau relationship between the gate current and collector current ( $I_G$  and  $I_C$ ) for a particular gate resistance ( $R_G$ ), and allows for a cycle by cycle measurement of  $I_C$  during both turn-on and turn-off transients. This technique is theoretically verified, experimentally demonstrated and integrated into an IGBT gate driver IC. The presented gate driver IC has a highly configurable gate driver, an on-chip CPU for local data processing and an integrated current sensor. This IC is prototyped using TSMC 0.18µm BCD Gen-2 process. A polynomial curve fitting is implemented by the on-chip CPU to predict  $I_C$  based on the digitized  $I_G$  value. Measurements using a double pulse test setup at room temperature show that an accuracy of  $\pm 1$  A could be ensured with a  $2^{nd}$  order polynomial curve fitting, within the current range between 1 to 30 A for turn-on and 1 to 50 A for turn-off. After the temperature effect is analyzed and factored in, a 3rd order polynomial curve fitting is implemented, an estimated accuracy of  $\pm 0.5$  A could be achieved within the current range of 1 to 30 A for turn-on and 1 to 50 A for turn-off from 25 to 75 °C.

#### Acknowledgments

First and foremost, I would like to express my deepest appreciation to my supervisor, Professor Wai Tung Ng, for his insightful guidance and great support throughout my entire graduate studies. My research background was focused on power device modeling and fabrication for my M.A.SC degree. However, I decided to endeavor to the power circuit and power IC design area for my PhD research. Without his tremendous support and confidence in me, this challenging transition would not be possible. I am truly thankful to have the opportunity to work under his guidance in the past six and half years. The things that I have learnt from him not only include technical and problem solving skills, but also attitudes towards life and family, which will inspire me and motivate me for my future life journey.

I would like to thank all my fellow graduate students in the Smart Power Integration and Semiconductor Devices research group. I want to thank Andrew Shorten, for his patient help and thoughtful guidance throughout my PhD project. I want to thank Weijia Zhang, Jingshu Yu and Tae Young Goh for their great help during my tape-out. I also want to thank Joshua Chung, Robert Mckenzie, Rophina Li, Mengqi Wang, Wenfang Du for their companionship and support during our shared time in the research lab.

Special thanks to Fuji Electric for their financial support of our lab and my research. In particular, I want to thank Sasaki Masahiro and Nishio Haruhiko for their technical support and contributions. It has been a great pleasure and honor to work with them.

Many thanks to Jaro Pristupa, for his patient help on the CAD tool setup and support. The financial support from University of Toronto fellowship and the Natural Sciences and Engineering Research Council of Canada are gratefully appreciated.

Lastly, I would like to extend my appreciation to my family for their unconditional love and support. In particular, I want to thank my dear husband, Patrick Li, for his love, companionship, encouragement and sacrifice for me during my entire graduate study time.

# Table of Contents

| Acknowledgn    | nents     | iv                                       |

|----------------|-----------|------------------------------------------|

| Table of Cont  | ents      |                                          |

| List of Tables | •••••     | ix                                       |

| List of Figure | s         | X                                        |

| List of Glossa | ry        | xix                                      |

| Chapter 1      |           |                                          |

| Introduction   |           |                                          |

| 1.1.           | IGBT De   | vices and Applications2                  |

|                | 1.1.1.    | IGBT Device Structures                   |

|                | 1.1.2.    | IGBT Power Modules 4                     |

|                | 1.1.3.    | Intelligent Power Modules                |

|                | 1.1.4.    | IGBT Applications                        |

| 1.2.           | Trends in | Smart Gate Driver ICs for IGBTs9         |

|                | 1.2.1.    | Gate Drivers for IGBTs9                  |

|                | 1.2.2.    | Smart Gate Drivers 11                    |

|                | 1.2.3.    | Integrated Smart Gate Drivers 13         |

|                | 1.2.4.    | BCD Process Technology 15                |

| 1.3.           | Conventio | onal IC Sensing Methods for IGBTs 16     |

|                | 1.3.1.    | Current Sensing using Shunt Resistors 16 |

|                | 1.3.2.    | Sense-FET Current Sensing 18             |

|                | 1.3.3.    | Other Current Sensing Methods 21         |

| 1.4.           | Thesis Ov | verview                                  |

### Chapter 2

| Proposed IGB   | T Collecto            | or Current Sensing Technique and Discrete Implementation              | . 26 |

|----------------|-----------------------|-----------------------------------------------------------------------|------|

| 2.1.           | Proposed              | Current Sensing Method                                                | . 27 |

|                | 2.1.1.                | Basic IGBT Switching Transients                                       | . 27 |

|                | 2.1.2.                | IGBT Modeling                                                         | 31   |

| 2.2.           | Demonst               | ration of $I_G$ and $I_C$ relationship                                | . 34 |

| 2.3.           | Discrete              | Implementation of an Automatic I <sub>C</sub> Current Sensing Circuit | . 38 |

|                | 2.3.1.                | Experimental Test Bench Setup                                         | 40   |

|                | 2.3.2.                | Turn-on and Turn-off Plateau Sensing                                  | 41   |

|                | 2.3.3.                | Integrator Design and ADC Interface                                   | 43   |

|                | 2.3.4.                | Fixed Time Integration                                                | 45   |

| 2.4.           | Chapter S             | Summary                                                               | 48   |

| Chapter 3      |                       |                                                                       |      |

| Integrated IGI | BT Collect            | tor Current Sensing with Gate Driver and CPU                          | 50   |

| 3.1.           | Design O              | verview                                                               | 51   |

| 3.2.           | Embedde               | d SPRUCE Processing Unit                                              | 52   |

| 3.3.           | Gate Driv             | ver Design                                                            | 56   |

| 3.4.           | I <sub>C</sub> Sensin | g Input Stage                                                         | 58   |

|                | 3.4.1.                | High Voltage Resistor Divider                                         | 58   |

|                | 3.4.2.                | Input Analog Buffer                                                   | 60   |

| 3.5.           | Plateau S             | ensing Circuit Block                                                  | 63   |

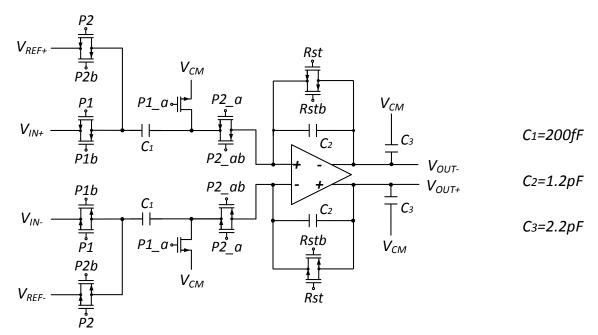

|                | 3.5.1.                | Switched-Capacitor Filter Design                                      | 64   |

|                | 3.5.2.                | Folded-Cascode Op-amp Design                                          | 68   |

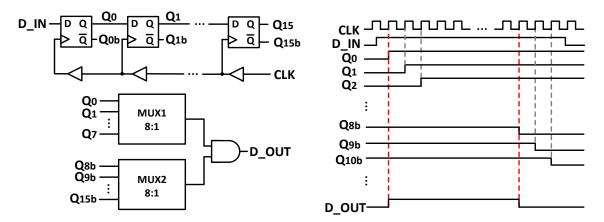

|                | 3.5.3.                | Logic Circuit for Fixed Time Integration                              | 81   |

| 3.6.           | Switched              | -Capacitor Integrator Design                                          | 84   |

| 3.7.        | Sample     | -and-Hold Design                     | 89  |

|-------------|------------|--------------------------------------|-----|

| 3.8.        | Delta-S    | igma ADC Design                      |     |

|             | 3.8.1.     | Architecture Modeling using MATLAB   |     |

|             | 3.8.2.     | Circuit Implementation               | 94  |

|             | 3.8.3.     | DSM Top Level Verification           | 101 |

|             | 3.8.4.     | SPRUCE Implemented Decimation Filter | 103 |

| 3.9.        | System     | Integration                          | 108 |

|             | 3.9.1.     | Clock Synchronization                | 108 |

|             | 3.9.2.     | System Configurability               | 109 |

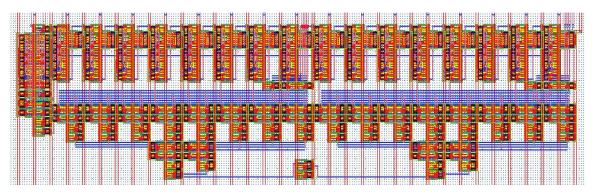

|             | 3.9.3.     | Final Chip Layout                    |     |

| 3.10.       | Chapter    | r Summary                            | 113 |

| Chapter 4   |            |                                      |     |

| Results and | Discussion | n                                    | 114 |

| 4.1.        | Test Se    | tup                                  | 114 |

| 4.2.        | Functio    | nality Test Results                  |     |

| 4.3.        | Temper     | rature Testing and Compensation      |     |

| 4.4.        | Chapter    | r Summary                            | 130 |

| Chapter 5   |            |                                      |     |

| Conclusion  | and Future | e Work                               |     |

| 5.1.        | Conclus    | sions                                |     |

| 5.2.        | Future     | Work                                 |     |

|             | 5.2.1.     | Accuracy Improvement                 |     |

|             | 5.2.2.     | Closed-loop Current Regulation       | 136 |

|             | 5.2.3.     | Zero Current Crossing Detection      | 136 |

|             | 5.2.4.     | Incorporate Active Gate Driving      | 137 |

|             |            |                                      |     |

| Reference                    | 138 |

|------------------------------|-----|

| Appendix A                   |     |

| Memory Map of the SPRUCE CPU | 144 |

| Appendix B                   |     |

| Publication List             | 145 |

# List of Tables

| Table 1.1: Comparison of existing current sensing methods and the proposed current   |

|--------------------------------------------------------------------------------------|

| sensing technique                                                                    |

|                                                                                      |

| Table 1.2: Application hints for existing current sensing methods and the proposed   |

| current sensing technique                                                            |

| Table 3.1: SPRUCE Instruction Set [78]    55                                         |

| Table 3.2: Gate driver output resistance for each segment.    58                     |

| Table 3.3: Transistor sizes and properties for the switches in the SC filter         |

| Table 3.4: Transistor sizes for the folded-cascode op-amp.    70                     |

| Table 3.5: Transistor Sizes for the Op-amp Bias Circuit                              |

| Table 3.6: Bias voltage levels for the op-amp.    71                                 |

| Table 3.7: Transistor Sizes and Properties for the Switches in the n-Booster      72 |

| Table 3.8: Transistor Sizes and Properties for the Switches in the p-Booster         |

| Table 3.9: Summary of the Simulation Results for the Folded Cascode Op-amp           |

| Table 3.10: Transistor Sizes for the Comparator    80                                |

| Table 3.11: Summary of the Simulated Performance for the Comparator                  |

| Table 3.12: Transistor Sizes for the Comparator in the DSM                           |

| Table 3.13: Summary of the specifications for the $\Delta\Sigma$ ADC                 |

| Table 3.14: Summary of the configuration bits for the $I_C$ sensing circuitry        |

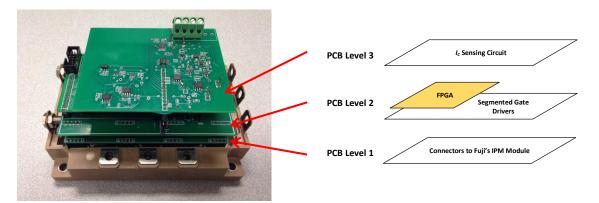

| Table 4.1: Component List for the Gate Drive IC test PCB    116                      |

| Table 4.2: Chip performance summary.    130                                          |

# List of Figures

| Figure 1.1: (a) Conventional Planar Gate and Punch-Through IGBT; (b) Planar Gate and       |

|--------------------------------------------------------------------------------------------|

| Non-Punch-Through IGBT; (c) Trench Gate and Non-Punch-Through IGBT                         |

| Figure 1.2: Cross-sectional view of a basic IGBT power module                              |

| Figure 1.3: A Fuji Electric 7MBP200VEA060-50 IPM module. (a) The driver and control        |

| circuit board, (b) the IGBTs and FWDs on the bottom                                        |

| Figure 1.4: Photo and simplified schematic of an IGBT chip for IPMs with on chip           |

| current and temperature sensors [10]7                                                      |

| Figure 1.5: Application spectrum for IGBTs [1]                                             |

| Figure 1.6: Simplified circuit for (a) voltage source, (b) current source and (c) resonant |

| gate driver topologies during charging and discharging intervals [25] 10                   |

| Figure 1.7: Developed features of modern smart gate drivers for power MOSFETs and          |

| IGBTs12                                                                                    |

| Figure 1.8: Functional block diagram of a generalized smart gate driver IC 13              |

| Figure 1.9: Illustration of the BCD IC technology which includes bipolar, CMOS and         |

| DMOS devices on the same IC 15                                                             |

| Figure 1.10: (a) Traditional IGBT collector current sensing methods using a shunt resistor |

| (b) shunt resistor current sensing implemented in a 3-phase power inverter 17              |

| Figure 1.11: Schematic of using a Sense-FET for over current protection                    |

| Figure 1.12: Schematic explaining the effect of residue resistance exerting on the current |

| sensing ratio variation [73]                                                               |

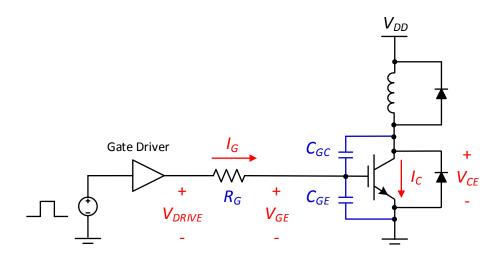

| Figure 2.1: Test bench schematic for IGBT switching transient analysis with inductive      |

| load                                                                                       |

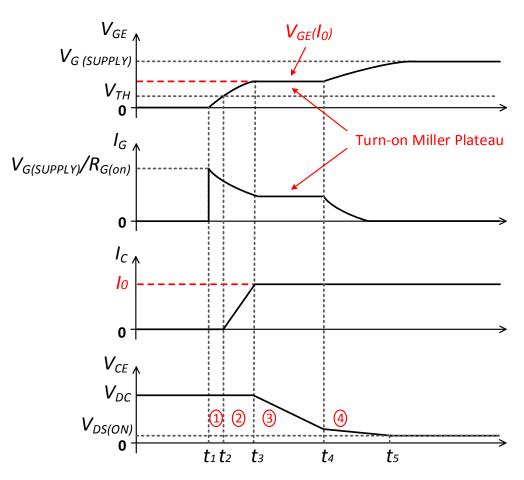

| Figure 2.2: Typical turn-on waveforms for IGBTs                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------|

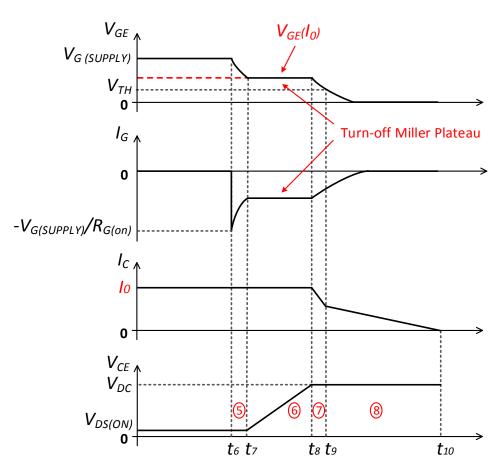

| Figure 2.3: Typical turn-off waveforms for IGBTs                                                                                       |

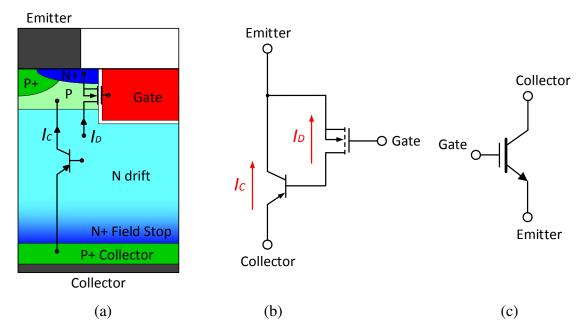

| Figure 2.4: (a) Cross section of a typical trench gate field-stop IGBT, (b) a simplified IGBT mode, (c) typical IGBT symbol            |

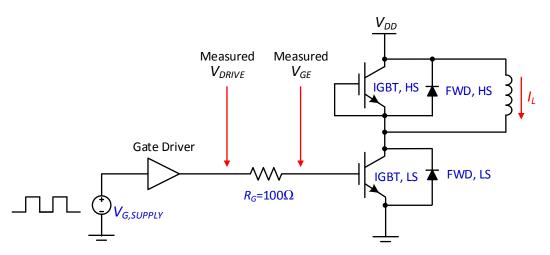

| Figure 2.5: Experimental test bench schematic (IGBT model: IGB30N60H3)                                                                 |

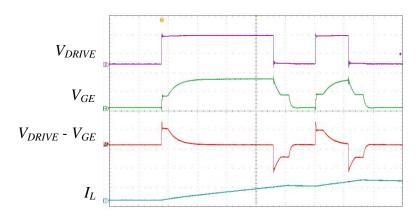

| Figure 2.6: Sample waveforms for $V_{DRIVE}$ , $V_{GE}$ , $V_{DRIVE}$ - $V_{GE}$ and $I_{L}$                                           |

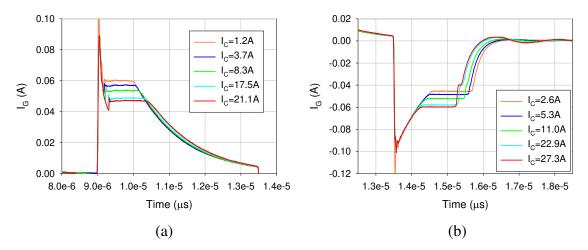

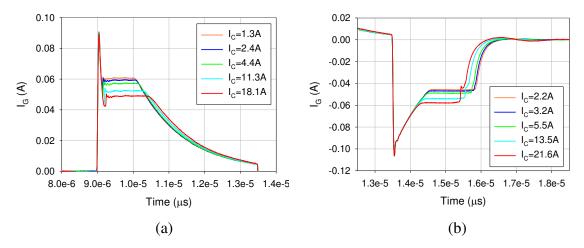

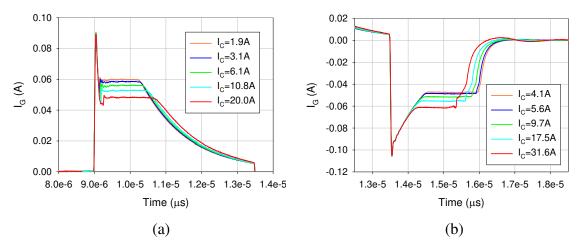

| Figure 2.7: Measured $I_G$ waveforms for different $I_C$ when $V_{DD} = 25$ V at (a) turn-on and (b) turn-off                          |

| Figure 2.8: Measured $I_G$ waveforms for different $I_C$ when $V_{DD} = 100$ V at (a) turn-on and (b) turn-off                         |

| Figure 2.9: Measured $I_G$ waveforms for different $I_C$ when $V_{DD} = 250$ V at (a) turn-on and (b) turn-off                         |

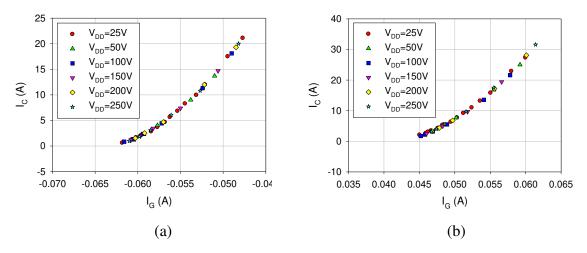

| Figure 2.10: Measured $I_C$ vs. $I_G$ for (a) turn-on plateau values (b) turn-off plateau values.<br>37                                |

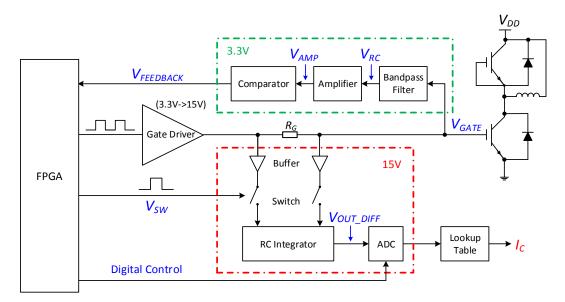

| Figure 2.11: Block diagram for the discrete implementation of the current sensing circuit.                                             |

| Figure 2.12 (a): Experimental Testbed for Current Sensing System                                                                       |

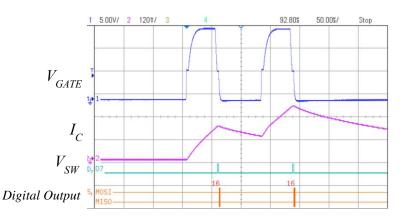

| Figure 2.13: Typical waveforms for $V_{GATE}$ , $I_C$ , $V_{SW(turn-off)}$ and digital outputs                                         |

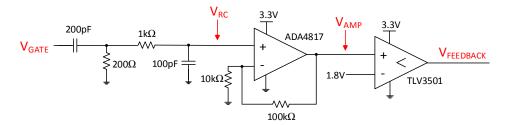

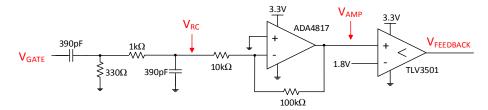

| Figure 2.14: Schematic for the turn-on Miller plateau sensing circuit                                                                  |

| Figure 2.15: Schematic for the turn-off Miller plateau sensing circuit                                                                 |

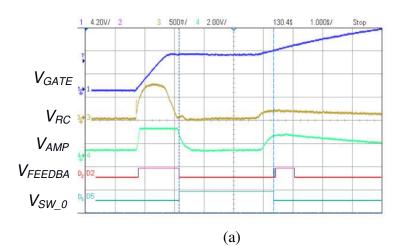

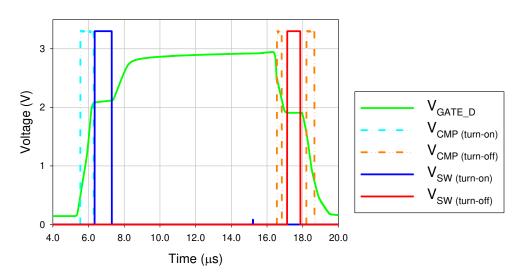

| Figure 2.16: (a) Sample waveforms for sensing the turn-on Miller plateau. (b) Sample waveforms for sensing the turn-off Miller plateau |

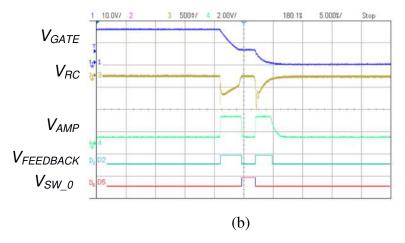

| Figure 2.17: Schematic for the fully differential integrator                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

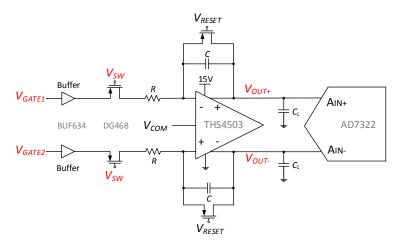

| Figure 2.18: (a) Output waveforms of the differential integrator during turn-on; (b) Output waveforms of the differential integrator during turn-off |

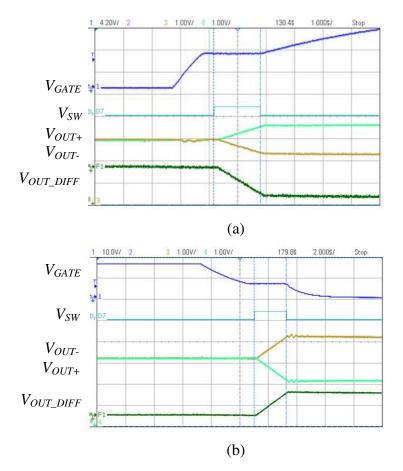

| Figure 2.19: Switching waveforms of $V_{GATE}$ , $V_{SW}$ , $V_{OUT+}$ , $V_{OUT-}$ and $V_{OUT\_DIFF}$ during turn-off                              |

| Figure 2.20: D Flip-Flop chain for fixed time integration                                                                                            |

| Figure 2.21: $I_G$ as a function of time at different $I_C$ levels for turn-off when $V_{CE} = 20$ V.46                                              |

| Figure 2.22: (a) Typical waveforms illustrating the fixed time integration for turn-on and (b) turn-off                                              |

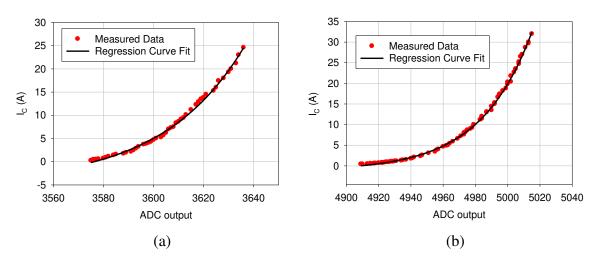

| Figure 2.23: (a) $I_C$ vs. digital ADC output for turn-on. (b) $I_C$ vs. digital ADC output for turn-off                                             |

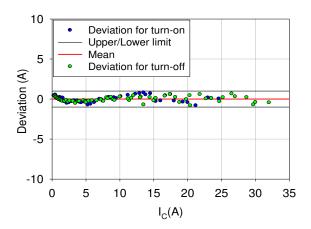

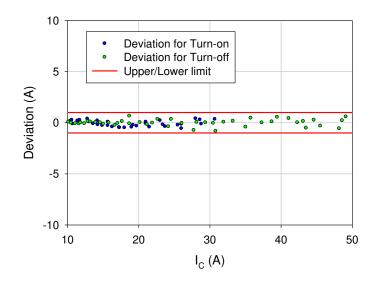

| Figure 2.24: Deviation of the measured $I_C$ to the regression fitted curve vs. $I_C$                                                                |

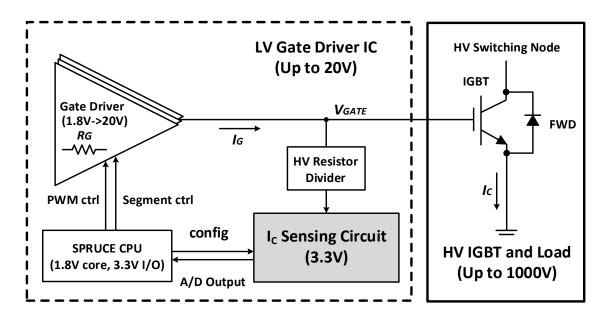

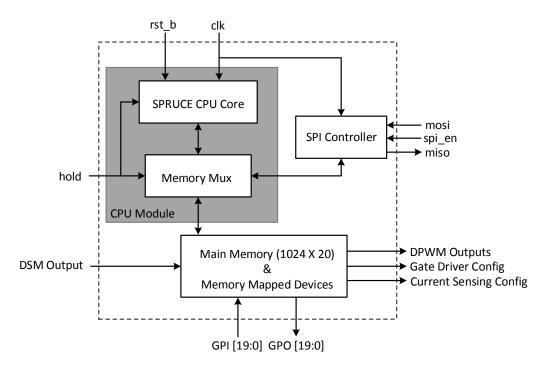

| Figure 3.1: Block diagram of the proposed gate driver IC with current sensing51                                                                      |

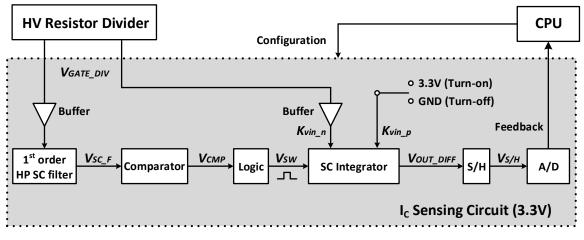

| Figure 3.2: Block diagram of the $I_C$ sensing circuit                                                                                               |

| Figure 3.3: The block level diagram for the SPRUCE unit and its peripheral digital modules on the gate driver IC                                     |

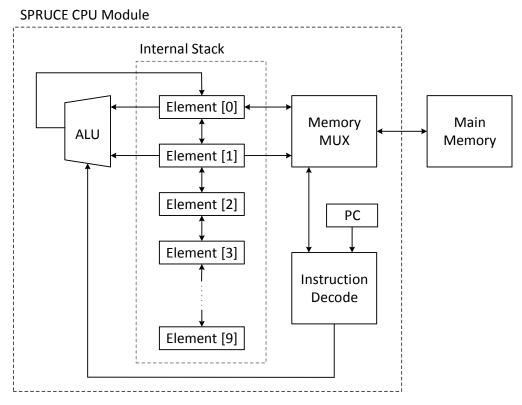

| Figure 3.4: Block Diagram of the SPRUCE architecture [78]                                                                                            |

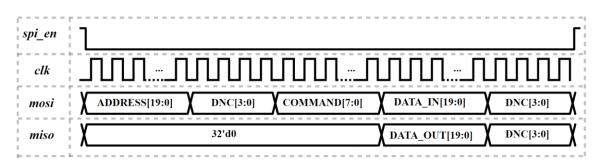

| Figure 3.5: SPRUCE SPI Communication Protocol                                                                                                        |

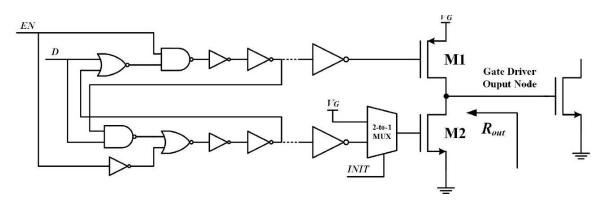

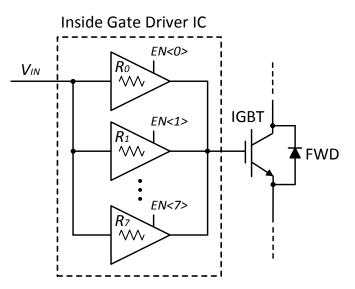

| Figure 3.6: General schematic of each gate driver segment [86]                                                                                       |

| Figure 3.7: Simplified diagram for the segmented gate driver [44]                                                                                    |

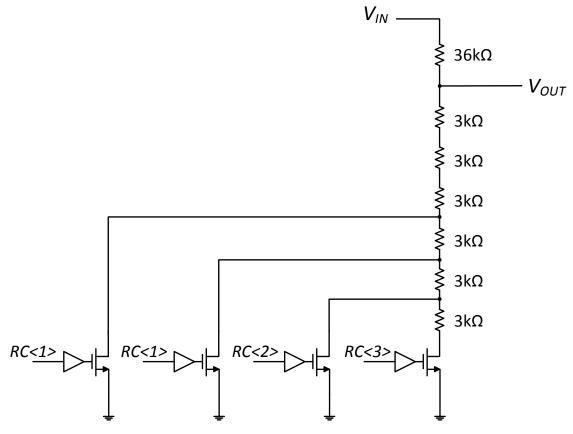

| Figure 3.8: High voltage resistor divider network                                                                                                    |

| Figure 3.9: HV resistor divider layout. The total area used is $440\mu m \times 270\mu m$                                                            |

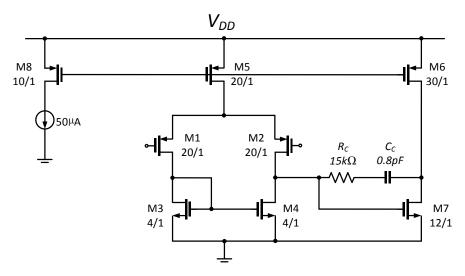

| Figure 3.10: Schematic of the two-stage op-amp used as the input buffer. The transistor                |

|--------------------------------------------------------------------------------------------------------|

| size unit is in µm61                                                                                   |

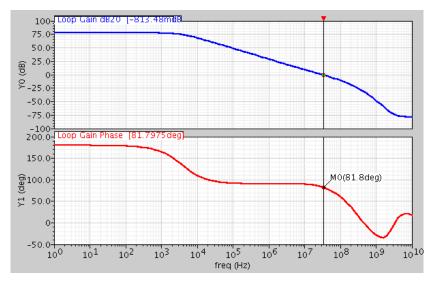

| Figure 3.11: Input buffer open loop frequency response when connected to SC filter 61                  |

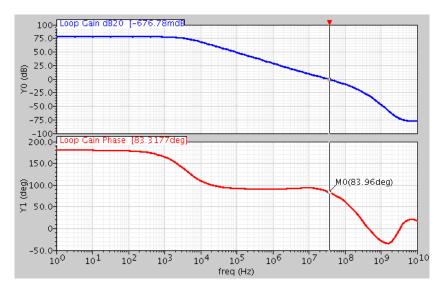

| Figure 3.12: Input buffer open loop frequency response when connected to SC integrator.                |

|                                                                                                        |

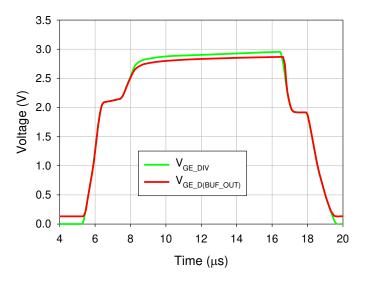

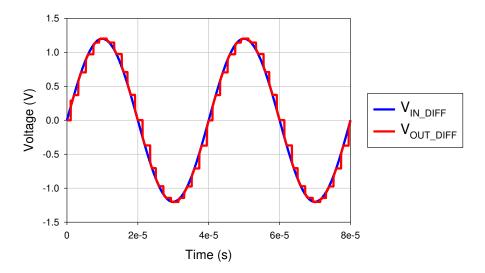

| Figure 3.13: Transient simulation results for the input buffer block                                   |

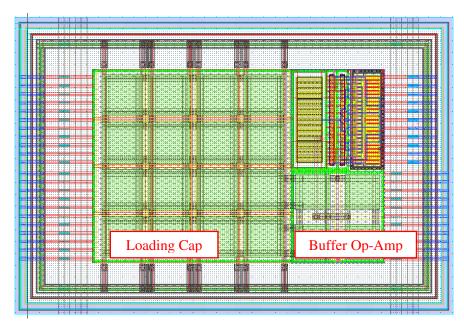

| Figure 3.14: Layout for the input buffer block. The total area used is $125\mu m \times 185\mu m$ . 63 |

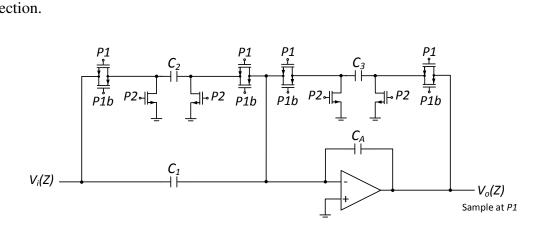

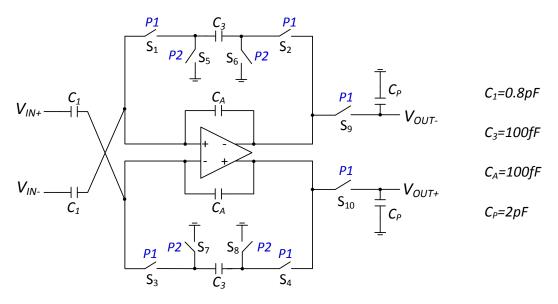

| Figure 3.15: A typical first order switched-capacitor filter [87]                                      |

| Figure 3.16: Switched-capacitor filter schematic                                                       |

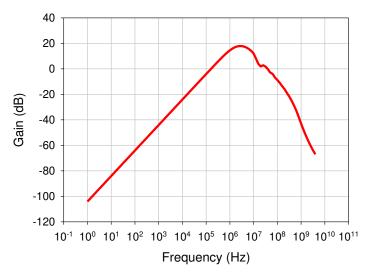

| Figure 3.17: Switch capacitor filter frequency response using Spectre PSS analysis 67                  |

| Figure 3.18: Simulated response for the Miller plateau detection at the output of the high             |

| pass (HP) SC filter                                                                                    |

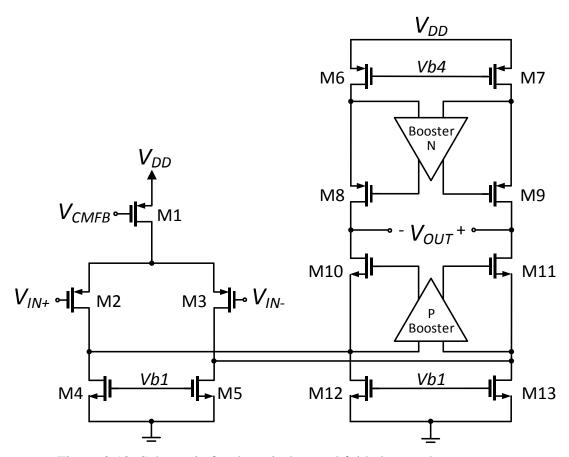

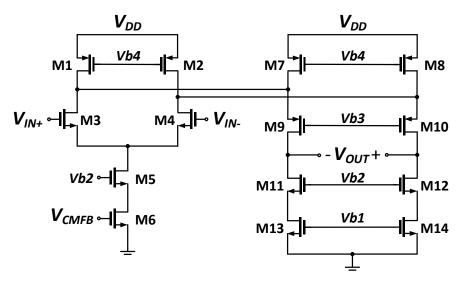

| Figure 3.19: Schematic for the gain-boosted folded-cascode op-amp                                      |

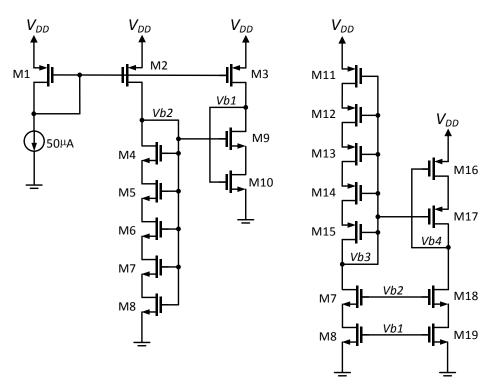

| Figure 3.20: Schematic for the op-amp bias circuit                                                     |

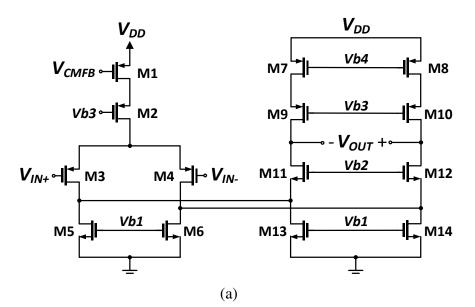

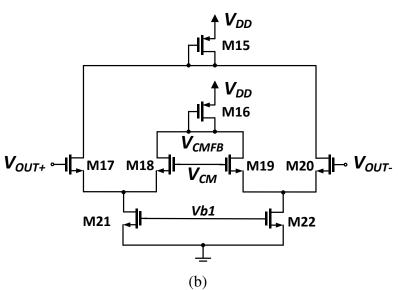

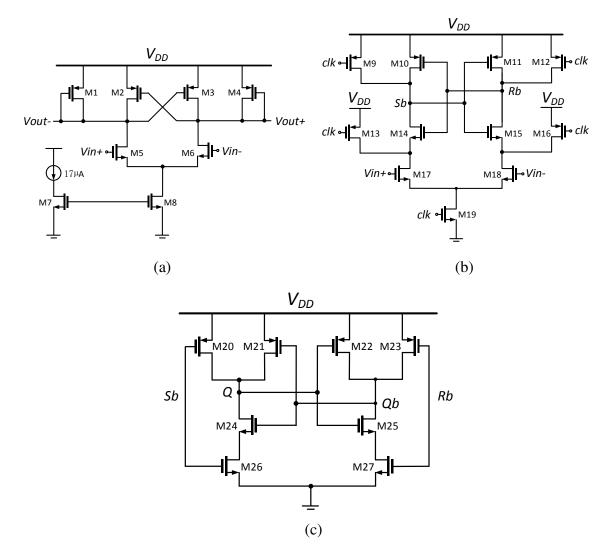

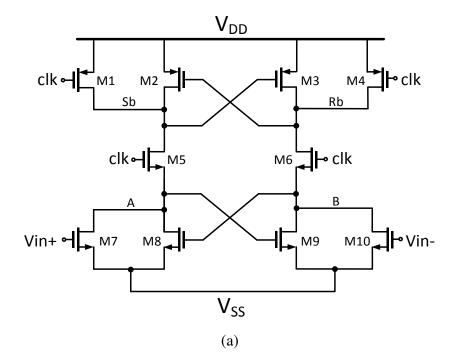

| Figure 3.21: Schematic of the n-booster circuit (a) main circuit branch (b) CMFB circuit.              |

| Figure 3.22: Schematic of the p-booster circuit (a) main circuit branch (b) CMFB circuit.              |

|                                                                                                        |

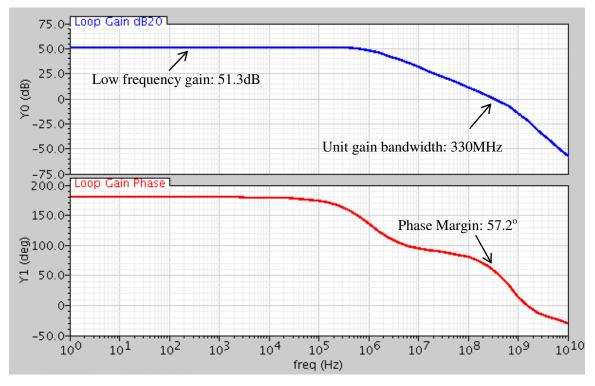

| Figure 3.23: Stability analysis result for the n-booster                                               |

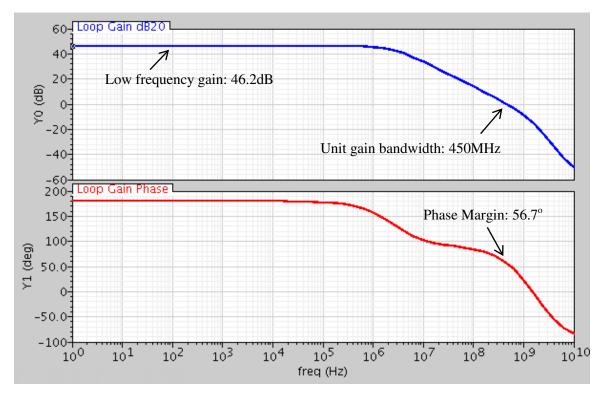

| Figure 3.24: Stability analysis result for the p-booster                                               |

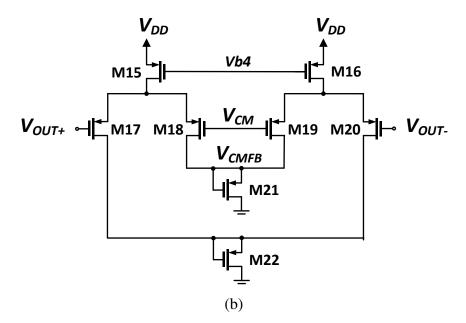

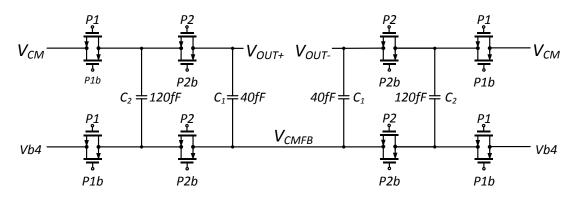

| Figure 3.25: Schematic of the switched-capacitor CMFB circuit                                          |

| Figure 3.26: Transient response of the CMFB circuit with a 100mV common mode input                  |

|-----------------------------------------------------------------------------------------------------|

| step disturbance76                                                                                  |

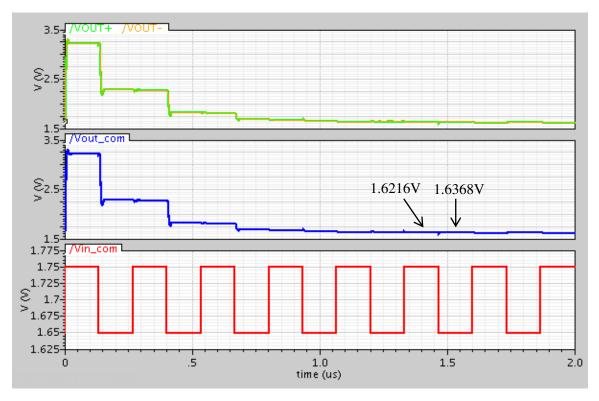

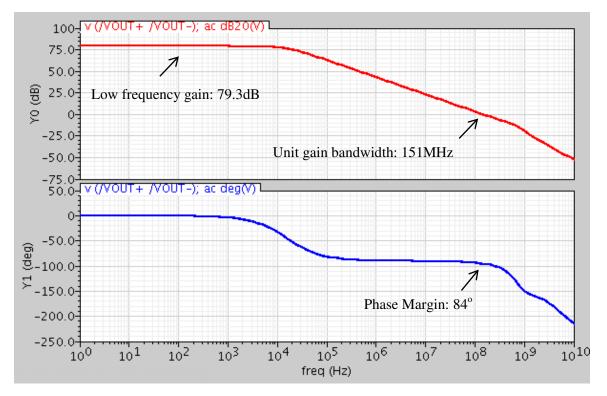

| Figure 3.27: Amplitude and phase response of the folded cascode op-amp                              |

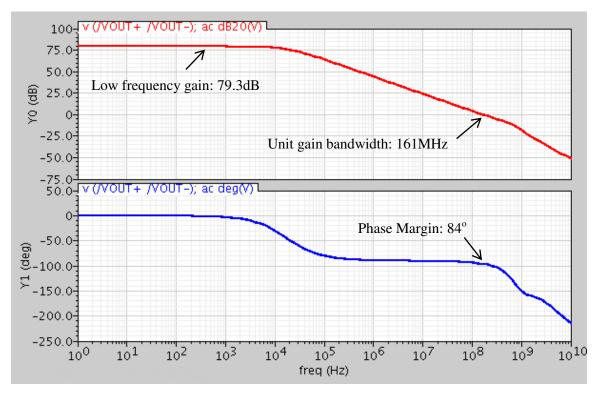

| Figure 3.28: Layout of the designed folded cascade op-amp. The total area used is 293µm             |

| × 152µm                                                                                             |

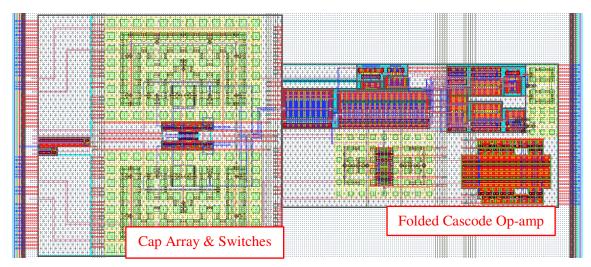

| Figure 3.29: Layout of the designed SC filter. The total area used is 606 $\mu$ m × 260 $\mu$ m. 78 |

| Figure 3.30: Schematic of (a) the preamplifier used in the comparator, (b) the strong-arm           |

| latched decider, (c) the conventional SR latch                                                      |

| Figure 3.31: Simulated transient response for the Miller plateau detection at the output of         |

| the comparator                                                                                      |

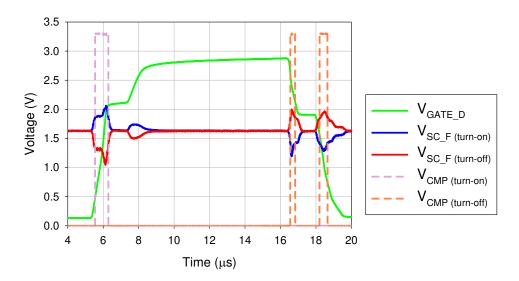

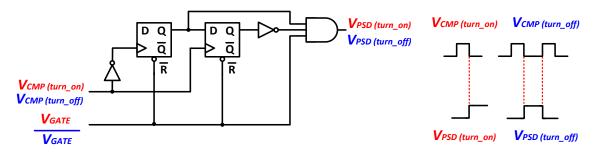

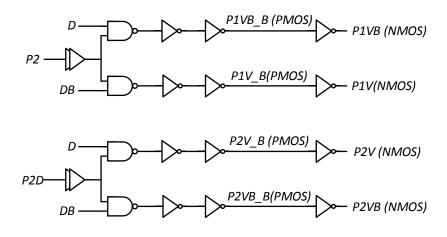

| Figure 3.32: Simple logic circuit for turn-on and turn-off plateau start detection                  |

| Figure 3.33: Circuit implementation for the fixed pulse width modulation                            |

| Figure 3.34: Simulated transient response for the Miller plateau detection at the output of         |

| the fixed time integration block                                                                    |

| Figure 3.35: Layout of the fixed time integration block. The total area used is 285 $\mu$ m ×       |

| 80 μm                                                                                               |

| Figure 3.36: Schematic of the SC integrator                                                         |

| Figure 3.37: AC simulation results for the op-amp in the SC integrator                              |

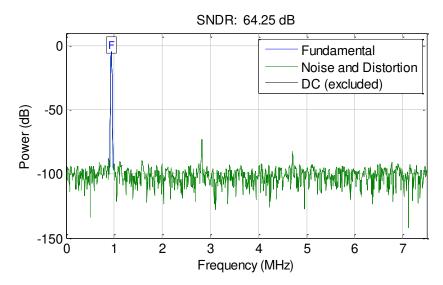

| Figure 3.38: Simulated FFT plot for the SC integrator showing the SNDR performance                  |

| for turn-on                                                                                         |

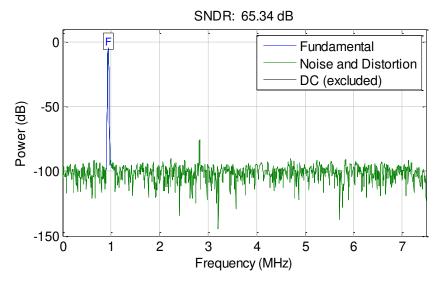

| Figure 3.39: Simulated FFT plot for the SC integrator showing the SNDR performance                  |

| for turn-off                                                                                        |

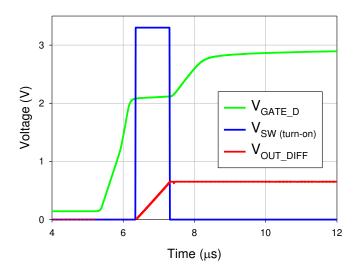

| Figure 3.40: Simulated $V_{OUT_DIFF}$ waveform. This voltage is an analog representation of                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| the collector current                                                                                                                                                 |

| Figure 3.41: Synchronization for the SC integrator triggering clocks                                                                                                  |

| Figure 3.42: Layout of the designed SC integrator block. The total area used is 725 $\mu$ m × 247 $\mu$ m                                                             |

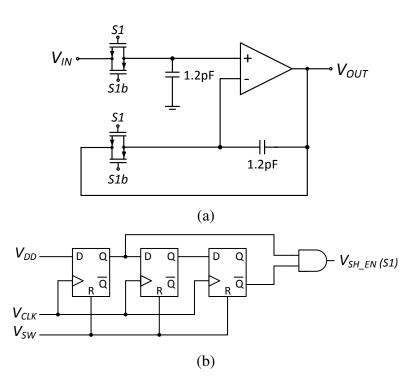

| Figure 3.43: (a) Sample-and-hold schematic (b) Logic for the sample-and-hold triggering signal                                                                        |

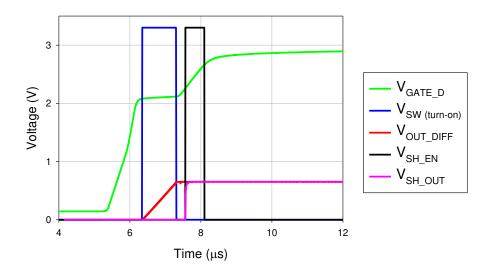

| Figure 3.44: Transient simulation shows the sample-and-hold enable signal ( $V_{SH\_EN}$ ) and output waveform ( $V_{SH\_OUT}$ ) in the $I_C$ current sensing circuit |

| Figure 3.45: Transient simulation shows the functionality of the sample-and-hold circuit.                                                                             |

| Figure 3.46: Layout of the designed sample-and-hold block. The total area used is 285 $\mu$ m × 240 $\mu$ m                                                           |

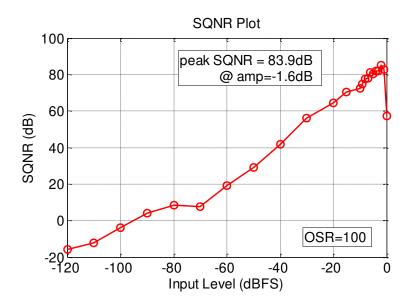

| Figure 3.47: Simulated SQNR of MOD2 with OSR=100                                                                                                                      |

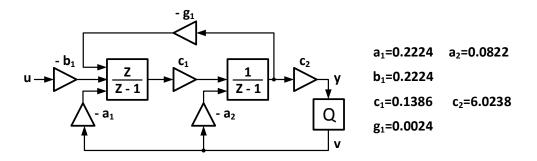

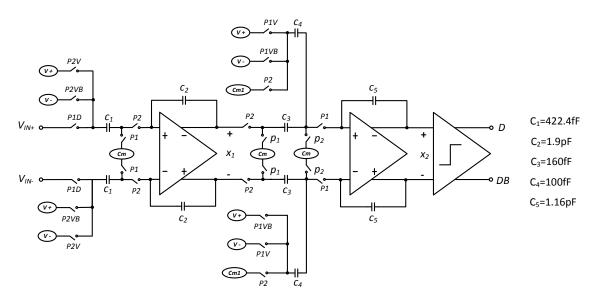

| Figure 3.48: Designed MOD2 $\Delta\Sigma$ ADC modulator                                                                                                               |

| Figure 3.49: The output power spectral density with ideal MATLAB modeling                                                                                             |

| Figure 3.50: Circuit diagram of the MOD2 DSM95                                                                                                                        |

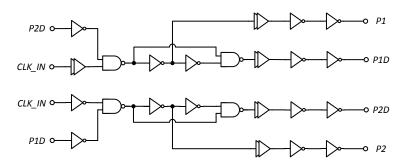

| Figure 3.51: Schematic of the non-overlapping clock generator                                                                                                         |

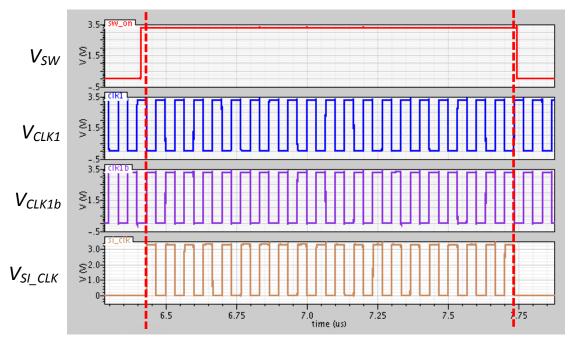

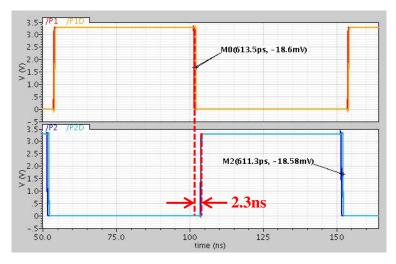

| Figure 3.52: Transient simulation results of the clock generator in the $\Delta\Sigma$ ADC                                                                            |

| Figure 3.53: Schematic of the (a) fully differential dynamic latched decider (b) SR latch.                                                                            |

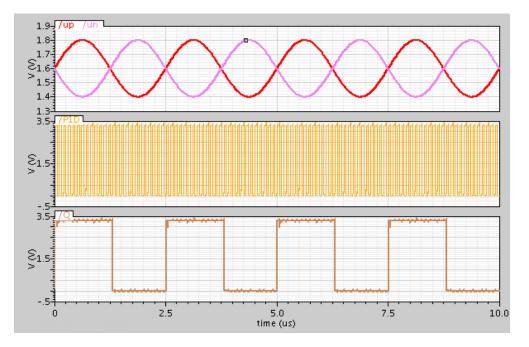

| Figure 3.54: Functionality simulation for the comparator in DSM. From top to bottom:                                                                                  |

| two input signals, latch clock, comparator final output100                                                                                                            |

| Figure 3.55: Schematic for the DAC 100                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

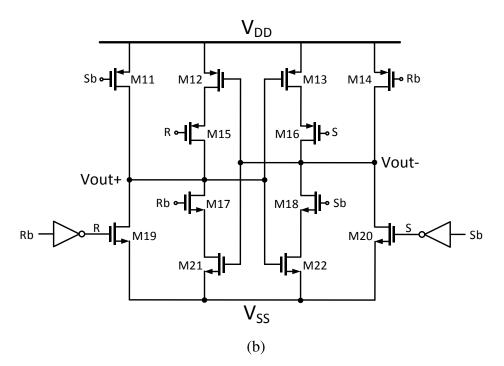

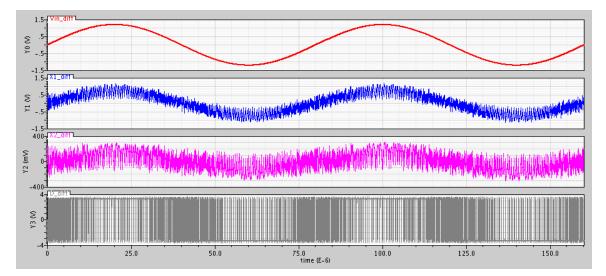

| Figure 3.56: Transient simulation results of the DSM block. From top to bottom: 12.5 kHz input sine wave, first SC integrator stage output (×1), second DC integrator stage output (×2), DSM final 1-bit output |

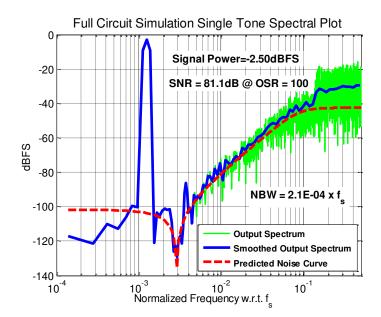

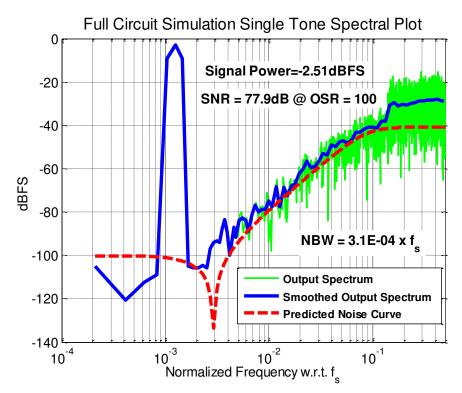

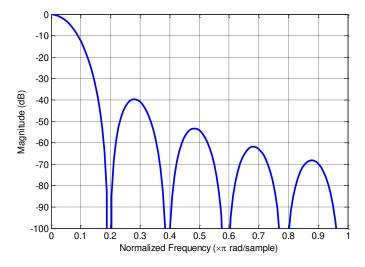

| Figure 3.57: Final SNDR simulation results with -2.5dBFS and 12.5 kHz input 102                                                                                                                                 |

| Figure 3.58: Layout for the DSM block. The total area used is 722 $\mu$ m × 490 $\mu$ m 102                                                                                                                     |

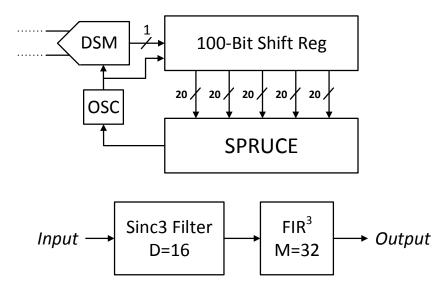

| Figure 3.59: The interface between the DSM and SPRUCE (upper) the architecture of the digital filter implemented by SPRUCE (lower)                                                                              |

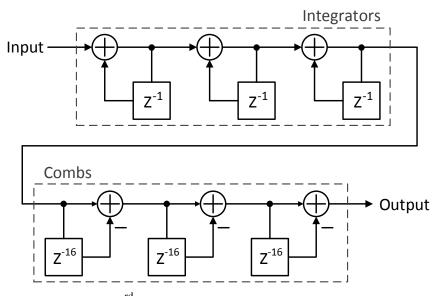

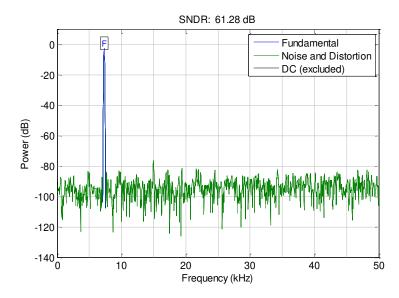

| Figure 3.60: The 3 <sup>rd</sup> order CIC (Cascaded Integrator-Comb) filter                                                                                                                                    |

| Figure 3.61: Frequency response of the 3 <sup>rd</sup> order CIC filter with D=16 104                                                                                                                           |

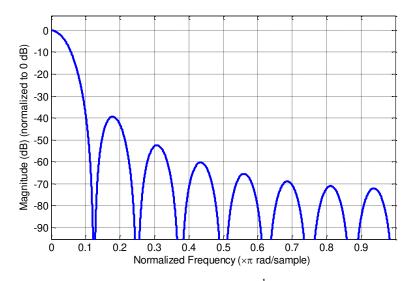

| Figure 3.62: Frequency response of the 3-stage moving average filter 105                                                                                                                                        |

| Figure 3.63: Final simulated SNDR plot after the decimation filter based on 4096 ADC output results                                                                                                             |

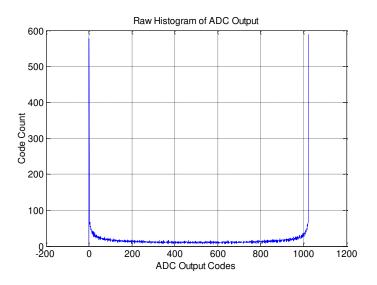

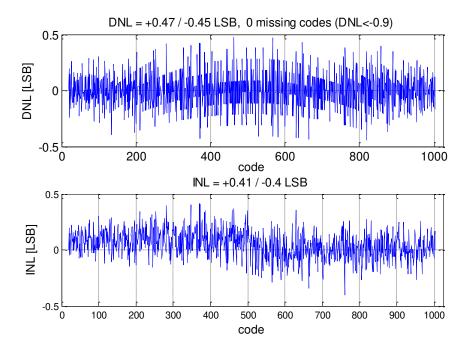

| Figure 3.64: Histogram for the ADC linearity test 106                                                                                                                                                           |

| Figure 3.65: Simulated static linearity of the $\Delta\Sigma$ ADC                                                                                                                                               |

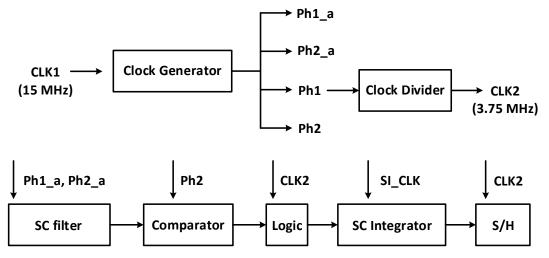

| Figure 3.66: System clock tree for the $I_C$ sensing circuit part                                                                                                                                               |

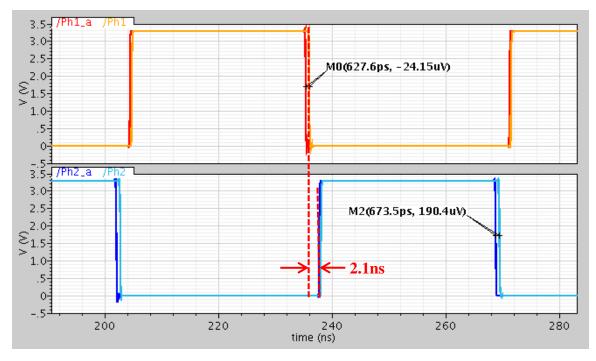

| Figure 3.67: Transient simulation results of the system clock generator 109                                                                                                                                     |

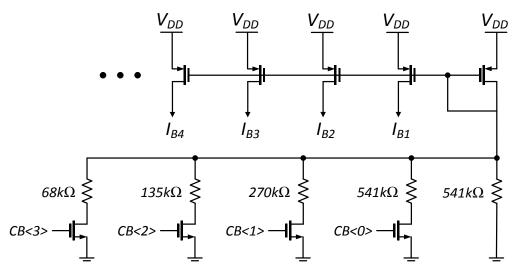

| Figure 3.68: The configurable bias current generator for the $I_C$ sensing circuit [88] 110                                                                                                                     |

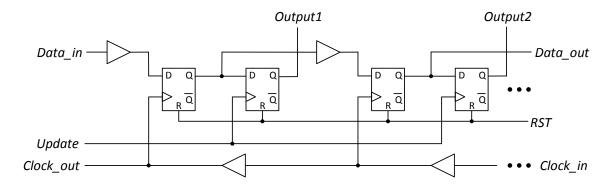

| Figure 3.69: Shift registers used for the configuration bits                                                                                                                                                    |

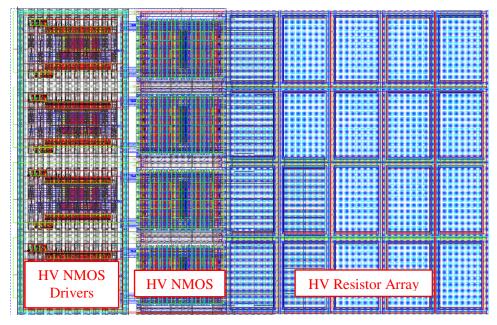

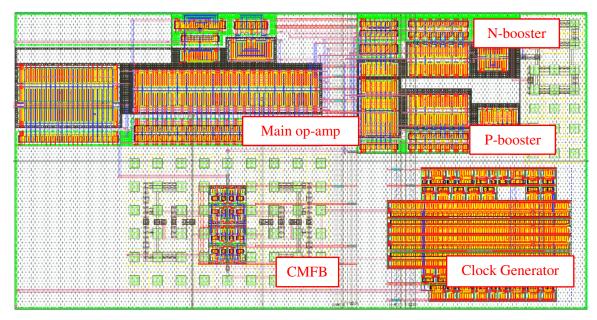

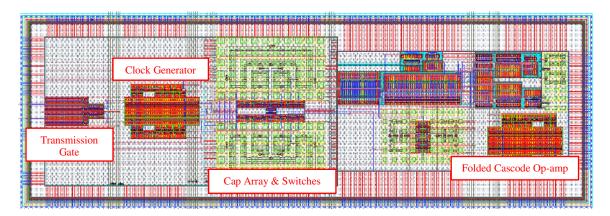

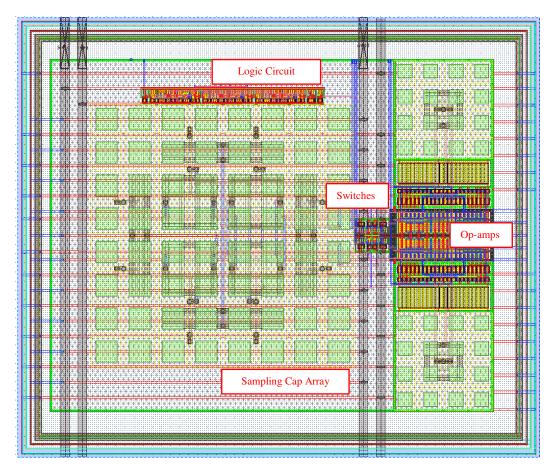

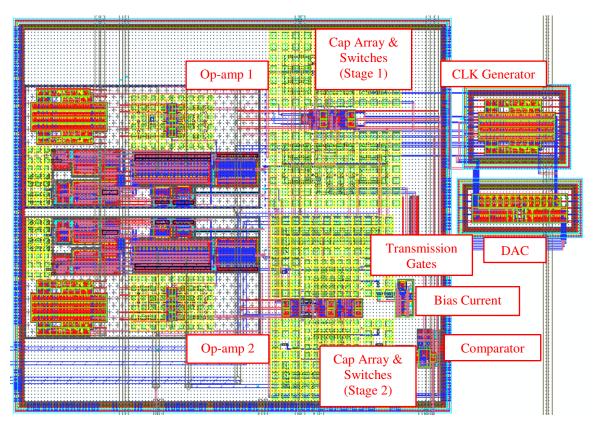

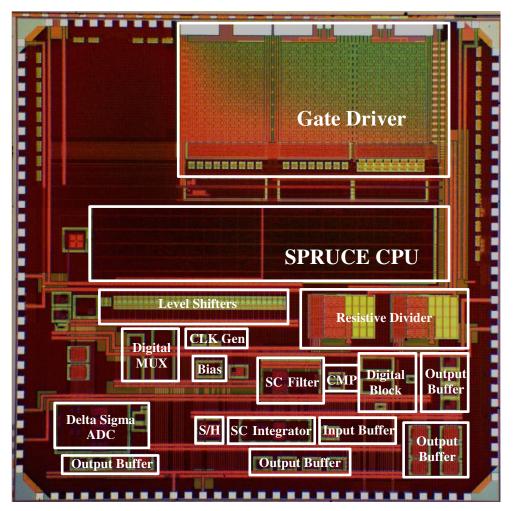

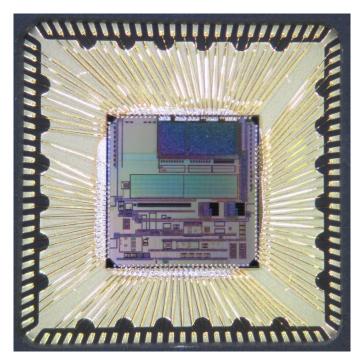

| Figure 3.70: Micrograph of the gate driver IC, fabricated using TSMC's 0.18 $\mu$ m BCD Gen-2 process (chip area 5 mm × 5 mm)                                                                                   |

| Figure 3.71: Bonding diagram of the gate driver IC chip in QFN 100 113                                                                                                                                          |

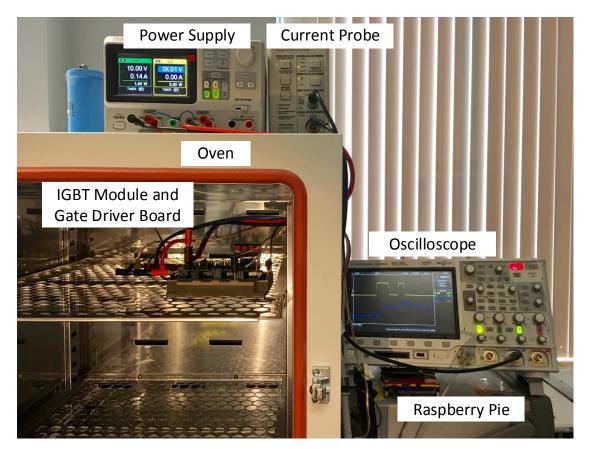

| Figure 4.1: Experimental test setup for the gate driver IC with real time collector current                   |

|---------------------------------------------------------------------------------------------------------------|

| display 115                                                                                                   |

| Figure 4.2: The proposed gate driver IC is intended to be incorporated into IPMs 115                          |

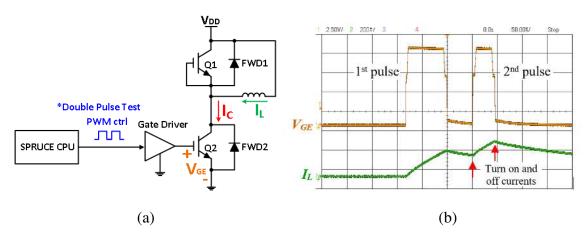

| Figure 4.3: (a) The double pulse test bench schematic, (b) Measured waveforms for $V_{GE}$                    |

| and $I_L$ during the double pulse test [ $V_{GE}$ : 2.5V/div, $I_C$ : 2A/div]                                 |

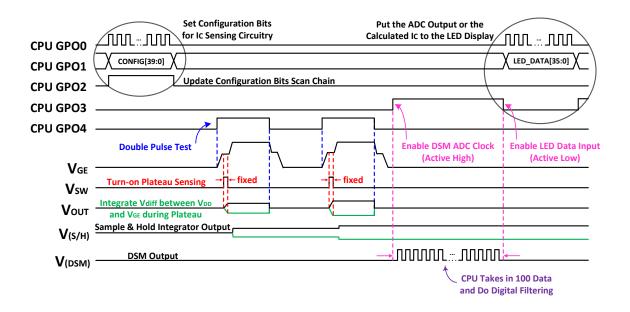

| Figure 4.4: Timing diagram for the sensing of $I_C$ during turn-on                                            |

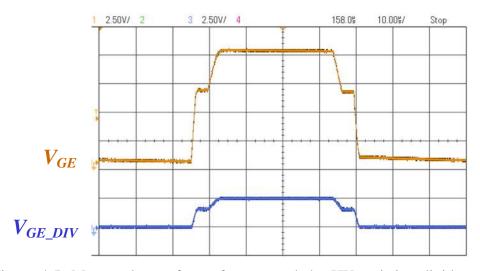

| Figure 4.5: Measured waveforms for $V_{GE}$ and the HV resistive divider output $V_{GE_DIV}$                  |

| [ <i>V<sub>GE</sub></i> : 2.5 V/div, V <sub><i>GE_DIV</i></sub> : 2.5 V/div]                                  |

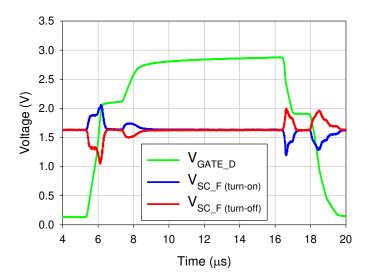

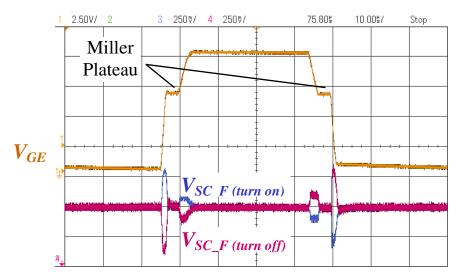

| Figure 4.6: Measured waveforms for $V_{GE}$ and the SC filter output $V_{SC_F}$ [ $V_{GE}$ : 2.5 V/div,       |

| V <sub>SC_F</sub> : 0.25 V/div]                                                                               |

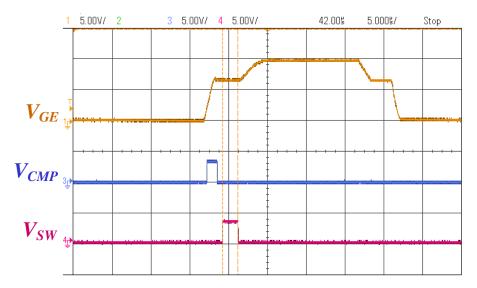

| Figure 4.7: Waveforms for $V_{GE}$ , the comparator output, $V_{CMP}$ and the logic output, $V_{SW}$ for      |

| turn-on transient [ $V_{GE}$ : 5 V/div, $V_{CMP}$ : 5 V/div, $V_{SW}$ : 5 V/div]                              |

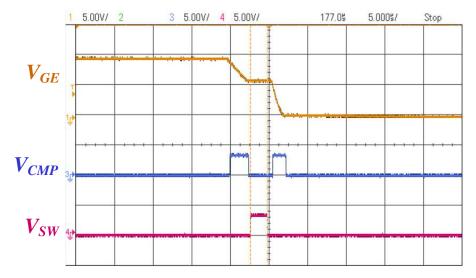

| Figure 4.8: Waveforms for $V_{GE}$ , the comparator output, $V_{CMP}$ and the logic output, $V_{SW}$ for      |

| turn-off transient [ $V_{GE}$ : 5 V/div, $V_{CMP}$ : 5 V/div, $V_{SW}$ : 5 V/div]                             |

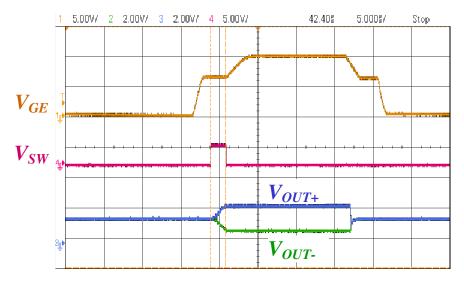

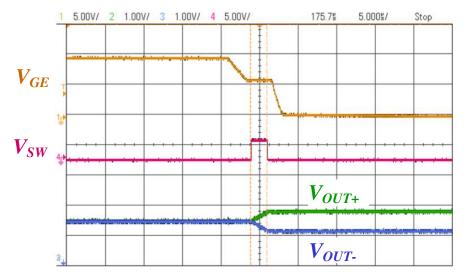

| Figure 4.9: Waveforms for $V_{GE}$ , $V_{SW}$ and SC integrator outputs, $V_{OUT+}$ and $V_{OUT-}$ for turn-  |

| on transient [ $V_{GE}$ : 5 V/div, $V_{SW}$ : 5 V/div, $V_{OUT+}$ and $V_{OUT-}$ : 2 V/div]                   |

| Figure 4.10: Waveforms for $V_{GE}$ , $V_{SW}$ and SC integrator outputs, $V_{OUT+}$ and $V_{OUT-}$ for turn- |

| off transient [ $V_{GE}$ : 5 V/div, $V_{SW}$ : 5 V/div, $V_{OUT+}$ and $V_{OUT-}$ : 2 V/div]                  |

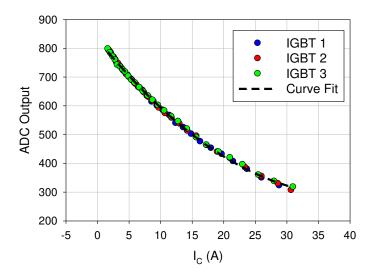

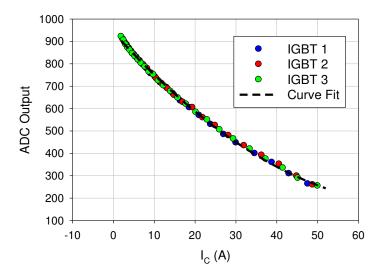

| Figure 4.11: ADC output vs. $I_C$ for three different IGBTs during turn-on at room                            |

| temperature                                                                                                   |

| Figure 4.12: ADC output vs. $I_C$ for three different IGBTs during turn-off at room                           |

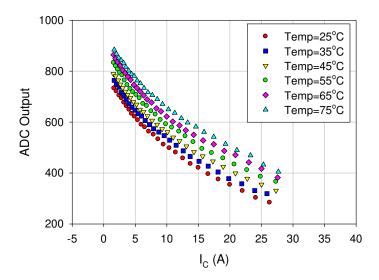

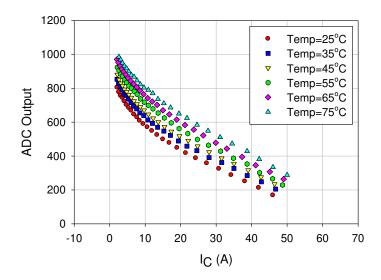

| temperature                                                                                                   |

| Figure 4.13: Deviation of the displayed $I_C$ to the probed $I_C$                                             |

| Figure 4.14: Experimental test setup for the gate driver IC in the oven                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

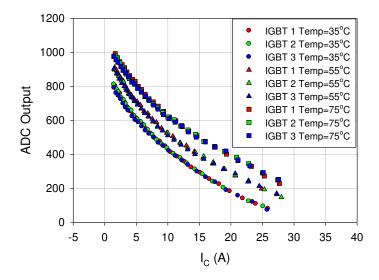

| Figure 4.15: Measured ADC output vs. <i>I<sub>C</sub></i> at different ambient temperatures during turn-<br>on                                                                  |

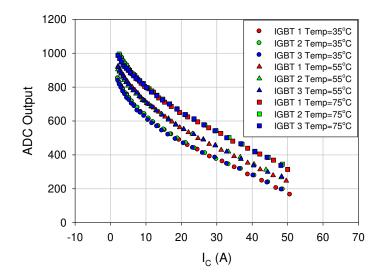

| Figure 4.16: Measured ADC output vs. <i>I<sub>C</sub></i> at different ambient temperatures during turn-<br>off                                                                 |

| Figure 4.17: Measured ADC output vs. $I_C$ at different ambient temperatures during turn-<br>on for three different IGBTs                                                       |

| Figure 4.18: Measured ADC output vs. $I_C$ at different ambient temperatures during turn-<br>off for three different IGBTs                                                      |

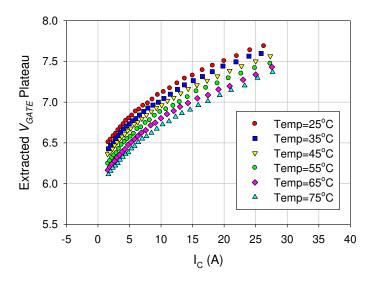

| Figure 4.19: The extracted gate plateau voltage vs. $I_C$ at different ambient temperatures during turn-on                                                                      |

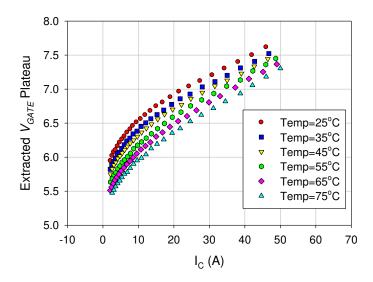

| Figure 4.20: The extracted gate plateau voltage vs. $I_C$ at different ambient temperatures during turn-off                                                                     |

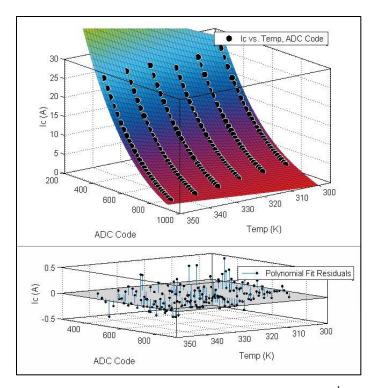

| Figure 4.21: <i>Ic</i> vs. ADC output codes and temperature, and the 3 <sup>rd</sup> order polynomial fit (Top). The polynomial fit residues plot (Bottom). (For IGBT Turn-on)  |

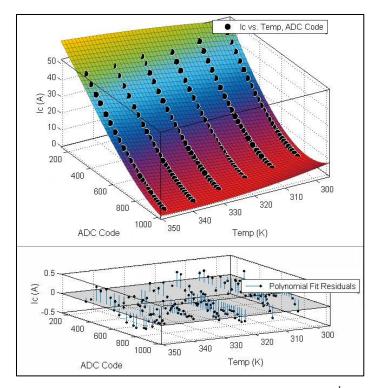

| Figure 4.22: <i>Ic</i> vs. ADC output codes and temperature, and the 3 <sup>rd</sup> order polynomial fit (Top). The polynomial fit residues plot (Bottom). (For IGBT Turn-off) |

| Figure A: Complete memory map for the SPRUCE CPU in the gate driver IC144                                                                                                       |

### List of Glossary

IGBT: Insulated Gate Bipolar Transistor IPM: Intelligent Power Module Freewheeling Diode FWD: Surface Mounted Device SMD: EMI: Electro Magnetic Interference Analog to Digital Converter ADC: DAC: Digital to Analog Converter DSM: Delta Sigma Modulator CMFB: Common Mode Feedback SNDR: Signal to Noise and Distortion Ratio S/H: Sample and Hold SC: Switched Capacitor PCB: Printed Circuit Board LDO: Low Dropout Regulators Cascaded Integrator-Comb CIC: IoT: Internet of Things AI: Artificial Intelligence

# Chapter 1

# Introduction

Power semiconductor switches are essential components in all modern power electronic systems which determine the performance, efficiency, size, and the cost of the electronic systems. Recently, wide bandgap power devices have attracted significant attentions due to their superior device characteristics. However, these devices are still in early generations of development and they are intended to replace Si devices in very high voltage, high frequency and high power applications. Therefore, Si based power MOSFETs and Insulated Gate Bipolar Transistors (IGBTs) remain dominant in the landscape from low to medium power conversion applications. As the silicon device technology evolves to a highly mature state, their performance is already approaching the physical limits. In order to further exploit silicon power devices, much effort has been put into the design of smart gate driver ICs to optimize the overall system performance. In the past decades, various gate drive circuits have been proposed and discussed, with more and more functions incorporated into the gate driver to make them 'smart'.

Meanwhile, precision current measurement is a critical function that must be incorporated into modern high voltage and high current power systems. Accurate measurement of current flow in power switches such as power MOSFETs and IGBTS is necessary for output regulation and for safety purposes. However, conventional current sensing methods for power switches using resistive sensors consume more power, increase discrete components count and involve accessing the high voltage load side; posing difficulties for integration into gate driver ICs. This thesis focuses on developing a new collector current sensing method for IGBTs and integrating this technique into a smart gate driver IC. In Chapter 1, a brief introduction to IGBTs, smart gate ICs and conventional IGBT collector current sensing methods is provided. This is followed by an overview of the research work. Chapter 2 introduces the proposed collector current sensing method for IGBTs. A discrete implementation which demonstrates the ideal is also presented. Chapter 3 describes the gate driver IC design details with the integrated current sensor. Chapter 4 discusses the experimental setup and measurements results. Conclusions and suggestions for future work are given in Chapter 5.

In this introductory chapter, the fundamentals on IGBT device structures and applications are reviewed in Section 1.1. The design trend in smart gate driver ICs for IGBTs is analyzed in Section 1.2. The conventional collector current sensing methods for IGBTs and their disadvantages are presented in Section 1.3. An overview of the research work conducted in this thesis are summarised in Section 1.4.

## 1.1. IGBT Devices and Applications

IGBT is widely used in a variety of power switching applications due to its superior electrical characteristics. It is basically a merged MOSFET-bipolar power transistor, synergizing the high-input impedance MOS-gate control with high bipolar current conduction. The size and complexity of the controlling circuitry is reduced compared to the power bipolar transistors, hence the overall system size and cost are reduced as well [1, 2].

#### 1.1.1. IGBT Device Structures

Ever since the IGBT concept was discovered and developed in the early 1980s, breakthrough technical innovations for IGBT structural optimization have been achieved over the past decades. Basic IGBT structures are derived from replacing the n+ drain with a p+ layer at the bottom of a vertical power MOSFET. This p+ layer is called the injection layer which injects holes into the n-drift base region; adding one more

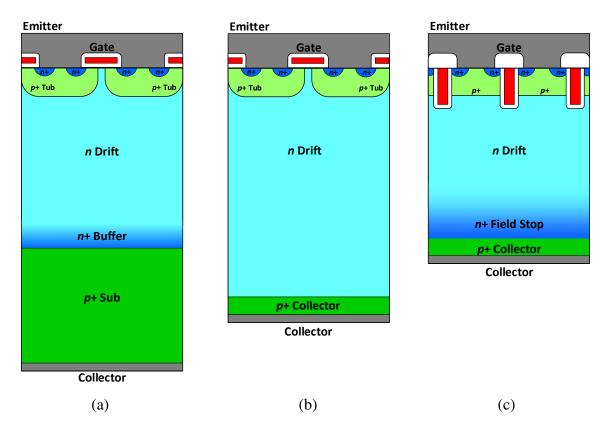

conducting carrier to increase the device current drive capability. Early generations of IGBTs feature planar gate and Punch-Through (PT) type bulk structure, as illustrated in Figure 1.1(a). The PT-IGBT is fabricated by growing the *n*-epitaxial drift layer on a highly-doped p+ substrates. This design provides strong hole injection from the collector into the drift region to achieve high conductivity and hence low on-state voltage drop. At the same time, the carrier life time control becomes necessary as the injected minority carriers in the drift region should be removed quickly when device needs to be turned off. However, device performance would be limited in this case since it is hard to optimize carrier profile, on-state voltage, and turn-off speed. In addition, PT structure has poor short circuit capability and is unsuitable for parallel operations due to its negative temperature coefficient [3].

Figure 1.1: (a) Conventional Planar Gate and Punch-Through IGBT; (b) Planar Gate and Non-Punch-Through IGBT; (c) Trench Gate and Non-Punch-Through IGBT.

The Non-Punch-Through (NPT) IGBT is developed to solve the aforementioned issues, as shown in Figure 1.1(b). The NPT bulk is fabricated using the float zone wafers instead of epitaxial wafers; which results in less crystal defects. The impurity concentration in the

p+ collector is well controlled in order to suppress the carrier injection volume. As a result, no lifetime control is required; and positive temperature coefficient is achieved, facilitating parallel operations for large current capacity applications [2, 3].

The NPT IGBT also has the advantage of higher withstand capability because of the thick n-drift region. However, there is a trade-off since the thicker n-drift region would reduce the carrier transport efficiency and increase the on-state resistance. The Field Stop (FS) IGBT was introduced to further improve the device characteristics. As shown in Figure 1.1(c), there is an extra high concentration field stop n+ layer inserted at the bottom of the n-drift region. It serves the purpose of stopping the depletion layer, allowing a thinner wafer to be used for the same high breakdown voltage. With the FS technology, it is possible to reduce the n-drift layer thickness of the NPT structure by approximately one third. This translates to less excess carriers and faster switching speed, hence lower switching loss for IGBT at turn-off [3].

Other than the bulk structure evolution, a new gate structure called 'trench gate' has also been developed for IGBTs. As illustrated in Figure 1.1(c), the gate region is formed by etching a trench into the upper surface and locating the gate inside the trench with a liner oxide for isolation from the bulk [4]. When the gate is biased with the proper voltage, a channel is formed along the vertical wall of the trench perpendicular to the surface of the chip. This is different from the conventional planar structure where the channel forms under the gate parallel to the surface of the device. The vertical channel requires less chip area, allows for substantially higher cell density and reduces the on-state voltage drop of the IGBTs [5]. Therefore, FS trench gate structure is widely adopted for modern IGBT designs. Recently more efforts have been carried out to further optimize the trench gate region design, in order to achieve better short circuit ruggedness [6], lower switching loss [7] and better *di/dt* control during IGBT switching transients [8].

#### 1.1.2. IGBT Power Modules

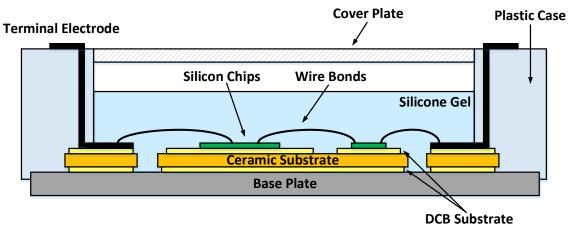

Power Modules were developed to assemble multiple IGBT dies in a single package to provide complex functionality. The modules usually integrate free-wheeling diodes (FWD) and IGBTs to provide single or multi-phase output stages for motor drive or power conversion applications [9]. Basic IGBT power modules usually do not contain control or protection circuitry inside the modules. They are normally driven by external gate drivers or controller boards [10]. The cross-sectional view of a basic IGBT power module is shown in Figure 1.2. The module has a copper baseplate which provides mechanical support for the module. It also absorbs heat during power transients and then transmits the heat to the heat sink. On top of the baseplate, a Direct Bonded Copper (DCB) substrate is attached and the silicon chips (IGBTs and FWDs) are mounted on the DCB substrate using solder, epoxy or other alloying methods. The DCB substrate provides electrical isolation of the silicon chips from the baseplate and heatsink. Therefore, it needs to withstand high temperatures and with low thermal resistance. In addition, the DCB layer should have similar thermal expansion coefficients to that of silicon to ensure good thermal cycling performance. In this case, the most suitable materials for the DCB layer are ceramics such as alumina (Al<sub>2</sub>O<sub>3</sub>), aluminum nitride (AlN), and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) [11, 12].

Figure 1.2: Cross-sectional view of a basic IGBT power module.

After mounting the substrate and silicon chips onto the baseplate, wire bonding is performed to interconnect the chips and connect them to the electrodes of the module. Aluminum wires are usually used with ultrasonic bonding technology [11]. During the IGBT thermal cycling, the bonded interface between the Al wire and the metalized Si chip top experiences repeatedly stress, leading to potential bonding wire damages such as bonding lifting and cracking. These types of damages were reported as the dominant failure modes for modern power modules [13].

For the purpose of providing insulation between the Al wires to prevent electric discharge and also protect the silicon chips from moisture corrosion and contamination, a layer of encapsulation such as silicone gels is used to fill the empty spaces between all the interconnects, devices and insulation layers inside the module [14]. Finally, a plastic case/cover provides protection against any mechanical and environmental abuse [11].

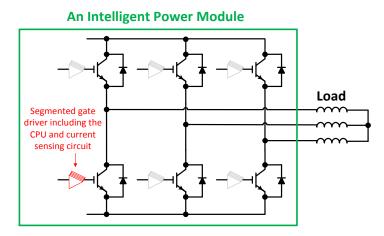

# 1.1.3. Intelligent Power Modules

In order to provide self-protection and load monitoring capability to the IGBTs, the concept of Intelligent Power Module (IPM) was introduced in the late 1980s [15, 16]. IPMs incorporate a dedicated circuit board with control and protection functions to improve their performance and reliability [17, 18].

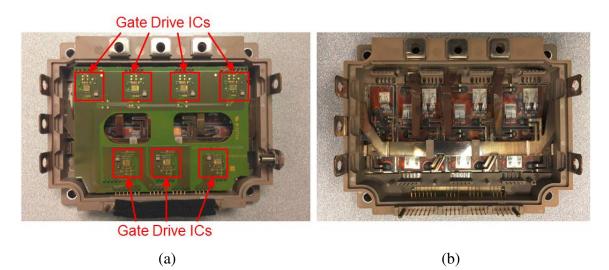

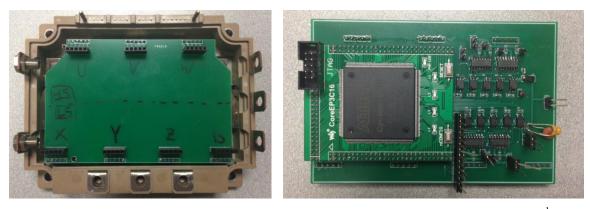

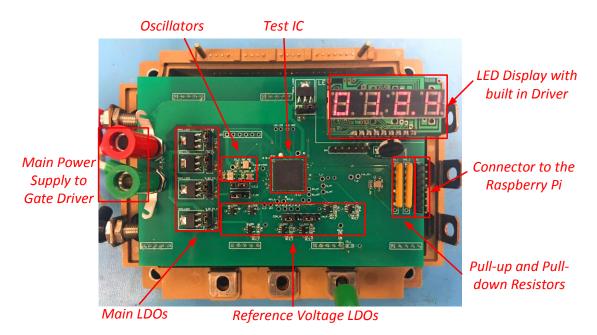

Figure 1.3: A Fuji Electric 7MBP200VEA060-50 IPM module. (a) The driver and control circuit board, (b) the IGBTs and FWDs on the bottom.

Figure 1.3 shows an off-the-shelf Fuji Electric IPM Module 7MBP200VEA060-50. The top circuit board serves as an interface between the microcontroller and the IGBTs. It contains the gate driving ICs and the protection circuits to prevent under-voltage, overcurrent, over-temperature, and short-circuit fault conditions. The bottom of the module are the IGBT and FWD chips with interconnects. The IGBT chips installed in IPMs have different design requirements compared to those discrete IGBT devices. The most significant one is the short circuit withstand time. The discrete IGBTs are typically used in power inverters and are expected to survive a certain time period (usually around  $10\mu$ s) in short circuit operation before the protection circuits are triggered. Special design techniques are needed to ensure adequate saturation current during short circuit condition. However these techniques such as regulating the MOS-channel current would usually compromise the on-state voltage drop in the normal operating condition of the IGBT [10]. While for the IGBTs in IPMs; these techniques are no longer necessary because of the fast short circuit protection scheme (usually 2~3µs).

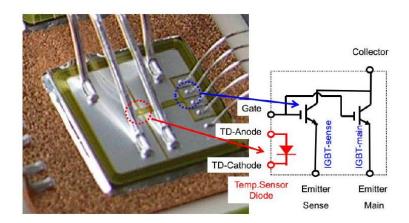

Another important feature of the IGBTs designed for IPMs is the integration of on-chip current and temperature sensor, as illustrated in Figure 1.4. The Sense-FET structure directs a small portion of the total collector current for over current protection. The details of this current sensing method will be discussed in a later section. A simple *pn* diode is placed in the center of the chip to monitor the junction temperature of the IGBT chips [10].

Figure 1.4: Photo and simplified schematic of an IGBT chip for IPMs with on chip current and temperature sensors [10].

The development of IPMs greatly reduces the time-to-market for the products and offers customers with advantages of reduced design efforts, lower manufacturing costs, and also improved system performance and reliability [15]. IPMs are now widely used in many electronic applications.

#### 1.1.4. IGBT Applications

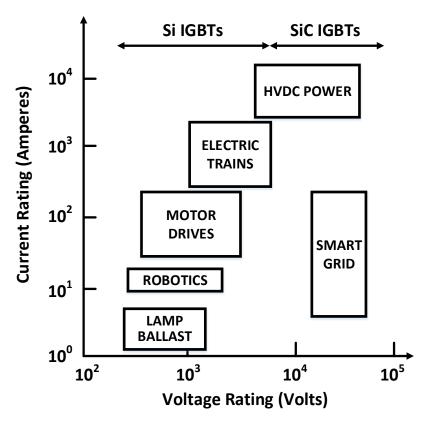

IGBTs have found widespread applications in medium to high power systems. Figure 1.5 illustrates the application spectrum for modern IGBTs. Their characteristics are suitable for applications with operating conditions of 200V and above, e.g. lamp ballasts, consumer appliances, and motor drives, etc. Compared to traditional Si-based IGBTs, SiC IGBTs offer promising characteristics with higher blocking voltages, higher switching frequencies and better thermal reliability. However, due to the lower wafer yield and higher cost, Si IGBTs are still the dominant power devices except for special applications such as smart grid which requires extremely high blocking voltages [1]. The IGBTs discussed in this thesis are limited to Si-based IGBTs.

Figure 1.5: Application spectrum for IGBTs [1].

IGBTs play an important role in the modern transportation sector. They are the most costeffective choice for the switches in power electronic systems. More significantly, the IGBT-based inverters are used in electric and hybrid electric vehicles such as electric buses, trains, electric trams and trolleys, and subways. The development of IGBT has a great impact on the industrial sector as well. IGBTs are the dominant power switches used in industrial motor drives. For all these applications, IGBTs offer many technical advantages when compared to other power switches including lower component count and power rating for the driver circuit, lower switching loss and steady state on-state loss, better short circuit withstand capability, better performance under parallel configurations and feasibility of higher blocking voltages [19, 20].

IGBTs are also widely used in many modern lighting systems. They enabled the introduction of the Compact Fluorescent Lamp (CFL) because of their high power handling capability and monolithic gate driver which makes the control system more compact. Other applications of IGBTs for lighting include LED drivers, dimmable luminaries and flash tubes used in digital still cameras [21].

In addition to above mentioned applications, IGBTs are extensively used for the control of power delivery in major home appliances used by consumers. These major appliances include air conditioning, heat pump unit, kitchen cooking range, washing machines, microwave, and refrigerator [22]. IGBTs also found numerous applications in the medical sector now as they have taken a critical role in the power delivery for major medical diagnostic tools such as CT scanners, MRI imagers, ultrasound machines, and medical lasers [23].

#### 1.2. Trends in Smart Gate Driver ICs for IGBTs

#### 1.2.1. Gate Drivers for IGBTs

Gate drivers for power semiconductor switches are crucial components in power systems. Investigations on the gate drive circuits for silicon power switches started as early as the devices were introduced [24]. The basic gate drive circuit for IGBT is simple because of its MOS-gate structure. The device can be controlled using relatively low voltage (typically 10-15V), and only transient currents are required to charge and discharge the

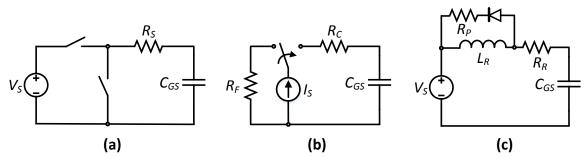

MOS-gate which can be delivered using integrated circuits [24]. Common gate driver topology can be categorized into three groups: voltage source gate driver, current source gate driver and resonant source gate driver [25]. Simplified circuits describing these topologies during the charging and discharging intervals are shown in Figure 1.6.

Figure 1.6: Simplified circuit for (a) voltage source, (b) current source and (c) resonant gate driver topologies during charging and discharging intervals [25].

Voltage source topology is the most popular gate driver topology due to its simplicity. This type of driver operates by charging and discharging the input gate capacitance of the IGBT ( $C_{GS}$ ) with a voltage source through a series resistance  $R_G$ .  $R_G$  is a critical factor for switching speed control. It is normally chosen based on the value of  $C_{GS}$  to make sure that the charging interval is less than 5% of the entire switching period of the IGBT. Larger  $R_G$  would inevitably limit the switching speed. However, it would not increase the power consumption of the gate driver. The energy dissipated in  $R_G$  during charging process is always equal to the energy stored in  $C_{GS}$ , which is given by [25]:

$$E_{v} = \frac{1}{2}C_{GS}V_{S}^{2}$$

(1.1)

Considering the same holds true for the discharging process, the power consumed in  $R_G$  for a switching frequency of  $f_s$  for the IGBT can be calculated as [26]:

$$P_{\nu} = f_S C_{GS} V_S^2 \tag{1.2}$$

Equation (1.2) implies that at higher switching frequency, the gate driver power consumption will become significant enough to affect the efficiency of the system. Therefore, current source gate driver topology as shown in Figure 1.6 (b) is introduced.

These gate drivers operate by charging the gate capacitance with a constant current source, and the charging time is inversely proportional to the charge current  $I_S$ . It can be demonstrated that the current source driven gate driver consumes less power than the voltage source gate driver with proper choice of the passive components [25]. However, this type of topology is less commonly used as it requires a high efficiency current source which is more difficult to design. In practical terms, a small inductor is usually implemented as part of the current source. This approach ventures into the resonant driver domain [26].

Figure 1.6(c) presents a simple resonance driven gate driver which is the most popular topology used in high frequency switching applications. In this type of driver, the resonant current charges and discharges the gate capacitance through the resonant inductor. There are two operation modes: full resonance and clamped resonance. Under full resonance condition, the inductor transfers all the energy to the gate capacitance. The turn-on time and the final gate voltage value are determined by the Q-factor. While under clamped resonance condition, the gate voltage will be clamped at a given voltage, the remaining energy in the inductor is then diverted [25]. All the commonly used resonance gate driver circuits are discussed with their advantages and limitations in [27].

In this research work, the IGBT devices under investigation are switching around 20 kHz only. Resonance type gate drivers require inductors which is not desirable for space and cost saving in integrated circuit design. Therefore, the voltage source topology is adopted for this thesis.

#### 1.2.2. Smart Gate Drivers

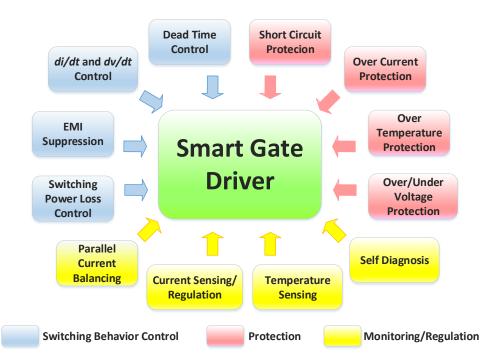

In the past decades, various gate drive circuits have been proposed and discussed, with more and more functions incorporated into the gate driver to make them 'smart'. These driving techniques and smart functions can be broadly divided into three categories, as shown in Figure 1.7.

The techniques in the first category are mainly used to optimize the switching behavior of the power devices. For example, active gate driving has been discussed extensively in literature [28-33], focusing on the turn-on /turn-off voltage and current waveform shaping for the power devices. The ultimate goal is to ensure acceptable compromise between switching speed, switching power loss and electromagnetic interferences (EMI). These are the most important design aspects for smart switching designs. Adaptive driving is an example of such system where closed-loop analog control is used to adjust the dv/dt and di/dt characteristics [28-30]. This control technique usually features simple circuit design, high dynamic speed and low power consumption. However, the analog control strategy and analog circuit necessitate major re-design effort for different devices, operating conditions and processing technologies. Another popular trend is to employ intelligent digital control to achieve adaptive slope shaping [31-33]. These types of gate drivers have the key advantage of high flexibility in driving strategies and high configurability for various design parameters such as gate resistance, gate current and drive stages. Some works also combine analog feedback and digital control to achieve intelligent switching [34, 35].

Figure 1.7: Developed features of modern smart gate drivers for power MOSFETs and IGBTs.

In the second category, there are various protection circuits for the power switches, including short circuit protection, over current protection, over temperature protection,

and over/under voltage protection. All of these are compulsory features for device reliability and safe operation. These functions have been well developed in the past decades [36]. Recent effort is to focus on how to make the protection schemes more robust and with faster reaction time [37].

The techniques in the third category are more for monitoring and regulation, such as temperature sensing [38], current sensing [39], current regulation and current balancing in parallel connected topology [40], and self-diagnosis for fault detection [41]. These are popular new features in smart gate drivers to improve functionality, flexibility and reliability.

#### 1.2.3. Integrated Smart Gate Drivers

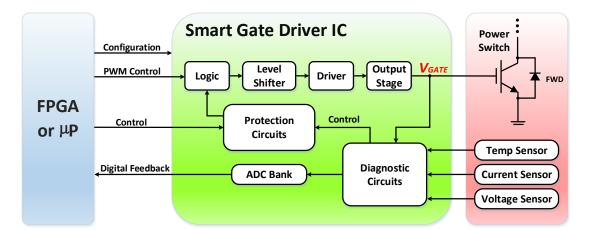

Modern smart gate drivers integrate all the components into a single package, resulting in a significantly smaller system size and enhanced reliability. The smart gate-driver ICs also simplify the PCB board layout and reduce design uncertainty. Some of the smart functions mentioned in Section 1.2.2 were initially implemented using discrete components and then gradually integrated into the gate driver IC. A generalized block diagram for recent smart gate driver ICs is shown in Figure 1.8.

Figure 1.8: Functional block diagram of a generalized smart gate driver IC.

Modern smart gate driver ICs usually rely on an external FPGA or a microprocessor to provide digital control, such as setting all the configurable parameters for the chip and PWM (Pulse Width Modulation) control for the driver. Recently, numerous gate drivers

ICs with digital controlled adaptive driving features were developed. One example is the segmented and programmable gate drivers [42-44]. Segmented drivers are composed of several paralleled output stages to achieve variable output resistance. In order to achieve fast switching speed, a lower gate resistance is needed for large *di/dt* and *dv/dt* but this results in higher EMI. A larger gate resistance could reduce EMI but increase the switching loss, leading to lower efficiency. The digitally controlled segmented gate driver could dynamically change the gate driver output resistance to suppress the EMI while maintaining similar switching speed and switching loss. Furthermore, multiple changes in the gate resistance during a single turn-on or turn-off transient are possible by appropriately changing the number of active segments in real time. An algorithm was developed in [45] to optimize the segmentation process according to the load current, the operating voltage, the temperature, and other variations in power devices.

Smart gate driver ICs could also process the feedback signals from sensors on the power switches or the load. These signals can be used to trigger certain protection circuits directly. In most designs, the processed signals are digitized by an ADC and fed back to an FPGA or microprocessor. After further processing, the FPGA or microprocessor will trigger the protection circuits or dynamically adjust the driving control signals to realize local regulation. A gate driver IC with integrated short circuit protection function based on a filtered feedback signal is introduced in [46]. A smart driver IC for inductive loads with self-monitoring capability by using the signals from a resistive sensor on the load side is presented [47]. Finally, the concept of integrating the *di/dt* and *dv/dt* analog feedback into the gate driver IC is described in [35]. This fully integrated closed-loop gate driver could provide digital slope shaping based on the analog feedback signals.

Recently, techniques that utilize the gate signal (gate voltage or gate current) to detect short circuit condition [48-50], to predict device junction temperature [51], to regulate the imbalance of currents in paralleled IGBTs [52] have been proposed. These types of techniques only use the low voltage signal on the gate driver, ensuring the feasibility of low cost integration. As illustrated in Figure 1.8, the diagnostic circuit could process the gate signal directly instead of monitoring the feedback signals from the high voltage load side which poses significant voltage isolation difficulties in monolithic integration.

#### 1.2.4. BCD Process Technology

Whether a certain feature should be integrated is not only dependent on the circuit design, but also on the integration cost. With rapid advancements in semiconductor fabrication technology, the cost of gate-driver ICs is becoming comparable to discrete circuits, making the IC solution even more attractive and feasible for most applications.

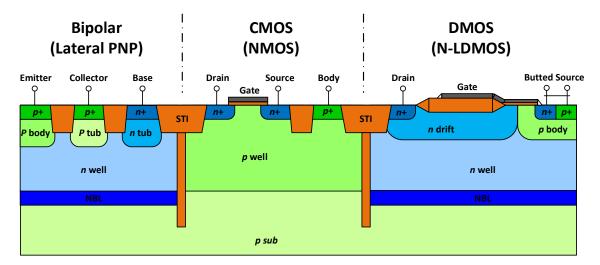

Most modern power ICs are fabricated using BCD (Bipolar CMOS DMOS) technology. It typically offers low-voltage transistors (for digital and analog signal processing), high voltage power transistors (for output stage), and also diodes, capacitors and resistors in the same process; with feature size ranges from 0.35  $\mu$ m to 0.13  $\mu$ m [53]. A typical cross section shows the BCD technology with a combination of bipolar, CMOS and DMOS devices on the same IC are illustrated in Figure 1.9. Robust isolations between low voltage and high voltage circuitries are required by using deep-trench isolation (DTI) and highly doped deep buried layers. The deep buried layers could shield any disturbances coming from the substrate and prevent any parasitic transistors from turning on, while the DTI technique could ensure great lateral isolation. Compared to previous LOCal Oxidation of Silicon (LOCOS) and Shallow Trench Isolation (STI) techniques, DTI technology offers much better physical isolation with increased area density.

Figure 1.9: Illustration of the BCD IC technology which includes bipolar, CMOS and DMOS devices on the same IC.

Another solution with better isolation capability is to use SOI (Silicon-on-Insulator) BCD [54]. A gate driver IC in SOI technology is presented in [55] which integrates all primary and secondary side driver functions for a three-phase MOSFET power inverter system on a single chip. This is possible because the insulated substrate enables full dielectric isolation for devices operating in different voltage domains. In addition, improved EMC and robustness could be realized by using SOI technology. However, due to the higher cost of the SOI substrate, it is usually only employed in high profit margin applications such as bio-medical and automotive sectors, etc.

## 1.3. Conventional IC Sensing Methods for IGBTs

Current sensing has always been critical for protection and regulation in modern high voltage and high current power systems. Different current sensing techniques have been reviewed in [56-58]. These current sensors include series/shunt resistors or magnetic/inductive sensors such as Rogowski coils, current transformers and Hall Effect sensors. Efforts have been made to integrate the above-mentioned sensors to various industrial power systems to monitor the output currents [59-61]. A few popular current sensing methods used for IGBTs and IGBT modules will be discussed next.

#### 1.3.1. Current Sensing using Shunt<sup>1</sup> Resistors

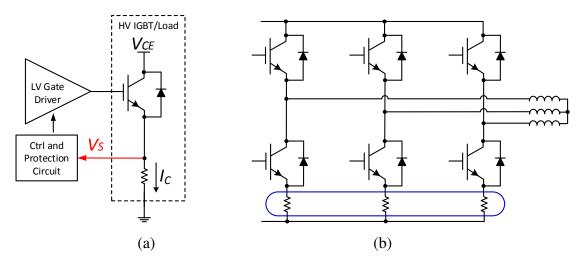

For current sensing in IGBT modules, the shunt resistor sensors remain the most popular due to their low cost and small size. As shown in Figure 1.10 (a), a low-value ohmic shunt resistor is inserted between the emitter of the IGBT and ground. The voltage drop across the resistor will be used by another circuit for monitoring and detection [58, 59, 62].

In order to achive fast response time to potential high-impluse and heavy-surge currents, coaxial shunts are usually used [63]. Neverthelss, calibrations are still needed when

<sup>&</sup>lt;sup>1</sup> Shunt resistor is usually placed in series with the load, and a voltage is generated across the shunt resistor which is proportional to the load current.

integrating them to different switching systems even for coxial shunts with excellent frequency response [64]. For highly compact electronic systems, the bulky coaxial shunt resistors are no longer suitable and Surface-Mounted-Device (SMD) resistors with small physical dimensions are generally used instead. However, the small size of SMD resistors causes the parasitic industance become a major concern as the frequency reponse could be seriously deteriorated. Compensation techniques using filters are sometimes needed to improve the bandwith for SMD shunt resistors [56].

Figure 1.10: (a) Traditional IGBT collector current sensing methods using a shunt resistor (b) shunt resistor current sensing implemented in a 3-phase power inverter.

For either the coaxial shunts or SMD resistors, the resistance values are usually quite small and in the milli-ohm range. The extracted  $V_s$  often needs to be amplified to an acceptable level before further processing. The amplifer stage may further limit the bandwith. Morevoer, the induced voltage due to the self-inductance of the shunts and the parasitic inductance of the contact leads may become comparable to the resistive voltage drop [65], causing noises on the measurements.

Another major disadvantage of shunt current sensing is its low efficiency. Considering the fact that IGBTs are usually implemented in high power systems, the power loss across the shunts can be very high when high currents are being switched. Sometimes a heat-sink may even be required; the system cost and size are then increased drastically. In addition, measuring  $V_S$  can be difficult as the load side voltage could have a swing of several hundreds of volts.

Figure 1.10 (b) shows the application of shunt current sensing in a 3-phase power inverter. The shunt resistors are placed below the low side switch of each branch for current monitoring. The sampling technique is critical as the phase current passes through the low side switch for only a portion of the fundamental cycle. Special algorithms should be developed and implemented to utilize the available current information effectively, so that the full output phase current waveforms could be reconstructed accurately [66].

In summary, the shunt resistor current sensing has poor accuracy, consumes too much power and provides no measurement isolation from load side. The only reason that they are still widely adopted in low end industrial drives is because of their low cost [59].

#### 1.3.2. Sense-FET Current Sensing

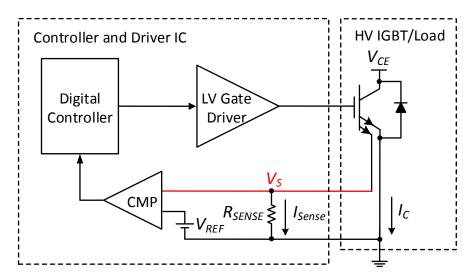

Another common collector current sensing method for IGBTs is to embed a sense structure inside the IGBT chip. This is similar to the sense-FET used in power MOSFETs [67, 68], as illustrated previously in Figure 1.4. The small sense current,  $I_{Sense}$  is directly proportional to the main collector current,  $I_C$ , and can be measured though a sense resistor. Figure 1.11 illustrates a typical application of using Sense-FET for over current protection.

Figure 1.11: Schematic of using a Sense-FET for over current protection.

Due to the unique characteristics of the IGBT, there are three options for the embedded current sensor: 'active current sense', 'MOS current sense' and 'bipolar current sense'. The linearity of these sensors has been studied in [69], and it is found that the active current sensor has the best linearity, while the MOS current sensor has least temperature dependence. Many steps have been taken to improve the accuracy and robustness of these integrated sensors through layout optimization [67, 70-72]. However in practical applications, it is almost impossible to achieve a constant current sensing ratio across all the entire operating condition of the IGBT. For example, the current sense ratio is sensitive to the collector emitter voltage  $V_{CE}$ . Even special sensing topology is implemented, the current sensing ratio can exhibit a variation of 5~10% across the normal operating range of  $V_{CE}$  [67, 71].

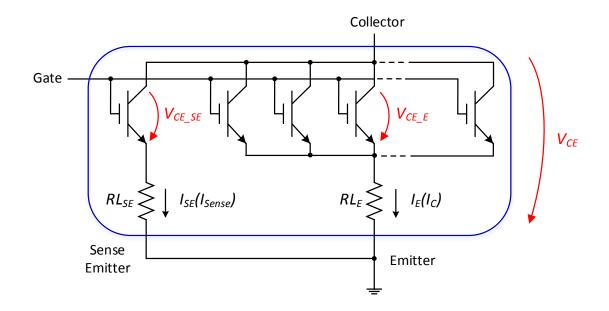

It is also well known that the current sensing ratio has a great dependence on the actual collector current  $I_c$ . As illustrated in Figure 1.12, the IGBT usually consists of tens of thousands of small cells connected in parallel, and the sense emitter uses part of these cells [73]. Ideally the current sensing ratio should be equal to the emitter area ratio. In reality, there are parasitic resistors at the emitter ends due to the interconnectors and leads. The values for the sense emitter parasitic resistor  $RL_{SE}$  and that for the main emitter  $RL_E$ are comparable in this case. Since the current flowing through the main emitter  $I_C$  is much greater than the current flowing through the sense emitter  $I_{Sense}$ ; the voltage drop across the sense device  $V_{CE\_SE}$  is much less than  $V_{CE\_E}$  which is the voltage drop across the main IGBT device. When a shunt resistor is inserted to the sense emitter, the voltage drop difference across the parasitic resistors may cancel out to certain extent. Therefore the real current sensing ratio is never just the emitter area ratio. It depends on the parasitic resistance values and the external shunt resistor value; causing considerable and nonlinear variations when the main emitter current level changes [73]. Therefore, in practical applications, it is compulsory to measure the current sensing ratio under actual use conditions to determine the correct overcurrent limit.

Figure 1.12: Schematic explaining the effect of residue resistance exerting on the current sensing ratio variation [73].

Another major drawback of the Sense-FET current sensing is the current overshoot problem when turning on the IGBT device. During the turn-on transient of the IGBT, there is normally a large overshoot in  $I_C$  due to the diode drawing reverse recovery current from the dc supply [74]. Excessive ringing on  $I_C$  can also be observed during turn-on when the gate drive resistance is small and the turn-on process is exceedingly fast, causing undesirable EMI (Electro Magnetic Interference) [43]. Consequently, the sense current  $I_{Sense}$  would also exhibit large over shoot and ringing. This could falsely trigger the over current protection circuity. Therefore, a blanking circuit is normally required for the protection circuit to have a blocking period during the turn-on transient to avoid any false triggering. However, the blanking circuit is not desirable and possibly harmful if a real short circuit condition happens during the blocking time.

Other than the above mentioned disadvantages, the Sense-FET current sensing ratio also has large dependence on the IGBT junction temperature [67, 72, 73]. This is attributed to the physical structure and location of the Sense-FET on the IGBT chip. Normally the Sense-FETs are placed at the side the chip while the temperature sensor is placed in the middle of the chip. Thus the average temperature of the Sense-FET is usually different from that the main emitter cells.

In addition, the sense resistor must be sufficiently small to keep the potential at the sense electrode to be less than 50mV. As a result, the sensing circuit has poor noise immunity [36]. Therefore, this current sensing method is widely adopted in IPMs for short circuit protection only as it lacks the accuracy required for current regulation.

#### 1.3.3. Other Current Sensing Methods

Another IGBT current sensing technique is inspired by the MOSFET current sensing method using the  $R_{DS}(on)$ . It assumes the MOSFET acts like a resistor when it is turned on, and the drain current can be deduced by measuring the voltage drop across the MOSFET [75]. International Rectifier extended this application to IGBT current measurement through measuring the  $V_{CE}(on)$  of the IGBT [76]. The accuracy of this technique depends on the tolerance of the on-resistance of the IGBT. Blanking circuit or filters are needed to prevent the noisy spikes from false triggering the protection circuits. Temperature effects are yet to be compensated. Moreover, this approach involves a HVFET which connects directly to the switching node for  $V_{CE}$  sensing; therefore, an expensive discrete component is necessary.

All the above mentioned current sensing techniques are based on resistive sensing and involving touching the high voltage power switch or load side which may cause safety concerns. For this reason, current sensors which are based on in-direct sensing and provide inherent electrical isolation are normally more attractive for applications where isolation is required [56]. For example, the Hall Effect sensor, Rogowski coils and Current Transformers are widely used in power electronic systems for current sensing.

Hall Effect sensor is a popular magnetic field sensor. It predicts the current level by sensing a voltage caused by the magnetic field. Therefore, it is non-intrusive and power efficient. It can be used for both DC and AC current sensing up to hundreds of kHz [57]. In addition, it has small and simple structure and can be fabricated using CMOS technology. However, Hall Effect sensor is usually more expensive than a Rogowski sensor or a current transformer. Other than the cost, the sensor often exhibits an unstable offset voltage which may vary over time. Meanwhile, it is also sensitive to temperature

and external magnetic field which make them less attractive for integrated applications [56].

Rogowski Coil is an application based on Faraday's law of induction. It is an air-cored coil placed around the conductor in a toroidal fashion [57]. The induced voltage across the coil can be measured to estimate the derivative of the primary current. Simple integration could then be carried out to predict the exact the current level. Rogowski Coil sensor has small size, low cost, high bandwidth and excellent linearity. Reference [60] presents a new power module concept which integrates a tiny PCB Rogowski Coil for IGBT switching current measurement in a compact converter. However, external circuitry including an integrator and ADC is needed to process the output voltage.

Current Transformers are widely used for AC current sensing. Similar to the Rogowski Coils, Current Transformers also exploit Faraday's law of induction to measure current. This technique thus provides galvanic isolation and consumes little power. Unlike the Rogowski Coil technique using an air core, Current Transformer has a magnetic core and needs to be terminated with a sense resistor. The core material design needs to be carefully considered as the hysteresis of the core material may degrade the measurement accuracy. Besides, the core should not be saturated under any condition especially in low frequency applications. This may lead to increased size and cost. Therefore, the Current Transformer technique is not suitable for DC current measurement [56-58].

It can be seen that all the non-intrusive current sensing methods either based on Faraday's Law or Magnetic field sensing are inevitably making use of external components which pose difficulties for system integration. These sensors are also sensitive to various parasitic effects and temperature, making them difficult to achieve high accuracy in practical applications.

A new current sensing method which involves no external component and can be fully integrated into an IGBT gate driver IC will be introduced in Chapter 2. This technique is based on the Miller effect of the IGBT devices, and it allows a cycle by cycle measurement of the IGBT switching current with high accuracy. A brief Comparison of

the proposed current sensing technique versus the existing current sensing methods is listed in Table 1.1 and Table 1.2.

| Current Sensing<br>Methods | Accuracy | Estimated<br>Bandwidth | Cost   | Power<br>Loss | Isolated |

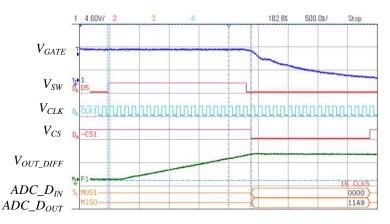

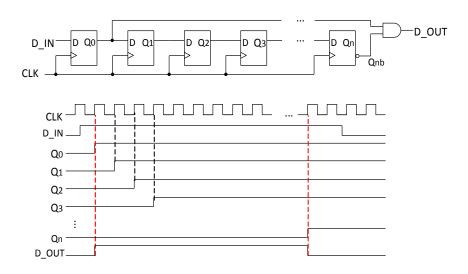

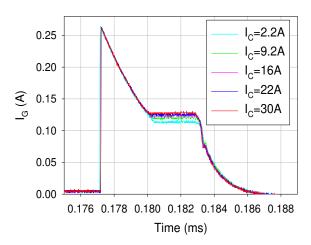

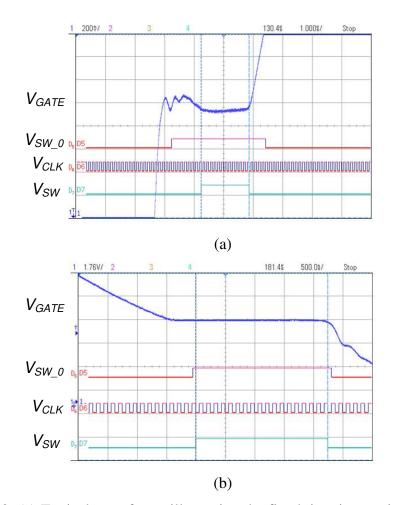

|----------------------------|----------|------------------------|--------|---------------|----------|