# 전원무결성 해석에 의한 PCB 전원안정화 설계기법 연구

정기현<sup>\*</sup> · 장영진<sup>\*\*</sup> · 정창원<sup>\*</sup> · 김성권<sup>\*\*\*</sup>

A study on Source Stability Design Method by Power Integrity Analysis

Ki-Hyun Chung\* · Young-Jin Jang\*\* · Chang-Won Jung\* · Seong-Kweon Kim\*\*\*

요 약

본 논문에서는 전원무결성(Power Source Integrity) 해석을 기반으로 PCB(Printed Circuit Board)내부 전원 선로의 RLC 공진(Resonance)현상을 해석하고 PCB내부 공진현상 감쇄를 위한 설계기법을 제시한다. 제시하는 기법은 PCB의 구조적 특성으로 형성되는 공진주파수를 예측하며, 공진현상 감쇄를 위한 디커플링 캐패시터의 적용위치 및 용량을 결정할 수 있다. 본 논문에서는 산업용 제어기 내부의 메인보드 회로 시뮬레이션 모델을 통해서 PCB 공진현상 감쇄 설계기법에 대한 타당성을 검증하였다. 본 연구결과는 향후, PCB 회로 설계에서 PDN(Power Delivery Network)구조의 안정도 향상에 기억할 것으로 기대된다.

#### **ABSTRACT**

This paper introduces the reduction design technique of the resonance phenomenon of the inner PCB based on power integrity from the analysis about the inner power supply line generating RLC resonance. With the technique, the resonant frequency resulted from the structural characteristics of the PCB can be analyzed and allows to predict and the capacitor for resonance phenomenon reduction can be decided as a decoupling capacitor. From the simulation result, it was confirmed that the PCB's resonance phenomenon reduction design technique should have the reduction effect in the inner motherboard of the industrial controller. This research will be contributed to the improvement of the safety of a PDN (Power Delivery Network) structure in the layout design technique of the PCB.

#### 키워드

Power Integrity, Resonance, PCB(Printed Circuit Board), Decoupling Capacitor 전원 무결성, 공진, 인쇄회로 기판, 디커플링 캐패시터

접수일자: 2014. 06. 21 심사(수정)일자: 2014. 07. 02 게재확정일자: 2014. 07. 18

<sup>\*</sup> 서울과학기술대학교 NID융합기술대학원(chungkihyun@gmail.com, changwoi@seoultech.ac.kr)

<sup>\*\*</sup> 서울과학기술대학교 일반대학원 미디어IT공학과(jyj0129@seoultech.ac.kr)

<sup>\*\*\*</sup> 교신저자(corresponding author): 서울과학기술대학교 전자IT미디어공학과(kim12632@seoultech.ac.kr)

## 1. 서 론

최근 전기, 전자 및 정보통신 기술의 급속한 발전과 더불어 각종 전자 기기 및 구성 부품들의 배치와 PCB 패턴의 구조도 점점 고집적화 되어가고, 고속 데이터 전송을 위해 사용되는 신호가 높은 주파수 영역으로 확장됨에 따라 불요전자파 및 노이즈(Noise)로인한 문제가 많이 발생되고 있다. 즉, PCB 보드상에서 회로가 고속, 고집적화 되어감에 따라서 전원의 안정화가 주요한 문제로 대두되고 있다. PCB 전원(Vdd/Ground)으로 유입되는 노이즈는 신호잡음, 전원에 의한 스위칭 노이즈(Switching Noise), 열잡음 등과 같이 여러 가지 형태로 존재하며, 이러한 노이즈는시스템 내부 제어보드의 주요 신호들을 왜곡하여 알수 없는 시스템 에러를 발생시키거나, 데이터를 손실시키고 있다.

최초 회로 및 아트웍(Artwork) 설계 이후에 전원 안정화를 위한 설계 기법 중 하나인 전원무결성 (Power Integrity :PI) 해석은 PCB의 구조적 특성으로 형성되는 공진주파수를 예측하며, 공진현상 감쇄를 위한 디커플링 캐패시터의 적용위치 및 용량값을 산출하여, 최대한 잡음을 억제하고 제어함으로써, 노이즈의 전달을 최소화하는 PCB 전원안정화와 관련지어질 수 있다[1-4].

PCB 전원안정화의 의미는 EMC / EMI 와도 상당히 밀접한 관계를 가지고 있다. 이상적인 전원구조라면 전위는 변동하지 않지만, 실제적인 회로에서는 Return Current 의 유입으로 전위가 변동하게 되며, 이로 인해서 에너지 변동과 함께 전원면(Vdd / Ground)을 방사원으로 하는 불요 전자파(EMI)가 발생한다[5-7].

본 논문에서는 PCB 회로 설계 및 아트웍 설계 이후 전원(Vdd/Ground)면의 구조적 공진주파수를 찾기위해서 전자장 해석법을 이용하였다[8]. PCB 동작에방해가 되는 공진주파수의 위치 및 크기를 파악하고,아울러 파악된 공진주파수에 대한 임피던스도 해석한다. 전자장 해석법을 통하여 공진주파수 및 임피던스에 대한 해석 결과를 바탕으로 PCB 레이아웃에 가상의 디커플링 캐패시터를 배치해 가면서 임피던스 및공진현상 발생을 최소화하게 하는 디커플링 캐패시터의 위치 및 용량 값을 도출하여 PCB 내부에서 발생

하는 공진현상을 최소화할 수 있음을 보이고자 한다.

## II. PCB 공진주파수

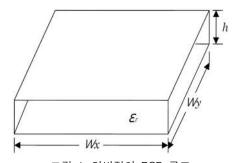

일반적으로 산업현장에서 설계되는 PCB의 모양은 대부분 사각형(Rectangular) 형태로 아트웍(Artwork) 이 이루어진다[9]. 그림 1은 일반적인 베어(Bare) PCB 형태를 나타낸 것이다. 식 (1)은 그림 1의 공진모드[TM(m,n)]에 따른 공진주파수를 나타낸 식이다. 식(1)에서 p=0 임을 고려하면 식(2)를 얻을 수 있다 [10-12]. 또한, 식(3)을 식 (2)에 대입하여 정리하면 식(4)와 같이 PCB의 크기와 유전율을 통해서 공진주파수를 구할 수 있다.

그림 1. 일반적인 PCB 구조 Fig. 1 General form of PCB structures

$$f_{res} = \frac{1}{2\sqrt{\mu\varepsilon}} \, \sqrt{(\frac{m\pi}{W_x})^2 + (\frac{n\pi}{W_y})^2 + (\frac{p\pi}{h})^2} \tag{1} \label{eq:fres}$$

$$f_{res(m,n)} = \frac{1}{2\sqrt{\mu\varepsilon}}\sqrt{(\frac{m\pi}{W_x})^2 + (\frac{n\pi}{W_y})^2} \tag{2}$$

$$C_0 = \frac{1}{\sqrt{\varepsilon_0 \mu_0}} = 3 \times 10^8 \, m/s \tag{3}$$

(  $\mu_0=4\pi\times 10^{-7} H/m$  ,  $\varepsilon_0=8.85\times 10^{-12} F/m$  )

$$f_{res(m,n)} = \frac{C_0}{2\sqrt{\varepsilon_r}} \sqrt{(\frac{m\pi}{W_x})^2 + (\frac{n\pi}{W_y})^2} \tag{4}$$

위에서 유도된 식들을 통해서 알 수 있듯이 공진 주파수는 PCB의 구조적 특성으로 형성됨을 알 수 있 다. 따라서, PCB의 구조에 대한 해석을 바탕으로 공 진 주파수를 예측할 수 있다.

#### III. PCB 레이아웃에 대한 공진해석

최초 PCB 아트웍 설계 이후의 베어(Bare) PCB에 대한 공진 해석은 원하지 않는 특정 주파수에 대한 공진현상의 분포를 예측할 수 있도록 도와준다. 본 연구에서 실험한 주파수 대역은 무선전화기 주파수에 포함되는 900~950MHz 이다.

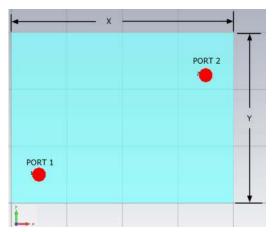

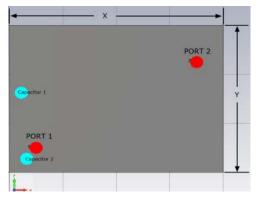

그림 2에서 해석 대상이 되는 PCB의 외곽 및 PCB에 인가될 전원 포트를 나타내고 있으며 표 1은 PCB레이아웃에 대한 정보를 표시하고 있다.

그림 2. 해석대상 PCB 레이아웃 및 전원포트 구성 Fig. 2 PCB layout and power ports configuration

표 1. 실험 대상 PCB 레이아웃에 대한 규격 Table 1. PCB layout specifications for test subjects [unit:mm]

| Param eters      | Length<br>/ thickness | X<br>Coordinates | Y<br>Coordinates |

|------------------|-----------------------|------------------|------------------|

| Х                | 80                    | -                |                  |

| Υ                | 60                    | -                | -                |

| PORT 1           | -                     | 10               | 10               |

| PORT 2           | -                     | 70               | 45               |

| PCB<br>thickness | 1.07                  |                  |                  |

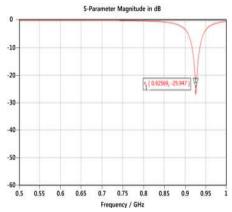

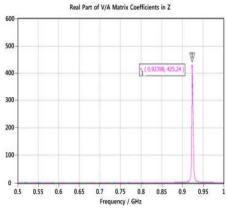

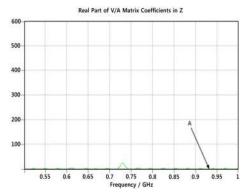

그림 3은 PCB의 포트에 가우시안(Gaussian) 펄스를 인가하여 S-Parameter를 얻은 결과이며, 그림 4는 전달 임피던스 해석을 통해서 약 930MHz 부근에서 전달 임피던스가 높아졌음을 나타내며, 현재 설계된 PCB 레이아웃 구조에서 930MHz 근처 주과수에 대한 공진현상 발생에 대한 대책이 필요함을 나타낸다.

그림 3. S-parameter 해석결과(S11) Fig. 3 S-parameter analysis results(S11)

그림 4. 전달 임피던스 해석 결과 Fig. 4 Transmission impedance analysis

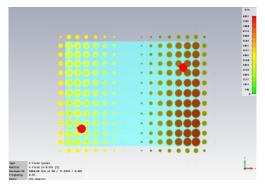

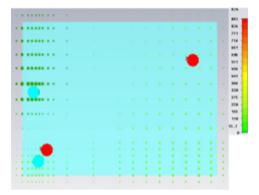

그림 5는 PCB 레이아웃 공진해석을 바탕으로 도출된 특정주파수(930MHz) 대역에서의 공진현상 발생을 나타내는 그림이다. 포트 1과 포트 2 주변 양쪽 모두에 공진현상 발생을 나타냄을 색깔로 표시되고 있다. (PCB 중앙을 중심으로 X 축 양쪽 방향임)

그림 5. 예측된 공진주파수(930MHz)에서의 공진현상 Fig. 5 The resonance phenomenon of Predicted resonance frequency(930MHz)

## Ⅳ. 공진발생 감쇄를 위한 대책 및 검증

전자장 해석결과를 바탕으로 아트웍(Artwork)이 완료된 PCB 레이아웃 상에서의 공진영역 및 공진주 파수를 알 수 있는데, 전원무결성 해석을 통해서 공진을 최소화하는 방법은 여러 가지가 있겠지만, 그 중에서도 디커플링 캐패시터를 통한 방법이 산업현장의실무 엔지니어들에게는 가장 간편한 방법으로 사용되고 있으며, 본 연구에서도 이 방법을 도입하였다. 디커플링 캐패시터는 전원면(Vdd/Ground) 사이에 캐패시터를 삽입하여, 공진발생 영역 및 공진주파수를 제어하기 위한 캐패시터를 의미한다.

공진 발생 감쇄를 위한 방안으로는 PCB 레이아웃 상에 가상의 캐패시터를 실장하면서, 임피던스 분석과 공진해석을 병행하여 최적의 캐패시터 값과 PCB 상 에 배치할 위치를 결정할 수 있다. 다음은 디커플링 캐패시터의 용량선정과 PCB 상의 위치 결정방법에 대한 사항이다.

첫째로 캐패시터의 용량 선정의 기준은 공진해석결과에 의해 도출된 공진주파수(930MHz) 대역에서 임피던스가 가장 작은 캐패시터를 선정한다. 캐패시터 의 주파수별 임피던스 특성은 제조사가 제공하는 Data sheet를 참조해야 한다. 둘째로 캐패시터의 위치 선정은 PCB 공진 해석을 기초로 하여 공진발생 위치부근에 대한 trial and error 기법으로 위치선정 및 캐패시터의 수량을 결정할 수 있었다.

그림 6. 디커플링 캐패시터의 용량 및 위치결정 Fig. 6 Positioning and capacity of the decoupling capacitor

그림 6은 상기 설명된 대책방안을 적용하여 Capacitor 1과 Capacitor 2를 최적의 위치 및 용량값 설정으로 디커플링 캐패시터를 PCB 레이아웃 상에 배치한 결과이다.

그림 7. 디커플링 캐패시터 적용 후 전달 임피던스 Fig. 7 Transfer impedance after applying the decoupling capacitor

그림 7은 디커플링 캐패시터의 위치 및 용량값 설정 이후의 전달 임피던스의 결과로 대책방안 이전의 그림 3의 결과와 비교하면 디커플링 캐패시터 적용이후에 상당히 감소했음을 알 수 있다( 그림 6의 화살표 A 참조).

그림 8. 산업용 제어기 메인보드에 디커플링 캐패시터 적용 후 검증(PCB 의 Top 면) Fig. 8 Verified by applying the decoupling capacitance on the industrial motherboard(PCB Top side)

그림 9은 제안된 대책방안을 적용하여 공진해석을 진행한 결과 980MHz 대역에서의 공진주파수 영역이 감쇄되었음을 확인할 수 있었다.

그림 9. 디커플링 캐패시터 적용 후 공진해석 결과 Fig. 9 Analysis result after applying the decoupling capacitor

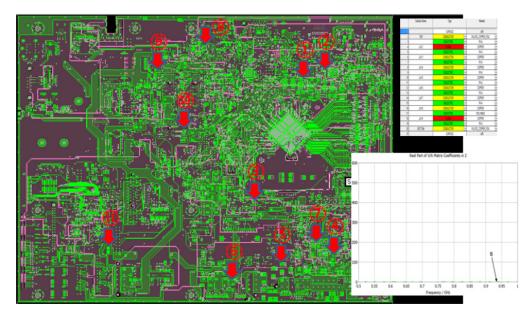

상기 실험에서 얻은 결과에 대한 타당성 검증을 위해서 산업용 제어기 내부의 메인보드에 디커플링 캐패시터를 배치하고 해석을 진행하였다. 그림 8은 메인

보드내의 디커플링 캐패시터를 배치한 결과를 나타내고 있다(그림 8의 화살표 ①-⑪ 참조). PCB의 Top 레이어(Layer)에 11개, Bottom 레이어(Layer)에 10개의 디커플링 캐패시터를 여러 전원에 나누어 배치하였다. 표 2는 각 전원별 캐패시터의 종류와 수량 및 배치된 PCB 면(Side)을 나타내고 있다.

표 2. 메인보드에 적용된 디커플링 캐패시터 Table 2. Mounted capacitors for verification

| Power | Capacitor | Quantity | PCB Layer |

|-------|-----------|----------|-----------|

| Vcore | 2.2uF/X5R | 3        | Top       |

| Vchr  | 4.7uF/X7R | 4        | Top       |

| V3p3s | 10uF/X5R  | 2        | Top       |

| V1p8s | 0.1uF/X7R | 1        | Тор       |

| Vbat  | 22uF/X5R  | 1        | Тор       |

| Vcddr | 0.1uF/X5R | 4        | Bottom    |

| V1p8  | 1uF/X6S   | 2        | Bottom    |

| Vgfx  | 1uF/X6S   | 4        | Bottom    |

공진해석 결과 실험대상 주파수인 930MHz에서의 전달 임피던스가 상당히 낮아짐을 확인할 수 있었다 ( 그림 8의 화살표 B 참조 ). 이와 같은 결과는 930MHz에서 PCB 공진에 의한 문제 발생을 최소화 할 수 있다는 의미로 메인보드 자체의 신뢰성 확보문 제와도 연관 지을 수 있다.

## V. 결 론

본 연구에서는 산업용 제어기 내부에 장착되는 메 인보드 회로 시뮬레이션 모델을 통해서 특정 주파수 대역에서의 공진현상을 감쇄 시켜서 PCB 전원안정화 를 위한 대책 방안의 타당성을 검증하였다.

복잡한 시뮬레이션 해석 부분에 대해서는 중요한해석 파라미터만을 선정 후에 해석하고 결과를 도출하였으며, 해석기법의 적용은 전체적인 제품 개발 프로세서 단계 중에서 PCB 회로설계 단계에 적용하여 PCB로 인한 문제 발생 가능영역을 사전에 예측하고이에 대한 대책을 수립하여, PCB 제작 이전에 구조적인 문제를 해결함으로써 불필요한 재설계를 최소화하여 개발 시간 단축 및 원가 절감에도 도움이 될 것으로 기대된다.

#### 감사의 글

본 논문은 2014년도 한국전자통신학회 봄철 종합학 술대회 우수논문 논문입니다.

이 연구는 서울과학기술대학교 교내연구비의 지원으로 수행되었습니다.

#### References

- [1] W. Liu and Y. Kami, "Analysis of crosstalk between finite-length microstrip lines: FDTD approach and circuit-concept modeling," *IEEE Trans. Electromagn. Compat*, vol. 43, no. 4, Nov. 2001, pp. 573-578.

- [2] Y. Kami, "Coupling model of Crossing Transmission Lines," *IEEE Trans. Electromagn.*

- Compat. vol. EMC-28, no. 4, Nov. 1986, pp. 204-210.

- [3] R. Sato, "Analysis of radiation characteristics of a finite-length transmission line using a circuit-concept approach," *IEEE Trans. Electromagn.* Compat., vol. EMC-27, no. 4, Nov. 1985, pp. 114-121.

- [4] O.-W. Kim, "Design of Dual-band Microstrip Antenna for Wireless Communication Applications," J. of the Korea Institute of Electronic Communication Sciences, vol. 7, no. 6, 2012, pp. 1275-1279.

- [5] W. Liu, "Analysis of coupling between transmission lines in arbitrary directions," *IEEE Int. EMC Symp., Denvor*, CO, USA, pp. 952-957.

- [6] J. Ju, J. Lee, and D. Park, "Analysis of coupling between PCB traces using a circuitconcept approach," 2004 Int. Symp. Electromagn. Environ. Tech., Daejeon, Korea, May 2004, pp. 1185-1188.

- [7] K.-H. Kim, D.-J. Song, and J.-W. Choi, "A Study on Risk Communication and Perception of Electromagnetic Waves from Cellular Phones," J. of the Korea Institute of Electronic Communication Sciences, vol. 8, no. 7, 2013, pp. 1066-1069.

- [8] K.-J. Kim and H.-S. Ko, "The Optimization using PCB EM interpretation of GEO satellite's L Band Converter," J. of the Korea Institute of Electronic Communication Sciences, vol. 8, no. 8, 2013, pp. 1220-1225.

- [9] H. Kim, PCB Process Technology. Hongrung Publishing Company, 2002.

- [10] G. T. Lei, R. W. Techentin, P. R. Hayes, D. J. Schwab, and B. K. Gilbert, "Wave Model Solution to the Ground/Power Plane Noise Problem," *IEEE Trans. Instrumentation and measurement*, vol. 44, no. 2, Nov. 1995, pp. 300-303.

- [11] G. W. Peterson, J. L. Prince, and K. L. Virga, "Investigation of Power/Ground Plane Resonance

Reduction Using Lumped RC Elements," *IEEE Int. Electronic Components and Technology Conf.*, Las Vegas NV, USA, May 2001, pp. 769-774.

[12] J. Mao, C. Wang, and G. Selli, "Memory DIMM DC Power Distribution Analysis and Design," IEEE Int. Electronic Components and Technology Conf., Las Vegas NV, USA, May, 2000, pp. 597-602.

## 저자 소개

정기현(Ki-Hyun Chung)

2000년 연세대학교 대학원 전자공 학과(공학석사)

2010년~현재 서울과학기술대학교 NID융합기술대학원 박사과정

※ 관심분야 : 고속회로 및 아날로그 회로설계, SL/PI, EMC.

장영진(Young-Jin Jang)

2012년 남서울대학교 전자공학과 (공학사)

2012년~현재 서울과학기술대학교 일반대학원 석사과정

※ 관심분야 : SoC, IC설계, charge pump 회로 설계

정창원(Chang-Won Jung)

2001년 University of Southern California 전자공학(공학석사) 2005년 University of California, Irvine 전자공학(공학박사)

1997~2000년 LG 정보통신 연구원 2005~2008년 삼성종합기술원 전문연구원 2008년~현재 서울과학기술대학교 NID융합기술대학 원 조교수

※ 관심분야 : 안테나, RF, EMI/EMC, RF-MEMS, 센서

## 김성권(Seong-Kweon Kim)

2002년 일본TOHOKU대학교 대학 원 전자공학과(공학박사) 2002~2004년 일본TOHOKU대학교 전기통신연구소 Assistant Professor

& Research Fellow

2004~2009년 목포해양대학교 해양전자통신공학부 조교수

2009년~현재 서울과학기술대학교 전자IT미디어공학 과 부교수

※ 관심분야 : 무선통신용 아날로그 LSI 설계, 멀티 미디어통신, 음향공학, RF 회로설계