# UCLA UCLA Electronic Theses and Dissertations

### Title

A Study On The Impact Of Compiler Optimizations On High-Level Synthesis

Permalink https://escholarship.org/uc/item/8vq0q6wc

Author Prabhakar, Raghu

Publication Date 2012

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# A Study On

# The Impact Of Compiler Optimizations On High-Level Synthesis

A thesis submitted in partial satisfaction of the requirements for the degree Master of Science in Computer Science

by

### Raghu Prabhakar

© Copyright by Raghu Prabhakar 2012

### Abstract of the Thesis

## A Study On

# The Impact Of Compiler Optimizations On High-Level Synthesis

by

### Raghu Prabhakar

Master of Science in Computer Science University of California, Los Angeles, 2012 Professor Jason Cong, Chair

High-level synthesis is a design process which takes an UN-timed, behavioral description in a high-level language like C and produces register-transfer-level (RTL) code that implements the same behaviour in hardware. In this design flow, the quality of the generated RTL is greatly influenced by high-level description of the language. Hence it follows that both source-level and IR-level compiler optimizations could either improve or hurt the quality of the generated RTL. The problem of ordering compiler optimization passes, also known as the phase-ordering problem, has been an area of active research over the past decade. An optimization has enabling and disabling effects on other optimizations, and such effects are caused by either the nature of the optimization itself, the input program being optimized, or the target platform for which the code is being optimized. A well-known fact in literature is that the standard optimization order chosen by the compiler writer may not be the best order for every input, and hence can end up producing inferior code.

All methods mentioned above are targeted towards compilers producing code that will be executed on a processor. In this study, we explore the effects of both source-level and IR optimizations on high-level synthesis. The parameters of the generated RTL are very sensitive to high-level optimizations, in the sense that a right choice can provide significant benefits and a wrong choice can cause significant degradation. We consider three source-level optimizations commonly used in High-level synthesis. We study them in isolation and then propose simple yet effective heuristics to apply them to obtain a reasonable latency-area tradeoff. We also study the phase-ordering problem for IR-level optimizations from a HLS perspective. As many optimizations that are employed in a typical HLS flow were originally developed with a standard compiler in mind, and given the increasing popularity of HLS, we feel that such a study is essential to building high-quality HLS tools. Our initial results show that an input-specific order can achieve significant reduction in the latency of the generated RTL, and opens up this technology for future research.

The thesis of Raghu Prabhakar is approved.

Glenn Reinman

Todd Millstein

Jason Cong, Committee Chair

University of California, Los Angeles

2012

# TABLE OF CONTENTS

| 1        | Intr | roducti | ion                               | . 1  | 1 |

|----------|------|---------|-----------------------------------|------|---|

| <b>2</b> | Bac  | kgrour  | $\mathbf{nd}$                     | . 7  | 7 |

|          | 2.1  | High-l  | level Synthesis                   |      | 7 |

|          | 2.2  | xPilot  |                                   | . 8  | 8 |

|          | 2.3  | Experi  | iment design flow                 | . 10 | 0 |

| 3        | Sou  | rce-lev | vel Optimizations                 | . 13 | 3 |

|          | 3.1  | AutoE   | ESL optimization options          | . 13 | 3 |

|          | 3.2  | Array   | Partitioning                      | . 14 | 4 |

|          | 3.3  | Loop    | Unrolling                         | . 10 | 6 |

|          | 3.4  | Loop l  | Pipelining                        | . 22 | 2 |

|          | 3.5  | Appro   | pach to search optimization space | . 25 | 5 |

|          | 3.6  | Evalua  | ation                             | . 25 | 5 |

|          |      | 3.6.1   | Experimental setup                | . 25 | 5 |

|          |      | 3.6.2   | Results                           | . 20 | 6 |

| 4        | IR-  | level o | ptimizations                      | . 30 | ) |

|          | 4.1  | Motiva  | $\operatorname{ration}$           | . 30 | 0 |

|          | 4.2  | Metho   | odology                           | . 34 | 4 |

|          |      | 4.2.1   | Optimizations considered          | . 34 | 4 |

|          |      | 4.2.2   | Random search                     | . 30 | 6 |

|          |      | 4.2.3   | Genetic Algorithm                 | . 30 | 6 |

|          |      | 4.2.4   | <i>n</i> -lookahead scheme        | . 38 | 8 |

|   |       | 4.2.5  | Latency estimation model                                                                                                                    | 39 |

|---|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 4.3   | Evalua | $tion \ldots \ldots$ | 41 |

|   |       | 4.3.1  | Experimental setup                                                                                                                          | 41 |

|   |       | 4.3.2  | Random sampling vs. xPilot                                                                                                                  | 42 |

|   |       | 4.3.3  | Comparison of approaches                                                                                                                    | 44 |

|   |       | 4.3.4  | Evaluating the latency estimation model                                                                                                     | 47 |

|   |       | 4.3.5  | Comparison of best sequences across benchmarks                                                                                              | 48 |

|   |       | 4.3.6  | Comparison with CPU performance                                                                                                             | 49 |

| 5 | Rela  | ated W | $\sqrt{\mathbf{ork}}$                                                                                                                       | 56 |

| 6 | Con   | clusio | $\operatorname{ns}$                                                                                                                         | 59 |

| R | efere | nces . |                                                                                                                                             | 62 |

# LIST OF FIGURES

| 1.1 | Example design optimized with -gvn, -indvars and -mem2reg. CPU best se-       |    |

|-----|-------------------------------------------------------------------------------|----|

|     | quence differs from HLS best sequence                                         | 3  |

| 2.1 | The high-level synthesis flow in xPilot.                                      | 9  |

| 2.2 | Broad design flow used in all our experiments. xPilot is used for IR-level    |    |

|     | optimizations while AutoESL is used for source-level optimizations            | 11 |

| 3.1 | Example design to study array partitioning                                    | 15 |

| 3.2 | Comparison of latency and area numbers for different partitions for design in |    |

|     | 3.2. Power-of-2 partitions perform better                                     | 15 |

| 3.3 | Two simple kernels subject to loop unrolling                                  | 17 |

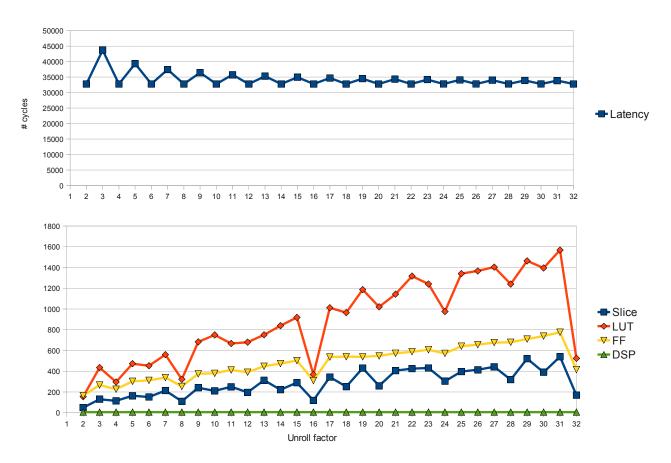

| 3.4 | Latency and area numbers for loop in $3.3(a)$                                 | 18 |

| 3.5 | Latency and area numbers for loop in $3.3(b)$                                 | 19 |

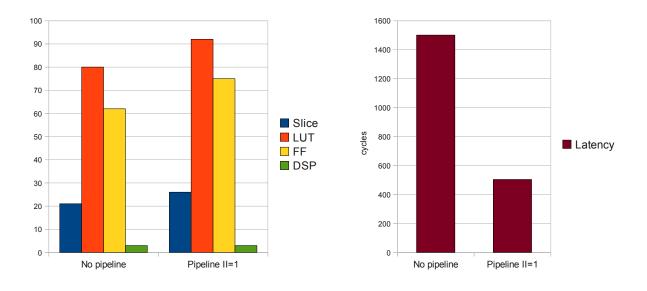

| 3.6 | Comparison: No pipelining v/s Pipelined loop (II=1) $\hdots$                  | 23 |

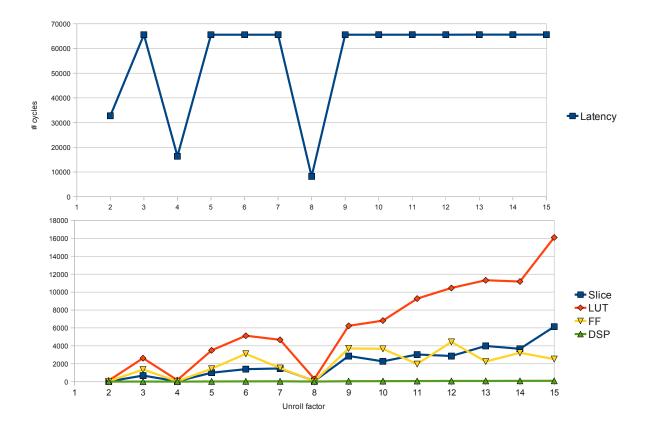

| 3.7 | Pipelining with unrolling loop in $3.3(a)$ for 65536 iterations               | 23 |

| 3.8 | Pipelining with unrolling and partitioning 3.3(a) for 65536 iterations        | 24 |

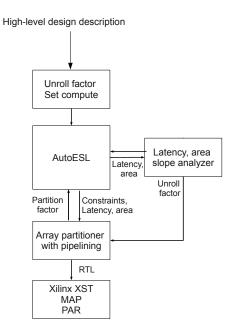

| 3.9 | Structure of our experimental flow                                            | 26 |

| 4.1 | Motivational example - simple addition                                        | 31 |

| 4.2 | Motivational example - factorial                                              | 31 |

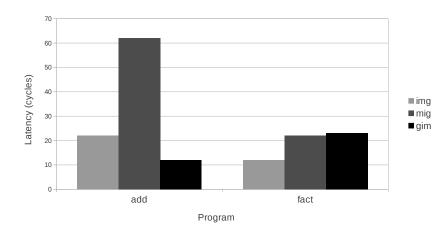

| 4.3 | Latency comparison for different optimization orders for examples in Figure   |    |

|     | 4.1 and Figure 4.2                                                            | 32 |

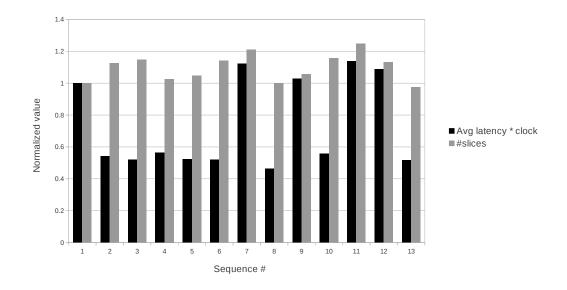

| 4.4 | Normalized latency and area numbers for $matrixmul$ obtained from AutoESL     |    |

|     | and Xilinx back-end.                                                          | 33 |

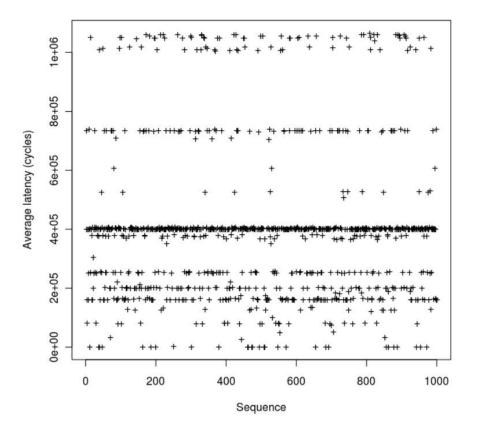

| 4.5 | Scatterplot of latencies for <i>matrixmul</i>                                 | 35 |

| 4.6 | Modified xPilot structure.                                                    | 41 |

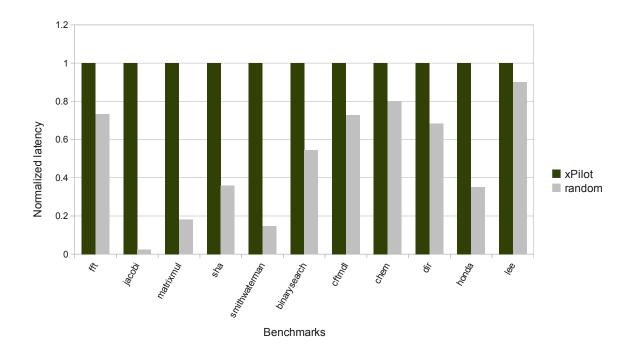

| 4.7  | Comparison of latencies: xPilot default sequence v Random search. Results    |    |

|------|------------------------------------------------------------------------------|----|

|      | are normalized to latency obtained by xPilot's default setting               | 43 |

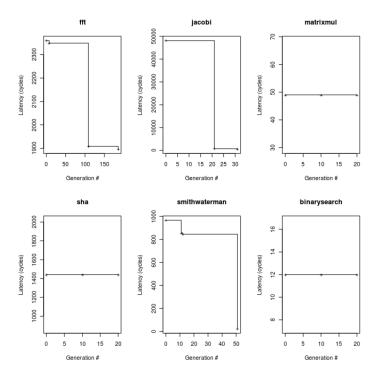

| 4.8  | Convergence rate of genetic algorithm for benchmarks                         | 47 |

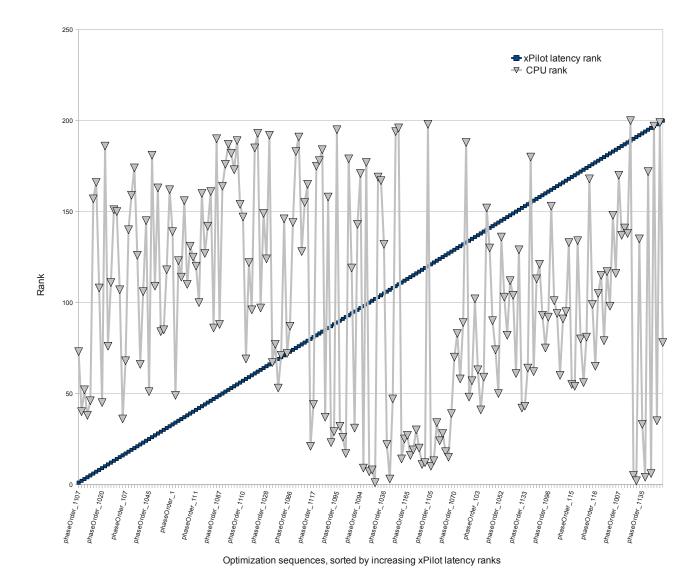

| 4.9  | Rank comparison for SmithWaterman: CPU vs xPilot. As can be observed,        |    |

|      | the same sequence ranks differently with respect to other sequences in a CPU |    |

|      | setting compared to a HLS setting                                            | 51 |

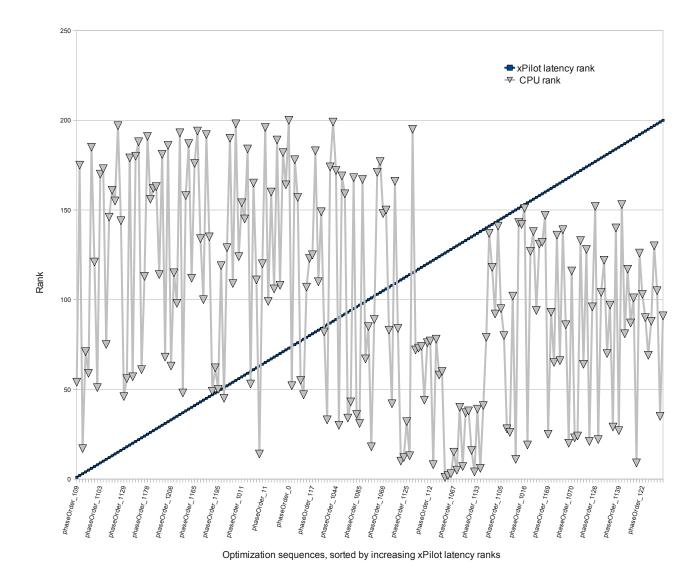

| 4.10 | Rank comparison for Sha: CPU vs xPilot. As can be observed, the same         |    |

|      | sequence ranks differently with respect to other sequences in a CPU setting  |    |

|      | compared to a HLS setting                                                    | 52 |

| 4.11 | Optimization sequence 1101 under comparative study between CPU and xPi-      |    |

|      | lot. This sequence favours HLS                                               | 52 |

| 4.12 | Optimization sequence 118 under comparative study between CPU and xPilot.    |    |

|      | This sequence favours CPUs                                                   | 53 |

# LIST OF TABLES

| 1.1 | Benchmarks and description                                                                                                                                                                                                          | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Benchmarks and description                                                                                                                                                                                                          | 12 |

| 3.1 | Options available in AutoESL. Each option can either be specified as a con-<br>figuration directive or as a pragma in source code                                                                                                   | 14 |

| 3.2 | Comparison between baseline and heuristically optimized benchmark versions                                                                                                                                                          |    |

|     | against latency and area using $ER$ . The unroll and partition factors used are also specified.                                                                                                                                     | 27 |

| 4.1 | Step-wise analysis of one sequence. Reported latency is reported (in cycles)                                                                                                                                                        |    |

|     | from xPilot. We used a target clock period of 50 ns                                                                                                                                                                                 | 36 |

| 4.2 | Subset of optimizations and descriptions                                                                                                                                                                                            | 37 |

| 4.3 | Benchmarks and description                                                                                                                                                                                                          | 42 |

| 4.4 | Comparison of different approaches. Some smaller benchmarks were left out                                                                                                                                                           |    |

|     | for brevity, as they closely resembled <i>binarysearch</i>                                                                                                                                                                          | 45 |

| 4.5 | Convergence of the genetic algorithm. Some smaller benchmarks were left out                                                                                                                                                         |    |

|     | for brevity, as they closely resembled <i>binarysearch</i>                                                                                                                                                                          | 46 |

| 4.6 | Evaluation of latency estimation metrics. The metric in the first column<br>was used to guide the GA, and a best sequence was obtained. The numbers<br>reported are the final latencies from xPilot upon applying the best sequence |    |

|     | obtained from the model-guided GA.                                                                                                                                                                                                  | 48 |

| 4.7 | Comparison of best sequences. We synthesize each of the four benchmarks us-                                                                                                                                                         |    |

|     | ing the best optimization sequence from each benchmark. Columns represent                                                                                                                                                           |    |

|     | benchmarks and rows represent the benchmark whose best sequence is being                                                                                                                                                            |    |

|     | used. Number reported is latency from xPilot, in cycles                                                                                                                                                                             | 49 |

| 4.8 | Best sequences for each individual benchmark                                                                                                                                                                                        | 50 |

| 4.9  | CPU cycle count from Simics of two binaries generated using the optimization |    |

|------|------------------------------------------------------------------------------|----|

|      | sequence in Figure 4.11, with and without <i>-bitwidthmin</i>                | 53 |

| 4.10 | Comparison of CPU and HLS settings with optimization sequences involving     |    |

|      | -gvn and -indvars                                                            | 54 |

#### Acknowledgments

I would like to take this opportunity to thank my adviser, Professor Jason Cong for all his support and encouragement over the course of two years. It is inspiring to have such an adviser who is so passionate about what he does. I am lucky to have had the opportunity to work with a very diverse group of bright researchers in our lab who have been gracious and patient enough to answer all my stupid questions. I would also like to thank Professor Todd Millstein for all the support and guidance. I am grateful to him for taking time off his schedule to meet me or to reply to my insane ideas through clear, detailed responses. The encouragement has always been there, and perhaps that is what has driven me into completing this thesis.

I would like to thank my parents who have always been supportive for everything. I would like to thank my flat-mates and friends without whom masters would not have been as much fun. While the list is endless, I would like to conclude by thanking UCLA for making my masters an experience.

# CHAPTER 1

### Introduction

The field of compiler optimizations has been an area of active research for more than fifty years. Numerous optimizations have been proposed and deployed over the course of time, each trying to optimize a certain aspect of an input program. With the increasing level of abstraction in programming languages and constantly evolving architectures, newer opportunities for optimization were created. Today, a great deal of literature is available to understand the mechanics, goals and theoretical complexities of each optimization. Optimizations play a key role in evaluating a compiler. Moreover, as processor clock speeds no longer increase in accordance with Moores law, the free ride of better performance obtained every couple of years by increased clock speeds is no longer available. Current trends in architecture favor a heterogeneous mix of general-purpose CPUs, application-specific accelerators like GPUs, FPGAs and hybrid memory hierarchies. Software must be explicitly written to take advantage of such a heterogeneous mixture of computing power. This places a heavy responsibility on the compiler to intelligently transform input code to achieve a certain objective, like code size, execution time or energy.

Given the significance of compiler transformations, it is important to understand the nature of each transformation so that it can be used intelligently. A well-known fact in literature is that optimizations have enabling and disabling interactions among themselves. This problem, also known as the phase-ordering problem, basically implies that applying transformation a before another transformation b can potentially increase the benefit obtained from b or can destroy the same. The interaction that exists between instruction scheduling and register allocation is a classical example for such a behavior. To make matters even more complicated, most of such interactions are input-dependent; depending on the existence of a certain structure and opportunities in the input program, interactions may or may not exist, and can vary in degree. Unfortunately, studies on most of the transformations have been conducted in unison, without considering the presence of other optimizations. A typical production compiler like GCC has more than 100 optimization flags. Standard optimization orders (i.e., -O2, -O3 etc.) are chosen by the compiler writer based on an averaged performance number on a large benchmark set. Past research has shown that the standard sequence yields inferior code, and that the best sequence is largely dependent on the input, the target architecture and the objective (time, code size etc.). As the solution space is huge, compiler researchers have tried a plethora of methods over the past decade based on searching techniques ([10] [9] [17] [16], [4]), analytical models ([29], [33], [32], [26], [31]), empirical approaches based on statistical data ([25], [24] [2]), and a mixture of all of these ([12], [27], [22]).

However, it is to be noted that all aforementioned approaches have been used to arrive at an optimal optimization sequence that can transform an input program such that the transformed version executes efficiently on a given processor, for some definition of efficiency. In this case, decisions regarding optimization orders are implicitly or explicitly influenced by code execution parameters such as the processor pipeline, size of the instruction window, live variables affecting register pressure, presence of hardware-managed caches and so on. How different would such optimization orders be if the code being optimized was not meant to be executed on hardware? In other words, what is the impact of the order of compiler transformations if the input is a behavioral description of some hardware itself?

For instance, consider the example design in Figure 1.1. The function walks through all elements of array a in a loop and computes the sum and product of all array elements. Note that the loop trip-count and array size are statically known. Array sizes are required to be known at compile-time for HLS to work, and loop trip-count needs to be known statically so that latency estimation can be performed. Also, let us consider a set of three optimizations mentioned below.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>We use the letters within brackets to refer to the respective optimizations in this section.

```

int add(int a[20], int o[2])

{

int i;

o[0] = 0;

o[1] = 1;

for(i = 1; i < 20; i++) {

if(a[i]%2 == 0) {

if(a[i]%2 == 0) {

o[0] += a[i];

o[1] *= a[i];

}

}

}</pre>

```

Figure 1.1: Example design optimized with -gvn, -indvars and -mem2reg. CPU best sequence differs from HLS best sequence.

- -gvn (g): Global value numbering.

- -mem2reg (m): Promote memory to register.

- -indvars (i): Canonicalize induction variables.

| Sequence | CPU (cycles) | HLS (cycles) |

|----------|--------------|--------------|

| gim      | 3903         | 12           |

| img      | 3814         | 22           |

Table 1.1: Benchmarks and description.

Consider two sequences, *gim* and *img*. In order to measure and compare the impact of the two sequences on the CPU and HLS, we optimized the design in Figure 1.1 using the two sequences, and ran a final dead-code elimination pass. To measure CPU performance, we compiled the optimized function into a binary by attaching some driver code. We used a cycle-accurate state-of-the-art out-of-order processor simulator Simics to get accurate CPU performance. We used xPilot to get latency measurements of the physical circuit this design represents, given a target clock period of 5 ns. Table 1.1 summarizes the performance of the sequences in these two scenarios.

We can observe that the sequence gim has a better performance in the HLS setting while sequence img has a better performance for code executed on the CPU. Upon examining the effects of the optimizations, we find that img produces smaller code with fewer loads. This is because the -gvn optimization applied after -mem2reg is exposed to far more opportunities like re-calculating array indices after their base addresses have been promoted to registers. This explains why the CPU shows better performance on the img optimization. However, this raises the question as to why the design with greater number of loads has a smaller latency in the HLS setting, especially because loads are expensive operations. Further examination revealed that while img reduced the loads by re-using computed values, it increased the length of the data dependency chain. This led to the img design having one extra state in its finite state machine created during scheduling.

The simple example shown above demonstrates that there are very subtle details and side effects that can have different impacts on CPU codes and HLS designs. Also, the impact of one optimization can be more pronounced in a HLS setting than in a CPU design. A typical CPU has many hardware features that enhance the performance of code that is being executed. For example, multiple levels of caches and out-of-order execution drastically reduce the cost of a single load. Techniques like branch prediction and speculative execution can hide the cost of evaluating a branch most of the times in case of loops. High-level synthesis is a different area in that way where each load corresponds to a read from a memory block, and each load costs the same number of cycles. Every branch instruction is dependent on another instruction that computes the exit condition, and branch prediction mechanisms have to be specified in software manually by the designer if needed. Also, HLS can potentially exploit greater ILP limited only by the physical resources available on the target platform. On a typical processor, only the ILP available within the instruction window is exploited.

In this study we perform an initial investigation into the impact of compiler transformations on behavioral descriptions of hardware circuits, which are passed through a high-level synthesis (HLS) tool. High-level synthesis is an automated design process that takes an UN-timed, behavioral description of a circuit in a familiar, high-level language like C, and generates a timed or UN-timed register-transfer-level (RTL) net-list that implements the same behavior. The generated RTL can then be passed through vendor-specific logic synthesis tools to obtain the final net-list. High-level synthesis provides a convenient way for a designer to specify the behavior of a circuit without worrying about low-level timing details. With the increase in the complexity of circuits application-specific processors, ASICs and FPGA-based accelerators, HLS is growing in popularity in the system design community.

In this study, we investigate the effects of compiler optimization orders on the quality of RTLs generated in HLS, for some definition of quality. The RTL generated by a HLS process is heavily influenced by the way the design is specified at the high-level. As a result, researchers have developed several source-level optimizations, some of them specific to HLS like array partitioning. Each high-level optimization can be tuned using specific parameters, and the choice of the parameters can either enable or disable another optimization. For example, a wrong array partition factor can be detrimental to loop pipelining. We have chosen three important high-level optimizations - loop unrolling, loop pipelining and array partitioning - and examined the interactions between them. We use AutoESL, an industrystandard High-level synthesis tool from Xilinx along with other EDA tools from Xilinx to analyze the effects of the optimizations under study. We describe and use a set of simple, yet effective heuristics to quickly search the space of the described optimizations and study their effects on several benchmarks.

We also study the impact of classical scalar optimizations on High-level synthesis. As AutoESL is a commercial tool that performs many optimizations internally, AutoESL is not a suitable tool to study such lower level optimizations. We motivate our study of this problem using data from xPilot [5], a research High-level synthesis tool developed at UCLA. xPilot provides the flexibility to enable and disable specific low-level optimizations, and thus is an ideal tool for our study. We evaluate several approaches, and suggest a new approach based on *lookahead* for optimizations. Our initial experiments show that latency improvements of more than 3X can be achieved by choosing the right order for an input behavioural description. We thus highlight the importance of phase ordering and the more general idea of having a strong compilation technology in a HLS tool-chain.

The rest of the thesis is organized as follows. We provide some necessary background information regarding HLS and xPilot in chapter 2. Our study on high-level optimizations are described in chapter 3. For scalar optimizations, we motivate, describe and evaluate all our methods in chapter 4. We discuss related work in chapter 5 and conclude with comments on future work in Section 6.

# CHAPTER 2

## Background

#### 2.1 High-level Synthesis

High-level synthesis (HLS), or behavioral synthesis, is the process of automatically generating cycle-accurate RTL models from behavioral specifications. The behavioral specifications are typically in a high-level language, like C/C++/Matlab. The generated RTL models can then be accepted by the downstream RTL synthesis flow for implementation using ASICs or FPGAs.

A high-level synthesis tool can be regarded as a compiler for such high-level language, with a target machine that are specifically created to run the particular program. Compared to the traditional RTL-based design flow, potential advantages of HLS include the following.

- Better management of design complexity. Raised level of abstraction leads to reduced code size and thus increased efficiency in design capture, simulation and verification.

With the increase of design complexity, this can lead to overwhelming improvement in time to market.

- Code reuse. Since a design is specified using a high-level language without much knowledge about the target platform, it is easy to re-target an existing design towards a different platform or a different frequency. In addition, libraries containing behavioral specifications of common functionalities can be built to facilitate such reuse.

- Easy design-space exploration. By applying different directives (e.g., loop unrolling, memory mapping, pipelining) and constraints (e.g., resource allocation, clock period), different architectures can be generated and evaluated easily. The designer can thus

generate a lot of design alternatives and pick the one that best fits the need of the system.

HLS has been an active research topic for more than 30 years. Early attempts to deploy HLS tools began when RTL-based design flows were well adopted. In 1995, Synopsys announced Behavioral Compiler, which accepts behavioral HDL code and connects to downstream flows. Similar tools include Monet from Mentor Graphics and Visual Architect from Cadence. This wave of tools received wide attention, but failed to widely replace RTL design. This is partly ascribed to the use of behavioral HDLs, which are not popular among algorithm and system designers and require steep learning curves. Since 2000, a new generation of HLS tools has been developed in both academia and industry. Unlike many predecessors, many of them use C-based languages to capture the design. This makes them more accessible to algorithm and system designers. It also enables hardware and software to be specified in the same language, facilitating software/hardware co-design and co-verification. The use of C-based languages also makes it easy to leverage new techniques in software compilers for parallelization and optimization. As of 2012, notable commercial C-based tools include Cadence C-to-Silicon Compiler, Calypto Catapult C (formerly a product of Mentor Graphics), NEC CyberWorkBench, Synopsys Synphony C (formerly a product of Synfora, and originating from the HP PICO project), and Xilinx AutoESL (originating from the UCLA xPilot project [5]). More detailed surveys on the history and progress of HLS are available from [13, 14, 6].

#### 2.2 xPilot

xPilot [5] is an academic HLS tool developed at UCLA. It takes as input a C function and generates an RTL Verilog module to implement the functionality. Internally, the process is divided into the following phases. Compiler transformations are first performed on the source code using LLVM [19] to obtain an optimized intermediate representation, which can be translated to a control-data flow graph (CDFG). Operation scheduling is then performed on the CDFG, and it generates a finite-state machine with data path (FSMD) model, where each

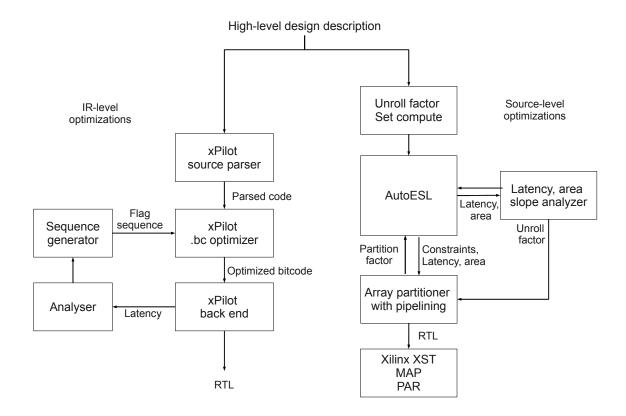

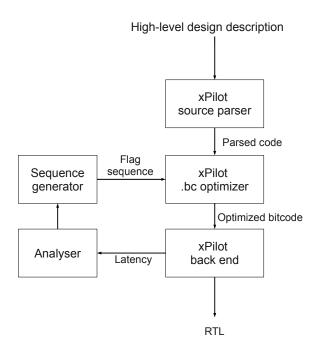

Figure 2.1: The high-level synthesis flow in xPilot.

operation is assigned to a state in the FSM. After scheduling, the cycle-accurate behavior is determined. Binding is then performed on the FSMD to allocate functional units, storage units and interconnects, and then the RTL net-list is decided. The basic flow is illustrated in Figure 2.1. Note that the flow can be organized in slightly different ways, e.g. [7] performs scheduling and binding in an iterative manner.

As mentioned earlier, the LLVM compiler framework [19] is employed as the front-end framework in xPilot. A sequence of LLVM passes, including the standard ones and one specifically designed for HLS, are performed to generate the CDFG. For a given CDFG, the scheduler in xPilot tries to minimize worst-case latency by default, under the constraints of data dependency, control dependency, clock frequency, and resource limits [8]. The scheduler tries to insert clock boundaries on certain edges of the dependency graph, in order to guarantee that the combinational delay of the logic in each state is within the target clock period, and that the number of operations of a certain type (e.g., multiplication) in each state is less than or equal to the number of corresponding functional units (e.g., multipliers). In a simplified model, operations in the same basic block are scheduled into consecutive control states; branches (including loops) are implemented as state transitions in the FSM. Thus, the resulting FSM is somewhat similar to the control-flow graph of the input function. If the control-flow graph of the input function is reducible, it is possible to estimate the worst-case latency of the module given the trip counts of loops.

As shown in Table 2.1, xPilot uses around 55 different optimizations during CDFG cre-

ation . These include standard compiler transformations like dead code elimination, algebraic re-association, common sub-expression elimination, peephole optimizations and so on. There are also certain other transformations which are unique to a HLS-based setting, one example being the *bitwidth minimization* optimization. By default, xPilot applies a pre-determined optimization sequence which has around 250 optimizations. Some optimizations like deadcode elimination are applied many times. In the default setting the user does not have an option to control these optimizations. However, for the purpose of our study, we have modified xPilot so that we have greater control over the optimization sequence used to generate the CDFG. Chapter 4 describes this aspect of our study in detail.

In order to study the effect of IR-level transformations, it is important that we have complete control over all the optimization phases that the code goes through before a CDFG is generated from it. Commercial tools like AutoESL do not provide this flexibility. Although it is possible to perform the transformations, AutoESL performs several transformations upon this input on invocation and hence our analysis would become inaccurate. As explained further in Chapter 3 and Chapter 4, we use AutoESL to study high-level transformations and xPilot to study IR-level transformations.

#### 2.3 Experiment design flow

Figure 2.2 describes the architecture of our flow, which will be described in the subsequent two chapters. Source-level transformations are studied using AutoESL. We use AutoESL's estimates in our iterative approach to quickly arrive at a good configuration for a design, and then invoke the Xilinx back-end. We use xPilot to study IR-level transformations and their impact on the latency of the RTL generated. As we are not factoring area utilization for IR-level transformations into our study here, we do not go through the Xilinx back-end.

Figure 2.2: Broad design flow used in all our experiments. xPilot is used for IR-level optimizations while AutoESL is used for source-level optimizations.

| Optimization            | Description                                 | Optimization         | Description                          |

|-------------------------|---------------------------------------------|----------------------|--------------------------------------|

| -ptrLegalization        | Convert pointers to array indices           | -interface-gen       | Interface generation                 |

| -func-inst              | Instantiate a function                      | -inst-simplify       | Operator strength reduction          |

| -globalsmodref-aa       | Mod-ref analysis for globals                | -loop-dep            | Loop dependency analysis             |

| -bitwidth               | Bitwidth analysis                           | -aggr-aa             | Aggressive alias analysis            |

| -flattenloopnest        | Flatten a loop nest                         | -function-uniquify   | Uniquify functions                   |

| -loop-merge             | Fuse loops                                  | -mergereturn         | Unify function exit nodes            |

| -mem2reg                | Promote memory to register                  | -array-seg-normalize | Array segment normalization          |

| -constprop              | Constant propagation                        | -globalopt           | Global variable optimizer            |

| $- {\rm doublePtrElim}$ | Eliminate double pointers                   | -pointer-simplify    | Simplify pointers                    |

| -directive-preproc      | Preprocess directives                       | -if-conv             | If-conversion                        |

| -rm-dup-func            | Remove duplicate functions                  | -array-normalize     | Normalize array accesses             |

| -argpromotion           | Promote 'by reference' arguments to scalars | -array-partition     | Array partitioning                   |

| -break-crit-edges       | Break critical edges in CFG                 | -loopsimplify        | Simplify loops                       |

| -dce                    | Dead code elimination                       | -loop-deletion       | Delete dead loops                    |

| -adce                   | Aggressive dead code elimination            | -syn-check           | Check synthesizability               |

| -array-map              | Perform array mapping                       | -deadargelim         | Dead argument elimination            |

| -function-inline        | Function in-lining                          | -xunroll             | Partially unroll loops               |

| -gcse                   | Global common sub-expression elimination    | -ipconstprop         | Interprocedural constant propagation |

| -scalarrepl             | Scalar replacement                          | -func-legal          | Legalize function                    |

| -ptrArgReplace          | Pointer Argment replacement                 | -deadtypeelim        | Dead type elimination                |

| -reassociate            | Algebraic re-association                    | -array-flatten       | Flatten arrays into scalars          |

| -indvars                | Canonicalize induction variables            | -condprop            | Conditional propagation              |

| -array-streaming        | Specify array as streaming                  | -instcombine         | Combine instructions                 |

| -simplifycfg            | Simplify the CFG                            | -expr-balance        | Expression tree balancing            |

| -dse                    | Dead store elimination                      | -gvn                 | Global value numbering               |

| -bitwidthmin            | Bit-width minimization                      | -loop-bound          | Loop-bound estimation                |

| -licm                   | Loop-invariant code motion                  | -basicaa             | Basic alias analysis                 |

| -simplify-libcalls      | Simplify library calls                      |                      |                                      |

Table 2.1: Benchmarks and description.

# CHAPTER 3

# Source-level Optimizations

In this chapter, we describe our study of high-level optimization interactions. By high-level optimizations, we are referring to optimizations that are typically performed on a high-level representation of a program like an abstract syntax tree (AST). In this study, we consider three optimizations commonly used on High-level synthesis designs - array partitioning, loop unrolling and loop pipelining. We have chosen these optimizations as they are most commonly employed in standard high-level designs. A quick survey of accelerators in the Open Accelerator Repository [1] shows that these three optimizations are applied in almost every design. AutoESL provides a convenient interface to specify these optimizations either via a directive in a configuration file or as a pragma in the source code itself. We first describe AutoESL's optimization options and study each of the three optimizations mentioned above individually. We then analyze interactions, draw conclusions and describe a set of simple heuristics to quickly eliminate bad choices and arrive at a good configuration.

### **3.1** AutoESL optimization options

Table 3.1 describes all the directives that AutoESL exposes to users to optimize the design. As can be seen, the solution space is large, not just because the number of directives is large, but also because each directive takes multiple parameters. The parameters used with the optimizations along with the choice of optimizations often has a significant impact on the latency and area occupied by the generated RTL.

| ration directive or as a pragma in source code. |                                                                             |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| set_directive_allocation                        | Specify instance restrictions for resource allocation                       |  |  |

| set_directive_array_map                         | Maps a smaller array into a larger array                                    |  |  |

| $set\_directive\_array\_partition$              | Partitions an array into smaller arrays or individual elements              |  |  |

| set_directive_array_reshape                     | Combines array partitioning with vertical array mapping                     |  |  |

| set_directive_array_stream                      | Use FIFOs are used instead of RAMs for arrays                               |  |  |

| set_directive_clock                             | Applies the named clock to the specified function                           |  |  |

| set_directive_dataflow                          | Specifies that dataflow optimization be performed on the functions or loops |  |  |

| set_directive_dependence                        | Allows the user to explicitly specify dependence information                |  |  |

| set_directive_expression_balance                | Rearrange expression operations to create a balanced tree                   |  |  |

| set_directive_function_instantiate              | Create a unique RTL implementation for each instance of a function          |  |  |

| set_directive_inline                            | Inline a function                                                           |  |  |

| set_directive_interface                         | Specify how RTL ports are created during interface synthesis                |  |  |

| set_directive_latency                           | Allows a maximum and/or minimum latency value to be specified on a function |  |  |

| set_directive_loop_flatten                      | Flatten nested loops into a single loop hierarchy                           |  |  |

| set_directive_loop_merge                        | Merge all the loops into a single loop                                      |  |  |

| set_directive_loop_tripcount                    | allows the user to loop trip-count                                          |  |  |

| set_directive_loop_unroll                       | Unroll a loop either completely or by a specified factor                    |  |  |

| set_directive_occurrence                        | Specify that code executes at a lesser rate than enclosing function or loop |  |  |

| set_directive_pipeline                          | Pipeline a given function or loop                                           |  |  |

| set_directive_protocol                          | Specify code region where no clock operations will be inserted by AutoESL   |  |  |

| set_directive_resource                          | Use specific library resource be used to implement a variable in the RTL    |  |  |

Table 3.1: Options available in AutoESL. Each option can either be specified as a configuration directive or as a pragma in source code.

### 3.2 Array Partitioning

Array structures in high-level design descriptions are implemented as memory blocks by default. This saves considerable amount of area than compared to using flip-flops to store individual elements, especially when the arrays are big. However, mapping arrays to available RAM resources creates resource constraints that may limit the ILP in the design. Each physical RAM block has a fixed number of read and write ports, and can therefore support only those many number of loads and stores in parallel. It is sometimes desirable to obtain a 'banked' implementation of an array, where the array elements are divided and mapped onto

Figure 3.1: Example design to study array partitioning

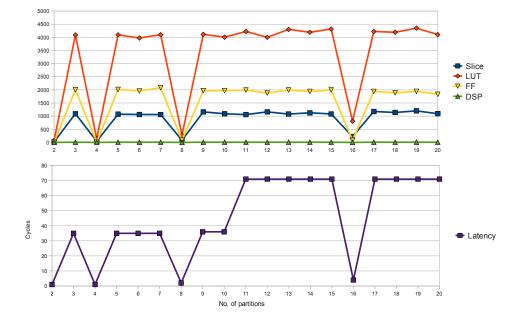

Figure 3.2: Comparison of latency and area numbers for different partitions for design in 3.2. Power-of-2 partitions perform better.

several RAM blocks. This effectively increases the number of read/write ports to the array and can alleviate the resource constraint problem. However, choosing the right splitting mechanism and number of banks is extremely crucial to obtain good benefits. A wrong partitioning choice can have a big negative impact not only by itself, but also on other optimizations. In this study, we concentrate only on cyclic distribution of array elements to different partitions.

For example, consider a simple piece of code as shown in Figure 3.2. Figure 3.2 shows the effect of various partition numbers on the latency and area. This is obviously a very simple contrived case where array partitioning is not needed, but it serves as a good example to

understand the effects of array partitioning. In particular, we make the observation that the best choices for the number of partitions seem to be powers of 2. This can be explained by observing and understanding the array partitioning optimization in action. When an array is partitioned, some additional code gets added into the design. This is required to select the right array bank and the right index within the bank. For instance, if the array *a* above has been divided into 3 partitions, each store into a[i] will require selecting the right array bank depending on the value of *i*. Hence additional code is inserted that performs *i mod* 3, based on the result of which a series of select statements will select the right bank. It turns out that the *mod* operator is very expensive as it is slow and occupies a large area. However, *mod* operator on powers-of-2 numbers are very cheap as it can be implemented by examining the appropriate number of least significant bits (LSB) and just truncating the rest. For example, to perform *i mod* 2, the least two significant bits of *i* provide the answer instantly. Similarly, least three significant bits are used to perform *i mod* 4, and so on. To perform *mod* on any other number, a 32-bit *mod* operator is required.

### 3.3 Loop Unrolling

Loop unrolling is a popular, commonly used optimization that fuses successive loop iterations into the same iteration. The number of iterations fused together is called as the *unroll factor*. Loop unrolling reduces the number of exit checks in a loop. Also, as consecutive loop iterations are merged into the same body, unrolling can potentially improve ILP. Loop unrolling also exposes more opportunities to other optimizations like scalar replacement and dead code elimination, especially in loops with a carried dependency.

in order to understand and illustrate the effects of loop unrolling from a HLS perspective, we consider two simple kernel loops shown in Figure 3.3. The first loop is a *daxpy*-style dataparallel vector computation operating on integer elements. The second loop is a sequential prefix sum implementation with a loop carried dependence across one iteration.

Figures 3.4 and 3.5 show the latency and area numbers of the loops in Figures 3.3(a) and 3.3(b) respectively. We make the following observations:

```

#define N 500

void daxpy(int a[N], int b[N], int k, int c)

{

int i;

L1:for(i=0;i<N;i++)

{

a[i] = b[i] * k + c;

}

}

(a) No dependency

#define N 500

void prefix(int a[N+1], int b[N+1], int k, int c)

{

int i;

L1:for(i=1;i<N+1;i++) {

a[i] = a[i-1] + a[i];

}

}

```

```

(b) Dependence distance = 1

```

Figure 3.3: Two simple kernels subject to loop unrolling.

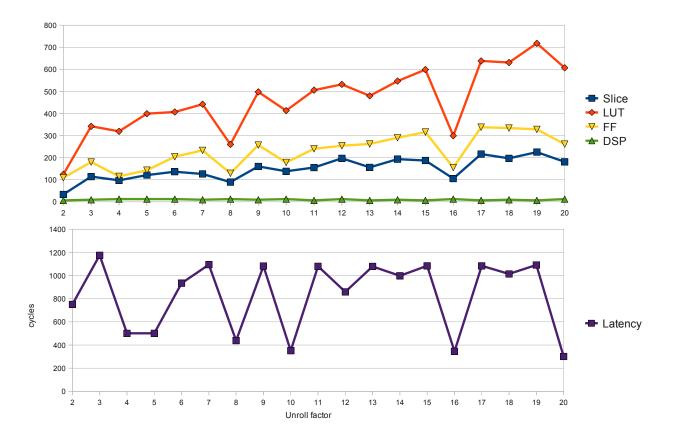

Figure 3.4: Latency and area numbers for loop in 3.3(a).

Figure 3.5: Latency and area numbers for loop in 3.3(b).

• We can observe that the best performing unroll factors in both the kernels considered are 2,4,5,8,10,16,20. While it is not immediately obvious from these results alone, further experiments with different trip-counts revealed that the set of best unroll factors consists of both the factors of the loop trip-count as well as all powers of 2 lesser than the trip count. This can be explained by understanding why the other factors are bad choices. Unrolling a loop with a number that is not a factor of the trip-count leaves some remainder iterations to be executed. In the actual implementation, this causes the addition of a number of exit checks and branches at various stages in the loop which add considerable overhead. For non-power-of-2 unroll factors, the exit checks need a full 32-bit comparator to check the index variable's size. Also, as the exit checks are dependent on the loop index variable, they introduce data dependency with the instructions that update the loop index variable. This limits the available ILP. Due to these reasons, the finite state machine created for this design during the scheduling phase is bigger with more nodes and much more complicated, thereby needing greater area (LUTs, multiplexers) to be implemented.

Limiting the unroll factor search space to just factors of the trip-count will lose some opportunities. Power-of-2 unroll factors are also good choices because they simplify exit check comparisons, needing smaller (and hence faster) comparators. Considerably lesser number of exit checks are generated for power-of-2 unroll factors, thereby not adding too much overhead in each iteration. Hence, the finite state machine of the design has fewer nodes and is relatively less complicated, thereby costing lesser area as well.

- Area consumption increases linearly with unroll factor. This is an obvious conclusion because unrolling exposes many instructions that could execute in parallel. Hence the scheduler gets extra freedom to pack more instructions into each cycle, and hence there is less re-use. Also, as each iteration in the unrolled loop is much bigger, it increases the number of nodes in the finite state machine, thus increasing area.

- Unrolling dependent loops enables optimizations like scalar replacement. As loads

from memory are expensive operations, unrolling dependent loops is a good choice. However, the reduction in latency due to saving loads quickly balances out with the increase in the size of each iteration.

• In both cases discussed here, it is clear from Figures 3.4 and 3.5 that the latency gain from unrolling (using good unrolling factors) quickly flattens out. For example, the relative gains between unroll factors 8 and 10 is far lesser than the gain between factors 5 and 8.

From the observations above, we form the following conclusions:

• The set of good unroll factors S for a loop L with a trip-count of n can be defined as follows:

$$S = \{f_i | mod(f_i, n) = 0\} \bigcup \{2^k | (k \in N) \land (2^k \le n)\}$$

(3.1)

- As area increases linearly with unroll factor, an incremental search algorithm can be used to search S for an unroll factor that provides a reasonable performance-area tradeoff. The initial latency and area occupied by the completely rolled version of the loop is considered as the starting point. Starting from the lowest unroll factor  $s_i$  in S, the loop in consideration is unrolled with factor  $s_i$ . The latency and area of the loop are measured. For area numbers, we need only a rough approximate such that relative increases in area are captured 'accurately enough'. For this purpose, we use the area numbers reported by AutoESL and skip the lengthy process of logic synthesis, map and place-route. After the latency and area numbers are obtained, we calculate the *latency slope l* and *area slope a*. Based on the values of *l* and *a*, one of the following actions are taken:

- If |l| > |a| and l < 0, then the unroll factor  $s_i$  is good. The next unroll factor will be compared to the results of  $s_i$ .

- If |l| < |a|, then the latency gain is smaller compared to the area it occupies. The algorithm stops and previous unroll factor is returned.

- If l > 0 and a > 0, then  $s_i$  is clearly a bad choice. In our current implementation, we remain optimistic by just skipping over  $s_i$  and moving on to the next unroll factor in S

The above algorithm can easily be generalized to sacrifice either latency or area. For example, in order to favour latency, we can modify the first condition by adding a weight w > 0 to the |a| parameter. This will allow unroll factors that still achieve latency reduction, but causing a greater increase in area.

### 3.4 Loop Pipelining

Software pipelining is another popular loop transformation that also attempts to exploit ILP, but in a different way. Software pipelining attempts to re-order instructions such that independent instructions across iterations are executed in parallel. The goal of software pipelining is to start execution of the second (or i + 1th) iteration in as short an interval as possible. This interval between the launch of two successive iterations is called as the *initiation interval (II)*. Software pipelining increases design throughput. In the steady state, effectively each iteration takes *II* cycles to complete. Therefore, pipelining a loop with low *II* yields a very high throughput.

To illustrate the benefit from pipelining, consider again Figure 3.3(a). Figure 3.6 compares the latency and area of the unpipelined loop with a pipelined version having an II=1. As we can see, almost a 3X reduction in latency is achieved with a modest 20% increase in the number of slices.

A common practice is to use loop unrolling and loop pipelining in tandem. If a loop with II=1 is unrolled twice and pipelined, and if the minimum II that can be achieved with the unrolled loop can still be 1, then in the steady state each iteration in the original rolled loop takes just 0.5 cycles in the pipelined version. In general, it is profitable to unroll and pipeline a loop as long as the minimum achievable II is increasing at a slower rate than the unroll factor.

Figure 3.6: Comparison: No pipelining v/s Pipelined loop (II=1)

Figure 3.7: Pipelining with unrolling loop in 3.3(a) for 65536 iterations.

Figure 3.8: Pipelining with unrolling and partitioning 3.3(a) for 65536 iterations.

However, software pipelining can be constrained by the available memory bandwidth. Consider Figure 3.7 for instance. Here the loop in 3.3(a) has been executed for a greater number of iterations (65536) for a better illustration. While unrolling is causing a linear increase in area, software pipelining is unable to achieve the required II due to a resource constraint in terms of the number of read/write ports. With appropriate array partitioning, software pipelining combined with loop unrolling proves to be a powerful combination. Figure 3.8 shows just that. We can clearly observe gains for unroll factors of 2,4 and 8, all of which happen to be factors of the trip-count (65536) and a power of 2, making them good candidates for array partitioning.

## 3.5 Approach to search optimization space

We adopt the following simple approach in order to arrive at a loop configuration that achieves a reasonable performance to area. We use the algorithm described in section 3.3 to obtain the unroll factor  $u_i$  giving best performance to area. The loop is unrolled  $u_i$  number of times and then pipelined. We leverage the detailed information that AutoESL provides regarding the minimum pipelining II achieved, resource and data constraints. If the II is constrained due to memory resources, the appropriate array is subjected to partitioning. The partition factor starts at 2 and is then doubled in subsequent iterations if the previous partition factor was insufficient to resolve the resource constraint. We have found that this approach is simple, yet is very effective in quickly arriving at optimal loop configurations.

In the next section, we evaluate our approach on a set of benchmark designs.

## 3.6 Evaluation

In this section, we evaluate the methods and heuristics presented in the previous section. We first discuss our experimental setup and flow. We then describe the set of kernels we have chosen for evaluation and discuss results.

#### 3.6.1 Experimental setup

Figure 3.9 shows the structure of our evaluation flow. For purposes of evaluation, we use AutoESL, an industry-standard High-level synthesis tool. We obtain area numbers from the EDA tool-chain provided by Xilinx. The target platform we consider here is Xilinx Virtex 5. However, there was no specific reason to choose Virtex5 over others, and the experiments can be run just as easily targeting any other platform. Currently, we can handle benchmarks whose loop trip-counts can be determined at compile-time.

Figure 3.9: Structure of our experimental flow.

## 3.6.2 Results

We tested our approach on five different kinds of kernels taken from the Open Accelerator repository [1] and MiBench [15]. We have hand-chosen different kernels in order to achieve a broader evaluation coverage. The benchmarks are described below :

- adpcm\_decoder: Kernel function of the ADPCM decoding algorithm. The main loop consists of a carried dependency through a scalar variable. Every iteration reads one element from an *inbuffer* and writes one element to the *outbuffer*. The trip-count of this main loop is 500.

- daxpy: A simple kernel function performing the vector operation A = Bk + c, where k and c are integer constants. The size of vectors A and B is 500, and the loop trip-count is 500.

- prefix: A kernel function calculating prefix sum on a vector of integers. The size of the array and the loop trip-counts are both 500. The loop carries a dependency through the vector.

- segmentation: Kernel performing one compute step in an image segmentation algorithm. The kernel consists of a nested loop with lots of floating point computations and *sqrt* operations. This loop is data-parallel. We currently handle the innermost loop in the nest. AutoESL automatically flattens the loop nest if any outer loop is attempted to be pipelined. We do not explore that here currently. The inner loop runs 64 times.

- smithwaterman: An implementation of the Smith-Waterman algorithm. This algorithm also contains nested loops with the core innermost loop having a trip-count of 76. This implementation contains many two-dimensional arrays and the loop body performs considerably many array loads and stores, more than any other benchmark that we have considered here. The loop carries a data dependency through an array.

| Benchmark     | Unroll factor | No. of partitions | Numbers         |       |      |               |    |       |         |        |

|---------------|---------------|-------------------|-----------------|-------|------|---------------|----|-------|---------|--------|

| Denullilark   |               |                   |                 | Slice | LUT  | $\mathbf{FF}$ | II | Depth | Latency | ER     |

|               | 4             | 1                 | Baseline        | 200   | 588  | 217           | -  | -     | 2502    | 1      |

| adpcm_decoder |               | 1                 | Baseline + PP   | 224   | 741  | 234           | 2  | 5     | 1006    | 2.22   |

|               |               | 1                 | U4 + PP         | 619   | 2009 | 471           | 8  | 11    | 1006    | 0.8035 |

|               | 8             | 1                 | Baseline        | 21    | 80   | 62            | -  | -     | 1501    | 1      |

| daxpy         |               | 1                 | Baseline $+ PP$ | 26    | 92   | 75            | 1  | 3     | 504     | 2.405  |

|               |               | 4                 | U8 + PP         | 89    | 324  | 315           | 1  | 3     | 67      | 5.286  |

|               | 8             | 1                 | Baseline        | 29    | 113  | 80            | -  | -     | 1501    | 1      |

| prefix        |               | 1                 | Baseline + PP   | 43    | 166  | 91            | 2  | 3     | 1003    | 1.009  |

|               |               | 8                 | U8 + PP         | 109   | 307  | 375           | 2  | 4     | 130     | 3.072  |

|               | 32            | 1                 | Baseline        | 31    | 110  | 65            | -  | -     | 8321    | 1      |

| segmentation  |               | 1                 | Baseline + PP   | 43    | 153  | 88            | 1  | 2     | 4100    | 1.463  |

|               |               | 16                | U32 + PP        | 173   | 522  | 160           | 1  | 3     | 132     | 11.296 |

|               | 4             | 1                 | Baseline        | 26    | 102  | 46            | -  | -     | 52281   | 1      |

| smithwaterman |               | 1                 | Baseline + PP   | 19    | 73   | 46            | 2  | 3     | 11708   | 6.110  |

|               |               | 1                 | U4 + PP         | -     | -    | -             | -  | -     | -       | -      |

Table 3.2: Comparison between baseline and heuristically optimized benchmark versions against latency and area using ER. The unroll and partition factors used are also specified.

Table 3.2 shows the optimal factor obtained, number of partitions required, latency and area numbers for all benchmarks. Each benchmark is reported under three configurations:

Baseline - where the benchmark was run without any high-level optimization, Baseline + PP - baseline with pipelining, where the main loop was pipelined with the required number of array partitions, and U(num) + PP - Unroll by obtained unroll factor with pipelining along with required number of array partitions.

We define the *efficiency ratio* ER as the latency-area product, as follows:

$$ER = \frac{latency_b * area_b}{latency * area} \tag{3.2}$$

Here,  $latency_b$  and  $area_b$  are the latency and area numbers of the baseline respectively. We use the number of slices occupied as the representative for area of a design.

The ER is basically a ratio of the speedup v/s area increase, and gives an indication about the how well the area has been utilized. We can see the ER increases with increase in speedup and decrease in area utilization. The higher the ER, better is the result.

We make the following observations:

- *adpcm\_decoder* does not benefit from unrolling. In fact, unrolling degrades its performance as can be seen by its *ER*. This can be explained by examining the structure of the loop. As mentioned before, the *adpcm\_decoder* loop contains a dependency across iterations carried over by a scalar. Due to the carried constraint, unrolling the loop just concatenated more instructions from the next iteration to the end of the loop body. As a result, the II scaled linearly with increase in the unroll factor, thereby mitigating the effects of software pipelining. Hence the best result for this benchmark is when unrolling is at its minimum i.e., the loop is completely rolled. Also, as the constraint is a data dependency, array partitioning cannot help alleviate the constraint.

- Benchmarks *daxpy* and *prefix* perform well, with *ERs* of 5.2 and 3 respectively. It is to be noted that the achieved performance is due to the combined effect of array partitioning, loop unrolling and software pipelining. Further experiments showed a decrease in performance if either one of these parameters were altered. *Prefix* has a slightly smaller gain than *daxpy* due to the carried constraint in the loop.

- Segmentation achieves a remarkable benefit with its configuration with an ER of around 11. As the core loop is data parallel, the only constraint to achieve minimal II would be array resources, and a partitioning factor of 16 resolves all resource constraints.

- Smithwaterman's numbers are surprising. The area occupied by the pipelined baseline version is lesser than the unpipelined version. This suggests that the schedule is utilizing the hardware very efficiently. Also, SmithWaterman benefits from pipelining with an ER of 6. Using our heuristics, an unroll factor of 4 was found to give the best performance to area value. However, pipelining the unrolled loop resulted in an AutoESL crash due to an internal bug in the tool.

Although some benchmarks we have chosen to evaluate our approach are relatively small in size, they are kernels which represent real-world computation. We see that the right combination of partition factor, unroll factor and pipelining can improve the performance by an order of magnitude.

# CHAPTER 4

## **IR-level** optimizations

In this chapter, we describe our study on the effects of phase-ordering of IR-level optimizations. Here, we use the latency of the RTL as the metric representing the quality of the RTL. We first describe the various optimizations used and how we chose them. We then describe several techniques that we have implemented and evaluated. We also compile and produce binaries using the same sequence used in HLS, simulate them on a cycle-accurate out-of-order processor simulator and compare the ranks of each sequence on a processor and in HLS.

## 4.1 Motivation

We motivated our study by discussing a simple example in Chapter 1. In this section we study the same example along with another simple design pattern in the HLS perspective only, to highlight the significance of compiler optimizations on the generated RTL.

Consider the two example programs shown in Figures 4.1 and 4.2. We consider the same set of optimizations that we consider in Chapter 1.

- -gvn (g): Global value numbering.

- -mem2reg (m): Promote memory to register.

- -indvars (i): Canonicalize induction variables.

Figure 4.3 provides the performance of three combinations - *img*, *mig* and *gim* on the two benchmarks. Two things are evident in this example:

```

void add(int i[20], int o[2])

{

int iter;

o[0] = o[1] = 0;

for(iter = 1; iter <= 20; iter++)

{

if(i[iter]%2 == 0) {

o[0] += i[iter];

o[1] += i[iter];

}

}

}</pre>

```

Figure 4.1: Motivational example - simple addition.

```

void fact(int *i, int *o)

{

int n = *i;

int fact = 1;

int iter;

for(iter = 1; iter <= n; iter++) {

fact = fact*iter;

}

*o = fact;

}</pre>

```

Figure 4.2: Motivational example - factorial.

Figure 4.3: Latency comparison for different optimization orders for examples in Figure 4.1 and Figure 4.2.

- There is a noticeable variance in the latencies of the RTLs generated with different optimization combinations. The latency of *add* varies from 12 to 62 while the latency of *fact* varies from 12 to 23

- The *best* sequence is different for the two programs. In case of *add*, it is sequence *gim* whereas in case of *fact*, it is *img*.

Although the example considered above is small, it helps illustrate the effect that the order of application of transformations has on the resulting RTL's latency.

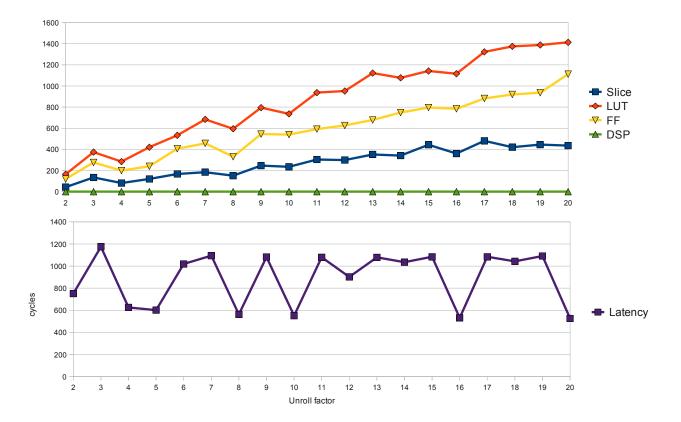

As a second case study, we examined a benchmark *matrixmul* that performs tiled matrix multiplication. This benchmark is greater in terms of both size and complexity than the example above. We considered 68 different optimizations and applied several transformation sequences on *matrixmul*, where each transformation sequence was of length 200. All optimizations were applied using xPilot's LLVM-based HLS front-end. The transformed output from xPilot was passed through AutoESL, a commercial High-level synthesis tool. We further synthesized the generated RTLs using XST, Xilinx's logic synthesis tool in order to get accurate area estimates.

Figure 4.4 shows the normalized latency and area numbers for a few sequences. We can

Figure 4.4: Normalized latency and area numbers for *matrixmul* obtained from AutoESL and Xilinx back-end.

see that a reduction in latency of almost 2X can be obtained, with a very modest increase in area. This shows that applications can derive significant benefit with the correct optimization order.

Another aspect that can be noticed is the irregularity and discreteness of the space of optimizations. As can be seen in later sections, latency does not take on a spread of values for different optimization sequences; there are discrete clusters of good and bad sequences. Such a *step-constant* nature of the optimization sequence space is not a new finding. Previous research [18][4] has shown the same result. This result suggests that the latency is affected only by a few "critical" optimizations. Section 4.2 provides further details on our investigation of this property.

We used AutoESL synthesis tool only as part of our initial study to explore the possible gains that could be achieved. While the encouraging results from such a tool provides a strong motivation, most commercial tools are licenced and are not open source. Also, it is likely that the tool performs many transformations on the input which cannot be turned off, and hence it would not be possible to correctly evaluate the sequences that we use to transform the input before passing it through the tool. On the other hand, xPilot is an academic tool which provides us with maximum flexibility to accurately test the effect of phase orders. Therefore, for all our experiments mentioned henceforth, we use only xPilot.

## 4.2 Methodology

In this section, we first describe the various optimizations used and how we chose them. We then describe several techniques that we have implemented and evaluated to search the optimization search space. We introduce the simple idea of *lookAhead* in Section 4.2.4. We then describe a technique that we tried to speed up our iterative algorithm using a static latency estimation model.

#### 4.2.1 Optimizations considered

In the default setting, xPilot applies close to 250 transformations from a set of 68 unique optimizations. While most of the optimizations in this set are standard compiler transformations like global value numbering, strength reduction etc., a few optimizations are specific to High-level synthesis. One example for such an optimization is the *bitwidth minimization* optimization. Unlike a conventional CPU, reconfigurable fabric like FPGAs can support arbitrary data sizes. This optimization can be very beneficial, as shown section 4.3. Intuitively, say we have an integer multiply instruction a \* b in the input program. If the maximum range of values taken by a and b can be statically estimated to not exceed 256, an 8-bit multiplier can be used to perform this operation as opposed to a 32-bit adder, thereby conserving area and also decreasing latency.

As mentioned earlier, the space of optimization sequences is discrete. To investigate this, we generated 1000 random sequences of length 200, where optimizations were taken from the same set that is used by Xpilot. While this is by no means exhaustive, it is sufficient for understanding some aspects of the solution space. Figure 4.5 shows the scatterplot of the average latencies obtained from the sequences. One can immediately observe the discrete horizontal steps and blank spaces in-between. We repeated the same experiment on multiple

Figure 4.5: Scatterplot of latencies for *matrixmul*

benchmarks, only to see a similar result.

Intuitively, such behavior is caused when a few optimizations are far more important than the others. In order to empirically support our claim, we randomly chose 100 sequences and examined the effect of each optimization on latency in a step-wise fashion, with the hope of finding the critical jump points. In other words, if the sequence under consideration is *abcde*, we examined the change in latency due to a alone, then ab, then abc and so on. Table 4.1 shows the result of one such examination.

Table 4.1 clearly shows the critical points where there is an observable change in latency. Similar experiments with other sequences and other benchmarks yield similar results with discrete changes. Although the order of optimizations was different in each case, there was a large overlap among the set of optimizations occurring in such critical points. We performed this exercise on 100 randomly chosen samples from five different benchmarks, and listed

| Position | Optimization  | Latency change (cycles) | Final (cycles) |

|----------|---------------|-------------------------|----------------|

| 2        | instcombine   | -27000                  | 708094         |

| 22       | inst-simplify | +27000                  | 735094         |

| 40       | loop-deletion | +3520                   | 738614         |

| 42       | indvars       | -6682                   | 731932         |

| 66       | gcse          | +316536                 | 1048468        |

| 68       | gvn           | -647792                 | 400676         |

| 74       | simplifycfg   | -400627                 | 49             |

Table 4.1: Step-wise analysis of one sequence. Reported latency is reported (in cycles) from xPilot. We used a target clock period of 50 ns.

the most commonly occurring optimizations. Table 4.2 gives a brief description of all the short-listed optimizations. From here on in this paper, we restrict all our experiments to this restricted subset of optimizations.

### 4.2.2 Random search

In our implementation of random search, we generate random sequences containing up to 25 optimizations each. We allow repetitions of optimizations, since it resembles a more natural setting. We generated and evaluated 5000 random sequences for each of the benchmarks considered. Section 4.3 has further information on our evaluation.

#### 4.2.3 Genetic Algorithm

We implement a genetic algorithm to search the space of optimization sequences using latency as the minimization cost function. Genetic algorithms are iterative algorithms that converge to a solution mimicking the process of natural evolution. In our implementation, we chose to have a randomly generated initial population of 20 sequences, each of which can have as many as 25 optimizations. We repeat the iterative search process for 500 generations. In each iteration, all the sequences in the population are evaluated and ranked. The sequence

| name                   | description                             |

|------------------------|-----------------------------------------|

| adce (a)               | aggressive dead code elimination        |

| bitwidthmin (b)        | bitwidth minimization                   |

| condprop (p)           | conditional propagation                 |

| constprop $(k)$        | constant propagation                    |

| dse (e)                | dead store elimination                  |

| gcse(c)                | global common subexpression elimination |

| gvn (n)                | global value Numbering                  |

| indvars (v)            | canonicalize induction variables        |

| instcombine (i)        | combine redundant instructions          |

| inst-simplify $(t)$    | operator strength reduction             |

| loop-deletion (d)      | delete dead loops                       |

| loop-preproc (o)       | Loop preprocess                         |

| loop-simplify (l)      | canonicalize natural loops              |

| mem2reg (m)            | promote memory to register              |

| ptr-legalization $(r)$ | convert pointers to array indices       |

| simplifycfg (s)        | simplify the control-flow graph         |

| xunroll (x)            | partially unroll loops                  |

Table 4.2: Subset of optimizations and descriptions.