# A sub-Hertz nanopower low pass filter

Esther Rodriguez-Villegas, Senior Member, IEEE, Alexander J. Casson, Member, IEEE, and Phil Corbishley

Abstract—This brief presents a first order low pass filter topology capable of providing cut-off frequencies down to 2 mHz with a power consumption of 5 nW. The circuit is intended for signal conditioning applications, particularly for use with very low frequency physiological signals in low power portable medical equipment. To achieve the low frequency cut-off the filter is based around the use of a clocked transconductor which provides a low transconductance while using a relatively high bias current level. The circuit is implemented in a 0.35  $\mu$ m technology with a 1 V supply and has a measured 32  $\mu$ V<sub>RMS</sub> of noise and 64 dB dynamic range. In terms of power consumption and cut-off frequency the reported filter outperforms previous filters from the literature.

*Index Terms*—Analog filtering, clocked transconductor, low power, biomedical signal conditioning.

## I. INTRODUCTION

C UB-Hertz low pass filters have many applications in sensor interfaces [1] and biomedical signal processing units [2]. Sensor interfaces are often applied to slowly varying phenomena such as flow rate, pressure, chemical concentration and temperature, and sub-Hertz filters are required for antialiasing filters, active gain controllers and isolation of the wanted signal in these applications. Similarly, biomedical signals are usually found in the 10 mHz to 100 Hz frequency range [3] and hence require sub-Hertz frequency filters to condition the signal before processing. For example, the filter presented here was designed as part of the breathing monitoring device presented in [4] (although it is not restricted to this use). In the system of [4], sub-Hertz frequency filters are used to smooth the signal after rectification and for finding the average of the signal. Sub-Hertz filters are used for a similar purpose in [5].

However, despite their utility, creating large time constant low pass filters on-chip is a challenging problem. To implement large time constants switched capacitor based topologies require large capacitor ratios [6], and a sufficiently high power supply must be used to achieve an acceptably low switch onresistance [2].

In  $g_m$ C based topologies the cut-off frequency is generally determined by the ratio  $g_m$ /C, where C is the integrating capacitance present. However, area limitations restrict the maximum capacitance that can be present on-chip to pico-Farad

E. Rodriguez-Villegas and A. J. Casson are with the Circuits and Systems Research Group, Electrical and Electronic Engineering Department, Imperial College London, UK email: ({e.rodriguez,acasson}@imperial.ac.uk)).

P. Corbishley is with Nordic Semiconductor, Trondheim, Norway.

The research leading to these results has received funding from the European Research Council under the European Community's 7<sup>th</sup> Framework Programme (FP7/2007-2013) / ERC grant agreement no. 239749.

Copyright (c) 2011 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending an email to pubs-permissions@ieee.org. values, limiting the minimum cut-off that can be achieved. Large off-chip capacitors can be used, but for a given cutoff frequency the required  $g_m$  value is decreased, decreasing the transconductor output current. On-chip currents down to femto-Amp levels are feasible, but moving off-chip the current is limited by the leakage currents in the bondpads to pico-Amp levels [7]. Larger  $g_m$  and C values must thus be used to keep the output current above this limit, but at the cost of power consumption.

For a fully on-chip solution, impedance scaling techniques, placing the capacitor across an inverting amplifier and utilising the Miller effect, can be used to increase the effective capacitance although this introduces increased complexity, power consumption and noise [8], [9]. More commonly, to achieve low frequency on-chip cut-offs the transconductor unit is modified to reduce the effective  $g_m$  value, and several techniques for this have been previously reported.

For example, floating gates can be added to the transconductor input transistors to capacitively attenuate the effective input voltage at the cost of increasing the input referred noise. [10] used this technique to achieve a 500 mHz cut-off low pass filter. Alternatively, [8], [11] made use of transistors in the triode region to perform the voltage-to-current conversion. [11] reported a 1.5 Hz cut-off low pass filter based upon this, but an additional feedback amplifier was required to keep the conversion transistors in the triode region. [12] used bulk driven (as opposed to gate driven) input transistors for the transconductor to take advantage of the generally lower  $q_{mh}$ transconductance. A 170 mHz cut-off was achieved, but at the expense of a reduced input impedance. Simultaneously, [12] made use of current division which is also used in [1], [8], [13], with [1] reporting a 53 mHz cut-off filter. The technique uses current mirrors or splitters to reduce the output current from the transconductor and hence the effective transconductance, but generally comes at the cost of circuit area. Current cancellation, where the transconductor current is reduced by adding input transistors of different sizes and cross connecting their drain terminals can also be used [14]. However, this use of partial positive feedback relies on very good matching for successful operation. Finally, [2], [15] cascaded transconductance amplifiers with transresistance amplifiers, each of differing value, such that the overall transconductance was reduced. [2] reported a 100 mHz cut-off integrator, but it is noticeable that reported circuits using this technique do not supply noise or distortion figures. These are likely to be poor since every section adds noise and distortion and cascading many times will result in low dynamic range.

This brief presents a new low pass filter topology based on a hybrid approach between switched capacitor and  $g_m$ C filters. Here a clocked transconductor is used to form the reduced transconductance  $g_m$  element in a  $g_m$ C filter. The duty cycle

Manuscript received 11<sup>th</sup> November 2010; revised 10<sup>th</sup> February 2011; accepted 21<sup>st</sup> March 2011.

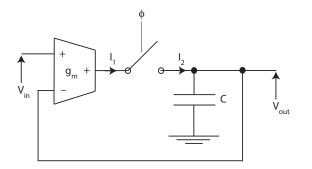

Fig. 1. Principle of operation of the proposed low pass filter. A standard first order  $g_mC$  filter is modified to include a switch between the transconductor output and the capacitor, reducing the effective transconductance.

of the clock then determines the effective transconductance and allows easy digital control of the filter cut-off frequency. In this brief, Section II describes the operation and design of the new low pass filter topology. Experimental results are then presented and compared to other filters from the literature in Section III. Finally conclusions are given in Section IV.

#### II. THE CLOCKED TRANSCONDUCTOR FILTER

## A. Principle of operation

Fig. 1 shows the basic principle of the proposed low pass filter topology: it is based around clocking the output of a standard transconductor element. A standard transconductor is placed in a feedback loop arrangement with a capacitor forming a first order  $g_m C$  low pass filter and a switch is then added between the output of the transconductor and the capacitor. This switch allows the output of the transconductor to be connected to and disconnected from the capacitor and feedback loop. As the output current from the transconductor,  $I_1$ , can only flow into the capacitor when the switch is closed the average current that flows into the capacitor,  $I_2$ , is reduced. If  $\delta$  is the duty cycle of the switch  $\phi$ , then

$$I_2 = \delta \times I_1. \tag{1}$$

As  $I_2$ , the effective output current of the transconductor is reduced, the effective transconductance of the transconductor is reduced by the same amount. Furthermore, this reduction in transconductance is achieved in the time domain and may be precisely controlled via the clock used to control the switching operation. This allows easy digital control of the transconductance and the filter cut-off frequency. For correct operation the clock frequency used must be sufficiently high so that the clock harmonics fall out of band. The precise clock frequency used is not important however, and this requirement is generally trivial to satisfy in a sub-Hertz filter where the passband frequencies may be orders of magnitude lower than the clock frequency.

The introduction of the switch in Fig. 1 also increases the effective output resistance of the transconductor. For a first order  $g_m C$  filter the time constant,  $\tau$ , is given by

$$\tau = \frac{C}{g_o + g_m} \tag{2}$$

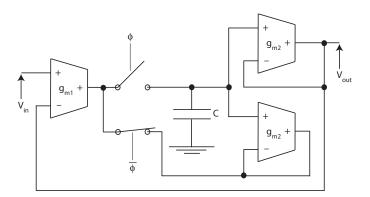

Fig. 2. The complete low pass filter incorporates two buffers to provide a path for the transconductor output current when the switch  $\phi$  is open and to mitigate the effect of charge injection.

where  $g_o$  is the transconductor's output conductance. For  $\tau$  to be tunable via the bias current the  $g_m$  term in (2) must dominate over  $g_o$ , which can be problematic to achieve as the effective value of  $g_m$  is reduced. The proposed topology overcomes this as when the switch is open  $g_o$  does not affect the capacitor voltage since the two nets are isolated. The capacitor is only loaded by  $g_o$  when the switch is closed, and hence the effective output conductance of the transconductor also scales with the duty cycle. Since both  $g_m$  and  $g_o$  scale at the same rate, if the transconductor  $g_m$  dominates  $g_o$  when no duty cycle is present then it will still dominate in the proposed topology. No additional design of the transconductor for low  $g_o$  values is required.

#### B. The complete low pass filter

In reality the simplistic diagram of Fig. 1 does not obey Kirchoff's current law: when the switch is open the transconductor's output current has nowhere to flow. This would cause the output of the transconductor to saturate at (or near) the supply rails as no output current could be provided. To overcome this two buffer cells are introduced as shown in Fig. 2. The first buffer is placed between the capacitor and the output/feedback node, Vout, to isolate the capacitor node from the load. The second buffer is then placed between the output of the filter transconductor  $(g_{m1})$  and the capacitor via a second switch,  $\phi$ , in anti-phase to the main switch. This second buffer thus provides a path for the output current of  $g_{m1}$  when the  $\phi$  switch is open. When  $\phi$  is open,  $\phi$  is closed and the output of  $g_{m1}$  is fixed to the same voltage as the capacitor, but without any current from  $g_{m1}$  flowing into the capacitor. Thus the voltage at the output of  $g_{m1}$  stays approximately constant regardless of whether the current from it is flowing into the capacitor or not, preventing the output of the transconductor changing between the supply rail voltages and the voltage at the capacitor each time the switch is toggled.

This arrangement also reduces the effects of charge injected through the switches. When  $\phi$  switches, charge is injected predominately into the capacitor C as this offers the lowest impedance. For low frequency operation C is generally large, and the resulting voltage spike produced is hence small. When  $\overline{\phi}$  switches, charge is predominately injected into a buffer connected in negative feedback. The load capacitance seen is thus both the buffer output capacitance and the input capacitance of the negative input, increasing the total capacitance present. Additionally, both switches can operate at frequencies much higher than the bandwidth of the filter and so remaining voltage ripple can be easily removed if required.

#### C. Implementation

For on-chip implementation a 39.8 pF poly-poly capacitor is used for C and the switches  $\phi$  and  $\overline{\phi}$  are implemented as single minimum sized NMOS FETs. Since the voltages across the switches are small and remain at approximately half the supply voltage the estimated 3 M $\Omega$  on-resistance of these is high, but sufficient for the application.

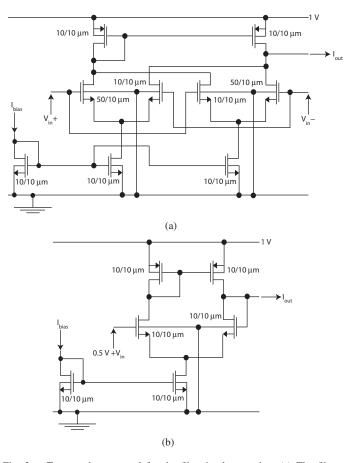

The transconductors used for  $g_{m1}$  and  $g_{m2}$  are shown in Fig. 3. The  $g_{m1}$  transconductor, Fig. 3(a), consists of two differential pairs connected in a doublet arrangement with input transistor width ratio 5:1. This ratio is chosen to maximise the differential input range for a Total Harmonic Distortion (THD) of 1% [16]. For nominal operation the bias current is set at 200 pA. The  $g_{m2}$  transconductors for the buffers, Fig. 3(b), consist of basic differential pairs with their outputs connected to the negative inputs for unity voltage gain. The bias current is set at 1 nA and since these buffers operate well below their bandwidth their inputs are approximately equal and they contribute little to distortion in the overall filter.

To bias the circuit an internal current mirror with current scaling is included on-chip so that only one external current source, set at 1 nA, needs to be applied. The designed transconductors are not temperature compensated and as such either PTAT (Proportional To Absolute Temperature) biasing or a temperature dependent duty cycle is required to give correct operation over large temperature changes. A suitable 2 nW current source is reported in [17], [18] but is not included here. For testing, the clock and bias current are generated off-chip using an HP8112A and Keithley 236 respectively and the filter output voltage is buffered to drive the test equipment. Neglecting the digital clock and bias generation the overall circuit thus draws approximately 5 nA from the 1 V supply.

### **III. EXPERIMENTAL RESULTS**

The proposed clocked transconductor based low pass filter has been fabricated in the austriamicrosystems 0.35  $\mu$ m, single well, 2 poly, 3 metal process, and a micro-photograph of the fabricated circuit is given in Fig. 4.

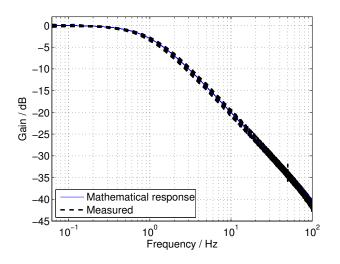

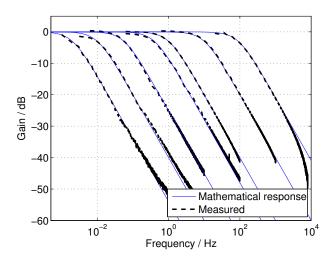

Fig. 5 then shows the Bode magnitude response from 10 measured samples using a 200 pA/1 nA bias, and 1 kHz clock with 10% duty cycle. This gives a relatively high 1 Hz cutoff frequency for increased measurement speed. Two readings from each chip are present to demonstrate the repeatable operation of the filter, with 10 averages taken per reading. The mean 3 dB cut-off frequency present is 1 Hz with a standard deviation of 0.06 Hz.

Under the same biasing conditions the output noise integrated between 20 mHz and 1 Hz has been measured as 32  $\mu$ V<sub>RMS</sub> and the largest in-band THD measured as 0.96% for a 140 mV<sub>pp</sub> 1 Hz input signal. The filter dynamic range

Fig. 3. Transconductors used for the filter implementation. (a) The filter transconductor  $(g_{m1})$  uses a doublet arrangement with 5:1 width ratio. A 0.5 V common mode signal is required at the input for correct operation. (b) The buffer transconductors  $(g_{m2})$  are differential pairs in a unity gain configuration.

Fig. 4. Micro-photograph of the fabricated circuit.

is thus in excess of 60 dB. These measured filter parameters are summarised in Table I.

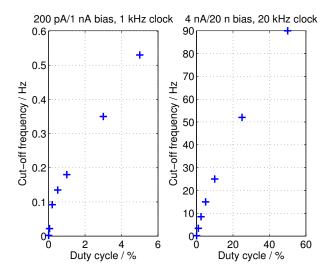

The tuning range of the filter is illustrated in Fig. 6. Using the same bias conditions as above, decreasing the duty cycle to 0.0025% lowers the filter cut-off frequency to 2 mHz. 0.0025% is a low duty cycle, but from a 1 kHz clock the 25 ns clock high-time corresponds to a 20 MHz component, which is still feasible to implement. Alternatively, increasing the bias current to 4 nA/20 nA and the clock frequency to 20 kHz with a 50% duty cycle, a 90 Hz cut-off is achieved. Overall, a greater than a four decade range in tunablity is possible and the cut-off tuning curve is shown in Fig. 7. The topology is thus highly versatile for use in a range of applications.

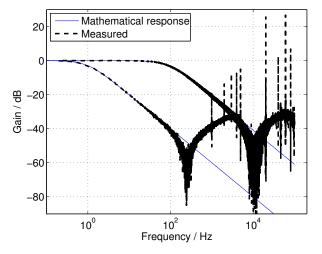

Note, however, that a high frequency parasitic is present:

Fig. 5. Bode magnitude responses from 10 measured samples (2 measurements per sample) show robust low frequency operation of the filter.

Fig. 6. Tuning range of the fabricated filter goes from 2 mHz to 90 Hz cutoffs. The following settings are used for these results in the format [Bias, Clock frequency, Duty cycle, Cut-off frequency]: [200 pA/1 nA, 1 kHz, 0.0025%, 2 mHz], [200 pA/1 nA, 1 kHz, 0.025%, 10 mHz], [200 pA/1 nA, 1 kHz, 10%, 1 Hz], [2 nA/10 nA, 10 kHz, 0.025%, 56 mHz], [2 nA/10 nA, 10 kHz, 0.25%, 400 mHz], [2 nA/10 nA, 10 kHz, 10%, 10 Hz], [4 nA/20 nA, 20 kHz, 50%, 90 Hz].

its effect can be seen at approximately 5 kHz for the 90 Hz cut-off filter in Fig. 6. Also, Fig. 8 illustrates the gain of the filter for input frequencies from the pass band to five times the clock frequency used. This shows that all input frequencies are attenuated, except at the clock frequency and harmonics of it. For correct operation the amplitude of inputs at these frequencies should thus be kept low. Since the clock frequency can be set to be much higher than the bandwidth of the signals typically encountered in low frequency applications this constraint is generally not difficult to satisfy.

Finally, Table II compares the results obtained here to other low frequency low pass filters and integrators reported in the literature. For conciseness only implementations with experimental results that have been reported since the year 2000 are included in this table. It can be seen that the filter

Fig. 7. Tuning curve showing how the filter cut-off frequency is controlled.

Fig. 8. Response of the filter to inputs at frequencies up to five times the clock frequency for the [200 pA/1 nA, 1 kHz, 10%, 1 Hz] and [4 nA/20 nA, 20 kHz, 50%, 90 Hz] bias conditions.

presented here has the lowest frequency cut-off, supply voltage and power consumption of all of the considered designs. This is achieved without a noticeable increase in area. The proposed clocked transconductor topology is thus highly suitable for use in low power, low voltage sensor interfaces and in portable medical instrumentation.

#### **IV. CONCLUSIONS**

A very low frequency, going down to sub-Hertz cut-offs, low pass filter topology has been presented showing excellent characteristics when compared with results in the literature. Operation is based upon using a switch at the output of a transconductor in a  $g_mC$  filter to decrease the value of the transconductance and to increase the output resistance. This allows very low transconductance values to be achieved, and the clock signal facilitates easy digital tuning. Measured results showing sub-Hertz operation with a current draw of 5 nA have been presented. In comparison to previous low pass filters from

TABLE II

Comparison of proposed topology performance with other reported low frequency low pass filters.

| Ref.      | CMOS<br>process /<br>µm | Minimum<br>cut-off / Hz | Filter order | Power con-<br>sumption /<br>W | Supply<br>voltage / V | Dynamic<br>range / dB | Area / mm <sup>2</sup> | Integrating<br>capacitance<br>per pole / F |

|-----------|-------------------------|-------------------------|--------------|-------------------------------|-----------------------|-----------------------|------------------------|--------------------------------------------|

| [19]      | 0.35                    | 35.0                    | 1            | _                             | 3.2                   | _                     | 0.025                  | 25f                                        |

| [8]       | 0.80                    | 02.4                    | 6            | $010\mu$                      | 3.0                   | 60                    | 1                      | 05p                                        |

| [11]      | 0.35                    | 01.5                    | 2            | $165\mu$                      | 3.3                   | 60                    | 0.336                  | 52.5p                                      |

| [10]      | 0.80                    | 500m                    | 2            | $002\mu$                      | 1.5                   | 70                    | _                      | _                                          |

| [7]       | 0.35                    | 500m                    | 1            | _                             | _                     | _                     | _                      | 100f                                       |

| [13]      | 0.80                    | 302m                    | 1            | 113n                          | _                     | 65.4                  | 0.2                    | 50p                                        |

| [20]      | 0.35                    | 250m                    | 2            | _                             | 3.0                   | 40                    | _                      | 29p                                        |

| [21]      | 0.50                    | 180m                    | 1            | 77.4n                         | _                     | 61.4                  | 0.035                  | 15p                                        |

| [12]      | 1.20                    | 170m                    | 2            | $08.2\mu$                     | 2.7                   | 70.5                  | 0.06                   | $10n^a$                                    |

| [2]       | 0.80                    | 100m                    | 1            | 230n                          | 3.0                   | _                     | 0.1                    | 70p                                        |

| [1]       | 1.00                    | 075m                    | 1            | _                             | 5.0                   | _                     | 0.25                   | 10p                                        |

| This work | 0.35                    | 002m                    | 1            | 005n                          | 1.0                   | 63.8                  | 0.07                   | 40p                                        |

<sup>a</sup>Off-chip

TABLE I SUMMARY OF MEASURED CIRCUIT PERFORMANCE.

| CMOS process technology                                  | 0.35 μm             |  |  |

|----------------------------------------------------------|---------------------|--|--|

| Power supply                                             | 1 V                 |  |  |

| Area                                                     | $0.07 \text{ mm}^2$ |  |  |

| Nominal current consumption                              | 5 nA                |  |  |

| Output noise (20 mHz – 1 Hz)                             | 32 $\mu$ Vrms       |  |  |

| THD (1 Hz, 140 mV <sub>pp</sub> input)                   | 0.96%               |  |  |

| Dynamic range                                            | 63.8 dB             |  |  |

| Input common mode range                                  | 400 mV - 550 mV     |  |  |

| PSRR+ (1 Hz, 100 mV <sub>pp</sub> V <sub>DD</sub> input) | -55 dB              |  |  |

| Cut-off tuning range                                     | 2 mHz – 90 Hz       |  |  |

the literature the proposed topology provides the lowest cutoff and power consumption seen, in addition to a very wide tuning range.

### REFERENCES

- [1] P. Bruschi, G. Barillaro, F. Pieri, and M. Piotto, "Temperature stabilised tunable Gm-C filter for very low frequencies," in *IEEE ESSCIRC*, Leuven, September 2004.

- [2] R. Rieger, A. Demosthenous, and J. Taylor, "A 230-nW 10-s time constant CMOS integrator for an adaptive nerve signal amplifier," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1968–1975, 2004.

- [3] C. Ray, *Medical Engineering*. Chicago: Year Book Medical Publishers, 1974.

- [4] P. Corbishley and E. Rodriguez-Villegas, "Breathing detection: Towards a miniaturized, wearable, battery-operated monitoring system," *IEEE Trans. Biomed. Eng.*, vol. 55, no. 1, pp. 196–204, 2008.

- [5] A. J. Casson and E. Rodriguez-Villegas, "Toward online data reduction for portable electroencephalography systems in epilepsy," *IEEE Trans. Biomed. Eng.*, vol. 56, no. 12, pp. 2816–2825, 2009.

- [6] W. M. C. Sansen and P. M. Van Peteghem, "An area-efficient approach to the design of very-large time constants in switched-capacitor integrators," *IEEE J. Solid-State Circuits*, vol. 19, no. 5, pp. 772–780, 1984.

- [7] B. Linares-Barranco and T. Serrano-Gotarredona, "On the design and characterization of femtoampere current-mode circuits," *IEEE J. Solid-State Circuits*, vol. 38, no. 8, pp. 1353–1363, 2003.

- [8] S. Solis-Bustos, J. Silva-Martinez, F. Maloberti, and E. Sanchez-Sinencio, "A 60-dB dynamic-range CMOS sixth-order 2.4-Hz low-pass filter for medical applications," *IEEE Trans. Circuits Syst. II*, vol. 47, no. 12, pp. 1391–1398, 2000.

- [9] A. Veeravalli, E. Sanchez-Sinencio, and J. Silva-Martinez, "A CMOS transconductance amplifier architecture with wide tuning range for very low frequency applications," *IEEE J. Solid-State Circuits*, vol. 37, no. 6, pp. 776–781, 2002.

- [10] A. El Mourabit, G.-N. Lu, and P. Pittet, "A low-frequency, sub 1.5-V micropower Gm-C filter based on subthreshold MIFG MOS transistors," in *IEEE ESSCIRC*, Grenoble, September 2005.

- [11] P. Bruschi, N. Nizza, F. Pieri, M. Schipani, and D. Cardisciani, "A fully integrated single-ended 1.5–15-Hz low-pass filter with linear tuning law," *IEEE J. Solid-State Circuits*, vol. 42, no. 7, pp. 1522–1528, 2007.

- [12] A. Veeravalli, E. Sanchez-Sinencio, and J. Silva-Martinez, "Transconductance amplifier structures with very small transconductances: a comparative design approach," *IEEE J. Solid-State Circuits*, vol. 37, no. 6, pp. 770–775, 2002.

- [13] A. Arnaud, R. Fiorelli, and C. Galup-Montoro, "Nanowatt, sub-nS OTAs, with sub-10-mV input offset, using series-parallel current mirrors," *IEEE J. Solid-State Circuits*, vol. 41, no. 9, pp. 2009–2018, 2006.

- [14] J. Silva-Martinez and J. Salcedo-Suner, "IC voltage to current transducers with very small transconductance," *Analog Integr. Circ. Sig. Process.*, vol. 13, no. 3, pp. 285–293, 1997.

- [15] U. Yodprasit and J. Ngarmnil, "Micropower transconductor for very-low frequency filters," in *IEEE APCCAS*, Chiangmai, November 1998.

- [16] P. Corbishley and E. Rodriguez-Villegas, "A nanopower bandpass filter for detection of an acoustic signal in a wearable breathing detector," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 3, pp. 163–171, 2007.

- [17] E. Camacho-Galeano, C. Galup-Montoro, and M. Schneider, "A 2-nW 1.1-V self-biased current reference in CMOS technology," *IEEE Trans. Circuits Syst. II*, vol. 52, no. 2, pp. 61–65, 2005.

- [18] E. M. Camacho-Galeano, J. Q. Moreira, M. D. Pereira, A. J. Cardoso, C. Galup-Montoro, and M. C. Schneider, "Temperature performance of sub-1V ultra-low power current sources," in *IEEE ISCAS*, Seattle, May 2008.

- [19] F. Gozzini, G. Ferrari, and M. Sampietro, "Linear transconductor with rail-to-rail input swing for very large time constant applications," *Electron. Lett.*, vol. 42, no. 19, pp. 1069–1070, 2006.

- [20] A. Wong, K.-P. Pun, Y.-T. Zhang, and K. Hung, "A near-infrared heart rate measurement IC with very low cutoff frequency using current steering technique," *IEEE Trans. Circuits Syst. I*, vol. 52, no. 12, pp. 2642–2647, 2005.

- [21] A. Becker-Gomez, U. Cilingiroglu, and J. Silva-Martinez, "Compact sub-Hertz OTA-C filter design with interface-trap charge pump," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 929–934, 2003.