Received March 30, 2019, accepted May 3, 2019, date of publication May 20, 2019, date of current version June 27, 2019. *Digital Object Identifier* 10.1109/ACCESS.2019.2917698

# A Survey of Computer Architecture Simulation Techniques and Tools

#### AYAZ AKRAM<sup>10</sup><sup>1</sup> AND LINA SAWALHA<sup>102</sup>, (Senior Member, IEEE) <sup>1</sup>Department of Computer Science, University of California at Davis, Davis, CA 95616, USA

<sup>1</sup>Department of Computer Science, University of California at Davis, Davis, CA 95616, USA <sup>2</sup>Department of Electrical and Computer Engineering, Western Michigan University, Kalamazoo, MI 49008, USA Corresponding author: Lina Sawalha (lina.sawalha@wmich.edu)

This work was supported in part by grants from the Faculty Research and Creative Activities Award (FRACAA) and the College of Engineering and Applied Sciences at Western Michigan University.

**ABSTRACT** Computer architecture simulators play an important role in advancing computer architecture research. With wider research directions and the increased number of simulators that have been developed, it becomes harder to choose a particular simulator to use. This paper reviews the fundamentals of different computer architecture simulation techniques. It also surveys many computer architecture simulators and classifies them into different groups based on their simulation models. Comparing computer architecture simulators with each other and validating their accuracy have been demanding tasks for architects. In addition to providing a survey of computer architecture simulators: gem5, MARSSx86, Multi2Sim, PTLsim, Sniper, and ZSim. We also performed a detailed comparison of these simulators based on other features such as flexibility and micro-architectural details. We believe that this paper will be a very useful resource for the computer architecture community especially for early-stage computer architecture and systems researchers to gain exposure to the existing architecture simulation options.

**INDEX TERMS** Computer architecture simulators, simulation techniques, validation, x86 simulators, simulators evaluation.

#### I. INTRODUCTION

Computer architects use simulation to assess different design options, test new research ideas and analyze the performance/power consumption of different processor models. Analytical models are not suitable for evaluating architectural/microarchitectural designs and design variations as they produce inaccurate results because of the huge amount of configurations and small details that can cause small variations in performance. Simulation is considered to be the standard performance modeling method [1]. The majority of published research is based on the use of simulators to analyze the performance of new ideas. Many computer architecture simulators support various instruction set architectures (ISAs), microarchitectures and are based on different simulation models ranging from trace-based to cycle-accurate. It can be a daunting task for new researchers in the area of computer architecture and systems, to choose one simulator

The associate editor coordinating the review of this manuscript and approving it for publication was Stavros Souravlas.

<sup>1</sup>A. Akram finished the work while at Western Michigan University.

and start their research. In addition, in order to have a trust in simulation studies, simulation results need to be validated. This can be challenging, especially when there is not enough documentation about simulators. There is little work that evaluates current computer architecture simulators, performs a comparison among them, and/or compares their accuracy to contemporary processors. Our major contributions in this paper are:

- Providing an up-to-date survey of computer architecture simulation techniques and simulators.

- Categorizing, analyzing and comparing various computer architecture simulators, which can help the community to understand the use-cases of different simulation tools.

- Providing detailed characteristics and experimental error comparison of six modern *x86* computer architecture simulators: gem5 [2], Multi2sim [3], MARSSx86 [4], PTLsim [5], Sniper [6], and ZSim [7].

- Reviewing the most important challenges for architecture simulators and the solutions that have been proposed to resolve those issues.

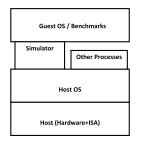

FIGURE 1. Simulator running on a host machine.

In computer architecture, the main goal of simulation is to model new research ideas for parts of a computer system (e.g. microprocessor, memory, IO devices) or a complete computer system and estimate the performance improvements and/or power consumption. Simulators also help computer architects in evaluating, debugging and understanding the behavior of existing systems. In simulation terminology, a computer system that is being simulated is called a *target*, and the system where the simulation is run is called a *host*. Workloads that run on simulators can be standard test programs, known as benchmarks, which are run to assess the performance of a processor or a computer. The workload being simulated can also be an operating system (OS), sometimes referred as a guest OS. The interaction between a simulator and a host system is shown in Figure 1. This survey is a more comprehensive and an updated survey compared to previous existing surveys, which either focused on teaching related simulators [8]–[11], memory simulators [12], [13] or were not much detailed. Nikolic et al. [10] have surveyed many computer architecture simulators suitable for teaching computer architecture courses. They evaluated various simulators based on the criteria of topics covered in the classroom, and simulation features. Uhlig and Mudge [12] and Holliday [13] discussed different memory simulation techniques, which use reference address traces. Urden [14] compared and evaluated the performance results of three different computer architecture simulators against each other. However, his study did not compare the simulators with real hardware runs. In this survey, we compare the simulators' results with that of real hardware experiments to measure their inaccuracies. Nowatzki et al. [15] discussed various pitfalls associated with the usage of architectural simulators. They have also discussed the errors they observed in four performance and power simulators: gem5 [2], GPGPUSim [16], McPAT [17] and GPUWattch [18]. Validation efforts for various simulators (e.g. SimpleScalar, SMARTS, Microlib, gem5, Sniper, SiNUCA, Ramulator) have also been published [19]-[25]. These papers focus only on one simulator that is being validated and usually do not include comparisons with related tools. This survey is up-todate, which includes newer processor architecture simulators, and it is more detailed compared to previous surveys. The survey also compares and contrasts several modern simulators. In order to accelerate the process of simulation, researchers often rely on sampling techniques. The paper also discusses

VOLUME 7, 2019

few of the commonly used sampling methods associated with simulating computer architecture components. Similarly, the accuracy of simulation results is always a concern for architects. We briefly explore different existing simulator validation approaches. Furthermore, this work compares the experimental error of six x86 simulators with hardware runs and provides the relative performance of the simulators when changing some microarchitectural configurations. Finally, we pinpoint some causes of inaccuracies in the simulation results that we observed.

Scope of the paper: Because computer architecture research covers a wide range of architectures, from processor microarchitectures to special purpose architectures and accelerators, which use different types of simulators, we limit the scope of the paper to review in details computer architectural and microarchitectural simulators and simulation models of processors. The paper mentions some uncore and accelerator simulators. It does not survey in details standalone specialized simulators for mircorachictectrual structures or uncore components; however, it does mention detailed microarchitectural or uncore simulations as features of those full computer architectural/microarchitectural simulators. It also discusses those full simulators that can also simulate accelerators or can be attached to accelerator simulators. The paper does not cover systems on chip (SoC) simulators, although many of the simulators that are discussed are capable of simulating embedded processors. The paper also discusses different simulation methodologies, categorizes them, and compares and contrast those techniques. In addition, the paper discusses the challenges associated with simulation and their possible solutions, and discusses simulation evaluation techniques. However, to limit the scope, the paper does not cover in details specific implementation limitations, such as handling target multi-threading.

The organization of the rest of the paper is as follows: Section II classifies simulators into different categories and discusses these categories in details. Section IV summarizes the different existing computer architectural/ microarchitectural simulators. Section V explores the challenges faced in computer architecture simulation and their solutions. Section VI briefly discusses the validation of simulators. Section VII describes in details six modern x86 simulators that we have chosen for detailed evaluation. Section VIII discusses the methodology used to measure the experimental error of simulators and their relative performance. Section IX shows the evaluation results of the x86 simulators. Finally, we conclude the paper in section X.

#### **II. CLASSIFICATION OF SIMULATORS**

Simulators can be classified into various groups on the basis of three most important factors: detail of simulation, scope of the target and input to the simulator. This section discusses in details the aforementioned classification taxonomy. It should be noted that this classification is not mutually exclusive and one simulator can belong to more than one class. In addition,

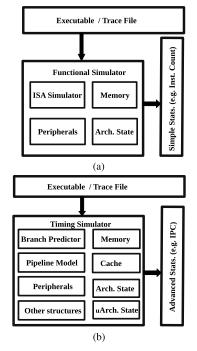

**FIGURE 2.** Simulators based on simulation details (adapted from [26], p. 492, Figure 9.2). (a) Functional Simulator. (b) Timing Simulator.

some simulators are classified based on certain aspects or specializations, which is also discussed in this section.

## A. CLASSIFYING SIMULATORS BASED ON THE DETAIL OF SIMULATION

An important factor to classify simulators is the level of detail that any simulator implements in its design. The main classes of simulators based on simulation detail are functional, timing and functional/timing simulators.

#### 1) FUNCTIONAL SIMULATORS

A functional simulator implements the architecture only and focuses on achieving the same functionality of the modeled architecture. In other words, functional simulators behave like emulators (emulate the behavior of target's instruction set architecture (ISA)). They are usually faster than the other types of simulators, but they cannot keep track of detailed microarchitectural parameters, as a program runs on the simulator, because they do not implement the microarchitecture. While developing new instruction sets, functional simulators can be used for testing purposes. Moreover, functional simulators can help in identifying architectural features of a program's execution, for instance, the total number of different types of instructions in a program, memory access locality, etc. Figure 2(a) shows a block diagram of a functional simulator.

SimpleScalar simulator [27] has been used for teaching and research purposes. SimpleScalar is a comprehensive toolset. It has various simulation models, out of which *sim-safe* is an example of a functional simulation model. It is a minimal

SimpleScalar simulator that only simulates the ISA. A speedoptimized version of sim-safe is named as sim-fast [27]. Simics [28] is another functional simulator, which has a unique ability of executing a program in forward or backward directions. SimCore [29] is a functional simulator for Alpha processors. It is claimed to be 19% faster than simfast of SimpleScalar toolset [29]. EduMIPS64 [30], a visual functional simulator written in java for MIPS, was designed to be used in classrooms for teaching computer architecture courses. HASE [31] is a tool for high-level simulation and visualization of computer architectures. It was developed in the 90's using object oriented simulation languages. HASE project provides many computer architecture models targetting teaching concepts related to computer architecture. Barra [32] is a functional simulator for GPGPU (general purpose graphics processing units). It supports simulation of CUDA applications. Another example of functional simulators is the 'AtomicSimple' CPU model of gem5. One alternative to creating a functional simulator is to instrument a program's binary with a code that is responsible for collecting the required information when the program executes on a real hardware [33]. Such tools are called dynamic binary instrumentation tools, for example, Pin tools [34]. There are many simulators (e.g. CMP\$im [35], Sniper [6]), which also rely on instrumentation tools to perform functional simulation.

#### 2) TIMING SIMULATORS

Timing simulators, also known as performance simulators, simulate the microarchitecture of processors (Figure 2(b)). They produce detailed statistics about the timing/performance of a target system [26]. For instance, in case of the simulation of a processor, this information might comprise statistics like instructions per cycle (IPC), program run time, performance of a memory system and other detailed microarchitecture-related statistics. It is not required for a timing/performance simulator to emulate the functionality of a target. Timing simulators have different subtypes, depending on the degree of details included in the simulator: cycle-level simulators, event-driven simulators and interval simulators.

*Cycle-level Simulators:* Cycle-level simulators simulate an architecture by imitating the operation of the simulated processor for each cycle. In contrast to cycle-accurate simulators that simulate *accurately* what happens on each cycle using RTL implementation [36], cycle-level simulators do not model the hardware with minute details. Cycle-level simulators are slow and utilize a considerable amount of memory compared to functional and other timing/performance simulators.

For instance, *sim-fast* (the fastest functional simulator for SimpleScalar) can simulate instructions 25 times faster than the detailed cycle-level simulation model of SimpleScalar. The cycle-level performance model of SimpleScalar is called *sim-outorder*, which is a detailed microarchitectural timing model. It implements an out-of-order superscalar processor that supports speculation. Most of the design parameters are

## **IEEE**Access

configurable by users, for example, the number and latency of functional units, instruction queue and reorder window sizes, memory latency, etc. Another example of cycle-level simulators is MSim [37], which is a multi-threaded microarchitectural simulation environment for Alpha processors that simulates major pipeline components. MSim is based on SimpleScalar.

*Event-driven Simulators:* An event-driven simulator simulates a target based on events instead of cycles. Usually, they make use of event queues. Simulation jumps to the time when an event is scheduled, based on the event queues, instead of going through all cycles. That way, simulators can save time by not simulating the cycles for which there are no scheduled events [38]. Often, some parts of a simulator are modeled on a cycle-level, while others are event-driven. For example, the work done by Reilly and Edmondson [39] to simulate the performance of Alpha microprocessors. An important point to note here is that often literature does not distinguish between cycle-level and event-driven simulators.

SESC [40], a relatively fast simulator is an example of an event-driven timing simulator that supports MIPS ISA. SESC supports various simulation models such as single processors, chip multiprocessors (CMPs), processor in memory (PIM). RSim [42] is another example of eventdriven timing/performance simulators. It was developed in the 1990's and focused on both instruction-level parallelism (ILP) and shared memory multiprocessors. Detailed accuracy in RSim is achieved at the cost of a slow speed [42]. Sampling microarchitecture simulation (SMARTS) [20] framework and Flexus (Simics) [43] form the basis of a cycle-level timing simulator SimFlex [44]. Some of the components of this simulator are event-driven internally. SimFlex can perform fast simulation of uniprocessor and multiprocessor systems. It supports various memory models, but implements a simple in-order CPU model.

*Interval Simulators:* With the diversion of research focus towards multi-core and many-core systems, researchers have been looking for new simulation techniques that balance simulation accuracy and speed as alternatives for cycle-level and event-driven only simulators. For instance, interval simulation [45] is one of such recently proposed techniques. This technique makes use of the fact that regular instruction flow through the pipeline can be broken down into sets of intervals based on miss events (cache misses, branch mispredictions). Special purpose portions of architectural simulators, like branch predictors and memory system, can be used to simulate the miss events and find their exact timings. Then, these timings along with an analytical model are used to estimate the duration for every interval of instructions.

#### 3) INTEGRATED TIMING AND FUNCTIONAL SIMULATORS

Functional simulators are often integrated with timing simulators to achieve a more flexible and accurate simulation model. The two types of simulators might or might not be coupled together. The technique of coupling the simulators, in which instructions execute at the execute stage of

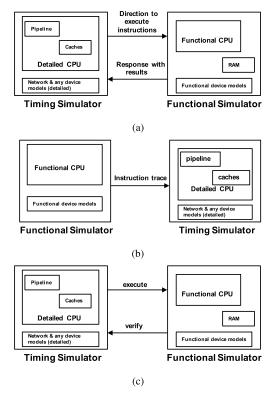

FIGURE 3. Three types of integrated timing and functional simulators. (a) Timing-directed Simulator. (b) Functional-first Simulator. (c) Timing-first Simulator.

the modeled pipeline, is known as execute-in-execute. This makes execute-in-execute a relatively complicated technique as compared to decoupling. On the other hand, it can increase the accuracy of the modeled timing-dependent instructions like synchronization and IO operations [46]. gem5 [2] is an example of a simulator that uses this technique. To simplify the development and reduce its complexity, often simulators decouple functional and timing (performance) simulation. Usually, some third party software is used for functional simulation. For example, Simics [28] is used by both Sim-Flex [44] and GEMS [38] for functional simulation, and Pin [34] is used by both Graphite [47] and Sniper [6] (based on Graphite) for functional simulation. For decoupling, there are three practical types [33]: timing-directed, functionalfirst and timing-first. In case of a timing-directed simulator, the timing model leads the simulation and gives directions to a functional model to execute instructions. This makes it possible for timing directed simulators to model speculative paths. Functional-first simulators use functional models to generate instruction traces which are fed to a timing model to derive detailed simulation. Since the functional models only executed instructions on the correct-path, it is hard to model speculative paths with this kind of simulators. In the case of timing-first simulators, the timing-simulator also executes instructions and uses a separate functional model to verify its execution. Figures 3(a), 3(b) and 3(c) illustrate these three types.

*Timing-directed Simulators:* In this category, a functional simulator records the architectural state (e.g. register and memory values) of the processor being simulated. The timing simulator, which has no idea of data values on its own, takes and uses these values from the functional simulator to perform a specific task when required [33]. The functional model and the timing models interact heavily in this type of simulators as the timing model directs the functional model and the functional model feeds values to the timing model. This interaction makes this simulation model suitable for modeling architectures with dynamically changing functional behavior, such as multicore architectures [48]. For example, for a load instruction the functional model computes the instruction's effective address, and the timing model uses this address to determine if the load is causing a cache miss. The returned value from the cache or the memory, will eventually be read by the functional simulator. Asim [49] is an example of this category of simulators.

Functional-First Simulators: In this simulation model, the functional simulator runs prior to the timing simulator and generates an instruction trace (a stream of instructions) that feeds the timing simulator at runtime. In the case of conditional branches, the functional simulator always follows the correct path and it cannot simulate the behavior of branch predictors [50]. If there is a mispredicted branch in the timing simulator's pipeline, the functional simulator restores its previous state before the branch and continues along the mispredicted path. Later, the pipeline has to be flushed due to this mispredicted branch. Since the timing simulator always lags behind the functional simulator, there can be ordering problems while simulating more than one thread [50]. For instance, the time at which the functional model reads a memory value in case of a load instruction can be different from the time when the timing model requests the same value, and this can result in reading different values. This problem can be resolved by a speculative functionalfirst simulation [33]. In this technique, whenever a timing model detects that the data it reads is different from the data that the functional model has read, it asks the functional model to restore the processor's state to the state before the load instruction and then it executes the load instruction with the correct data. As, timing and functional models run in parallel, there is an opportunity to exploit this parallelism for better performance of the simulator. This type of simulators has much better performance as compared to timing-directed simulators, because it is not required for the timing model to direct the functional model at every instruction or cycle as in timing directed simulators. SimWattch [51] is an example of functional first simulators. SimWattch integrates Simics with Wattch [52]. Wattch is based on SimpleScalar and simulates both power and performance.

*Timing-First Simulators:* In this approach, timing simulators run ahead of functional simulators [50]. Timing simulators simulate the microarchitecture of a target processor at the cycle-level. Timing simulators usually use functional simulators for verification of functional execution of

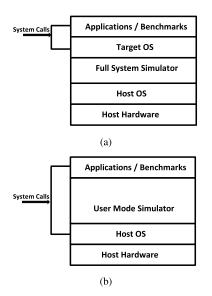

FIGURE 4. Simulators based on scope of target (adapted from [26], p. 491, Figure 9.1). (a) Full System Simulator. (b) User Mode Simulator.

all instructions. The instruction is retired in case of a match between the architectural state of both the functional and the timing simulators. In case of a mismatch, the timing simulator recovers by flushing the pipeline and restarting the instruction fetch following the problematic instruction. As such, the timing simulator makes forward progress. If these recoveries happen frequently, they can impact the simulated system's timing, and thus accuracy, depending on the depth of the simulated pipeline [50]. GEMS [38], FeS<sub>2</sub> [53] and Multi2sim [3] are some examples of timing first simulators.

## B. CLASSIFYING SIMULATORS BASED ON THE SCOPE OF THE TARGET

Another factor to consider while categorizing simulators is the scope of the target system that is being simulated. Simulators can be classified into two types based on scope:

#### 1) FULL-SYSTEM SIMULATOR

Given any supported operating system (OS) binary, a full system simulator is able to completely boot that OS and run application benchmarks on that OS as they would run normally on a real target machine. Figure 4(a) shows the basic functionality of a full system simulator. A full-system simulator simulates all needed I/O devices, memory and network connections that are required to boot and run any system. Applications that run on a simulated target system execute their system calls directly on the target system [26]. As a result, this form of simulation is complicated and time consuming. Ideally the OS should not be modified, but sometimes binaries of the OS are customized to make the process of OS booting less resource consuming.

Full-system simulators may or may not be timing simulators. For instance, gem5 [2] is an example of a fullsystem timing simulator, while SimOS [54] is a full-system functional simulator. gem5 has the ability to boot Linux, Solaris and Android operating systems on specific hardware that it supports. SimOS developed in the late 90's, was one of the first full-system simulators (not currently active). Sunflower [55] suite includes a full-system simulator with microarchitecture and IO modeling. Simics is able to boot unmodified OS. SimFlex [44], ML-RSim [56], MARSSx86 [4] and PTLsim [5] are other examples of this type of simulators.

## 2) APPLICATION LEVEL/USER MODE SIMULATOR

These simulators run only target applications instead of simulating a complete OS. They simulate microprocessor and limited peripherals. In this kind of simulators, system calls are usually bypassed by the simulator and are serviced by the underlying host operating system, as shown in Figure 4(b). It might not be a problem to simulate only usermode code for benchmarks that execute system-level code for a short duration (e.g. compute intensive benchmarks as SPEC CPU2006 and CPU2017) [33]. However, for benchmarks that spend a significant time to execute system-mode code, user mode simulation is not enough-(e.g. server related benchmarks such as Web-Bench and NetBench, real world performance benchmarks for example SYSMARK, and transaction processing and database benchmarks such as TPC-C). For multithreaded workloads, OS scheduling should be taken into account as it affects workload performance. Thus, it is necessary to simulate OS-level effects to get a better estimation of performance. On the other hand, application-level simulators are usually less complex and fast as compared to full system simulators. SimpleScalar is the most known example of application-level simulators. SESC [40], Sniper [6], and RSim [42] are other examples of application only simulators.

## C. CLASSIFYING SIMULATORS BASED ON THE INPUT TO THE SIMULATOR

We can categorize simulators into two categories based on the input to the simulator itself, traces or executables.

## 1) TRACE-DRIVEN SIMULATORS

Trace files are used as inputs to trace-driven simulators. These trace files are prerecorded streams of instructions executed by benchmarks with some fixed inputs. As benchmarks execute on real machines statistics including instruction opcodes, data addresses, branch target addresses, etc are recorded in a trace file. Trace-driven model makes the implementation of the simulator simple. Trace-driven simulators can be easily debugged because experimental results can be reproduced. The size of trace files can be huge, which poses limits on the total instruction count in each trace file and/or the number of trace files used at once, and may lead to a slower simulation time [33], [57]. Different trace sampling and trace reduction techniques [58], are used to resolve the problem of large size of trace files. Apart from this, these simulators usually do not model execution of mispeculated code, which can affect

performance estimation results of structures such as branch predictors. To solve the problem of branch mispredictions, techniques like reconstruction of mispredicted path [59] are used.

Trace-driven models do not include the run-time changes in behavior of multi-threaded applications [60]. This becomes a more visible problem if trace-driven simulation is run for a simulated multiprocessor system that is different from the one that was used to collect the trace. Trace-driven simulation should be avoided for parallel and timing-dependent systems as emphasized by Goldschmidt et al. [61].

Shade [62] is a trace-driven instruction set simulator, supporting SPARC and MIPS systems. Shade is also used to generate traces. Simplescalar also has the capability to run simulations from trace files. Cheetah [63] is a trace-driven simulator that simulates different cache configurations. MASE [64] is another example of this type of simulators. It is very hard for trace driven simulators to model the run-time changes in the behavior of multi-threaded applications [60], [61]. However, lately, few research works have been put forward to efficiently use trace-driven simulators for multi-threaded workloads, [65], [66].

## 2) EXECUTION-DRIVEN SIMULATORS

Execution-driven simulators do not use trace files. Instead, these simulators use binaries or executables of benchmarks for simulated target machines directly. These simulators can simulate misspeculated instructions unlike trace-driven simulators. However, they are complicated as compared to trace-driven simulators. SimpleScalar [27] falls into this category of simulators. Rsim [42], a discrete event-driven simulator based on YACSIM library [67], also interprets application executables rather than trace files. SESC and ESESC [68] are other examples of this type of simulators.

Often, users are interested in the performance of selected regions of code instead of entire benchmarks. The technique of *direct/native execution* can help in this respect. In direct execution, simulators only simulate particular portions of code (or *regions of interest*) of an application and execute the rest of the application directly on the host machine [57]. In this case, both the target and the host systems should have same instruction set architecture (ISA) to perform native execution. This technique is also referred as *co-simulation*. PTLsim [5] makes use of this method to speed up simulation. Tang [69], Proteus [70] and FAST [36] use this approach as well.

## D. OTHER SIMULATOR CATEGORIES

Apart from the aforementioned classifications of simulators, simulators can also be classified based on other aspects or their specializations as follows:

## 1) MULTIPROCESSOR/MULTICORE SIMULATORS

Recently, multiprocessor/multicore systems have become ubiquitous. Multiprocessor simulators are more complex than uniprocessor ones as they have to cope with the challenges of keeping the critical regions of applications consistent for all processors/cores and scheduling of processes [26]. Simulators with a modular design are better able to simulate multiprocessor systems, as they can easily instantiate different processors and corresponding modules to simulate a multicore system. There are two main approaches for simulating parallel targets: sequential simulation and parallel simulation. In case of sequential simulation, there is only one simulator thread to simulate all target cores. Simulators in this case simulate cores in a round robin fashion [26]. In case of parallel simulation methodology, different simulator threads are used to simulate different cores. This method speeds up simulation, but it is difficult to implement due to general challenges of multithreaded software development.

SimOS [54] and Simics [28] both support multiprocessor simulation. SimCA [71] is a simulator which is no longer maintained but was developed on top of SimpleScalar's outof-order model. It focused on multithreaded processor architecture. MINT [41] is a software package that was designed to build event-driven memory hierarchy simulators for multiprocessors. It only runs on MIPS based machines and supports simulation of MIPS. PTLsim supports multithreading and multiprocessor simulation. Augmint [72] is a publicly available execution driven multiprocessor simulation environment for Intel x86 architectures. MINT forms the basis of Augmint, however; Augmint adapts Tango Lite's [73] augmentation technique as well. In this augmentation approach, the application is augmented with instrumentation code at compile time. This instrumentation code updates simulation clock and generates events for simulation. ZSim [7], ESESC [68], SESC [40] and SimCore [29] are other examples of simulators that support multicore simulations.

#### 2) ENERGY AND POWER SIMULATORS

With the pressing need of building energy efficient processors and computer systems, the significance of energy and power simulators is increasing. There are many examples of such simulators in present days. Wattch [52] is widely used to simulate consumed power. It is based on Simplescalar and designed to examine and optimize power dissipation and energy consumption of Alpha microarchitecture. It can also be merged with other simulators. For example, SimWattch integrates Simics and Wattch. CACTI [74] is another example that simulates power and area for cache like structures. McPAT [17] can simulate timing, area and power of multicore processors. Some other examples are Powertimer [75], PowerAnalyzer [76] and SimplePower [77]. SESCTherm [78] and Hotspot [79] are two other examples of this category of simulators which model thermal effects at the micro-architectural level. Power Blurring [80] is another temperature calculating model, which is developed based on a matrix convolution approach, to reduce computation time. Ziabari et al. [81] have compared Power Blurring with HotSpot and SESCTherm. Their experiments have shown that the Power Blurring technique can achieve better accuracy to generate temperature

#### TABLE 1. Existing specialized/accelerator simulators.

| Simulator type   | References                                                   |

|------------------|--------------------------------------------------------------|

| Memory System    | Mem-Sim [83], DRAMSim [84], Ramulator [25]                   |

| Cache only       | Dinero IV [85], Cachesim5 [86]                               |

| Branch Predictor | [87]                                                         |

| Value predictor  | CVPv6 [88]                                                   |

| Storage devices  | HRaid [89], FlashSim [90], MQSim [91]                        |

| NoC              | GARNET [92], NoC simulator [93], Noxim [94]                  |

| GPU              | Multi2Sim [3], GPGPU-Sim [95]                                |

| ASIC             | Aladdin [96], PARADE [97], Minerva [98], Firesim [99]        |

| FPGA             | ActiveHDL [100], ISim [101], Incisive Enterprise Sim. [102], |

|                  | ModelSim & Questa [103], QSim [104], FireSim [99]            |

| DSP              | [105], [106], [107]                                          |

profiles in less amount of time. ESESC [68] uses modified McPAT and Hotspot for energy simulations.

#### 3) SPECIALIZED/ACCELERATOR SIMULATORS

Many specialized simulators that are capable of simulating parts of a processor's architecture/microarchitecture exist. Among those, memory and network on chip (NoC) simulators are most common. Specialized simulators are only capable of executing certain types of instructions and usually use traces of specific instructions of executed programs/benchmarks as their inputs. They are easier to develop and can give a good idea about the behavior of specific parts of a processor; however, they are less accurate as they do not simulate the entire processor and the interaction with the other parts of the processor. They usually do not simulate 'off-path' instructions in case of mispredicted branches for example, in branch prediction simulators.

Memory simulators simulate data and instruction accesses to memory. Most of the existing memory simulators are trace-driven in nature, where trace files contain streams of memory accesses only. For example, DRAMSim is a timing simulator that can simulate different kinds of memories like DDR, SDRAM, DRDRAM etc. [83]. DRAMSim can also be integrated with other simulators. Cachesim5 [85] and Dinero IV [84] are examples of simulators that simulate only cache accesses. Network on chip simulators simulate the communication infrastructure of a processor. Emerging many-core processors design calls for a faster/less congested networks on a chip. As such, NoC simulator's have been increasingly built and used. They are capable of simulating different types of networks on chips, topologies, routing policies, etc.

Accelerator simulators have been used to simulate the behavior of programs or program portions accelerated using a graphical processing unit (GPU), an application specific integrated circuit (ASIC), a digital signal processor (DSP), a field programmable gate array (FPGA), near-data and inmemory processing, etc. Accelerators have been recently integrated with processors on the same chip or on a system-on-chip (SoC). In addition, they have been proposed to be tightly coupled with processors. The simulation of accelerators in addition to processors give a complete view of the performance of benchmarks. Table 1 shows different existing types of specialized and accelerator simulators with

| Simulation Model                                       | Accuracy         | Performance         | Level of details      | Easiness of development           |

|--------------------------------------------------------|------------------|---------------------|-----------------------|-----------------------------------|

| Functional simulation                                  | A-               | P+++                | L                     | E+++                              |

| Timing - cycle accurate simulation                     | A++              | Р                   | L++                   | E                                 |

| Timing - event driven simulation                       | A+               | P+                  | L+                    | E+                                |

| Coupled functional-timing                              | A+++             | Р                   | L++                   | E                                 |

| Decoupled functional-timing/ timing first              | A+               | Р                   | L+                    | E+                                |

| Decoupled functional-timing/ functional first          | A                | P++                 | L+                    | E++                               |

| Decoupled functional-timing/ timing direct             | A++              | P+                  | L++                   | E                                 |

| Full-system simulation                                 | A++              | Р                   | L+++                  | E                                 |

| User-level simulation                                  | A+               | P+                  | L++                   | Е                                 |

| Trace-driven simulation                                | A+               | Р                   | L+                    | E+                                |

| executable-driven simulation                           | A++              | P+                  | L++                   | E                                 |

| Note: [evaluation parameter's first letter] with a sur | ffix of +++ repr | resents the highest | value and without a s | uffix represents the lowest value |

TABLE 2. Comparison of different categories of simulation techniques in terms of accuracy, performance, level of details and easiness of development.

some examples. The interaction of accelerators and processors is also important to simulate, some computer architecture simulator's include (or can be integrated to) accelerator simulators such as gem5 [2] and Multi2Sim [3].

#### 4) MODULAR SIMULATORS

Modular simulators, instead of having a monolithic design, contain independent modules for different portions of the processor that can be initialized and linked to other blocks of the simulated system. These simulators can be debugged easier and better suit complex designs than non-modular simulators. This modularity makes simulators more manageable. Liberty Simulation Environment (LSE) [107] is one example of modular simulators. LSE uses a single software function for each hardware component, and the designer can use those components connected in an hierarchy to construct any complex system. Asim [49] is another example of this type of simulators. It is a user-mode simulator that extends SimpleScalar to modular components within the simulator itself. MicroLib [21], M5 [46], Soonergy [108], [109] and gem5 are some other examples of modular simulators, which provide the ability to reuse modules of a certain processor component in a new computer system.

#### **III. EVALUATION OF SIMULATORS**

The evaluation of simulators is challenging because of the contradicting metrics that should be considered. Eeckhout [33] represented simulation trade-offs as a diamond with contradicting factors: accuracy, evaluation time, development time and coverage. In this paper, we consider six trade-off metrics that can be used to evaluate simulators: accuracy, performance, level of details, easiness of development, flexibility and user friendliness.

The accuracy of a simulator refers to the performance accuracy of the simulated target compared to real hardware. The performance of a simulator refers to how fast or slow the simulator can run while simulating the target architecture. The level of details represent the amount and level of details that a simulator includes while representing a target architecture. It is not easy to achieve the best results in all of these trade-offs as most of them are contradicting metrics. Flexibility refers to both the configurability of the simulator and how flexible the simulator is to modify (or add new) structures. User friendliness refers to how easy it is for users to learn how to use a simulator, modify it, and run different experiments. Table 2 compares the first four tradeoffs for the different categories of simulation models described earlier in section II. Flexibility and user friendliness are affected more by the simulation implementation than the category of simulators and thus excluded from the comparison.

#### **IV. SUMMARY OF EXISTING PROCESSOR SIMULATORS**

There exist several processor architecture simulators. Table 3 below summarizes existing computer architecture/ microarchitectural simulators; all simulators are open source except Simics. It summarizes different aspects of the simulators including supported hosts and targets, etc. In addition, it characterizes simulators based on the classification taxonomy described in section II above.

#### **V. CHALLENGES OF SIMULATION**

The main challenges in simulation are related to simulator's performance and accuracy [121]. This section describes these challenges and proposes strategies to tackle them.

#### A. SLOW SIMULATION

Computer architects and system designers rely on simulations with accurate timings for proper design decisions. Simulating a single application only can take a long time- from few hours to days. The primary reasons for long simulation time is the complexity of modern microarchitectures that are simulated and the length of today's programs, consisting of billions and trillions of instructions. With the advent of multiprocessor and multicore systems, simulators have to keep track of shared resources and deal with synchronization, which is resource consuming. Benchmarks have also become more complex than they were in the past [33]. For example, SPEC CPU benchmarks have become more complex overtime. The dynamic instruction count per benchmark was 2.5 billion on average in CPU89, it increased to 230 billion instructions in CPU2000 [122] and to 2.5 trillion instructions in CPU2006 [123]. CPU2017 has on average 10X higher dynamic instruction count compared to CPU2006 [124]. Today, applications are becoming increasingly multithreaded to utilize multicore processors efficiently, and

#### TABLE 3. Simulators summary table.

| Name           | Supported hosts<br>(ISA/OS)                                               | Supported targets<br>(ISA)                                               | Category                                                                                                                                                                                                               | Supported<br>pipeline<br>models                              | MultiCore<br>Support                | Notes                                                                                  |

|----------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------|

| ASim [49]      | x86                                                                       | Alpha, x86                                                               | UM/MOD/TIM<br>(decoupled timing<br>and functional<br>models)                                                                                                                                                           | out-of-order                                                 | yes                                 |                                                                                        |

| Augmint [72]   | x86/Unix,<br>x86/Windows<br>NT                                            | x86                                                                      | EDr/TD                                                                                                                                                                                                                 |                                                              | yes                                 | based on MINT and Tango<br>Lite                                                        |

| CMP\$im [35]   | x86                                                                       | x86                                                                      | parallel UM cache<br>(decoupled)                                                                                                                                                                                       | I                                                            | yes                                 | uses Pin for functional simu-<br>lation                                                |

| COTSon [110]   | x86                                                                       | x86                                                                      | FSys/FUNC                                                                                                                                                                                                              |                                                              | yes                                 |                                                                                        |

| Dinero IV [83] | x86/Linux,<br>Alpha/Linux,<br>x86/Solaris,<br>Alpha/OSF,<br>SPARC/Solaris | input trace files                                                        | TD cache                                                                                                                                                                                                               | -                                                            | ОП                                  |                                                                                        |

| DRAMSim [84]   | x86/Linux                                                                 | input trace files                                                        | TD cycle-level<br>DRAM                                                                                                                                                                                                 | I                                                            | Ю                                   | integrated with many other<br>simulators like Sim-Alpha,<br>GEMS, MASE, MARSSx86       |

| ESESC [68]     | x86-64/Linux and<br>ARMv7                                                 | ARMv7                                                                    | TIM/UM (cycle-<br>level)                                                                                                                                                                                               | out-of-order,<br>in-order                                    | yes                                 | has power and thermal mod-<br>els, supports CPU-GPU sim-<br>ulation                    |

| Flexus [43]    | inux                                                                      | SPARC, x86                                                               | FSys/TIM/EDr<br>(cycle-level)                                                                                                                                                                                          | in-order, out-<br>of-order                                   | yes                                 | uses Simics for full system<br>simulation                                              |

| gem5 [2]       | x86, ARM,<br>SPARC, Alpha,<br>PPC/ Linux,<br>MacOSx, Solaris,<br>OpenBSD  | x86, ARM, MIPS,<br>Alpha, PPC,<br>SPARC                                  | FSys/MOD/TIM<br>(cycle-level)                                                                                                                                                                                          | in-order, out-<br>of-order                                   | yes                                 | based on M5 and GEMS sim-<br>ulators                                                   |

| GEMS [38]      | x86/Linux,<br>AMD64-linux,<br>and SPARCV9<br>(Solaris 8)                  | SPARC, x86                                                               | FSys/TIM (decou-<br>pled functional and<br>timing models)                                                                                                                                                              | out-of-order                                                 | yes                                 | uses Simics for functional simulation, not maintained now                              |

| GPGPUSim [16]  | Linux                                                                     | PTX and SASS,<br>PTXPlus                                                 | UM cycle-level<br>(decoupled timing<br>and functional<br>models)                                                                                                                                                       | in-odrer, out-<br>of-order                                   | yes                                 | supports Nvidia's Fermi and<br>GT200 like GPUs, integrates<br>energy model (GpuWattch) |

| Graphite [47]  |                                                                           | 98x                                                                      | parallel UM/TIM<br>(decoupled)                                                                                                                                                                                         | in-order with<br>in or out-of-<br>order memory<br>completion | yes                                 | uses Pin for functional<br>simulation, integrates power<br>model                       |

| HASE [31]      | x86/Linux, MAC,<br>Windows                                                | SdIM                                                                     | MOD/FSys                                                                                                                                                                                                               | out-of-order                                                 | no                                  | based on Sim++                                                                         |

| HAsim [111]    | FPGA                                                                      | SdIM                                                                     | FPGA based TIM                                                                                                                                                                                                         | out-of-order                                                 | yes                                 |                                                                                        |

| Note: FUN      | C=functional, TIM=tin<br>MOD=modula                                       | ning, <b>EvDr</b> =event-drive<br>r, <b>IS</b> =instruction set, $\mu_i$ | Note: FUNC=functional, TIM=timing, EvDr=event-driven, FSys=full system, UM=user mode, EDr=execution-driven, TD=trace-driven, MOD=modular, IS=instruction set, μAr=micro-architecture, HMP=heterogeneous multiprocessor | M=user mode, ED<br>HMP=heterogenec                           | r=execution-dri<br>ous multiprocess | ven, TD=trace-driven,<br>or                                                            |

| Name          | Supported hosts<br>(ISA/OS)                                                        | Supported targets<br>(ISA)                                            | Category                                                                                                                                                                                               | Supported<br>pipeline<br>models     | MultiCore<br>Support                | Notes                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| LSE [107]     | x86/Unix                                                                           | PowerPC, SPARC,<br>IA64, DLX                                          | MOD                                                                                                                                                                                                    | out-of-order                        | yes                                 |                                                                                                                                        |

| LiveSim [112] | x86                                                                                | MIPS64                                                                | TIM/UM (cycle-<br>level)                                                                                                                                                                               | out-of-order                        | no                                  | based on QEMU and ESESC                                                                                                                |

| MARSSx86 [4]  | x86-64/Linux                                                                       | x86-64                                                                | FSys/TIM (decou-<br>pled functional and<br>timing models)                                                                                                                                              | in-order, out-<br>of-order          | yes                                 | based on QEMU and PTL-Sim                                                                                                              |

| McPAT [17]    | x86/Linux                                                                          | Alpha, ARM, x86,<br>SPARC                                             | power, area and<br>TIM                                                                                                                                                                                 | I                                   | yes                                 | flexible interface for easier<br>integration with performance<br>simulators                                                            |

| McSimA+ [60]  | x86                                                                                | x86                                                                   | UM/TIM<br>(decoupled<br>functional and<br>timing models)                                                                                                                                               | in-order, out-<br>of-order          | yes (HMP)                           | uses Pin for functional simu-<br>lation                                                                                                |

| MicroLib [21] | x86                                                                                | Alpha, PowerPC,<br>SHARC                                              | MOD/FSys                                                                                                                                                                                               | out-of-order                        | no                                  | modules are based on sys-<br>temC                                                                                                      |

| Mint [41]     | SGI, SPARC and DEC stations                                                        | MIPS                                                                  | UM/EDr                                                                                                                                                                                                 |                                     | yes                                 | used by many other detailed simulators                                                                                                 |

| MLRSim [56]   | x86/Linux,<br>SGI IRIX,<br>SPARC/Solaris                                           | ~                                                                     | FSys/TIM (EvDr<br>and MOD)                                                                                                                                                                             | out-of-order                        | no                                  | based on RSim                                                                                                                          |

| Multi2Sim [3] | x86/Linux                                                                          | MIPS32, x86,<br>ARM, AMD<br>Evergreen,<br>NVIDIA Fermi                | UM/MOD/TIM                                                                                                                                                                                             | out-of-order                        | yes (HMP)                           | major use case is CPU-GPU simulation                                                                                                   |

| MSim [37]     | Linux/ x86,<br>Win2000, SPARC/<br>Solaris                                          | Alpha                                                                 | UM/TIM (cycle-<br>level)                                                                                                                                                                               | in-order, out-<br>of-order          | yes                                 | based on SimpleScalar, inte-<br>grates Wattch's power model                                                                            |

| OVPsim        | x86/Windows,<br>x86/Linux                                                          | ARM, MIPS, x86                                                        | FSys/FUNC                                                                                                                                                                                              | I                                   | yes (HMP)                           | uses dynamic binary transla-<br>tion                                                                                                   |

| PTLsim [5]    | x86/Linux                                                                          | x86                                                                   | FSys/TIM (cycle-<br>level)                                                                                                                                                                             | out-of order                        | yes                                 | processors like AMD K8, In-<br>tel P4 and Core 2 form the<br>basis of core model, XEN in-<br>tegration for full system sim-<br>ulation |

| RSim [42]     | SUN machines<br>running Solaris<br>2.5, SGI Power<br>Challenge running<br>IRIX 6.2 | SPARC v8                                                              | UM/EDr/EvDr/TIM                                                                                                                                                                                        | out-of-order                        | yes                                 | based on MIPS R10000 ar-<br>chitecture                                                                                                 |

| SESC [40]     | Unix-based<br>systems (e.g.<br>Linux and<br>Darwin/MacOSx)                         | SdIM                                                                  | UM/TIM/EvDr                                                                                                                                                                                            | out-of-order                        | yes                                 | uses MINT emulator                                                                                                                     |

| Note: FUN     | Note: FUNC=functional, TIM=tin<br>MOD=modula                                       | ing, <b>EvDr</b> =event-drive<br>r, <b>IS</b> =instruction set, $\mu$ | ional, TIM=timing, EvDr=event-driven, FSys=full system, UM=user mode, EDr=execution-driven, TD=trace-driven, MOD=modular, IS=instruction set, μAr=micro-architecture, HMP=heterogeneous multiprocessor | M=user mode, ED)<br>HMP=heterogeneo | r=execution-driv<br>us multiprocess | en, <b>TD=</b> trace-driven,<br>or                                                                                                     |

## TABLE 3. (Continued.) Simulators summary table.

#### TABLE 3. (Continued.) Simulators summary table.

| Name                              | Supported hosts<br>(ISA/OS)                                      | Supported targets<br>(ISA)                                                                                                                                                                                             | Category                                                       | Supported<br>pipeline<br>models    | MultiCore<br>Support | Notes                                                                      |

|-----------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------|----------------------|----------------------------------------------------------------------------|

| Shade [62]                        | SPARC                                                            | SPARC (v8 and v9)                                                                                                                                                                                                      | profiler                                                       |                                    | no                   | supports dynamic profiling                                                 |

| SIMCA [71]                        | SPARC/ Solaris                                                   | Alpha, x86                                                                                                                                                                                                             | UM/EDr/TIM                                                     | out-of-order                       | yes                  | based on SimpleScalar, not in<br>active development now                    |

| SimCore [29]                      | x86/Linux,<br>Alpha/Linux, Ul-<br>traSPARC/Solaris,<br>MIPS IRLX | Alpha                                                                                                                                                                                                                  | UM FUNC                                                        | I                                  | yes                  | multiprocessing support at<br>functional level only                        |

| SIMFLEX [44]                      | x86/Linux                                                        | x86, SPARC                                                                                                                                                                                                             | FSys/MOD/TIM<br>(decoupled<br>functional and<br>timing models) | out-of-order                       | yes                  | uses Simics for functional simulation and SMARTS for statistical sampling  |

| SIMICS [28]                       | Alpha, PPC,<br>UltraSPARC, x86/<br>Linux, Windows                | Alpha, ARM,<br>MIPS, PPC,<br>SPARC, x86,<br>Linux, Solaris,<br>Windows                                                                                                                                                 | FSys/FUNC                                                      | I                                  | yes                  | commercial simulator                                                       |

| SimOS [54]                        | x86/Linux, MIPS<br>IRIX                                          | SGI, IRIX MIPS                                                                                                                                                                                                         | FSys/TIM                                                       | out-of-order                       | yes                  | based on MIPS R4000 &<br>MIPS R10000, supports di-<br>rect execution       |

| SimpleScalar [27]                 | Linux/x86,<br>Win2000/x86,<br>SPARC/Solaris                      | Alpha, Pisa, ARM,<br>x86                                                                                                                                                                                               | UM/EDr/TIM                                                     | out-of-order                       | no                   | models ranging from simple<br>emulation to detailed simula-<br>tion        |

| SiNUCA [24]                       | x86-64/Linux                                                     | x86-64                                                                                                                                                                                                                 | TD/UM/TIM                                                      | out-of-order                       | yes                  | validated for Intel Conroe and Sandy-Bridge $\mu$ -Arch                    |

| Sniper [6]                        | x86/Linux                                                        | x86, <b>RISC-V</b>                                                                                                                                                                                                     | parallel UM/TIM                                                | in-order, out-<br>of-order         | yes (HMP)            | uses Pin for functional simu-<br>lation, based on interval sim-<br>ulation |

| SMTSIM [115]                      | Х,                                                               | Alpha                                                                                                                                                                                                                  | TIM                                                            | out-of-order                       | yes                  |                                                                            |

| SPim [116]                        | Windows, Mac<br>OSx, Linux                                       | MIPS32                                                                                                                                                                                                                 | FUNC                                                           |                                    | no                   | used largely for teaching in<br>academia                                   |

| TEM2P2EST<br>[117]                | x86/Linux                                                        | Alpha, Pisa, ARM,<br>x86                                                                                                                                                                                               | power/TIM (cycle-<br>level)                                    | out-of-order                       | no                   | based on SimpleScalar                                                      |

| Turandot [118]                    | AIX, Linux                                                       | PowerPC                                                                                                                                                                                                                | UM/TIM                                                         | in-order, out-<br>of-order         | yes                  |                                                                            |

| Wisconsin Wind<br>Tunnel II [119] | SPARC                                                            | SPARC                                                                                                                                                                                                                  | parallel discrete<br>EvDr/EDr                                  | in-order                           | yes                  | part of Wisconsin Wind Tun-<br>nel Project                                 |

| Zesto [120]                       | x86                                                              | x86                                                                                                                                                                                                                    | UM/TIM cycle-<br>level                                         | out-of-order                       | yes                  | built on top of SimpleScalar                                               |

| ZSim [7]                          | x86/Linux                                                        | x86-64                                                                                                                                                                                                                 | parallel TIM/UM<br>simulator                                   | out-of-order,<br>in-order          | yes                  |                                                                            |

| Note: FUN                         | C=functional, TIM=tin<br>MOD=modula                              | Note: FUNC=functional, TIM=timing, EvDr=event-driven, FSys=full system, UM=user mode, EDr=execution-driven, TD=trace-driven, MOD=modular, IS=instruction set, µAr=micro-architecture, HMP=heterogeneous multiprocessor | m, FSys=full system, U                                         | M=user mode, ED<br>HMP=heterogenec | r=execution-dr       | ven, <b>TD=</b> trace-driven, sor                                          |

simulating multicore processors consumes more resources and time than single-core processors. Many techniques and innovative strategies have been proposed for accelerating the speed of simulation. Some of them are discussed below:

## 1) SAMPLED SIMULATION

One of the mostly used techniques to accelerate simulation is Sampling. In sampled simulation, instead of simulating the entire benchmark only a small number of samples are simulated. These samples are groups of instructions, which are considered to represent the entire benchmark. The selection of the sampling points can be done in two ways: (1) statistical sampling and (2) targeted sampling. One approach for statistical sampling is to randomly pick samples from the entire instruction stream to acquire unbiased samples. The other statistical sampling approach is to go for periodic sampling which selects sampling units at regular intervals across the entire program. For example, periodic sampling is used by SMARTS [20] and Flexus [43].

Targeted sampling picks sampling points after analyzing program's behavior. Single sampling points/units are selected from each phase (a phase is a group of a large number of consecutive instructions that have a similar behavior). The weights of phases are usually calculated and considered in choosing sampling points. Since target sampling uses program behavior to pick sampling points, it is possible that the targeted sampling may result in less number of total samples compared to statistical sampling. However, target sampling cannot provide a confidence bound on performance estimates [33]. SimPoint [125] is a tool that follows the targeted sampling approach and uses basic blocks to detect program phases. SimPoint combines basic blocks into intervals, then uses Manhattan distance to find the similarities among different intervals to locate program phases; each phase contains many intervals [126]. Intervals from each phase are chosen as a sampling point for simulation to represent a complete picture of program execution. Each sampling point is referred as a simulation point or sometimes a SimPoint. Yi et al. [127] performed a comparison of Simpoint and SMARTS. Their study indicated that SMARTS is more accurate but slower than SimPoint.

There are two challenges associated with sampled simulation techniques [33], [128]. The first challenge is to accurately provide a sampling point with its architectural state's starting image (ASSI). Functional simulators require ASSI, the processor's architectural state (register and memory contents), for each sampling point to achieve a correct output. In addition, timing (performance) simulators use ASSI checkpoints for accurate timing simulation, i.e., the ASSI should be as close as possible to the program's architectural state at the beginning of the simulation point to achieve accurate simulation results. Many simulators have a *fast forwarding* feature that uses a quick functional simulator to construct the ASSI [33], [128]. Timing simulators use detailed simulation for the entire sampling point, but switches to functional simulation at the end of each sampling point until it reaches amount of time when the sampling units are located far from the start of the program and far from each other in the dynamic instruction execution [33]. In addition, using fast forwarding and detailed simulation intervals serializes the simulation for all the sampling points. This means, to construct the ASSI for the next sampling unit, one needs to simulate all previous sampling units and fast forward between the sampling units. One technique that can be used to speed up fast forwarding is direct execution as implemented in PTLsim [5], where the program is executed on native hardware directly instead of functional simulation. Checkpointing [129] is another technique that can be used to solve this problem of initiating an architectural state [33]. Checkpointing stores the ASSI up until a sampling point. This checkpoint is then loaded from a disk during sampled simulation. Checkpointing also allows parallel simulation as opposed to fast forwarding [33]. However, the space required to store large checkpoint files on disk is a drawback associated with checkpointing.

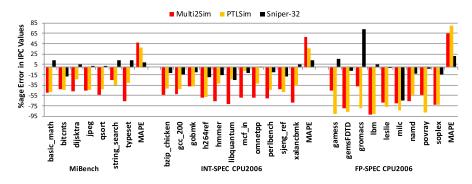

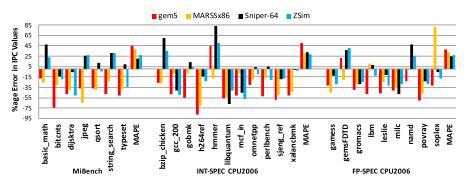

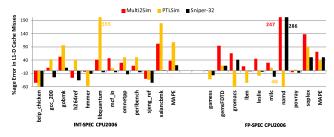

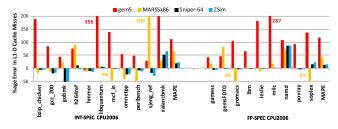

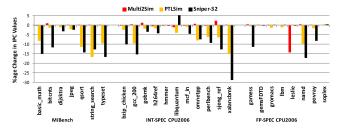

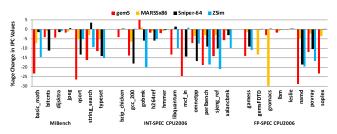

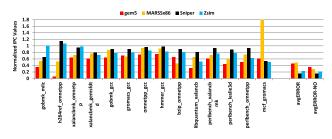

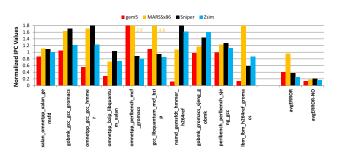

the next one. Fast forwarding can consume a considerable