# A Survey on Network Verification and Testing With Formal Methods: Approaches and Challenges

Yahui Li<sup>®</sup>, Xia Yin, Zhiliang Wang, Jiangyuan Yao, Xingang Shi, Jianping Wu, Han Zhang, *Member, IEEE*, and Qing Wang

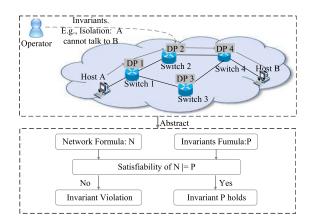

Abstract—Networks have grown increasingly complicated. Violations of intended policies can compromise network availability and network reliability. Network operators need to ensure that their policies are correctly implemented. This has inspired a research field, network verification and testing, that enables users to automatically detect bugs and systematically reason their network. Furthermore, techniques ranging from formal modeling to verification and testing have been applied to help operators build reliable systems in electronic design automation and software. Inspired by its success, network verification has recently seen increased attention in the academic and industrial communities. As an area of current interest, it is an interdisciplinary subject (with fields including formal methods, mathematical logic, programming languages, and networks), making it daunting for a nonprofessional. We perform a comprehensive survey on well-developed methodologies and tools for data plane verification, control plane verification, data plane testing and control plane testing. This survey also provides lessons gained from existing solutions and a perspective of future research developments.

Index Terms—Network verification, network testing, formal methods, network reliability, software-defined network.

# I. INTRODUCTION

ODERN enterprise networks are complicated. A single service request in Google or Azure is responded to by hundreds of servers. Networking devices modify packets quite differently, e.g., firewalls, which interdict messages based on various rules, and load balancers, which spread traffic using hash functions. Hundreds of devices perform complex network functions, which is quite challenging and hence error prone. Errors (e.g., configuration

Manuscript received November 6, 2017; revised May 11, 2018 and June 26, 2018; accepted August 23, 2018. Date of publication August 31, 2018; date of current version February 22, 2019. This work was supported in part by the National High Technology Research and Development Program of China 863 Program under Grant 2015AA016105, and in part by the National Natural Science Foundation of China under Grant 61402253. (Corresponding author: Zhiliang Wang.)

- Y. Li, X. Yin, J. Wu, and Q. Wang are with the Department of Computer Science and Technology, Tsinghua National Laboratory for Information Science and Technology, Tsinghua University, Beijing 100084, China.

- Z. Wang and X. Shi are with the Institute for Network Sciences and Cyberspace, Tsinghua National Laboratory for Information Science and Technology, Tsinghua University, Beijing 100084, China (e-mail: wzl@cernet.edu.cn).

- J. Yao is with the College of Information Science and Technology, Hainan University, Haikou 570228, China.

- H. Zhang is with the School of Cyber Science and Technology, Beihang University, Beijing 100191, China.

Digital Object Identifier 10.1109/COMST.2018.2868050

errors, software implementation bugs, and unexpected protocol interactions) can lead to numerous security vulnerabilities, including network outages, router oscillations and forwarding blackholes.

A survey [1] conducted by the North American Network Operators Group revealed that 35 percent of all respondents encountered more than 25 tickets per month. Other surveys revealed that Microsoft Azure suffers from more than 10,000 cores being down per hour. Unfortunately, network administrators still use primitive tools, e.g., Ping [2] and TraceRoute [3], to manage networks. In addition, a new network architecture, Software-Defined Networking (SDN), is attracting increasing attention from industry and academia [4]. The innovative features of centralized control and programmability dramatically simplify network management and enable network innovations. However, the programmability of SDN increases the risk of network errors. Traditional network testing techniques cannot be directly applied to SDN. Therefore, we urgently need automated analysis of network systems.

Network operators manage networks with experience and intuition. They have been regarded as "masters of complexity" [5]. Reasoning networks manually is challenging fundamentally because of the scale and diversity of large networks and the rapidity of deployments. Looking for a bug in a bad access control list or simple questions about a network are notoriously difficult tasks. We do not know which packet headers from host A can reach host B, let alone answer security questions such as whether group X is isolated from group Y [6]. Certain quantitative questions, such as "is my load balancer distributing evenly?" or "why is my backbone utilization poor?", are also difficult to answer.

Inspired by the well-honed automated reasoning technologies for software and hardware, networking researchers have proposed a new research paradigm, called network-level verification and testing <sup>1</sup> [5]. They regard the whole network system as a software program that takes packets from the network input edges and outputs packets of the output edge after rewriting them [2]. Previous research in networks focused on verifying the design and implementation of protocols [7], [8], rather than network verification and testing that formally verify or test the correctness of the entire network

<sup>&</sup>lt;sup>1</sup>In this paper, we use the terms 'network-level verification and testing' and 'network verification and testing' interchangeably.

#### TABLE I Data Plane Versus Control Plane

|                    | Data Plane (DP)                                                 | Control Plane (CP)                                              |

|--------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| Definition         | Collection of forwarding tables and logic that forward packets. | Program builds forwarding tables with topology and lived links. |

| Formula            | $(FIB*Packet) \rightarrow FwdResult$                            | (Config*Environment) 	o FIB                                     |

| Program types      | Forwarding table in IP network. Flow table in SDN network       | RIP, OSPF, BGP etc. in IP network                               |

| Verification tasks | For all packets, invariants hold with the forwarding tables.    | For all packets, invariants hold with the configurations.       |

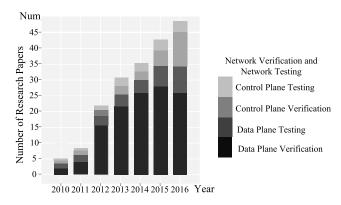

Fig. 1. Number of research papers on network verification and testing in this survey.

system by collecting network data plane or control plane information.

Recently, network verification and testing have seen increased popularity in the verification and programming language community [5], [9], [10]. Many companies and universities, including Microsoft, Stanford, and UIUC, have set up network verification research groups [11], [12]. Fig. 1 shows that research in this field has intensified. Some efforts have been made to introduce the development of formal verification techniques (e.g., model checking) [13]. This is orthogonal to our goal, which is to introduce the application of formal verification to network systems. Despite some work referring to the application of formal methods to networking [14]–[18]. a detailed survey on this topic, network-level verification and testing, has not yet be conducted. Specifically, a survey conducted by Qadir and Hasan [19] is the closest to our survey. The survey introduces the broad use of formal verification in networking, including checking security properties for different protocols (e.g., medium access control protocols, routing protocols, reliability protocols and other protocols) and verifying network systems. We focus on the application of formal method techniques to control and data plane verification (testing), therein attempting to prove or check network-wide properties rather than properties for individual protocols. Qadir and Hasan [19] provide detailed background of formal methods, but brief introduction of the works on data and control plane verification. In this paper, we focus on summarizing the developments of the techniques, and discussing future research directions in this domain field. In addition, as a new research paradigm, network verification and testing have seen increased popularity in the verification and programming language community since 2011. Some recent progresses in this area are not involved in the survey [19].

We introduce the background of this survey in Section II. Section III introduces formal methods that are the foundation

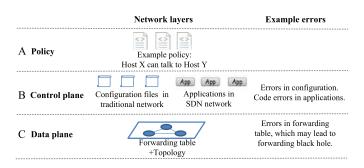

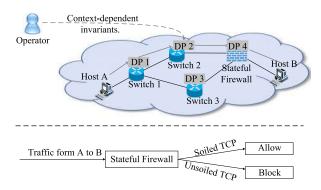

Fig. 2. Network layers and example errors. In traditional network, users implement policies (A) by configuring device-specific configurations (B). Then devices generate FIBs (C) using routing protocols, which determine the forwarding behavior of packets. In SDN network, polices (A) are implemented via SDN applications (B) in a programmable way. Then controller translates the logic of applications into flow entries installed in the switches (C).

of network verification. In Section IV, we provide a brief overview of techniques in the area. Then, we provide detailed introduction of data plane verification in Section V, control plane verification in Section VI, data plane testing in Section VII, and control plane testing in Section VIII. Section IX gives a comprehensive comparison of network verification and network testing. Sections X–XI discuss the challenges and potential research directions in this area. Finally, concluding remarks are given in Section XII.

# II. BACKGROUND

#### A. Data Plane and Control Plane

Fig. 2 illustrates the layers of network, including policy (A), control plane (B) and data plane (C). Users usually need to implement a set of policies (A), such as whereby host X can talk to host Y. In traditional networks, users use low-level configurations (B) to realize high-level policies (A) manually. Devices in networks such as routers and switches then run control protocols, e.g., routing protocols, whose parameters are defined by these configurations, finally generate forwarding information base (C). The incoming packets to these devices are handled (possibly modified or forwarded to a neighboring router) according to the forwarding state. While in SDN networks, the polices (A) are implemented via SDN applications (B) in a programmable way. Then the controller translates the control logic of the applications into flow entries to be installed in the switches (C), which are responsible for packet forwarding.

Before discussing the focus of the sub topic (data plane and control plane), we introduce the following term, *invariant*, to facilitate subsequent presentation. In verification community, an *invariant* is a property, held by a class of objects, which remains unchanged when transformations of a certain type are applied to the objects. Given a model of the system, we can check or prove whether the model meets a set of invariants.

| Abbreviation | Definition                           |

|--------------|--------------------------------------|

| ACL          | Access control list                  |

| BDD          | Binary decision diagram              |

| CTL          | Computation tree logic               |

| CP           | Control plane                        |

| DP           | Data plane                           |

| EFSM         | Extended finite state machines       |

| FIB          | Forwarding information base          |

| FSM          | Finite state machines                |

| LTL          | Linear temporal logic                |

| PCTL         | Probabilistic computation tree logic |

| PSL          | Property specification language      |

| SAT          | Satisfiability theories              |

| SDN          | Software-Defined networking          |

| SMT          | Satisfiability modulo theories       |

| TA           | Timed automata                       |

TABLE II

ABBREVIATION NOTATIONS

Invariants of the network specify the correctness properties of the forwarding or routing behavior. For example, the invariant, no forwarding loops, asserts that packets do not encounter forwarding loops in the network.

The data plane, such as the flow table in SDN networks [20] and the forwarding information base (FIB)<sup>2</sup> in traditional networks [21], is the snapshot of the forwarding table in network devices. As shown in Table I, the inputs of data plane verification tool are the data plane's snapshot and network invariants (e.g., no forwarding loops and no black holes.). It models the snapshot as logical facts, which determine whether a packet should be forwarded to a neighbor in each router or dropped. Then, it formally checks whether the snapshot is consistent with the invariants. However, it cannot detect failed links/routers or performance problems caused by network congestion. To address these challenges, researchers have proposed data plane testing. With the forwarding table and topology information, such testing generates abstract test cases via a formalized model, and converts abstract test cases into real test traffic to detect forwarding errors and performance issues [1].

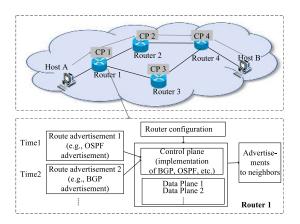

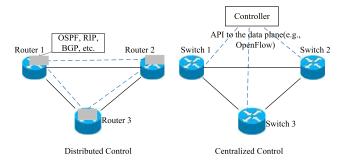

The control plane refers to the network program that establishes the data plane forwarding tables integrated with topology information – (e.g., which router ports are interconnected) and the environment (e.g., route advertisements) [22]. The control plane in traditional networks includes the algorithm protocols (e.g., OSPF [23] and BGP [24]) distributed in configuration files scattered among thousands of network devices. The control plane in SDN networks is concentrated in the controller and in the application on top of it [25]. The inputs for control plane verification and testing are route announcements, link states and other information.

The policy is the reference of con trol plane and data plane verification. To ensure the configuration and SDN program is well designed, control plane verification checks consistency between policies and the configuration or the SDN program. To ensure the network behaves as designed, data plane verification checks consistency between policies and the forwarding states of network data plane. How do users

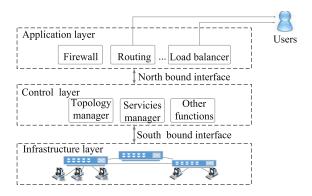

Fig. 3. A high-level overview of the software-defined networking architecture [4].

correctly check whether policies satisfy business requirements before the policies are converted in to configuration? This type of work is not within the scope of this paper, as this survey introduces verification works that check the network wide properties. We focus on whether the data plane or control plane of the actual network satisfies the policies that correspond to the invariants of the users.

#### B. Software-Defined Networking

This section introduces the basic concepts of *Software-Defined Networking*. Automatic reasoning technologies in traditional networks and SDN networks are quite different.

SDN decouples the control logic from forwarding devices. The prototype of SDN is preliminarily implemented based on the OpenFlow protocol [21]. The foundation of SDN proposed by the standardization organization the Open Network Foundation (ONF) is shown in Figure 3. The foundation defines three conceptual layers: the infrastructure layer, the control layer and the application layer [21]. (I) The infrastructure layer is generally referred to as a forwarding device and is responsible for packet forwarding. It offers programmable flow tables, which consist of many flow table entries. The controller configures the switch through the Southbound API [21]. (II) For the control layer, the controller can be seen as the 'network brain', which undertakes massive compute and storage tasks. It maintains a global network view. (III) In the application layer, applications are the programs on top of the controller and allow users to define network behaviors in a programmable way [26]. The communication interface between the controller and the applications is called the Northbound API. Generally speaking, the controller and applications represent the control logic, which forms the control plane. The control plane translates the control-logic policy of the applications into rules installed in the data plane.

The entire structure of traditional networks is highly decentralized and operates in an entirely distributed manner, making it difficult to realize automatic network verification tools. In contrast, SDN networks are built on top of standard interfaces. This enables the controller to configure and communicate among different underlying devices. These features (e.g., the centralized control logic and standard interface) enable users to verify the correctness and security network properties with formal methods.

<sup>&</sup>lt;sup>2</sup>All used abbreviation notations in this survey are listed in Table II.

TABLE III

SUMMARY OF REPRESENTATIVE TOOLS BASED ON MODEL CHECKING

| Tool        | Model language    | Specification language | Brief summary                                                  |

|-------------|-------------------|------------------------|----------------------------------------------------------------|

| SPIN [27]   | Promela           | LTL                    | Verifies distributed and concurrent systems.                   |

| NuSMV [28]  | Verilog           | LTL, CTL, and PSL      | Extends the symbolic model checking tool SMV based on BDD.     |

| Alloy [29]  | First-order logic | Alloy                  | Analyzes user-specified properties based on a partial model.   |

| UPPAAL [30] | Timed automata    | TCTL                   | Used for the verification of real-time systems.                |

| PRISM [22]  | PRISM             | CSL, LTL, and PCTL     | Models systems that exhibit random or probabilistic behaviors. |

TABLE IV

SOME APPLICATIONS OF FORMAL METHODS IN NETWORKING

| Project               | What it does                                                                                     | Based on    |

|-----------------------|--------------------------------------------------------------------------------------------------|-------------|

| Model Checking        |                                                                                                  |             |

| Sethi et al. [48]     | Present a model-checking-based method to test SDN controllers with customized model language.    | Murphi [53] |

| NICE [25]             | Performs symbolic execution and model checking to check the entire network state space.          | -           |

| Kuai [49]             | Combines partial order reduction and abstraction to perform model checking on SDN controllers.   | Murphi [53] |

| Verificare [36]       | Utilizes the Verificare modeling language to perform model checking on SDN controllers.          | Murphi [53] |

| Flowlog [50]          | Proposes a declarative finite-state SDN programming language that supports model checking.       | Alloy [29]  |

| FlowChecker [51]      | Verifies the correctness of OpenFlow networks based on symbolic model checking.                  | NumSVM [28] |

| Theorem Proving       |                                                                                                  |             |

| VeriCon [54]          | Apply theorems proving the verification of infinite-state SDN programs.                          | -           |

| Guha et al. [55]      | Propose a language for SDN controller programming, Netcore, which supports verification.         | Coq [56]    |

| Reitblatt et al. [57] | Ensure consistency of network updates using the Coq prover.                                      | Coq [56]    |

| NATKAT [58]           | Utilizes a sound program logic for verifying SDN controller based on Kleene Algebra.             | Coq [56]    |

| Symbolic Execution    |                                                                                                  |             |

| BUZZ [59]             | Generates abstract test cases for stateful data planes based on Klee.                            | Klee [60]   |

| HSA [6]               | Models packets as Ternary bit-vectors. Performs symbolic simulation for finding data plane bugs. | -           |

| SymNet [61]           | Statically analyzes the network data plane based on optimized symbolic execution.                | -           |

| Dobrescu et al. [52]  | Apply symbolic execution to verify the data plane.                                               | S2E         |

| NICE [25]             | Applies symbolic execution to exercise code paths of controllers.                                | -           |

| SAT solver            |                                                                                                  |             |

| Anteater [9]          | Verifies invariants in the data plane by an SAT solver.                                          | -           |

| NATSAT [62]           | Employs an SAT solver to verify whether the properties of the data plane are violated.           | -           |

| FLOVER [63]           | Verifies flow policies in an SDN network.                                                        | Yices [64]  |

| NoD [65]              | Implements a new SAT-based solution for the reachability set predicate in the data plane.        | Z3 [60]     |

# III. FOUNDATION OF FORMAL VERIFICATION AND TESTING

Broadly speaking, formal methods are based on mathematically techniques, which can be used in the specification and modeling of systems. This section discusses the terminology of formal methods used throughout this survey.

#### A. Model Checking

Model checking was first developed independently by Clarke *et al.* [31] and Baier and Katoen [32]. This technique checks whether the system *model* satisfies the *specifications*. The *system model* is defined by a finite state model such as automata or finite state machines (FSM). *Specifications* are described as temporal logic formulas. Model checking checks whether the system model satisfies a specification [33], [34].

Generally speaking, model checkers typically consist of three components: (i) a method that describes the state transition of the system (*S*) to be verified, where *S* is typically written in a state machine [35], a prepositional logic language [36], the Datalog language [37] etc.; (ii) a specification that describes the properties of the system with prepositional temporal logic formula (*F*), such as computation logic formula (CTL) [38], temporal logic, and linear time formula (LTL) [39]; and (iii) a checking procedure that checks whether the system satisfies the desired invariants. It is formulated as a mathematical problem of whether the state transition system model *S* satisfies formula *F*. It converts the model of the

system into logical formulas, and then, it computes the satisfiability of the formulas. After finding a violation, it produces a counterexample. The counterexamples allow users to diagnose and repair errors in the system. Various model checking tools have been proposed (e.g., SPIN [27], NuSMV [28] and Alloy [29]), as illustrated in Table III.

Since the checking procedure exhaustively searches the system state space, the size of the system state space increases exponentially. Many optimized approaches have been proposed. Bounded model checking leverages a fast SAT solver [40]. Symbolic model checking represents state transitions symbolically [41]–[44] using a Binary Decision Diagram (BDD). Other techniques (e.g., partial order reduction [45] and abstraction) reduce the size of the state space that needs to be searched.

Model checking has been widely used to find errors in software and hardware systems [46], [47]. Recently, it has attracted significant attention in the network verification and testing research community [25], [36], [48]–[51]. As illustrated in Table IV, Flowchecker, proposed by Al-Shaer and Al-Haj [51], detects network configuration bugs using the NuSMV tool. NICE [25] combines symbolic execution and model checking to test SDN applications [25]. Sethi *et al.* [48] presented another test SDN controller based on a model checking method.

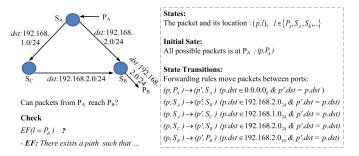

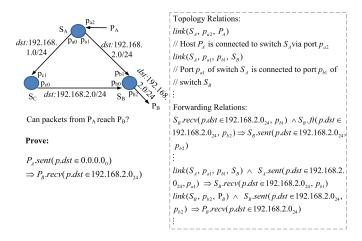

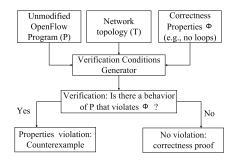

Fig. 4 presents an example network with three switches. Each switch has forwarding rules which indicate the packets forwarding behaviour. For example, forwarding rule

| Technology     | Tool          | Brief summary                                                                                             |

|----------------|---------------|-----------------------------------------------------------------------------------------------------------|

| Theorem        | Coq [56]      | An interactive theorem prover that assists in extracting a certified program from the constructive proof. |

| Proving        | HOL [66]      | Represents a family of interactive theorem provers based on higher order logics and strategies.           |

| Troving        | Isabelle [55] | A popular LCF-style theorem prover (written in Standard ML) that can work with various logics.            |

|                | Klee [60]     | Performs automatic generation for programs. The supported languages are C and LLVM.                       |

| Symbolic       | SAGE [67]     | Dynamic symbolic execution engine with whitebox fuzzing. The supported languages include C and C++.       |

| Execution      | Pex [68]      | A dynamic symbolic execution engine. The supported language is NET.                                       |

|                | JPF [69]      | Combines symbolic execution and model checking. The supported language is Java.                           |

|                | Z3 [70]       | A state-of-the-art SMT solver from Microsoft Research.                                                    |

|                | Yices2 [64]   | An efficient SMT solver that can also act as an SAT or a MaxSAT solver.                                   |

| SAT/SMT Solver | CVC4 [71]     | Works with a version of first-order logic.                                                                |

|                | MiniSAT [72]  | Supports incremental SAT and has mechanisms for adding non-clausal constraints.                           |

|                | Kodkod [73]   | An SAT-based constraint solver that can work with first-order logic                                       |

$\label{thm:constraints} TABLE\ V$  Summary of Representative Tools Based on Formal Methods

Fig. 4. A simple network with three switches. Switch  $S_A$  has a forwarding rule  $r_{A1}$  that forwards packet whose destination is 192.168.1.0/24 via port  $p_{a0}$ , a forwarding rule  $r_{A2}$  that forwards packet whose destination is 192.168.2.0/24 via port  $p_{a1}$ . Rules in switch  $S_B$  and switch  $S_C$  are similarly defined.

Fig. 5. A simple model checking encoding of the network in Fig. 4. The initially state represents all possible packets are at host  $P_A$ . The forwarding rules on switches moving packets between ports can be viewed as state transitions

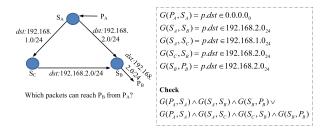

$r_{A1}$  on switch  $R_A$  forwards packets whose destination ip are 192.168.1.0/24 via port  $p_{a0}$ . The *states* of the network system are defined by the *packet and its location*. All possible packets are at host  $P_A$ , which is the initial state. The forwarding rules on switches moving packets between ports can be viewed as state transitions. The corresponding model checking encoding of the network is shown in Fig. 5. The state is encoded as (p, l), where l is the location of the packet p. The initial state is encoded as  $(p, P_A)$ , which represents all possible packets are at host  $P_A$ . The relevant transitions are defined according to the forwarding rules. For example, the formula,  $(p, S_A) \rightarrow (p', S_B)$   $(p.dst \in 192.168.2.0_{24} \& p.dst' = p.dst)$ , represents the forwarding logic of  $r_{A2}$ . We introduce a convenient way to write the matching condition in forwarding rules. For example,  $dst \in 192.168.2.0_{24}$  is a boolean formula

testing the equality between the first 24 bits of destination ip and 192.168.2.0. After encoding initial state and state transition, we define a property, there exists a path such that packets from  $P_A$  to  $P_B$  can be expressed as  $EF(l=P_B)$  in CTL. In syntax of CTL, E means that there exists at least one path starting from the current state where the property holds, and F means that the property eventually has to hold (somewhere on the subsequent path). The model and property can be input to a model checker engine (e.g., NuSMV [28]). If the engine returns pass, the property holds on the system model. If the model violates the property, the system will return a counterexample. In this simple example, the model satisfies the input property.

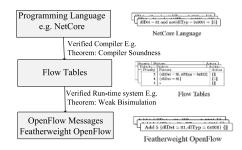

#### B. Theorem Proving

Theorem proving is another important formal verification method. As depicted in [74] and [75], it consists of formulas that represent the implementation and that describe the system properties. The formulas (also known as formalized mathematical statements) consist of a set of axioms and derivation rules. This technique checks whether the property is valid with the axiom and derivation rules [74]. In early research, engineers manually designed a verification framework and then manually verified the reasoning correctness in the sketch. Recently, procedures (e.g., decision procedures) have been processed automatically by the machine, named, theorem prover. Theorem proving can be classified into automated theorem proving and interactive theorem proving. The former addresses proving mathematical theorems with computer programs. Despite the complexity, automated reasoning over algebraic proofs greatly improves developments in computer science. Interactive theorem proving handles the proof problem with human assistance. Users have to support the axioms and proof strategies with expert knowledge, which is the most creative part of the verification [75]. Table V lists various theorem provers that are routinely used in verification projects.

Unlike model checking, theorem proving does not need to exhaustively check the entire state space. This technique takes a mathematical statement and checks the proof. When checking the properties of a network system with theorem proving, users can check all admissible network topologies specified with the logic. However, scaling theorem proving to

Fig. 6. A simple theorem proving encoding of the network in Fig. 4. The statements on the right of the figure define the forwarding logic of the network. The formula on the lower left of the figure defines the invariant: packets from  $P_A$  can reach  $P_B$ .

complex networks is challenging. It heavily depends on the users' knowledge of the system. In general, the underlying logics are very complex and difficult to understand. In addition, the process is slow and fallible because it requires user interaction in most cases.

Theorem proving is popular in network verification [54], [55], [57], [58]. As shown in Table IV, VeriCon [54] applies theorem proving to verify infinite-state SDN programs. Reitblatt *et al.* used the Coq prover to ensure the update consistency of SDN networks [76]. Guha *et al.* [57] proposed Netcore for SDN controller programming, which also uses the Coq tool.

Fig. 6 shows a theorem proving encoding of the network in Fig. 4, which is motivated by VeriCon [54]. To verify the properties of the system, the theorem prover receives three inputs, including the forwarding rules, the toplogy of the network system, and an invariant formula such as a firstorder logic formula. Topology relations define the links in the topology. For example,  $link(S_A, p_{a1}, p_{b1}, S_B)$  means that port  $p_{a1}$  of switch  $S_A$  is directly connected to port  $p_{b1}$  of switch  $S_B$ . Forwarding relations model the logic of existing forwarding rules on switches moving packets between ports. For instance,  $S_A.ft(p.dst \in 192.168.2.0_{24}, p_{h2})$  defines a matching condition in a forwarding rule  $r_{B2}$  in the network.  $S_B.recv(p.dst \in 192.168.2.0_{24}, p_{b1})$  defines that the packet p can be received on switch  $S_B$  at ingress port  $p_{b1}$ .  $S_B.sent(p.dst \in 192.168.2.0_{24}, p_{b2})$  defines that the packet p can be sent on switch  $S_B$  at port  $p_{b2}$ . To check whether packets from  $P_A$  can reach  $P_B$ , we can prove whether the formula on the lower left of the Fig. 6 is true. After users inputs the deduce rules, a theorem prover can prove whether the property holds.

# C. Symbolic Execution

Symbolic execution is a popular approach for analyzing a software program and represents program inputs with symbolic values instead of concrete values [77]. On the surface, the network does not resemble software code. It consists

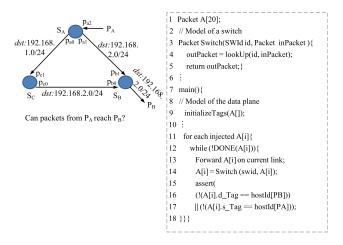

Fig. 7. A simple symbolic execution encoding (pseudocode) of the network in Fig. 4. Lines 3-5 in the pseudocode indicate the behaviour of switch. Lines 11-14 model the forwarding behavior of data plane. Lines 16-17 define an assertion, which indicates the network property.

of routers, network interface cards, cabling etc. Moreover, the entire network can be considered as the "program". For instance, a forwarding table of the router can be considered as a program statement that forwards packets to the destination address. Therefore, the symbolic execution concept can be applicable to the analysis of the network. Instead of running with the normal inputs, it uses symbolic variables representing arbitrary values as inputs to run a program. An interpreter follows the program and logically forks and follows both branches at each code branch. It exercises all possible paths and records the constraints of the symbolic variables on each path, referred to as path conditions. Then, it solves path constraints using a constraint solver, and it obtains inputs that follow the associated path during an execution [78].

Unfortunately, symbolic execution does not scale to large programs because of path explosion. The number of feasible paths increases exponentially with increasing program size. This is unacceptable when applied to actual network code [52], [79]. The various efforts shown in Table V have made symbolic execution practical for verification such as by merging similar paths and parallelizing independent paths.

Symbolic execution has been widely used in network verification and testing [6], [25], [52], [59], [61], as shown in Table IV. SymNet [61] analyzes the network data plane based on symbolic execution [80]. Dobrescu and Argyraki [52] applied symbolic execution to verify the data plane code. NICE [25] also employs symbolic execution to the exercise code paths of the controller [25]. BUZZ generates abstract test cases for stateful data planes based on Klee [59].

Fig. 7 shows a symbolic execution encoding of the simple network in Fig. 4, which is motivated by BUZZ [59]. The program snippet indicates how forwarding rules move packets between ports. In each iteration, a packet is processed (line 12) in two steps: (1) it is forwarded to the other end of the current link (line 13), (2) it is then passed as an argument to the switch connected at this end (line 14). The output packets are then processed in the next iteration. We can define an assertion: packets from  $P_A$  can be moved to  $P_B$  (lines 16-17).

Fig. 8. A simple SAT encoding of the network in Fig. 4. The forwarding rules on switches move packets between ports, which can be formulated as boolean formulas on the upper right of the figure.

A[i].s\_Tag records the original source ip of the packets, and A[i].d\_Tag records the current location of the packets. This will allow the symbolic execution engine to find a "violation". We input the program and assertion into a symbolic execution engine (e.g., Klee [60]). The engine injects symbolic packets and tracks their evolution through the program of the network. The engine ultimately returns whether the assertion holds.

#### D. SAT/SMT Solvers

Many practical problems in network verification have been reduced to SAT problems and solved by SAT solvers. The satisfiability problem is as known as SAT and can be applied to all logic formulas [81]. If the given propositional formula is satisfiable, we can obtain values of the boolean variables that make the formula logically true. A Boolean formula consists of Boolean variables and operators. The input of the SAT solver is a formula expressed in propositional logic theories. The solver automatically decides on the satisfiability in the corresponding syntax.

The satisfiability modulo theories (SMT) problem generalizes pure the SAT problem. To express design and verification conditions, SMT provides first-order theories [82]–[84]. The express ability of first-order logic (e.g., difference logic, arrays, bit-vectors, and linear arithmetic) is much greater (richer) than that of propositional logic [85] in SAT. Both SAT and SMT have proven to be typical NP-complete problems, which are difficult to solve in theory. Fortunately, various SAT/SMT tools, as shown in Table V, have been proposed and seen rapid progress [13], [86], [87].

SAT/SMT solver has attracted significant attention in network verification and testing [9], [62], [63], [65]. FLOVER verifies the properties of SDN networks based on the SMT Yices solver [63]. Anteater employs an SAT solver to determine whether the properties of the network data plane are violated [9]. NetSAT is another example that verifies SDN networks based on an SAT solver [62].

A simple SAT encoding of a simple network is shown in Fig. 8. It is motivated by Anteater [9]. Similarly, we encode the matching condition in forwarding rules in a convenient way. For example, the matching condition in rule  $r_{A2}$  in Fig. 8 is represented as  $dst \in 192.168.2.0_{24}$ . The forwarding rules on switches move packets between ports, which can be formulated as a boolean formulas. For example, the forwarding rule at  $S_A$  which forwards packets to  $S_B$  is formulated as a boolean formula  $G(S_A, S_B) = p.dst \in 192.168.2.0_{24}$ . The formula

TABLE VI Summary of Formal Methods Used in Networking

| Technique       | Model<br>Check-<br>ing | Interactive<br>Theorem<br>Proving | Automated<br>Theorem<br>Proving | Symbolic<br>Execu-<br>tion | SAT/<br>SMT<br>Solver |

|-----------------|------------------------|-----------------------------------|---------------------------------|----------------------------|-----------------------|

| Soundness       |                        |                                   |                                 |                            |                       |

| Automation      |                        | ×                                 | $\sqrt{}$                       | $\sqrt{}$                  |                       |

| Generic         | ×                      | $\checkmark$                      |                                 | ×                          | ×                     |

| Counterexample  | $\sqrt{}$              | ×                                 | ×                               | $\checkmark$               | $\checkmark$          |

| State-explosion |                        | ×                                 | ×                               |                            | ×                     |

$G(P_A,S_A) \wedge G(S_A,S_B) \wedge G(S_B,P_B)$  encodes the constraints on the physical path  $P_A \rightarrow S_A \rightarrow S_B \rightarrow P_B$  in Fig. 8. The constraints on the path  $P_A \rightarrow S_A \rightarrow S_B \rightarrow P_B$  in Fig. 8. The similarly defined. If we want to check whether packets can be delivered from  $P_A$  to  $P_B$  (which is defined by the formula on the lower of Fig. 8), we can query the formula with an SAT solver (e.g., Z3 [70]). After we input the formulas, if the solver returns true, then the property holds; otherwise, it returns a counterexample.

#### E. Conclusion on Formal Methods

We provide a comparison of well-known formal methods. As shown in Table VI, the first characteristic is soundness, which indicates that the results verified by the technique are always true. A technique is termed sound if the results verified by it are always true. All techniques in Table VI can be termed sound. Note that symbolic execution can be sound in principle. For symbolic execution, users simply provide their program, and the symbolic execution engine will examine all the feasible paths to generate test inputs or check assertions. In fact, the number of possible inputs of the system is usually very large and cannot be covered even in symbolic form. In order to tackle path explosion, techniques like approximations are often introduced [88]. However, those approximations techniques can make the execution unsound. The second characteristic is automation: a technique is automatic if it does not require user guidance. As well known, model checking is a automatic verification technique for finite-state systems. Logic in theorem proving is expressive for defining many formal language semantics and concepts in mathematics. As introduced earlier, theorem provers consist of automated theorem provers and interactive theorem provers. The main challenge of interactive theorem provers is proof automation. They always require explicit user guidance in the verification process [55]. The third characteristic refers to whether the context of the problem being modeled is generic. In terms of tackling a wide range of problems, among all techniques in Table VI, theorem proving is the only technique that supports verifying generic problems. Theorem proving supports verifying generic theorems, as it does not require an instantiation. For example, theorem proving is able to verify that an SDN program is correct on all admissible topologies and for all possible (infinite) sequences of network events [54]. While model checking usually requires a specific instantiation (e.g., a particular network topology and a specific sequence of network events) [25]. Similarly, symbolic execution cannot verify the general property for all possible networks (e.g., the correctness property of the SDN program for all possible sequences of network events) [25]. SAT/SMT solvers decide whether logic formula is satisfiable, and they also require an instantiation (e.g., the correct property holds on a specific topology [89]). The fourth characteristic is the provisioning of illustrative counterexamples upon finding a bug. Both model checkers, symbolic execution engines and SAT/SMT solvers provide one counterexample when invariant violation occurs. However, theorem proving does not provide an example with a negative connotation, which restricts the ability to debug the system. The final characteristic refers to state-explosion that must be addressed to solve most real-world problems. Symbolic execution engine suffers the explosion problem as the growth of code path. SAT/SMT solvers decide whether logic formula has a solution. They do not have a notion of state. Model checkers face a combinatorial blow up of the state-space. If we use model checking to check that the systems (e.g., finite state SDN programs) behave correctly, scaling the method to large networks is highly nontrivial [49]. While, theorem proof does not have a notion of state, and it does not model the state-space of the system. Users usually try to do theorem proof as the main verification to avoid the state-explosion problem.

#### IV. OVERVIEW

In this section, we introduce the shortcomings of traditional analysis approaches for networks, and summarize how the verification techniques in each plane attempt to address the challenges. In addition, we briefly explain how each plane in traditional and SDN networks impacts the choice of formal verification techniques.

As introduced earlier, the complexity of a network can inevitably lead to errors. Clearly, manually reasoning, such as checking mailing lists or naively using ping or traceroute, is inefficient. Some works check for problems in the network in a black-box manner. For instance, they send probes or review logs, which is very slow for detecting failures. Some analysis approaches which are based on the information of network configurations have been also proposed. For instance, FIREMAN [90] automatically analyzes ACLs in configuration files using a rule graph model. However, they are developed on customized models for limited aspects of the configuration. Other methods check specific correctness properties of the network to handle complexity. In addition, because they do not analyze all aspects of the configuration, they are inefficient at helping users determine how the discovered errors impact the final packet forwarding of the network.

To address these challenges, data plane verification approaches have been proposed to *check the combined impact of all configuration aspects* [9]. The first application of formal verification techniques to the data plane was Anteater [9]. Anteater avoids modeling complex protocol behaviors in configurations by analyzing the FIB in networks. It can verify network invariants such as reachability, isolation and loop freedom. Similar to Anteater, various data plane verification works (e.g., HSA [6]) focus on verifying forwarding tables. However, most works can only support off-line verification at low speeds. Some works, such as Veriflow [91],

improve and optimize the calculation, and they can verify in near real time. Moreover, there are various middleboxes (e.g., firewalls) in the data plane whose forwarding behaviors are determined by previously observed traffic. Some tools, including SymNet [61] and VMN [92], utilize algorithms to verify such stateful data planes. Other works, such as SLA-verifier [93], attempt to use algorithms to verify performance properties. While these works represent great progress for data plane verification, there are a number of open problems in this area. For example, one of the main problems is scalability in the verification of stateful data planes.

The only difference is the data collection process when we verify the data plane in traditional vs SDN networks. When we verify traditional networks, we can collect FIBs from networking devices through SNMP, or terminals. When verifying SDN networks, with the Southbound Interface, we can obtain the forwarding rules by monitoring the rules, which are inserted, modified or deleted in switches by the controller. SDN alone does not make the data plane verification problem easy. It makes data collecting much easier so that we can verify the data plane in real time by monitoring rule updates. The details of data plane verification are shown in Section V.

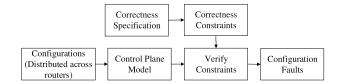

Control logic in SDN is logically centralized in the controller, in contrast to distributed protocols in devices in traditional networks. Therefore, we introduce control plane verification work in traditional networks and in SDN networks. In SDN networks, the task can be converted into how to verify the program code of the SDN controller and applications. Therefore, formal verification techniques, such as model checking, theorem proving and symbolic execution, which are widely used in code verification, can also be used to verify SDN programs. In traditional networks, due to the complexity of routing protocols and their interactions, it is not an easy task to verify all aspects of a configuration. Some standard formal verification methods (e.g., model checking and theorem proving) cannot be applied to this verification task. For example, due to the huge state space of the distributed devices in network, verification via model checkers is not scalable (also known as state explosion problem). Because of the complex logic of the control plane, the network invariants also cannot be proved by standardized theorem provers.

Unlike prior configuration analysis work that customizes models for limited aspects of the configuration and checks specific correctness properties, some work has made progress in configuration verification. Batfish [94] can simulate the behavior of all distributed protocols to obtain the forwarding tables; then, it verifies the network properties with a data plane verifier. ARC [95] abstracts the control plane as abstract weighted graphs. ERA [96] and Minesweeper [89] analyze the control plane via the abstraction of a special data structure: the route record. This is significant progress; however, scalability is an open problem in this field. The details of control plane verification in traditional networks are shown in Section VI-A.

Although SDN can be tailor-made to suit the user's needs, its programmability amplifies the opportunity for errors. The control plane in SDN networks is the program of the centralized controller and applications. These verification works can be classified into verifying the SDN programs and developing

verified controller. First, certain tools (e.g., Kuai [49] and Veificare [36]) check the SDN program using model checkers. In contrast, VeriCon [54] uses first-order logic to formulate the network and invariants, and it then proves the correctness of the program. Second, various verification-friendly languages have been proposed for SDN controllers (e.g., Flowlog [50] and NATKAT [58]). They can prevent problematic rules from being installed on the data plane. The details of control plane verification in SDN networks are shown in Section VI-B.

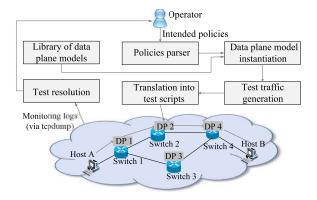

Data plane verification and control plane verification cannot be used to determine if there is a hardware failure or congestion problems. Network testing is complementary to network verification. Network testing tools detect these types of errors by systematically generating packet probes. They observe whether the actual forwarding violates the intentions of the network operator. In SDN networks, testing focuses on checking the behavior of each individual behavior of each switch, as the controller has an overview of each switch. Monocle [97] and RuleSope [98] were developed to check the flow tables in the switch. In traditional networks, testing probes are usually designed in an end-to-end manner. For instance, ATPG [99] can check both failure rules and performance failures such as congestion. The details of data plane testing are shown in Section VII.

Most control plane testing works have focused on the control plane in SDN networks. Although some efforts have been made to analyze and verify configurations, no related work on control plane testing in traditional networks has been performed. Most control plane testing approaches have been proposed to detect design and implementation errors. Certain white-box testing approaches (e.g., NICE [25]) assume that the sources code of the controller can be obtained. They extract formal models from the source codes and perform modelbased testing to find faults. Because these methods depend on the application's source codes, they cannot test controllers developed in languages that they do not support. To address this challenge, various black-box testing approaches have been proposed. For instance, Yao et al. [100], [101] described the system behaviors with parallel component models in a novel manner. The details of control plane testing in SDN networks are given in Section VIII.

# V. TECHNIQUES FOR NETWORK DATA PLANE VERIFICATION

This section provides a detailed description of data plane verification techniques. Compared with the control plane, the data plane has well-understood semantics and reflects the combined impact of all configuration aspects. The data plane does not need to unify diverse configuration languages from different vendors (e.g., Cisco and Arista) or model dynamic behaviors across various protocols. Fig. 9 summarizes a high-level image of data plane verification. Given a topology and network data plane snapshot, it derives a logical formula that models the entire network. It then verifies logical formulas derived from the specified invariants. The invariants specify the correctness conditions of the forwarding behavior in the

Fig. 9. Workflow of data plane verification. DP refers to data plane (forwarding information bases). The FIBs and user's invariants are collected. Then they are expressed with formal formulas. With novel algorithms, we can verify whether the network model stratify these invariants.

network, including the absence of loops, packet reachability and bidirectional forwarding.

For data plane verification, the only difference between traditional and SDN networks is the data collection process. When verifying traditional networks, we can collect FIBs through SNMP, terminals, or control sessions. For SDN networks, we can obtain the forwarding rules by monitoring the rules that are inserted, modified or deleted with a layer controller and switches.

#### A. Static Analysis and Off-Line Verification

Significant effort has been made to verify the actual behavior of a network through formal analysis of data plane states. In early research, such tools collected the FIBs and then verified the properties off-line. If the network state violated an invariant, these tools gave counterexamples to help users find the errors. Anteater [9] realized the first verification system of the data plane based on the reachability algorithm proposed by Le *et al.* [102]. FlowChecker [51], NetSAT [62], and HSA [6] are also based on similar ideas. These techniques indeed make data plane verification of widespread interest.

1) Verification Based on SAT Solver: Anteater [9] was the first data plane verification system used to detect errors in networks including ACLs, VLAN tags, etc. First, it obtains the data plane snapshot by collecting forwarding tables. Second, the operator defines the invariants (e.g., forwarding, connectivity, or consistency) to be checked against the network. Third, it encodes the snapshot into Boolean expressions and translates the invariants into SAT instances. Then, Anteater checks the invariants with an SAT solver. The system derives a counterexample (e.g., a packet header or FIB entries) to assist in diagnosis once violations occur. Anteater finds various bugs such as forwarding loops caused by configuration errors in the campus network and packet loss in router software (Quagga).

NetSAT [62], proposed by Zhang and Malik, is another approach that reduces the data plane verification problem to an SAT problem. NetSAT also provides a framework for modeling networks and verifies a set of network invariants. Compared with Anteater, it achieves better performance. For

instance, loops are caught in Anteater by making two copies of every switch and checking if each switch can reach its copy. Each switch must be checked separately, which is extremely inefficient. In contrast, NetSAT builds a single formula and checks the loop invariant. NetStat is more modular because it separates the network from the invariant formula.

However, both Anteater and NetSAT have limitations. First, if the FIBs dynamically change while being collected, an inconsistent data plane snapshot will be produced, resulting in false positives. Second, if the network suffers from reachability failures, it is difficult to collect the FIB snapshots. Third, these systems suffer from poor scalability and minimal time efficiency problems. For instance, Anteater spends two hours checking three standard invariants in the campus network. In addition, these systems only provide a single counterexample if an invariant violation occurs, which makes it difficult to locate which rule leads to the violation.

- 2) Verification Based on Model Checking: Flowchecker [51] applies model checking to SDN network. In fact, Al-Shaer et al. have been working on firewalls networks with model checking for 10 years [103]. FlowChecker encodes forwarding rules into Boolean expressions. In addition, network invariants are expressed with Computation Tree Logic (CTL). FlowChecker uses the binary decision diagram (BDD) to model a state machine that encodes an inter-connected network of OpenFlow switches behavior, where BDD is the data structure that can compress the state space. In addition, then it uses symbolic model checking tool NuSVM [28] to check network invariants. Although Flowchecker could check the correctness of the configuration deployed by new protocols, it suffers a serious scalability problem. Evaluation shows that it can be only applied to the small-scale network.

- 3) Verification Based on Symbolic Simulation: Unlike the Anteater, HSA [6] proposed by Kazemian et al. can find all counterexamples, when a violation occurs. HSA is a vendorindependent and protocol agnostic verification framework. It is a novel methodology that combines formal methods (model checking, symbolic simulation) with network domain features together [5]. First, packet headers are modeled as subsets of a geometrical space. Each bit in the geometrical space is commensurate with one dimension in space and does not have a protocol-specific (associated) meaning. Second, the network topology is modeled using a topology transfer function  $\gamma$ . Meanwhile, the networking boxes (e.g., routers and firewalls) are abstracted as transfer functions  $\gamma$  on sets of headers.  $\phi$ consists of an ordered set of rules. HSA computes reachability sets from A to B by composing  $\phi$  and  $\gamma$  along all paths. It can check against network invariants (e.g., reachability failures, routing loops and slice isolation) with several algorithms. However, when the head space is 80 bits, the cost of exploring the head space state of  $2^{80}$  packets is huge. HSA then uses some optimizations based on the cube compression technique to mitigate the state space explosion issue.

- 4) Verification Based on SMT Solver: Frameworks such as Anteater and HSA cannot detect non-direct network violations (such as OpenFlow's Set-Field or Goto-Field modification actions) or perform stateful monitoring. FLOVER [63] extends

these techniques. FLOVER models and verifies intermediate actions (e.g., 'goto' and 'set' actions). FLOVER demonstrates the conformance of flow rules against network invariants. It translates flow tables into many Yices (an SMT solver) assertions. Finally, it detects whether they are inconsistent with network invariants.

- 5) Verification Based on Symbolic Execution: Dobrescu et al. proposed a verification tool [52] that checks whether a software data plane satisfies invariants (e.g., bounded-execution, crash-freedom, and filtering). It is challenging to check these invariants in general software; the problem is even unsolvable with existing tools. Dobrescu et al. sidestepped the challenge by combining symbolic execution and compositionality with domain optimization. As long as the pipeline meets some standards, it can be utilized to validate the entire data plane of the network.

- 6) Conclusion on Off-Line Verification: The abovementioned approaches statically analyze network data plane snapshots. Anteater makes data plane verification practical by converting it into an SAT problem. HSA [9] addresses static checking using functional simulation. FlowChecker [51] encodes flow tables into BDDs and uses model checking to verify security invariants. FLOVER [63] leverages the ability of Yices to efficiently verify flow rule sets. Table VII compares these tools.

Frameworks such as Anteater and NetSAT provide a single counterexample if an invariant violation occurs. In contrast, HSA can find the full set of failed packet headers, which is useful for detecting failures. A counterexample is detrimental because operators analyze the invariant and the error for the network location. Outputting all counterexamples makes it easier to locate which rule leads to the counterexample under HSA. For example, if an ACL erroneously drops packets that are sent to 192.168.0.0/16, reachability fails with a counterexample (e.g., 192.168.1.200). We need substantially more insight to detect all dropped packets. If it outputs the set of packets being dropped, it can suggest the ACL bug more directly (e.g., packets with destinations that match 192.168.\* .\*). HSA can output all counterexamples because HSA moved beyond finding reachability predicates to finding reachability sets and for arbitrary protocols.

These tools find problems after bugs occur in the data plane, which may potentially damage the network. Despite this, these tools could play a similar role as post-layout verification tools do in hardware design but in networks.

# B. Real-Time Online Verification

Because of rule insertion and deletion performed by protocols, networks change over time. Previous tools are not adequate for checking the correctness of every network update such as the migration of fast virtual machines. The structure of traditional networks is highly decentralized and operates in an entirely distributed manner. Therefore, it can be impossible to obtain the FIBs in real time. Fortunately, in SDN networks, we can obtain the forwarding rules by monitoring the rules that are inserted, modified or deleted with a layer controller and switches. However, it has been proved in [65] that packet

| Project              | Technology          | Counterexamples | Comparison                                           |

|----------------------|---------------------|-----------------|------------------------------------------------------|

| Anteater [9]         | SAT Solver          | One             | Cannot scale to large networks.                      |

| NATSAT [62]          | SAT Solver          | One             | More modular than Anteater.                          |

| FLOVER [63]          | SMT Solver          | One             | Models set and goto table action commands.           |

| Dobrescu et al. [52] | Symbolic Execution  | One             | Combines symbolic execution with domain knowledge.   |

| HSA [6]              | Symbolic Simulation | All             | Provides a protocol-agnostic verification framework. |

TABLE VII

SUMMARY OF REPRESENTATIVE PROJECTS OF OFF-LINE VERIFICATION

filters make reachability checks NP-Complete. The problem of checking the properties in real time is more difficult. However, some efforts have been made to verify the data plane in real time, therein attempting to obtain a quick response to failures.

- 1) Heuristic Verification Based on Equivalence Classes: VeriFlow [91], [109] is the first verification system that can check network invariants within a few hundred microseconds. It can be viewed as an improved version of Anteater. VeriFlow observes state changes between the control plane and the switches. Therefore, a new rule can be verified before it is installed in the switch. First, the network is sliced into equivalence classes (ECs), in which packets experience the same forwarding actions throughout the network. Second, it builds individual forwarding graphs for every EC. Then, it traverses these graphs to check invariants. When the network changes (e.g., a forwarding rule is inserted), a very small number of ECs are affected. VeriFlow searches rules via a trie structure and updates the graph. However, it is not appropriate to verify the network of multiple controllers because of the difficulty in obtaining a complete view of the network state.

- 2) Verification Based on Incremental Computation: NetPlumber [107] is the most closely related work with VeriFlow. It incrementally checks for compliance of state changes. It models the network box as the node and establishes a dependency graph, the Rule Dependency Graph (RDG), between the rules. Network invariants are equivalently converted into reachability assertions. Once the network changes (a message goes through a network box), it updates the corresponding network dependency graph and redoes all forms of verification. Upon detecting a violation, NetPlumber blocks the change. The change must be determined by a rule, and adding a rule does not significantly affect the forwarding rule equivalence class. Moreover, it provides a policy query language, FlowExp, which is similar to FML. Therefore, it can not only define simple invariants (packet loss and loops) but also support flexible policy definitions.

However, NetPlumber takes a long time to process link access and does not apply to networks with frequent link changes. VeriFlow and NetPlumber achieve similar runtime performance. Similar to VeriFlow, NetPlumber is protocol independent and can additionally verify arbitrary header modifications, including rewriting and encapsulation.

3) Verification Based on Equivalence Classes: Atomic Predicates Verifier [104] (AP) is more efficient than previous tools (e.g., NetPlumber and Veriflow) for network verification. Packet filters are represented as a set of predicates. Yang and Lam developed a novel algorithm to calculate atomic predicate sets. Each predicate can be expressed as the disjunction of atomic predicates, which speeds up computation. Atomic

- predicates can be stored as integers, and the disjunction is computed as the union of integer sets. Therefore, packet sets can be calculated quickly, with atomic predicates being the minimum. Redundancy in forwarding and ACL is eliminated by AP Verifier. In particular, AP encodes the state model with BDDs, and the use of BDDs is more efficient than BDDs in other tools (e.g., FlowChecker [51]).

- 4) Verification Based on MapReduce: Although tools such as Anteater and Veriflow can find forwarding errors, they cannot scale to large data centers. In data center networks, the forwarding state makes it difficult to obtain an accurate snapshot (e.g., different routing processes update their switches using unsynchronized clocks). An inaccurate data plane snapshot can result in false positives. To address these challenges, Zeng et al. [105] proposed a new method for verifying very large networks, called Libra. On the one hand, Libra records network event streams from routing processes and provides an algorithm to capture table and consistent data plane snapshots in large-scale networks. On the other hand, it substantially improves scalability by exploiting the scaling properties of MapReduce. It reduces the verification task into smaller, parallel computations (e.g., partitioning based on switches or subnets). For the evaluation, Libra can verify the forwarding behavior of a network with 10,000 switches in less than a minute by harnessing 50 servers. This is the beginning of distributed computing for network verification.

- 5) Verification Based on Symmetry: Previous checkers face difficulties verifying large data centers with millions of routing rules. Most data center networks are highly regular by design. Plotkin et al. [106] proposed a new method, network transformations, to verify large networks by exploiting these regularities. In other words, the network snapshot and the invariants to be verified are transformed into simpler versions. If the transformed invariant is valid in the transformed network, the original invariant is valid in the original network. Network transformations consist of network symmetry and network surgery. It exploits the domain structure w of packet headers, packet locations, and rules distributed in devices. Irrelevant or redundant headers, rules, or ports are "sliced" away with network surgery. Experiments show that this technique speeds up the verification task in a large data center network of 100,000 virtual machines by 65x. The time needed to calculate the all-pair reachability of the virtual machines was reduced from 5.5 days to 2 hours.

- 6) Verification Based on Similarity: Most tools exploit two observations: (i) only small parts of a network tend to be affected by typical changes to the data plane, and (ii) many different packets tend to share the same forwarding behavior across the entire network. Delta-net [108] shows how to

| TABLE VIII                                                    |

|---------------------------------------------------------------|

| SUMMARY OF REPRESENTATIVE PROJECTS FOR REAL-TIME VERIFICATION |

| Project             | Optimizations                | Comparison                                                          |

|---------------------|------------------------------|---------------------------------------------------------------------|

| AP [104]            | Computes equivalence classes | Exploits a heuristic strategy to discover invariance violations.    |

| Libra [105]         | Computes via MapReduce       | Leverages distributed computing in network verification.            |

| Plotkinet al. [106] | Exploits symmetries          | Exploits regularities in rules and topology (not headers).          |

| VeriFlow [91]       | Computes equivalence classes | Exploits optimal strategy to discover invariance violations.        |

| NetPlumber [107]    | Exploits incrementally       | Verifies only small parts of model which is caused by rule changes. |

| Delta-net [108]     | Exploits similarity          | Exploits similarity among forwarding behaviors of packets.          |

effectively exploit the "similarity among forwarding behavior of packets through parts of the network". The method is proposed as the first provably amortized quasi-linear algorithm to do so. In experiments with SDN-IP, Delta-net checks a rule insertion or removal in 40 microseconds on average; this is a 10x improvement over previous tools.

7) Conclusion on Real-Time Verification: The abovementioned approaches can verify the network data plane in real time. Table VIII shows that they perform optimizations from various aspects, including (I) incremental computation. A single rule (e.g., an ACL) change does not change the network state significantly. NetPlumber [107] leverages that fact to perform incremental computation. It only performs small modifications to incorporate the rule change. (II) Equivalence Classes. Although the verification complexity is proportional to the number of headspace and forwarding rules, the number of header equivalence classes is small [110]. Khurshid et al. [91] and Yang and Lam [104] leveraged this fact. They proposed two strategies (a heuristic strategy in Veriflow [91] and an optimal strategy in AP [104]) to obtain the equivalence classes. (III) Symmetries. Plotkin et al. [106] observed that many rules and boxes are repeated. For instance, some backup routers have many redundancy rules. They exploit symmetry to increase the verification speed. (IV) Similarity. Delta-net [108] effectively exploits another characteristic, the similarity among the forwarding behaviors of packets through parts of the network, rather than its entirety. (V) Distributed computing. These approaches, except for NetPlumber and Libra [105], assume centralized computing. NetPlumber introduces a 'rule clustering' technique to enhance scalability. Libra is more efficient and is based on MapReduce, therein scaling linearly with both rules and subnets.

#### C. Optimization via Adding Functionality

The above-mentioned tools all assume that the forwarding behavior is defined by the control plane. However, networks contain not only routers but also middleboxes (e.g., caches and stateful firewalls) whose forwarding behavior is dependent on the previous traffic. In other words, the forwarding behavior of the middleboxes can be altered by the previously transmitted traffic. Fig. 10 shows a usage of reflexive ACLs. Traffic is allowed if it belongs to a TCP connection initiated by an internal host. The above-mentioned verification tools, which only take FIBs into consideration, cannot verify a stateful data plane with middleboxes. In this section, we introduce optimization techniques based on adding verification functionality such as the support of a stateful data plane.

Fig. 10. Invariants in stateful networks [59]. DP refers to data plane (forwarding information bases). The invariant here specifies that only traffic belonging to a TCP connection initiated by host B inside the department (i.e., if traffic context is "solicited") be allowed. The state of stateful firewall depends on the history traffic.

1) Verification Based on the Datalog: Existing tools, including Anteater [9], VeriFlow [91], and NetPlumber [107], assume fixed packet headers and forwarding rules. However, new mechanisms continuously result in new forwarding behaviors (e.g., adding VXLAN). Lopes et al. [65], [111] proposed an approach for automatically verifying dynamic networks, called Network Optimized Datalog (NoD). This approach uses a Datalog to specify network invariants and model network forwarding behaviors. Compared with the regular expression language, Datalog is more expressive. By adding new rules, NoD can check dynamic networks (e.g., add new packet headers without changing the internal structure of the tool). However, the Datalog engine suffers from poor scalability. To address this challenge, NOD modifies the Z3 implementation by adding new optimizations (e.g., a new combined Filter-Project operator).

The SecGuru [112] tool is an early version of NOD, deployed in the Microsoft production cloud Azure. It precisely encodes policies (policies and semantic diffs) and the analysis questions as bit-vector logic formulas. A key design aspect of SecGuru is an algorithm for compactly enumerating symbolic diffs. SecGuru requires a database of predefined common beliefs. These policies rarely change, which makes it usable as a regression test. It can also be used as a regression test suite before network policies are deployed. SecGuru proactively detects and avoids policy miscalculations that lead to security and availability issues. Each check in SecGuru takes 150-600 ms in Azure.

2) Verification Based on SMT Solver: Velner et al. [98] address the complexity of verifying safety invariants in stateful networks. Reasoning about reachability policies is

TABLE IX

SUMMARY OF REPRESENTATIVE PROJECTS THAT OPTIMIZE DATA PLANE VERIFICATION BY ADDING FUNCTIONALITY

| Project           | Technology         | Optimization (Support for)                    | Comparison                                               |

|-------------------|--------------------|-----------------------------------------------|----------------------------------------------------------|

| NOD [65]          | Optimized Datalog  | Dynamic networks and imperfect specifications | Nearly as fast as HSA but substantially more expressive. |

| VMN [92]          | SMT Solver         | Stateful boxes                                | Extends verification to stateful boxes such as NAT.      |

| SymNet [61]       | Symbolic execution | Dynamic networks and stateful boxes           | More expressive and faster than NOD.                     |

| Sung et al. [113] | SMT Solver         | Quantified invariants                         | Extends verification to support non-Boolean invariants.  |

$\label{table X} \text{Summary of Representative Projects for Data Plane Verification}$

|                       | HSA [6]      | Anteater [9] | NetPlumber [107] | VeriFlow [91] | Delta-net [108] | NOD [65]     | VMN [92]     | SymNet [61]  |

|-----------------------|--------------|--------------|------------------|---------------|-----------------|--------------|--------------|--------------|

| Scalability           | High         | Low          | Middle           | Middle        | High            | Low          | Low          | High         |

| Online                | ×            | ×            |                  |               | $\checkmark$    | <b>√</b>     | ×            |              |

| Coverage              |              |              |                  |               |                 |              |              |              |

| Packet reachability   | $\checkmark$ | $\checkmark$ | $\checkmark$     | $\checkmark$  | $\checkmark$    | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Packet header changes | ×            | $\sqrt{}$    | $\sqrt{}$        | $\sqrt{}$     |                 |              | $\sqrt{}$    |              |

| Modeling              |              |              |                  |               |                 |              |              |              |

| Model independence    | $\checkmark$ | $\checkmark$ | $\sqrt{}$        | $\checkmark$  | $\checkmark$    | ×            | $\checkmark$ | $\checkmark$ |

| Model language        | Impressive   | Impressive   | Impressive       | Impressive    | Declarative     | Declarative  | Declarative  | Impressive   |

| Expressiveness        |              |              |                  |               |                 |              |              |              |

| Routers               | $\checkmark$ | $\checkmark$ | $\checkmark$     | $\checkmark$  | $\checkmark$    | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Dynamic tunnel        | ×            | ×            | ×                | ×             | ×               | ×            | $\sqrt{}$    |              |

| NATs                  | ×            | ×            | ×                | ×             | ×               | $\checkmark$ | $\sqrt{}$    | $\checkmark$ |

| IP fragmentation      | ×            | ×            | ×                | ×             | ×               | ×            | ×            | ×            |

| Accuracy              |              |              |                  |               |                 |              |              |              |

| False positives       | $\checkmark$ | $\checkmark$ | $\checkmark$     | ×             | ×               | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| False negative        | $\sqrt{}$    | V            | ×                | $\checkmark$  | $\checkmark$    |              | $\sqrt{}$    |              |

undecidable because of unbounded ordered channels among middleboxes. They proved that checking reachability policies is EXPSPACE-complete in a stateful network.