Digital Object Identifier 10.1109/OJIES.2021.3050214

# A Survey on Reduced Switch Count Multilevel Inverters

# HARI PRIYA VEMUGANTI<sup>1</sup>, DHARMAVARAPU SREENIVASARAO<sup>1</sup>, SIVA KUMAR GANJIKUNTA<sup>1</sup>, HIRALAL MURLIDHAR SURYAWANSHI<sup>3</sup> (Fellow, IEEE), AND HAITHAM ABU-RUB<sup>4</sup> (Fellow, IEEE)

<sup>1</sup>Department of Electrical and Electronics Engineering, SR University, Warangal, India

<sup>2</sup>Department of Electrical Engineering, National Institute of Technology Warangal, India

<sup>3</sup>Department of Electrical Engineering, Visvesvaraya National Institute of Technology, Nagpur, India

<sup>4</sup>Department of Electrical and Computer Engineering, Texas A&M University at Qatar, Doha, Qatar

CORRESPONDING AUTHOR: DHARMAVARAPU SREENIVASARAO (e-mail: luckysrinu@gmail.com)

**ABSTRACT** An efficient and cost-effective power converter is a pre-requisite for the modern power applications. With the evolvement of matured medium power self-commutated switching devices, multilevel inverters (MLIs) are emerged as a promising solution for high-power medium-voltage applications. Though, MLIs are performing a promising role in industrial applications, their high device count, size, cost and control complexities have restricted their market penetration. To address the disadvantages of MLIs, researchers are continuously contributing to new generation topologies under the name of reduced switch count (RSC) MLIs. From the past decade, numerous RSC-MLIs topologies have been reported for various applications. Therefore, this paper presents a comprehensive review and classification of RSC-MLI topologies, in terms of their structure, features, limitations, suitability and selection for specific applications.

**INDEX TERMS** Power converters, multilevel inverters, reduced switch count.

# I. INTRODUCTION

The idea of reducing the switch count in inverters was originated in 1996 by proposing a low power bidirectional dclink inverters with a total of eight switches for motor drive application [1]. However, the continuous evolution of highperformance semiconductor devices has motivated the creation of various research trends in inverters, such as multilevel inverters (MLIs) [2]-[7]. The MLIs use the concept of aggregating multiple small voltage levels to synthesize a stepped output voltage waveform, which turns out to be an attractive solution for high-power, medium-voltage applications [8]. Lower total harmonic distortion (THD), reduced stress on switches, reduced dv/dt, lower di/dt and reduced electromagnetic interference (EMI) are the prime advantages of MLIs [2]-[4]. Thus, MLIs are proven to be a matured technology for various commercial and customized products for a wide power range of applications such as high-voltage directcurrent (HVDC) transmission, flexible ac transmission systems (FACTS), adjustable speed drives (ASD), active frontend converters (AFC), custom power devices (CPD), battery energy storage systems (BESS), electric vehicles (EV) and renewable energy generation (REG) [4]–[6], [9]–[17]. Among the topologies of MLIs, diode clamped (DCMLI) [4], [6], [16]–[19], flying capacitor (FCMLI) [5], [20]–[24] and cascade H-bridge (CHB) [4], [11], [14], [15], [21], [25], [26] are most popular and termed as classical MLIs. Even though, these topologies have gathered a great attention both from academia and industry, their practical implementation is heavily influenced by the application, control complexity and cost.

The main drawback of the DCMLI is its unequal loss distribution which further leads to uneven distribution of junction temperature and impart the limitations on maximum power rating, output current, and switching frequency of the inverter [4], [19]. This unequal loss distribution can be substantially improved by replacing the clamping diodes with active switches and thus, this inverter configuration is known as active neutral point clamped (ANPC) [19]. However, the advantages with ANPC comes at the expense of more complex circuit and the need to control the additional switching devices. The requirement of large number of capacitors and their pre-charge circuit limits the use of FCMLI in traction drives only [5]. On the other hand, modular structure and

fault tolerant ability of CHB turns out to be a sounding solution for applications such as FACTS, HVDC, CPD, EV and REG. Cascaded family of inverters are also characterized by cascade connection of modular chopper cells to form each cluster/phase-leg/arm. Cascaded MLI with H-bridge cells is known as cascaded H-bridge (CHB) MLI. Whereas, cascaded MLI composed with bi-directional chopper cells are known as modular multilevel inverters (MMI). However, the common concepts hidden among the family members allow to use the common term modular multilevel cascade inverter (MMCI) as a family name [15], [27]. Although, these topologies are scalable and suitable for high power applications but the requirement of isolated dc sources has limited their usage to active power transfer applications such as FACTS and HVDC [11].

The switch count of these MLIs increases with the number of levels. An increase in switch count involves additional drivers, band-circuits, isolation circuits and their associated heat sinks and protection requirements [28]-[31]. Moreover, increased switch count further increases computational burden on the controller. Thus, the size, cost and complexity of classical MLIs increase at higher levels, making the overall inverter expensive and imposing limitations on practical implementation and market penetration [29]. The reliability and losses in the conventional MLIs can be improved by incorporating a Z-source network, popularly known as Z-source inverters (ZSI) [32], [33]. These ZSIs operate in single buckboost mode with fewer number of components and no dead time requirement [34], however, the size of Z-source network, possible EMI and limited modularity restricted their penetration in high-power applications.

Hence, researchers continued to explore and evolve newer topologies by making more or less changes to the classical MLIs. Thus emerged, asymmetrical CHB configuration to increase the number of levels with significant reduction in switch count [11] and other modified configurations to improve the performance of classical MLIs [19], [35]–[42]. However, control complexity, unequal device blocking voltages and limited switching redundancies of these configurations limited the fault tolerant ability, utilization of dc-sources, and even power distribution [29]. On the other hand, the increased component count of power semiconductor devices and capacitor/dc sources of classical MLI topologies has triggered the researchers to come up with newer topologies with reduced size and cost. Thus, MLI with reduced device count originated and this domain of MLIs has been called reduced switch count (RSC) MLIs [43]. From the past decade, various enthusiasts carried out extreme research on RSC-MLIs and developed numerous topologies with significant reduction in component count, total blocking voltage, cost and ease of control.

In recent years, several review papers on RSC-MLIs have been reported. In [44], RSC-MLIs are divided into unipolar and bipolar topologies and further classified into series, parallel and mixed connection of submodules. In this classification, only five different submodules are considered.

In [45], recently developed RSC-MLIs for renewable energy integration and drives application are discussed. However, the topologies are summarized based on three categories, i.e., symmetrical, asymmetrical, and modified. In [46], another classification of RSC-MLIs topologies is presented based on number of phases, presence of transformer, number of dc sources, and voltage ratio of dc sources. On the other hand, in the proposed paper the categorization is carried out by considering either the motivating factors behind the development of the topology or its key contributing features. Based on this, the topologies are classified as generalized, stacked, unit based, switched capacitor, transformer based, and three-phase topologies. In this context, the qualitative and quantitative features of topologies of RSC-MLI have been discussed in this paper. Also, a comparison has been made among all the reported topologies in-terms of their structural and operational features such as device count, device ratings, device blocking voltages, power distribution, redundant switching states, utilization of input dc-sources, modularity, fault tolerant ability and generalization to higher levels. This facilitates selection of a well-informed topology for any given application.

The structure of this paper is as follows. Section-II presents a detailed report on RSC-MLIs, starting from the various factors considered for developing an RSC-MLI and classification of RSC-MLIs topologies. Section-III presents detailed features of each reported RSC-MLI topology. Further, a comparison of reported topologies is given in Section-IV. Finally, future trends and conclusions of the paper are given in Section-V and VI.

# II. RSC-MLI: BACKGROUND

The objective of RSC-MLIs is to overcome the limitations of classical MLIs in terms of their size and complexity. However, the changes in their topological arrangement affect their structural and operational features such as device blocking voltages, switching redundancies, device ratings, utilization of dc-sources, charge balancing of dc-link capacitors, power distribution, modularity, generalization to higher levels, switching operation and fault tolerant ability.

# A. MOTIVATIONAL FACTORS

Researchers often consider one or more features mentioned below as a motivation factor behind developing a new RSC-MLI topology. The main features are listed as follows.

- **Device count:** To develop the topology with appreciable reduction in device (switches/diodes/capacitors/dc-sources) count.

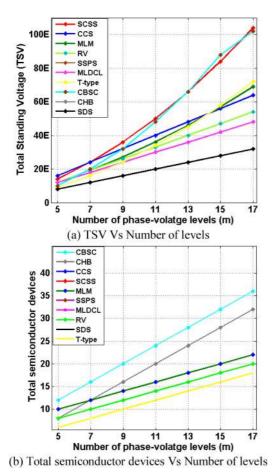

- **Device blocking voltages/ratings:** To develop the topology, involving identical device ratings and producing minimum device blocking voltages. For a topology, the total sum of the voltage blocking capability requirement for all its power switches is referred to as total standing voltage (TSV) or total voltage blocking capability of inverter [43].

- **Modularity:** Topologies with modular structure can easily be extended to higher levels.

- **Fault tolerant ability:** Fault tolerant ability enables the inverter to withstand abnormal working conditions such as faults on switching devices or dc sources, ensuring reliability with balanced operation.

- Even power distribution: Ability of the inverter to obtain required phase-voltage levels by distributing uniform power across all basic units/H-bridges. This feature contributes to charge balance among dc link voltages.

- **Requirement and Utilization of dc-sources:** Equal utilization of dc sources to contribute to natural balancing of dc-link voltages in closed loop applications. Reduction in the requirements of dc sources increased the role of capacitors and thus emerged self-balancing and voltage boosting topologies.

- Application area: As the features of RSC-MLI vary with topological arrangement, there exists no specific topology, which can be absolutely advantageous in any sort of application. Hence, a critical analysis is carried out among the newly developed topologies in finding out its best application in the areas such as FACTS, HVDC, CPD, BESS, ASD, IPQC, EV and consumer electronics.

# B. CLASSIFICATION

The interconnection of the switching devices, dc link voltages, diodes and other auxiliary components in a topology, can be arranged in any of the physical pattern such as ladder, staircase, column, U-shaped, cascade structure and even sometimes may not have any specific layout. Thus, considering the topological and operational features, developed RSC-MLIs can be classified as follows.

- *Modular topologies*: Topologies which can be extended to higher levels without affecting the device ratings are called modular configuration. Presence of modularity increases the ease in extending the topology to higher levels.

- *Unit based configurations*: Topology that can be scalable for any level in phase-voltage termed as generalized configuration. On the other hand, if the topology is designed for obtaining a fixed number of output voltage levels, then it is known as Unit based configuration.

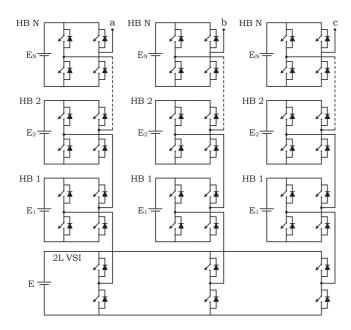

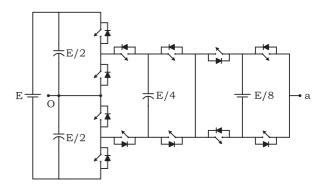

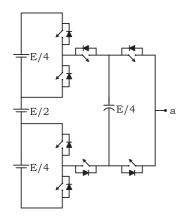

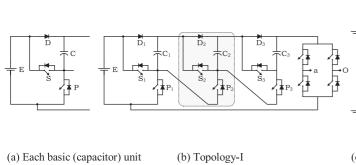

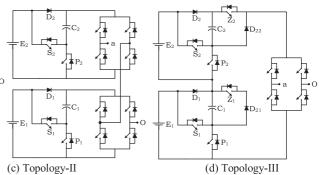

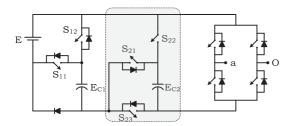

- *Half-bridge (chopper) cell-based topologies:* To preserve modularity, most of the RSC-MLI's incorporate a half-bridge cell as a basic building block. Chopper units producing a two-level voltage i.e., *E* or 0, are further connected in series, parallel, cascade as per the desired output voltage of RSC-MLI.

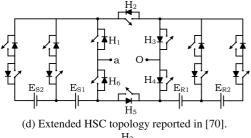

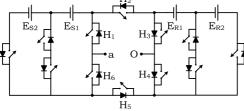

- *Topologies with H-bridge/HSC structure*: To avail the benefits of classical H-bridge, multiple topologies are reported by integrating H-bridge with multiple modular/non-modular units. On the other hand, to permit the topology produce output for multiple switching combinations, few topologies involve hexagon switched cell (HSC) structure.

- *Topologies with bi-directional switching devices*: Several RSC-MLI topologies have been reported with

bi-directional switching devices to clamp the midpoint of dc sources. A discrete semiconductor devices are incorporated to construct a switch with bi-directional voltage blocking and current conducting capability or a reverse blocking insulated gate bipolar transistor (RBIGBT) is used [47].

- Symmetrical/Asymmetrical topologies: Most often MLIs incorporate symmetrical sources (in terms of magnitude) in the input (dc-link), and can be called as symmetrical topologies. However to increase the number of levels without increasing the device count, asymmetrical topologies are preferred [11]. These topologies incorporate unequal ratio of sources in the input (dc-link), and attempts to produce output voltage for their possible additive and subtractive combinations. The dc-voltage ratios of sources can either be in geometric progression (GP) or arithmetic progression (AP), but to obtain effective reduction in device count, GP with common ratio of two (binary) or three (trinary) is preferred. Operation with trinary voltage ratios is feasible if the topology has the ability to facilitate output for all the additive and subtractive combinations of input dc voltages. The reduced device count of these configurations decreases the inverter size but increase the device blocking voltages/ratings, limits switching redundancies, restricts fault tolerant ability, limits capacitor voltage balancing and produces non-uniform power distribution among basic units.

- *Topologies with even power distribution*: Even power distribution is a feature of control aspect. This phenomenon is also referred as charge balance control or equal utilization of dc-sources. To achieve this, the topological switching operation is carried out in a way, that the average current consumed from each of the sources is equal, which makes the average powers equal. In other way, for a given topology, even power distribution or even load sharing is possible only, if all the input sources contribute equally towards the output voltage.

- *Topologies with equal blocking voltages*: Reduction in switch count of RSC-MLIs has modified their topological arrangement, which in turn modified the interconnection of switching devices and input dc-sources (or capacitors). This impacted the voltage rating/stress of the switching devices, such that they may encounter unequal blocking voltages. Thus, considering the device blocking voltages, RSC-MLI can be classified into topologies with even and uneven blocking voltages.

- *Topologies with fault tolerant ability*: Reliability of an inverter is ensured by its fault tolerant ability. Reduced device count of RSC-MLI's drastically restricted the switching redundancies, which provides an alternate path for the faulty switch and play a vital role in inverter reconfiguration. Thus, prominence of RSC-MLIs for industrial and domestic applications demands the topologies with fault tolerant ability.

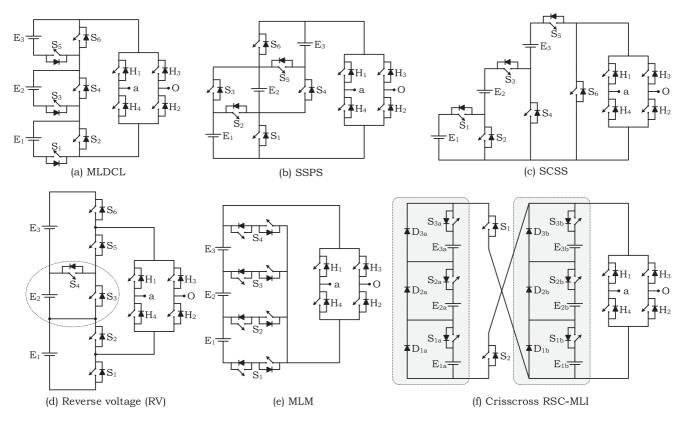

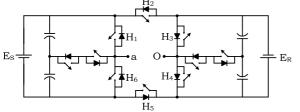

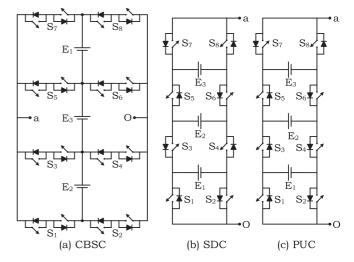

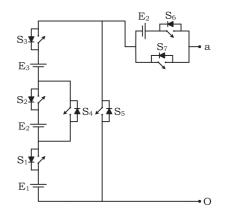

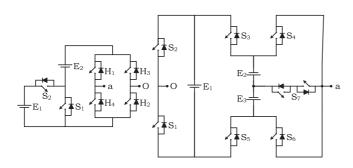

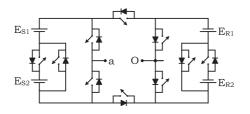

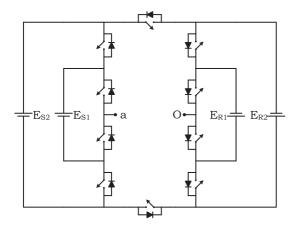

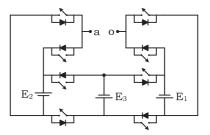

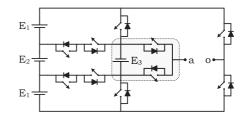

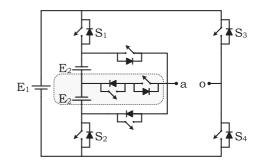

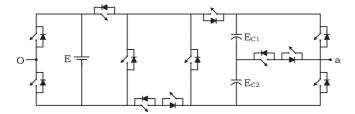

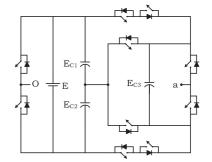

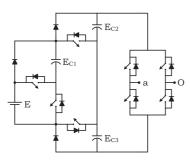

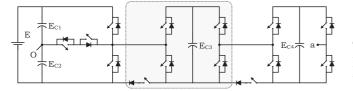

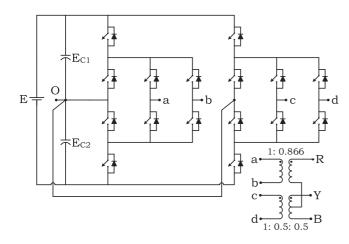

**FIGURE 1.** Topologies with separate level and polarity generators.

# C. CATEGORIES

Considering the above classification, the reported RSC-MLI topologies can be categorized as shown in Table 1. It is to be noted that, this categorization is carried out by considering either the motivating factors behind the development of the topology or its key contributing features.

# **III. RSC-MLI TOPOLOGIES AND FEATURES**

The physical structure, operational features, merits, limitations and suitable applications of these topologies shown in Table 1 are explained in this section.

# A. GENERALIZED RSC-MLI TOPOLOGIES

Considering the similarities in physical structure and type of the switching devices incorporated, the topologies listed under generalized RSC-MLI can further be classified as follows

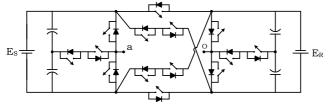

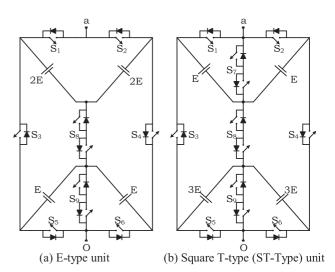

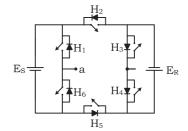

# 1) TOPOLOGIES WITH SEPARATE LEVEL AND POLARITY GENERATOR

Most of the RSC-MLI possess the topological arrangements that produce odd number of phase-voltage levels with separate polarity and level generators. Among these, the popular configurations are multilevel dc-link (MLDCL) [48], [49], switched series parallel sources (SSPS) [50], [51], reverse voltage (RV) [52], [53], series connected switched sources (SCSS) [54], [55], multilevel module (MLM) [56] and criss-cross (CC) [57]. Per-phase structures of these configurations

VOLUME 2, 2021

with three dc sources are shown in Fig. 1. The level generator in these structures consists of series connection of several basic units. Each basic unit consists of a half-bridge or choppercell with an isolated dc source. In case of MLM, the level generator consists of bidirectional switches. For MLDCL and SSPS topologies, the switches in the level generator operates with uniform voltage stress and equal device blocking voltages. In case of RV, SCSS and MLM the voltage stress increases with addition of new basic unit. However, in all these topologies, the blocking voltage of each device in polarity generator is equal to the total dc link voltage. All these topologies support both symmetrical and asymmetrical configurations except SCSS and MLM. However, their inability to synthesize output voltage for subtractive combination of dc-sources limits their asymmetric ability for trinary voltage ratios. The modular and redundant structure of MLDCL allows to tolerate multiple open-circuit (OC) faults on certain devices in level generator [141]. In [142], a modified MLDCL configuration is reported for grid integrated PV system by replacing by-pass switches in the level generator of MLDCL with diodes. Though, this modification reduced the device requirement, however, the main disadvantage for this solution is that it cannot inject reactive power into the grid.

In SSPS, the level generator cannot produce zero voltage and it is obtained from polarity generator. To obtain any positive or negative voltage level in SSPS shown in Fig. 1(b), only two devices in level generator are in conduction. With

#### **TABLE 1.** Categorization of RSC-MLI Topologies

| Generalized RSC-MLIs:         * With separate level and polarity generators         * Multilevel de-link (MLDCL) [48, 49]         * Switched series parallel sources (SSPS) [50, 51]         * Reverse voltage (RV) [52, 53]         * Series connected switched sources (SCSS) [54, 55]         * Multilevel module (MLM) [56]         * Crisscross switched (CCS) RSC-MLI [57]         * A trinary asymmetric topology [58]         * T-Type topologies         * T-Type topologies (Gr-69]         * Topology - II (bi-directional switch on one side of HSC) [67, 68]         * Topology - II (bi-directional switch on both side of HSC) [67, 68]         * Topology - II (bi-directional switch on both side of HSC) [67, 68]         * Topology - II (bi-directional switches inside HSC) [69]         * Extended HSC structures [70-72]         * Topologies with ladder-based structures         * Cascaded bi-polar switched cells (CBSC) [73]         * Switched d-sources (SDS) [74-76]         * Packed Ucoll (PUC) [43, 77]         Stacked configuration with level doubling network (LDN) [78-81]         * CHB with LDN [78-80] and T-type with LDN [81]         * Non-LDN based topologies [82-93]         * Hybrid ANPC [82, 87-90]         * Here [91, 92]         * T-type (ST-type) [98]         * Sumeterical unit-based topologies <t< th=""></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Multilevel dc-link (MLDCL) [48, 49]</li> <li>Switched series parallel sources (SSPS) [50, 51]</li> <li>Reverse voltage (RV) [52, 53]</li> <li>Series connected switched sources (SCSS) [54, 55]</li> <li>Multilevel module (MLM) [56]</li> <li>Crissercoss switched (CCS) RSC-MLI [57]</li> <li>A trinary asymmetric topology [58]</li> <li>T-Type topologies</li> <li>Topologies with Hexagon switched cell (HSC) structure</li> <li>Hybrid T-type topologies [67-69]</li> <li>Topology - I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology - I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology - I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology - I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology - I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology - I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology and the sources (70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched de-sources (SDS) [74-76]</li> <li>Switched de-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Saguare T-type (ST-type) [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Five-level topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-II [71, 102]</li></ul>                                                                                                                                                                         |

| <ul> <li>\$ Switched series parallel sources (SSPS) [50, 51]</li> <li>Reverse voltage (RV) [52, 53]</li> <li>\$ Series connected switched sources (SCSS) [54, 55]</li> <li>\$ Multilevel module (MLM) [56]</li> <li>Crisseross switched (CCS) RSC-MLI [57]</li> <li>\$ A trinary asymmetric topology [58]</li> <li><b>*</b> T-Type topologies</li> <li>* T-Type [59-63] and Cascaded T-type [64]</li> <li>\$ Half-leg T-type RSC-MLI [57, 65, 66]</li> <li>* Topology = Ni (bi-directional switch on one side of HSC) [67, 68]</li> <li>\$ Topology - II (bi-directional switch on one side of HSC) [67, 68]</li> <li>\$ Topology - II (bi-directional switch on one side of HSC) [67, 68]</li> <li>\$ Topology - II (bi-directional switch on both side of HSC) [67, 68]</li> <li>\$ Topology are tructures [70-72]</li> <li>* Topologies with ladder-based structures</li> <li>\$ Cascaded bi-polar switched cells (CBSC) [73]</li> <li>\$ Switched de-sources (SDS) [74-76]</li> <li>\$ Packed U-cell (PUC) [43, 77]</li> <li>* Stacked configuration with level doubling network (LDN) [78-81]</li> <li>\$ CHB with LDN [78-80] and T-type with LDN [81]</li> <li>* Non-LDN based topologies [82-93]</li> <li>* Hybrid ANPC [82, 87-90]</li> <li>* HFC [91, 92]</li> <li>* T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>* Symmetrical unit-based topologies</li> <li>* Five-level topology [95]</li> <li>* Nine-level topology [95]</li> <li>* Asymmetrical unit-based topologies</li> <li>* Envelope (E-type) type [97]</li> <li>* Square T-type (ST-type) [98]</li> <li>* Compact module multilevel inverter [99]</li> <li>* HSC unit [100]</li> <li>* Extended HSC units</li> <li>* Topology-11 [104]</li> <li>* Witched capacitor (SC) RSC-MLIs:</li> <li>* Series/parallel based SC unit topologies</li> <li>* Topology-11 [104]</li> <li>* Witched capacitor (SC) RSC-MLIs:</li> <li>* Series/parallel based SC unit 1005]</li></ul>                                                                                                                                                      |

| <ul> <li>Reverse voltage (RV) [52, 53]</li> <li>Series connected switched sources (SCS) [54, 55]</li> <li>Multilevel module (MLM) [56]</li> <li>Crisscross switched (CCS) RSC-MLI [57]</li> <li>A trinary asymmetric topology [58]</li> <li>T-Type topologies</li> <li>T-type [59-63] and Cascaded T-type [64]</li> <li>Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>Topologies with Hexagon switched cell (HSC) structure</li> <li>Hybrid T-type topologies [67-69]</li> <li>Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked topologies: Stacked topologies [82-93] <ul> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based tupology [95] <ul> <li>Nine-LoN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based tupology [95] <ul> <li>Nine-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Square T-type (ST-type) [98]</li> </ul> Compact module multilevel inverter [99] Setices/parallel based SC unit topologies <ul> <li>Topology-II [101]</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLLs: <ul> <li>Series/parallel based SC unit 1[05]</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) CNSC-MLLs: <ul> <li>Switched capacitor (SC) CNSC-MLLs:</li> <li>Series/parallel based SC unit 1[06]</li> <li>HSC (full bridge ccll) with inher</li></ul>                                                         |

| <ul> <li>Series connected switched sources (SCSS) [54, 55]</li> <li>Multilevel module (MLM) [56]</li> <li>Crisscross switched (CCS) RSC-MLI [57]</li> <li>A trinary asymmetric topology [58]</li> <li>T-Type topologies</li> <li>T-type [59-63] and Cascaded T-type [64]</li> <li>Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched de-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLLs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> </ul> Compact module multilevel inverter [99] HSC unit [100] Extended HSC units <ul> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLLs: <ul> <li>Series/parallel based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li></ul>                                                 |

| <ul> <li>Crisscross switched (CCS) RSC-MLI [57]</li> <li>A trinary asymmetric topology [58]</li> <li>T-Type topologies</li> <li>T-Type (59-63] and Cascaded T-type [64]</li> <li>Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>Topologies with Hexagon switched cell (HSC) structure</li> <li>Hybrid T-type topologies [67-69]</li> <li>Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switches inside HSC) [69]</li> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched de-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93] Unit-based MLLS: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> </ul> Asymmetrical unit-based topologies <ul> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-II [101]</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit (106]</li> <li>Fibe (rulp topologies [103, 104]</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit (106]</li> <li>FBC (tull bridge cell) with inherent SC unit</li> <li>Seviex/earallel based SC unit (106]</li> <li>FBC (tull bridge cell) with inherent SC unit</li> <li>Seviex/earallel based SC unit (106]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li></ul></li></ul>                                 |

| <ul> <li>A trinary asymmetric topology [58]</li> <li>T-Type topologies</li> <li>T-Type topologies</li> <li>T-type [59-63] and Cascaded T-type [64]</li> <li>Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>Topologies with Hexagon switched cell (HSC) structure</li> <li>Hybrid T-type topologies [67-69]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked topologies: <ul> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> </ul> Non-LDN based topologies [82-93] <ul> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLLs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Ninc-level topology [95]</li> <li>Knine-level topology [95]</li> <li>Knine-level topology [97]</li> <li>Square T-type (ST-type) [98]</li> </ul> Compact module multilevel inverter [99] HSC unit [100] Extended HSC units <ul> <li>Topology-1 [101]</li> <li>Topology-1 [103]</li> <li>Topology-11 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit (106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Series/parallel based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Series/parallel based SC unit [106]</li> <li>Stuched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Sout</li></ul>                                                  |

| <ul> <li>T-Type topologies</li> <li>T-type [59-63] and Cascaded T-type [64]</li> <li>Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>Topologies with Hexagon switched cell (HSC) structure</li> <li>Hybrid T-type topologies [67-69]</li> <li>Topology – I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – III (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched de-sources (SDS) [74-76]</li> <li>Packed topologies:</li> <li>Stacked topologies:</li> <li>Stacked topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLLs:</li> <li>Sommetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Signar T-type (97)</li> <li>Square T-type (97)</li> <li>Square T-type (97)</li> <li>Square T-type (103)</li> <li>Topology-II [101]</li> <li>Topology-II [103]</li> <li>Topology-II [103]</li> <li>Topology-II [103]</li> <li>Somology-II [104]</li> <li>Swintehical SC unit topologies [103, 104]</li> <li>Topology-II (104]</li> <li>Swintehical CCC) [103]</li> <li>Topology-II [104]</li> <li>Swintehical CCC) [104]</li> <li>Swintehical CCC) [105]</li> <li>Swintehical CCC) [106]</li> <li>Swintehical CCC) [107]</li> <li>Se Seice/arallel based SC unit topologies</li> <li>Topology-II [104]</li> <li>Swintehical CCC) [106]</li> <li>Swintehical CCC) [107]</li> <li>Source Cology [109]</li> <li>Swintehical CCC) [107]</li> <li>Topology-II [103]</li> <li>Topology-II [104]</li> <li>Swintehical CCC) (202 (201) [105]</li> <li>Source Cologies [105, 106]</li> <li>Source Cologies [105, 106]</li> <li>Source Cologies [105, 106]</li> <li>Source Cologies [105, 106]</li> <li>Source Cologies [106]</li> <li>Switched Capacitor Cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched Ca</li></ul> |

| <ul> <li>Titype [59-63] and Cascaded T-type [64]</li> <li>Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>Topologies with Hexagon switched cell (HSC) structure</li> <li>Hybrid T-type topologies [67-69]</li> <li>Topology – I (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched d-Sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLIs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC units</li> <li>Topology-II [101]</li> <li>Topology-II [104]</li> </ul> Switched d-SC with topologies [103, 104] <ul> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLLIs: <ul> <li>Seven-level SC inpler plus doubler topologies</li> <li>Topology-II [104]</li> </ul> Switched capacitor cell (SC) with half-bridge cells (HBC)[110, 111] Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111] Wodified HSC based switched capacitor topology [104] Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111] Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111] Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111] Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111] Switched capacitor cell (SCC) wit                                                                                                  |

| <ul> <li>* Half-leg T-type RSC-MLI [59, 65, 66]</li> <li>* Topologies with Hexagon switched cell (HSC) structure</li> <li>* Hybrid T-type topologies [67-69]</li> <li>* Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>* Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>* Topology – II (bi-directional switches inside HSC) [69]</li> <li>* Extended HSC structures [70-72]</li> <li>* Topologies with ladder-based structures</li> <li>* Cascaded bi-polar switched cells (CBSC) [73]</li> <li>* Switched dc-sources (SDS) [74-76]</li> <li>* Packed U-cell (PUC) [43, 77]</li> </ul> Stacked topologies: <ul> <li>* Stacked configuration with level doubling network (LDN) [78-81]</li> <li>* CHB with LDN [78-80] and T-type with LDN [81]</li> <li>* Non-LDN based topologies [82-93]</li> <li>* Hybrid ANPC [82, 87-90]</li> <li>* HFC [91, 92]</li> <li>* T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLIs: <ul> <li>* Basic unit topology [94]</li> <li>* Symmetrical unit-based topologies</li> <li>* Five-level topology [95]</li> <li>* Nine-level topology [96]</li> <li>* Asymmetrical unit-based topologies</li> <li>* Envelope (E-type) type [97]</li> <li>* Square T-type (ST-type) [98]</li> <li>* Compact module multilevel inverter [99]</li> <li>* HSC unit [100]</li> <li>* Extended HSC units</li> <li>* Topology-II [101]</li> <li>* Topology-II [103]</li> <li>* Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLLIs: <ul> <li>* Series/parallel based SC unit [106]</li> <li>* Topology-II: Modified SC unit [106]</li> <li>* FBC (full bridge cell) with inherent SC unit</li> <li>* Series/parallel based SC unit [106]</li> <li>* Stricked capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>* Scologies [112, 113]</li> <li>* Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                               |

| <ul> <li>Hybrid T-type topologies [67-69]</li> <li>Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switches inside HSC) [69]</li> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLIs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> </ul> Asymmetrical unit-based topologies <ul> <li>Envelope (E-type) [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-II [71, 102]</li> <li>Asymmetrical T-type topologies [103, 104]</li> <li>Topology-II [71, 102]</li> <li>Asymmetrical based SC unit [106]</li> <li>Series/parallel based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [107, 108]</li> <li>Topology-II [104]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>Topology – I (bi-directional switch on one side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – II (bi-directional switches inside HSC) [69]</li> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked topologies: <ul> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLIs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>TopologyI [28]</li> <li>TopologyII [71, 102]</li> <li>Asymmetrical T-type topologies [103, 104]</li> <li>TopologyII [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>TopologyII [71, 102]</li> <li>Asymmetrical SC unit [106]</li> <li>FEC (full bridge cell) with inherent SC unit</li> <li>Series/parallel based SC unit [106]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>Series/parallel based SC unit [106]</li> <li>Switched capacitor (SC) CN CW inhalf-bridge cells (HBC)[110, 111]</li> <li>Sc doubler topologies [112, 113]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>Topology – II (bi-directional switch on both side of HSC) [67, 68]</li> <li>Topology – III (bi-directional switches inside HSC) [69]</li> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [101]</li> <li>Topology-1 [103]</li> <li>Topology-1 [103]</li> <li>Topology-1 [104]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>Series/parallel based SC unit [105]</li> <li>Topology-11 Modified SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [109]</li> <li>Switched capacitor (SC) With half-bridge cells (HBC)[110, 111]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [104]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>Topology – III (bi-directional switches inside HSC) [69]</li> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLIs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [101]</li> <li>Topology-1 [101]</li> <li>Topology-1 [103]</li> <li>Topology-1 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>Topology-11 [04]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Seven-level SC tripler plus doublet topologies</li> <li>Topology-11 [05]</li> <li>Topology-11 [06]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doublet topology [109]</li> <li>Switched capacitor (SC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [104]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>Extended HSC structures [70-72]</li> <li>Topologies with ladder-based structures</li> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>Packed U-cell (PUC) [43, 77]</li> </ul> Stacked configuration with level doubling network (LDN) [78-81] <ul> <li>ChB with LDN [78-80] and T-type with LDN [81]</li> </ul> Non-LDN based topologies [82-93] <ul> <li>Hybrid ANPC [82, 87-90]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> </ul> Unit-based MLIs: <ul> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> </ul> Asymmetrical unit-based topologies <ul> <li>Five-level topology [96]</li> </ul> Asymmetrical unit-based topologies <ul> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> </ul> Compact module multilevel inverter [99] HSC unit [100] Extended HSC units <ul> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [103]</li> <li>Topology-II [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>Topology-I: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [107, 108]</li> <li>Topology-I: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [107, 108]</li> <li>Witched capacitor cell (SCC) with half-bridge cells (HBC)[110</li></ul>                                                                                     |

| <ul> <li>Cascaded bi-polar switched cells (CBSC) [73]</li> <li>Switched dc-sources (SDS) [74-76]</li> <li>Packed U-cell (PUC) [43, 77]</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [95]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [101]</li> <li>Topology-1 [103]</li> <li>Topology-1 [103]</li> <li>Topology-1 II (04]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>Series/parallel based SC unit [105]</li> <li>Topology-1: Basic SC unit [105]</li> <li>Topology-1: Modified SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [104]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>\$ Switched dc-sources (SDS) [74-76]</li> <li>* Packed U-cell (PUC) [43, 77]</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>\$ Stacked configuration with level doubling network (LDN) [78-81]</li> <li>* CHB with LDN [78-80] and T-type with LDN [81]</li> <li>* Non-LDN based topologies [82-93]</li> <li>* Hybrid ANPC [82, 87-90]</li> <li>* Hybrid ANPC [82, 87-90]</li> <li>* T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>* Basic unit topology [94]</li> <li>\$ Symmetrical unit-based topologies</li> <li>* Five-level topology [95]</li> <li>* Nine-level topology [96]</li> <li>* Asymmetrical unit-based topologies</li> <li>* Envelope (E-type) type [97]</li> <li>* Square T-type (ST-type) [98]</li> <li>* Compact module multilevel inverter [99]</li> <li>* HSC unit [100]</li> <li>* Extended HSC units</li> <li>* Topology-1 [101]</li> <li>* Topology-1 [101]</li> <li>* Topology-1 [103]</li> <li>* Topology-1 [103]</li> <li>* Topology-1 [104]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>* Series/parallel based SC unit [106]</li> <li>* FBC (full bridge cell) with inherent SC unit</li> <li>* Seven-level SC tripler plus doubler topology [109]</li> <li>* Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>* Stoubler topologies [112, 113]</li> <li>* Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>Packed U-cell (PUC) [43, 77]</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-11 [101]</li> <li>Topology-11 [101]</li> <li>Topology-11 [104]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>Series/parallel based SC unit [105]</li> <li>Topology-1: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [109]</li> <li>Switched capacitor (SC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Stacked topologies:</li> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-II [28]</li> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [103]</li> <li>Topology-1 [103]</li> <li>Topology-1 [103]</li> <li>Topology-11 [104]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>Series/paralle based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripter topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>Stacked configuration with level doubling network (LDN) [78-81]</li> <li>CHB with LDN [78-80] and T-type with LDN [81]</li> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-I [28]</li> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-I [103]</li> <li>Topology-1 [103]</li> <li>Topology-1 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Non-LDN based topologies [82-93]</li> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [101]</li> <li>Topology-1II [71, 102]</li> <li>Asymmetrical T-type topologies [103, 104]</li> <li>Topology-1I [103]</li> <li>Topology-1I [104]</li> <li>Switched capacitor (SC) RSC-MLIs:</li> <li>Series/parallel based SC unit [105]</li> <li>Topology-1: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched thSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>Hybrid ANPC [82, 87-90]</li> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [28]</li> <li>Topology-1 [101]</li> <li>Topology-1 [101]</li> <li>Topology-1 [103]</li> <li>Topology-11 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>* Topology-1: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [107, 108]</li> <li>* 13-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>St doubler topologies [12, 113]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>HFC [91, 92]</li> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based MLIs:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-II [28]</li> <li>Topology-II [28]</li> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [103]</li> <li>Topology-1 [103]</li> <li>Topology-11 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/paralle based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched topologies [112, 113]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>T-type with cross connected modules (CCM) [93]</li> <li>Unit-based ML1s:</li> <li>Basic unit topology [94]</li> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [101]</li> <li>Topology-1 [101]</li> <li>Topology-1 [103]</li> <li>Topology-1 [104]</li> </ul> Switched capacitor (SC) RSC-ML1s: <ul> <li>Series/parallel based SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Unit-based MLIs:<br>* Basic unit topology [94]<br>* Symmetrical unit-based topologies<br>* Five-level topology [95]<br>* Nine-level topology [96]<br>* Asymmetrical unit-based topologies<br>* Envelope (E-type) type [97]<br>* Square T-type (ST-type) [98]<br>* Compact module multilevel inverter [99]<br>* HSC unit [100]<br>* Extended HSC units<br>* Topology-I [28]<br>* Topology-I [101]<br>* Topology-II [101]<br>* Topology-III [71, 102]<br>* Asymmetrical T-type topologies [103, 104]<br>* Topology-II [103]<br>* Topology-II [104]<br>Switched capacitor (SC) RSC-MLIs:<br>* Series/parallel based SC unit topologies<br>* Topology-I: Basic SC unit [105]<br>* Topology-I: Basic SC unit [106]<br>* FBC (full bridge cell) with inherent SC unit<br>* Seven-level SC tripler plus doubler topology [109]<br>* Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]<br>* SC doubler topologies [112, 113]<br>* Modified HSC based switched capacitor topology [114]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>Symmetrical unit-based topologies</li> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [28]</li> <li>Topology-11 [101]</li> <li>Topology-11 [101]</li> <li>Topology-11 [103]</li> <li>Topology-1 [103]</li> <li>Topology-11 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>Topology-1: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [107, 108]</li> <li>13-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>St Coubler topologies [112, 113]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>Five-level topology [95]</li> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-II [28]</li> <li>Topology-II [28]</li> <li>Topology-II [101]</li> <li>Topology-II [101]</li> <li>Topology-II [103]</li> <li>Topology-1 [103]</li> <li>Topology-11 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>Topology-1: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>SC doubler topologies [112, 113]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

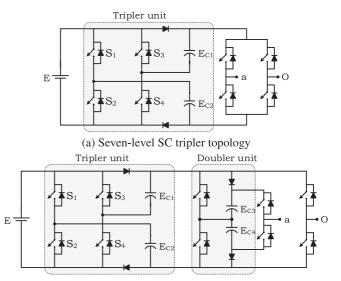

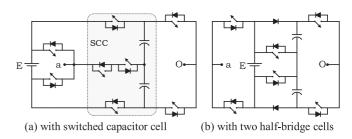

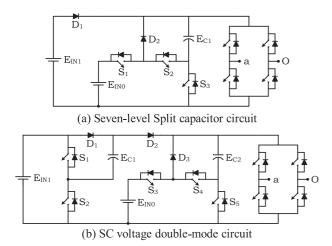

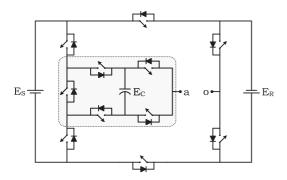

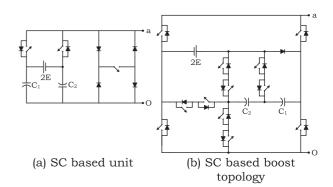

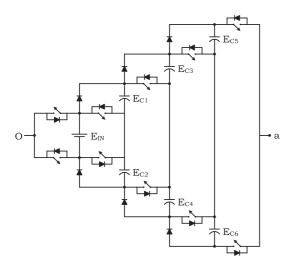

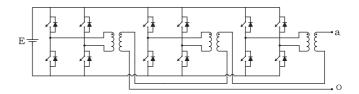

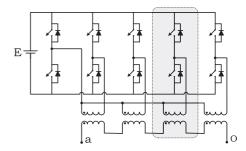

| <ul> <li>Nine-level topology [96]</li> <li>Asymmetrical unit-based topologies</li> <li>Envelope (E-type) type [97]</li> <li>Square T-type (ST-type) [98]</li> <li>Compact module multilevel inverter [99]</li> <li>HSC unit [100]</li> <li>Extended HSC units</li> <li>Topology-1 [28]</li> <li>Topology-1 [101]</li> <li>Topology-III [101]</li> <li>Topology-III [101]</li> <li>Topology-III [103]</li> <li>Topology-1 [103]</li> <li>Topology-1 [104]</li> </ul> Switched capacitor (SC) RSC-MLIs: <ul> <li>Series/parallel based SC unit topologies</li> <li>Topology-1: Basic SC unit [105]</li> <li>Topology-1: Basic SC unit [106]</li> <li>FBC (full bridge cell) with inherent SC unit</li> <li>Seven-level SC tripler topology [107, 108]</li> <li>13-level SC tripler plus doubler topology [109]</li> <li>Switched capacitor cell (SCC) with half-bridge cells (HBC)[110, 111]</li> <li>SC doubler topologies [112, 113]</li> <li>Modified HSC based switched capacitor topology [114]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |