# UC Berkeley UC Berkeley Electronic Theses and Dissertations

## Title

A System-level Approach to Fault and Variation Resilience in Multi-core Die

**Permalink** https://escholarship.org/uc/item/0nd0b98v

**Author** Markovskiy, Yury

Publication Date 2009

Peer reviewed|Thesis/dissertation

# A System-level Approach to Fault and Variation Resilience in Multi-core Die

by

Yury Markovskiy

B.S. (University of California, Berkeley) 2000 M.S. (University of California, Berkeley) 2004

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in Charge:

Professor John Wawrzynek, Chair Professor Jan M. Rabaey Professor Paul K. Wright

Fall 2009

A System-level Approach to Fault and Variation Resilience in Multi-core Die

Copyright © 2009

$\mathbf{b}\mathbf{y}$

Yury Markovskiy

## Abstract

A System-level Approach to Fault and Variation Resilience in Multi-core Die

Yury Markovskiy Doctor of Philosophy in Computer Science University of California, Berkeley Professor John Wawrzynek, Chair

With shrinking transistors and growth in parametric variability, statically managing die yield is no longer possible. Design for Manufacturing (DFM) techniques use increasingly bigger guard-bands that waste area, power, and performance, impeding Moore's Law of semiconductor device scaling. Process Voltage Temperature (PVT) variations can turn a nominally homogeneous many-core die into a set of cores with heterogeneous performance.

Network-on-Chip provides an effective and scalable way to integrate hundreds of heterogeneous cores without forcing each to give up its own PVT-induced operating point for the chip-wide common worst case. As with asynchronous logic, a NoC of regular, redundant, many-CLK/ $V_{DD}$  cores can deliver the average rather than the worst case system performance with greater power efficiency and fault tolerance than its globally synchronous monolithic counterparts [41, 92]. This work shows that the Voltage-Frequency Island (VFI) architectures are also the key to tolerating and compensating for PVT variations.

The VFI advantages cannot be realized without run-time task-to-core mapping and adaptive network routing that optimally match application resource requirements with heterogeneous cores and communication fabric. These systematic techniques are more effective at mitigating a variety of faults and variations than layout and circuit DFM. Most importantly, the gains from these techniques can be translated into die yield improvements and smaller DFM guard-bands.

This work investigates core sparing and network routing. The developed models demonstrate that core sparing reduces the die cost asymptotically from  $O(A^3)$ to  $O(A^{\frac{1}{2}})$ , and it is more cost efficient than larger design guard-bands of layout and circuit redundancy. The analysis outcome favors a greater number of smaller unreliable cores as opposed to a fewer larger reliable cores given a fixed die area. This points to the limitations and ultimately the futility of DFM techniques in the future semiconductor process generations.

Adaptive network routing enables core sparing. More critically, it simultaneously combats the two sources of network load imbalance: on-die performance heterogeneity from PVT variations and application communication topology. With stochastic PVT variations, the developed Minimal Adaptive Total Congestion (MATC) router increases the expected network saturation bandwidth by 7–23% and reduces its variance by 2–10x as compared to the Dimension Order router. With systematic PVT variations, the improvements are 5–35%. These gains of the adaptive router can compensate for degradation due to performance variations and can thus be used to reduce design guard-bands. By treating cores as units of fault and variation tolerance, these systematic techniques provide a simple and consistent way to deal with static and dynamic performance variations and faults. These techniques are more effective than isolated DFM solutions. Rather than fighting and minimizing the on-die parametric variations, our approach takes advantage of the platform heterogeneity and manages its net system performance impact.

> Professor John Wawrzynek Dissertation Committee Chair

# Contents

| $\mathbf{A}$ | bstra | $\operatorname{ct}$                            | 1   |

|--------------|-------|------------------------------------------------|-----|

| Li           | st of | Figures                                        | iv  |

| Li           | st of | Tables                                         | vii |

| A            | cknov | wledgments                                     | ix  |

| 1            | Intr  | oduction                                       | 1   |

|              | 1.1   | Moore's Law: a blessing and a curse            | 3   |

|              |       | 1.1.1 End to Moore's Law scaling?              | 3   |

|              |       | 1.1.2 Minimizing Variations                    | 6   |

|              | 1.2   | Our Novel Approach                             | 10  |

|              | 1.3   | Multi-core and Reliability                     | 14  |

|              | 1.4   | Research Contributions                         | 20  |

|              | 1.5   | Related Works                                  | 22  |

|              | 1.6   | Dissertation Organization                      | 32  |

| <b>2</b>     | Perf  | formance Variations                            | 35  |

|              | 2.1   | Sources and Trends                             | 37  |

|              |       | 2.1.1 PVT Variation Sources                    | 37  |

|              |       | 2.1.2 Minimizing Variations                    | 45  |

|              |       | 2.1.3 Problems with Current Approaches         | 48  |

|              | 2.2   | Variation Modeling                             | 50  |

|              |       | 2.2.1 FMAX Model and Simulation Infrastructure | 50  |

|              |       | 2.2.2 Variations and Multi-core                | 64  |

|              | 2.3   | Summary                                        | 67  |

|              |       |                                                |     |

| 3        | Mu  | lti-core Architecture for Heterogeneous Performance | 69  |

|----------|-----|-----------------------------------------------------|-----|

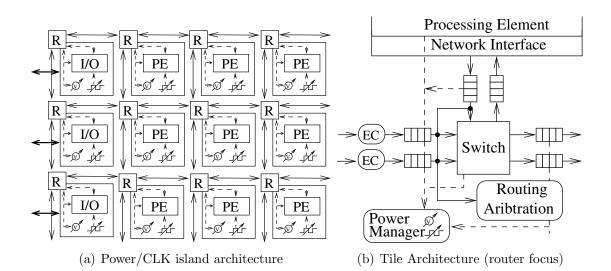

|          | 3.1 | Compute and Router tile                             | 70  |

|          | 3.2 | Communication Fabric                                | 82  |

|          |     | 3.2.1 Motivation for NoC                            | 82  |

|          |     | 3.2.2 NoC Organization                              | 85  |

|          | 3.3 | Summary                                             | 98  |

| <b>4</b> | Spa | ring: Redundancy and Multicore                      | 100 |

|          | 4.1 | Resource Redundancy                                 | 101 |

|          | 4.2 | Traditional Chip Cost Model                         | 107 |

|          | 4.3 | Sparing Defective Cores                             | 111 |

|          | 4.4 | Yield and Over-engineering                          | 116 |

|          | 4.5 |                                                     | 121 |

|          | 4.6 | Model Comparison                                    | 124 |

|          | 4.7 |                                                     | 127 |

| <b>5</b> | Net | work-on-Chip Simulation Infrastructure              | 129 |

|          | 5.1 | Simulation Infrastructure                           | 130 |

|          |     | 5.1.1 Discrete Event Simulator                      | 133 |

|          |     | 5.1.2 Implementation of Key Actors                  | 136 |

|          | 5.2 | NoC Router Micro-architecture                       | 145 |

|          |     | 5.2.1 Router-specific Actors                        | 145 |

|          |     | 5.2.2 Router Implementation                         | 152 |

|          |     | 5.2.3 Router Performance Annotation                 | 155 |

|          | 5.3 | Flit Source and Traffic Generators                  | 157 |

|          | 5.4 | Task to core mapping                                | 162 |

|          | 5.5 | Summary                                             | 163 |

| 6        | Ada | aptive Routing Algorithms                           | 165 |

|          | 6.1 |                                                     | 166 |

|          |     | -                                                   | 168 |

|          |     |                                                     | 169 |

|          |     | 6.1.3 Flow Control Bound                            | 170 |

|          | 6.2 | Communication Patterns                              | 171 |

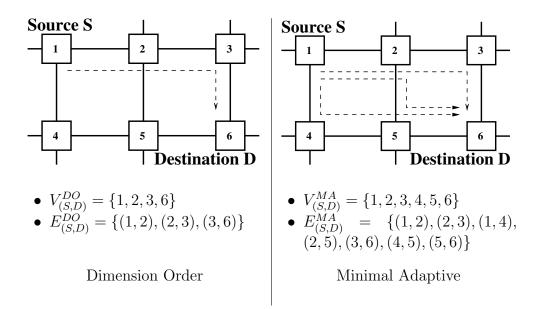

|          | 6.3 | Routing Algorithms                                  | 173 |

|          |     | 6.3.1 Dimension Order Routing                       | 176 |

|          |     | 6.3.2 Minimal Adaptive Routing                      | 177 |

|          |     | 6.3.3 The Minimal West First Routing                | 184 |

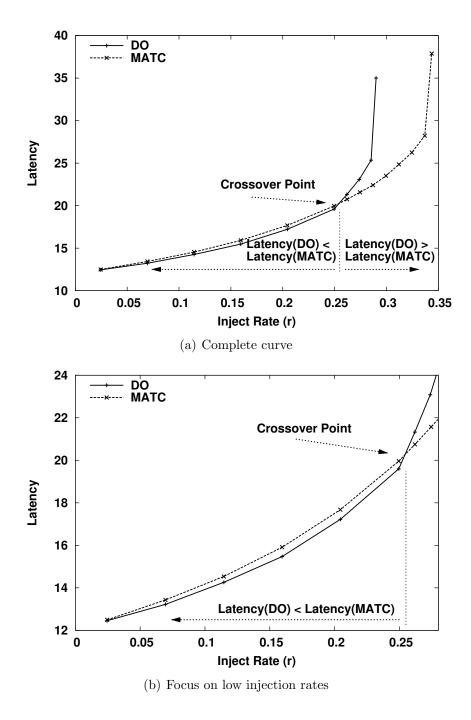

|          |     | 6.3.4 Latency                                       | 188 |

|          | 6.4 | Summary                                             | 192 |

|          |     |                                                     |     |

| <b>7</b>     | Ada   | ptive Routing and PVT Variations                | 194        |

|--------------|-------|-------------------------------------------------|------------|

|              | 7.1   | PVT Variation Bound                             | 195        |

|              | 7.2   | Impact of PVT Variations                        | 199        |

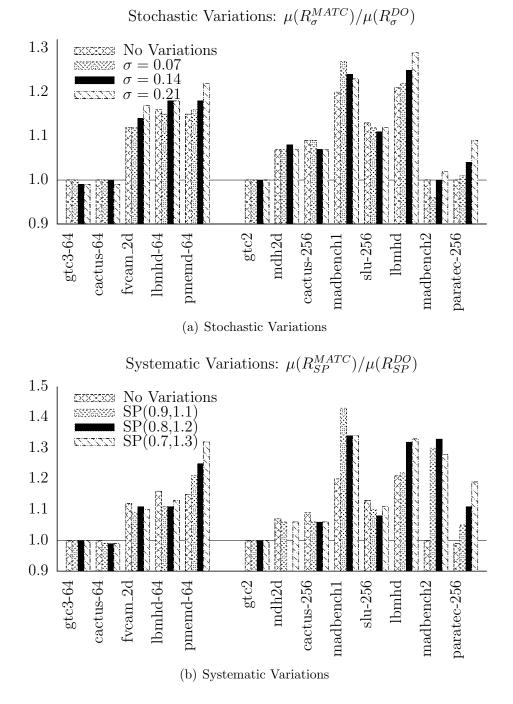

|              |       | 7.2.1 Stochastic Variations                     | 201        |

|              |       | 7.2.2 Systematic Variations                     | 215        |

|              |       | 7.2.3 Stochastic and Systematic Results Summary | 222        |

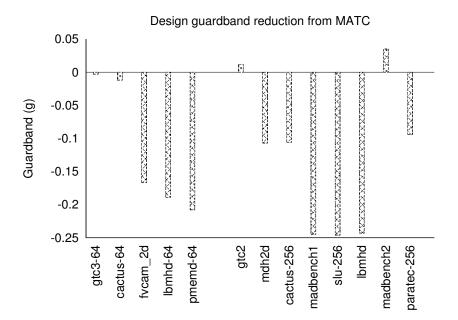

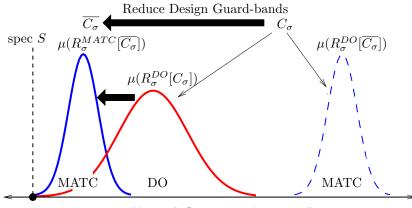

|              | 7.3   | Reducing Design Guard-bands                     | 225        |

|              | 7.4   | Benefits of Heterogeneous Architectures         | 231        |

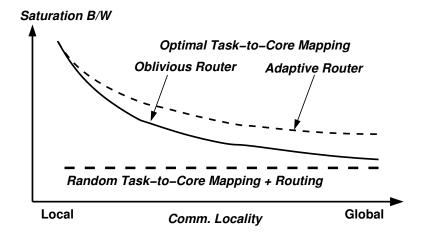

|              | 7.5   | Task-to-Core Mapping Impact                     | 235        |

|              | 7.6   | Summary                                         | 241        |

| 8            | Net   | work Performance Analysis                       | <b>244</b> |

|              | 8.1   | Topology Bounds                                 | 245        |

|              | 8.2   | Router Bounds                                   | 255        |

|              | 8.3   | Summary                                         | 265        |

| 9            | Cor   | aclusion                                        | 266        |

| 10           | Fut   | ure Directions                                  | 274        |

|              | 10.1  | Refining Die Yield Models                       | 274        |

|              | 10.2  | Task-to-Core Mapping                            | 276        |

|              | 10.3  | Using Architecture Knobs                        | 278        |

| Bi           | bliog | graphy                                          | 279        |

| $\mathbf{A}$ | ppe   | ndices                                          | 293        |

| $\mathbf{A}$ | Ada   | ptive Routing and PVT Variations                | 294        |

# List of Figures

| 1.1   | Ideal Moore's Law $vs$ the actual and projected scaling [19]                   | 5  |  |

|-------|--------------------------------------------------------------------------------|----|--|

| 1.2   | Ideal Moore's Law vs the actual $T_{ox}$ , $V_{dd}$ , and $V_t$ scaling [55] 5 |    |  |

| 1.3   | Variations and scaling effect on transistor and gate performance [39].         |    |  |

| 1.4   | Decreasing device sizes result in parametric variations that degrade           |    |  |

| max   | imum circuit operating frequency FMAX [22]                                     | 7  |  |

| 1.5   | PVT variations impact performance distribution on the current                  |    |  |

| state | e of the art VLSI                                                              | 11 |  |

| 1.6   | The impact of PVT variations is reduced with multi-level tech-                 |    |  |

| niqu  | es and translated in smaller design guardbands                                 | 12 |  |

| 1.7   | An illustration of core performance ranges controlled by DVS/DFS.              | 15 |  |

| 2.1   | A die performance profile comprises stocastic and systematic pro-              |    |  |

| cess  | effects and a dynamic gradient                                                 | 39 |  |

| 2.2   | The relationship between process, voltage and temperature varia-               |    |  |

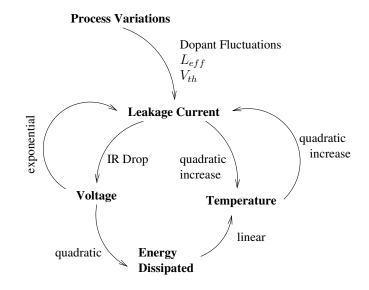

| tions | s and their impact on circuit performance                                      | 43 |  |

| 2.3   | Real gate delay exhibits some spatial correlation [22]                         | 55 |  |

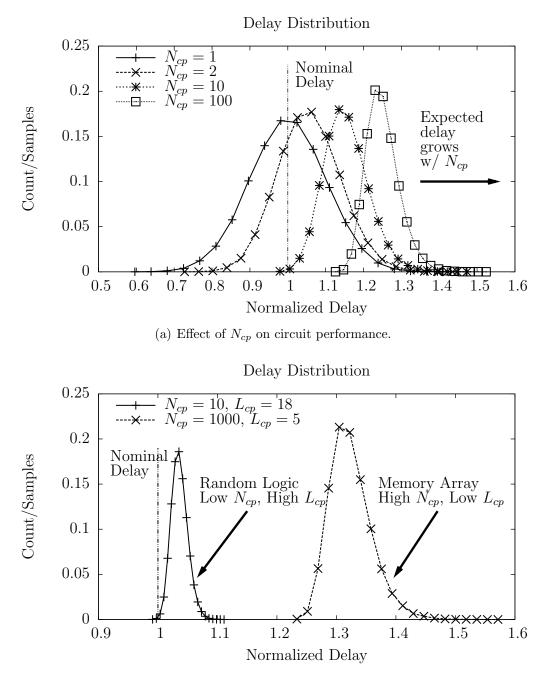

| 2.4   | Impact of $L_{cp}$ and $N_{cp}$ on circuit performance distribution            | 57 |  |

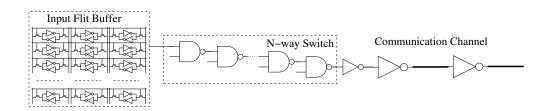

| 2.5   | Simple first order router model                                                | 59 |  |

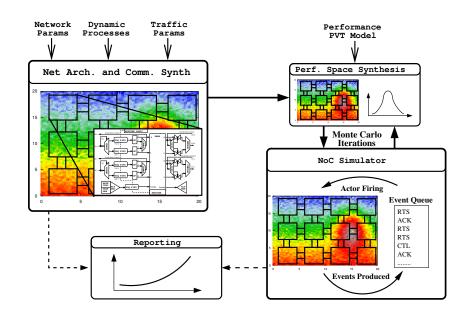

| 2.6   | NoC simulation framework forms a part of variation-aware archi-                |    |  |

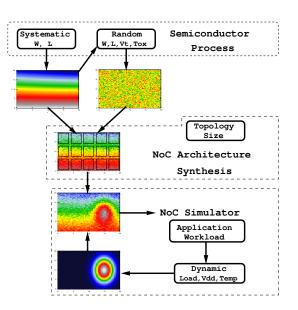

| tecti | re exploration environment.                                                    | 62 |  |

| 2.7   | A sampling of operating regions for different types of on-die tiles.           | 66 |  |

| 3.1   | A multicore tiled architecture envisioned in this work                         | 71 |  |

| 3.2   | A sampling of operating regions for different types of on-die tiles.           | 80 |  |

| 3.3   | Routing algorithm determines average packet latency and satura-                |    |  |

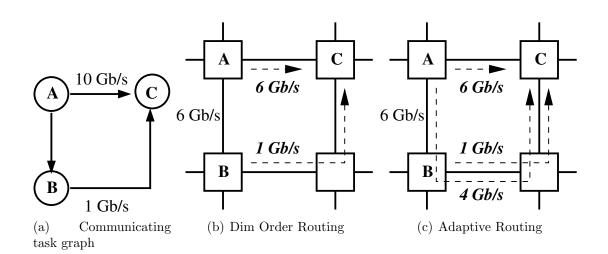

| tion  | bandwidth of the network.                                                      | 87 |  |

| 3.4   | Deadlock and livelock impede forward communication progress                    | 88 |  |

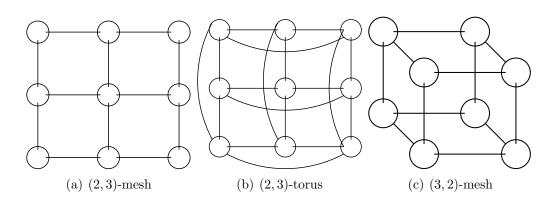

| 3.5   | Examples of mesh and torus network topologies                                  | 90 |  |

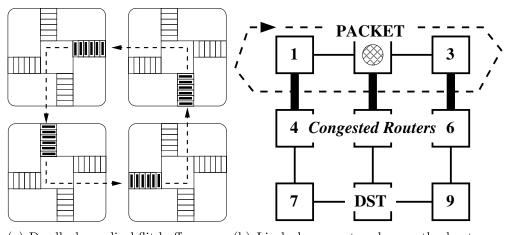

| 3.6          | Head-of-Queue blocking                                                                                                                                                                        | 96         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

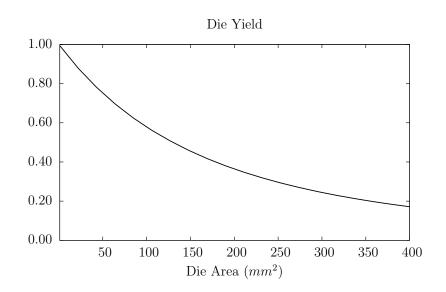

| 4.1          | The relationship between die area and its yield and cost                                                                                                                                      | 109        |

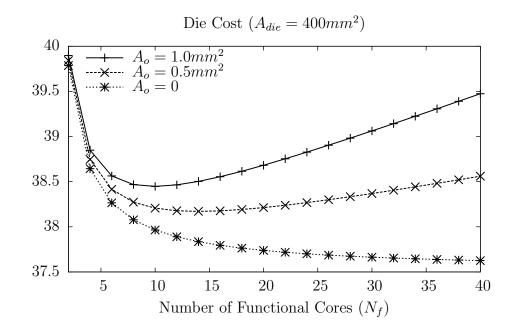

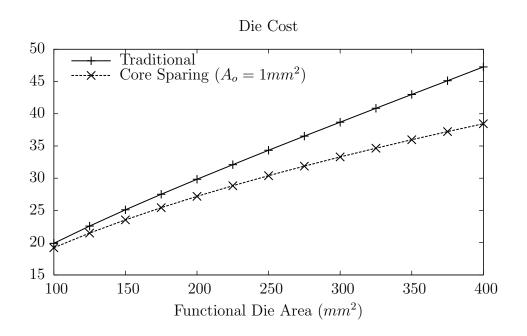

| 4.2          | Die cost $vs$ the total core count for different overheads                                                                                                                                    | 112        |

| 4.3          | Die cost for the traditional <i>vs</i> core sparing dice                                                                                                                                      | 114        |

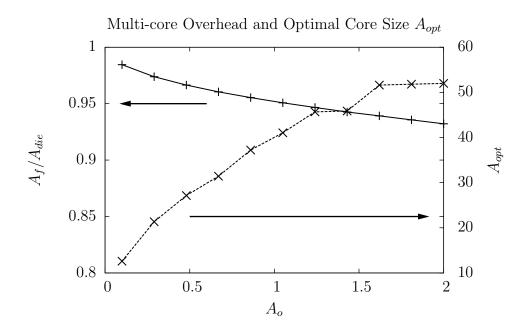

| 4.4          | The ratio of functional $A_f$ to the total die area $A_{die}$ is sensitive to                                                                                                                 |            |

|              | i-core overhead $A_o$                                                                                                                                                                         | 115        |

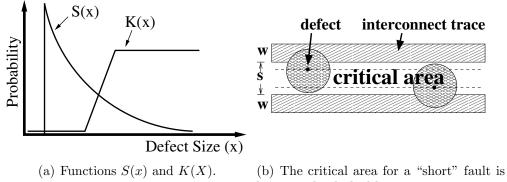

| 4.5          | Critical area parameters                                                                                                                                                                      | 117        |

| 4.6          | Device oversizing vs the number of functional cores on a $A_{die} =$                                                                                                                          |            |

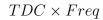

|              | $m^2$ . The values of $N = 11$ , $F = 1$ maximize $TDC \times Freq.$                                                                                                                          | 120        |

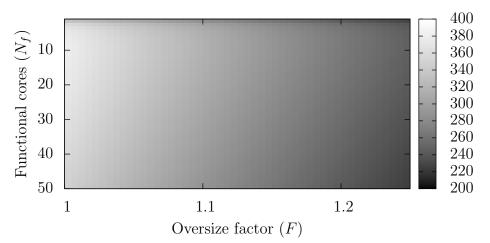

| 4.7          | The total die area vs r and $N_f$ . $(A_f = 400, A_o = 1, R = 1.5)$                                                                                                                           | 123        |

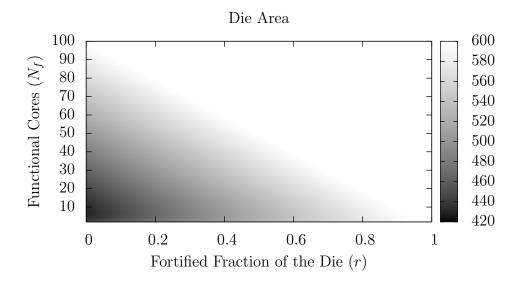

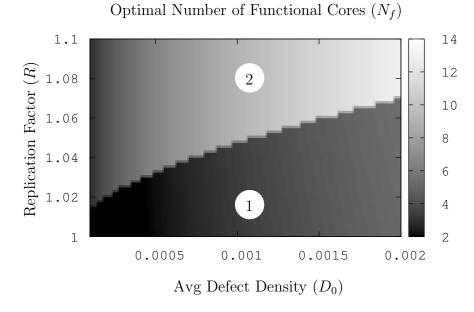

| 4.8          | Optimal $(r, N_f)$ parameters to minimize the total die area $A_{die}$ for                                                                                                                    | 105        |

|              | tional area $A_f = 400.$                                                                                                                                                                      | 125        |

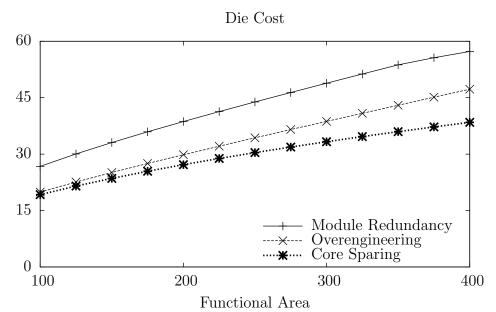

| 4.9          | Die cost comparison with different schemes. Parameters: $A_o =$                                                                                                                               | 100        |

| Imm          | $R^{2}, \alpha = 3, R = 2$                                                                                                                                                                    | 126        |

| 5.1          | NoC Simulator Components                                                                                                                                                                      | 132        |

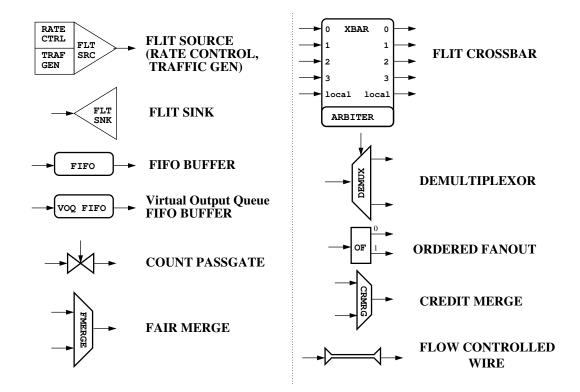

| 5.2          | NoC simulator components that exchange discrete events                                                                                                                                        | 137        |

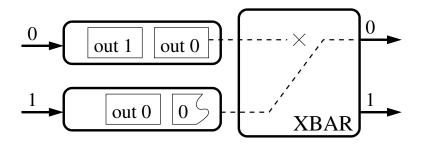

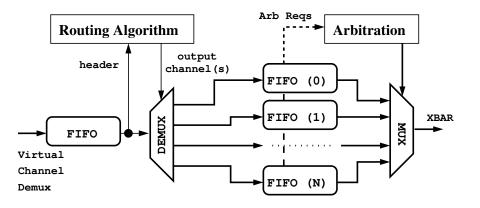

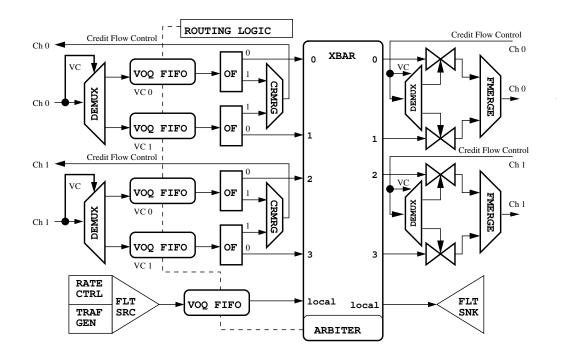

| 5.3          | Logical implementation of a Virtual Output Queue FIFO buffer.                                                                                                                                 | 149        |

| 5.4          | Router micro-architecture implemented in NoC simulator.                                                                                                                                       | 153        |

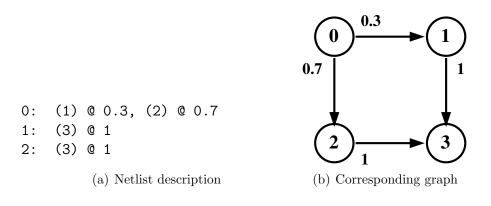

| 5.5          | An example of the netlist format extracted from IPM trace                                                                                                                                     | 162        |

| C 1          |                                                                                                                                                                                               |            |

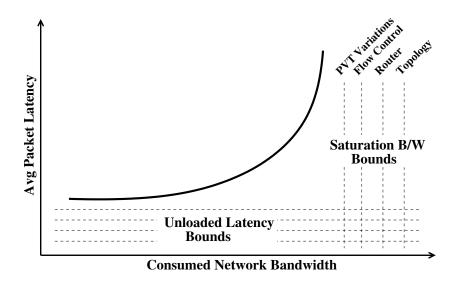

| 6.1          | Queuing systems defined relationship between packet latency (wait                                                                                                                             | 160        |

|              | ) and network bandwidth consumption                                                                                                                                                           | 168<br>177 |

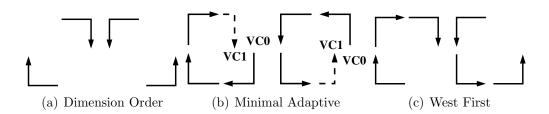

| $6.2 \\ 6.3$ | Allowed routing turns to avoid cyclical resource dependency $\dots$                                                                                                                           | 185        |

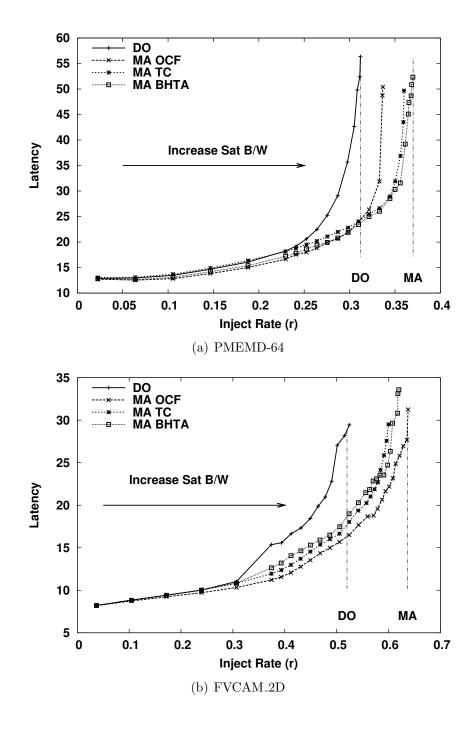

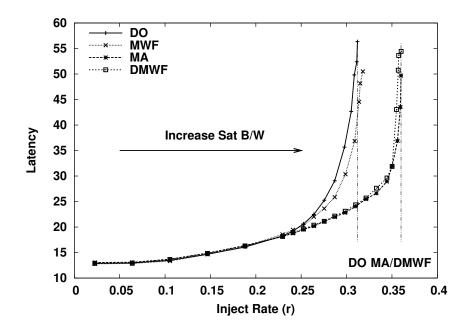

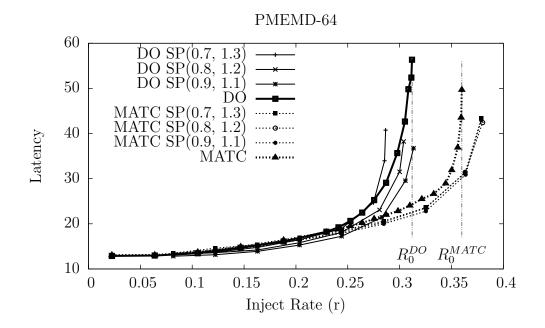

| 0.3<br>6.4   | SELECT() performance impact for two application graphs<br>Performance of West First algorithms on PMEMD-64                                                                                    | 183        |

| 6.5          | LBMHD application: the average packet latency for deterministic vs                                                                                                                            | 100        |

|              | tive algorithms                                                                                                                                                                               | 189        |

| auap         |                                                                                                                                                                                               | 109        |

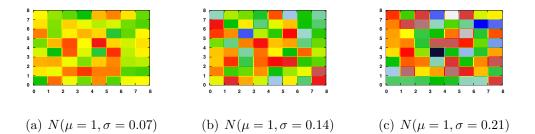

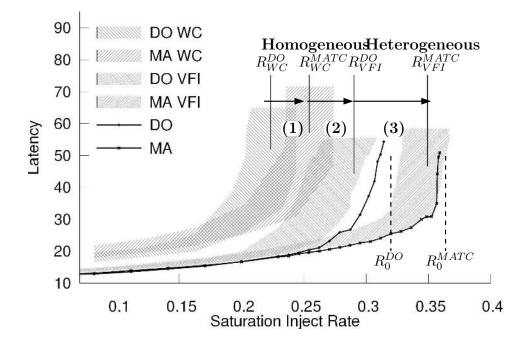

| 7.1          | Performance model for normally distributed stochastic variations.                                                                                                                             | 202        |

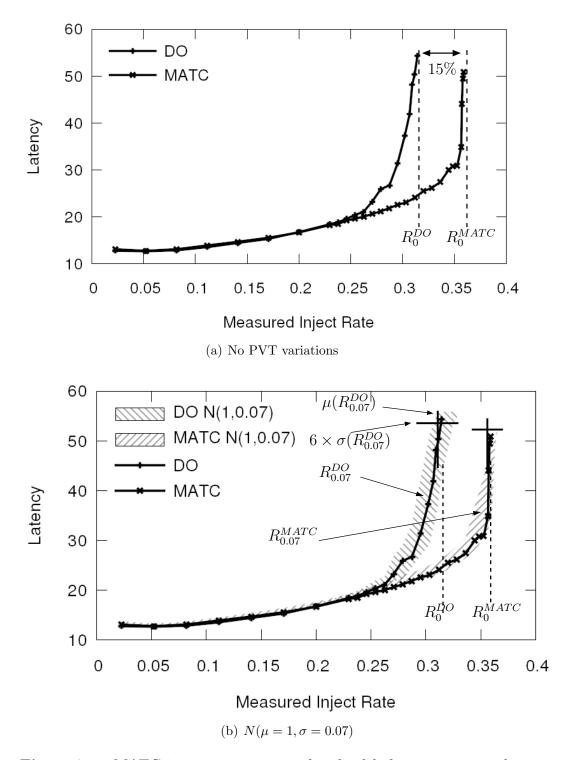

| 7.2          | MATC improves saturation bandwidth for PMEMD-64 and compen-                                                                                                                                   |            |

| sates        | for PVT variations                                                                                                                                                                            | 203        |

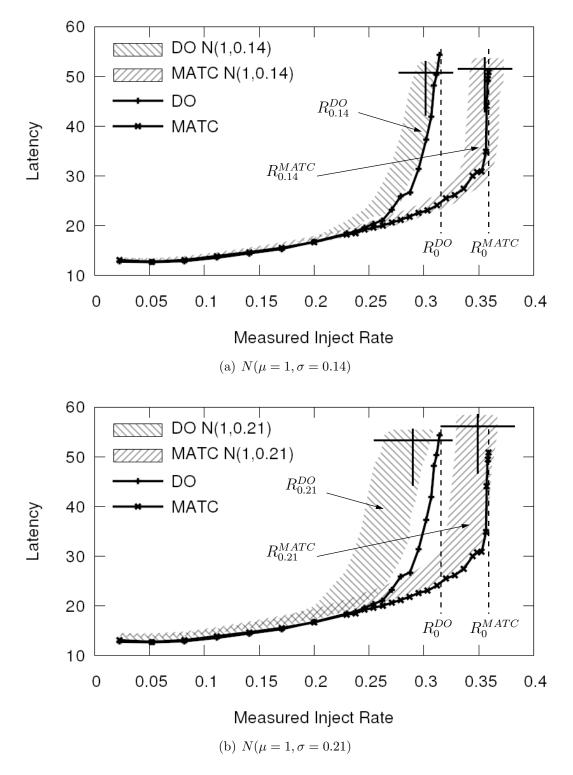

| 7.3          | MATC improves saturation bandwidth for PMEMD-64 and compen-                                                                                                                                   |            |

| sates        | for PVT variations                                                                                                                                                                            | 204        |

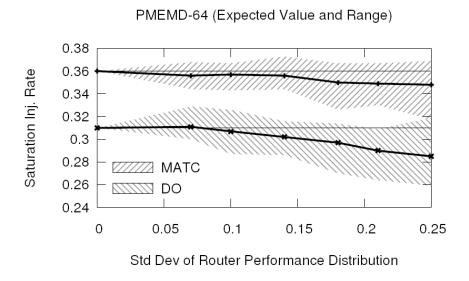

| 7.4          | PMEMD-64 Illustration of saturation bandwidth degradation for DO                                                                                                                              |            |

| and          | MATC                                                                                                                                                                                          | 207        |

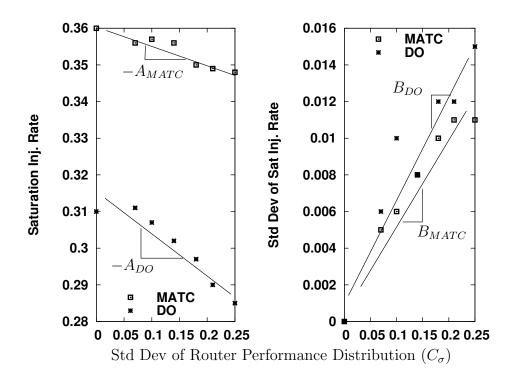

| 7.5          | <b>PMEMD-64</b> Extracting parameters A and B from curves $\mu(R_{\sigma}^{\mathcal{R}})$ vs                                                                                                  |            |

|              | $\operatorname{nd} \sigma(R^{\mathcal{R}}_{\sigma}) vs \sigma \ldots $ | 208        |

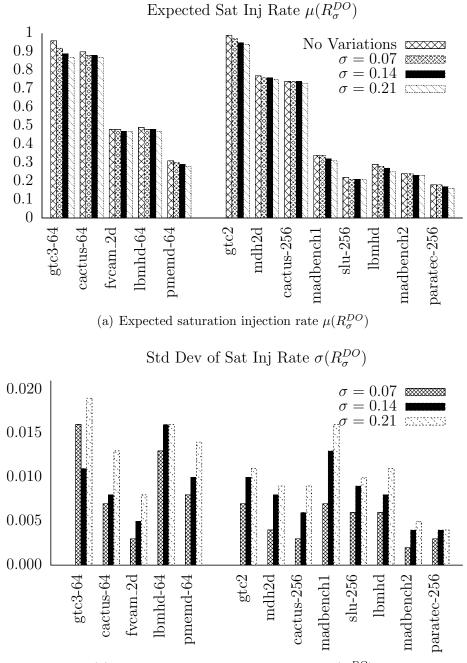

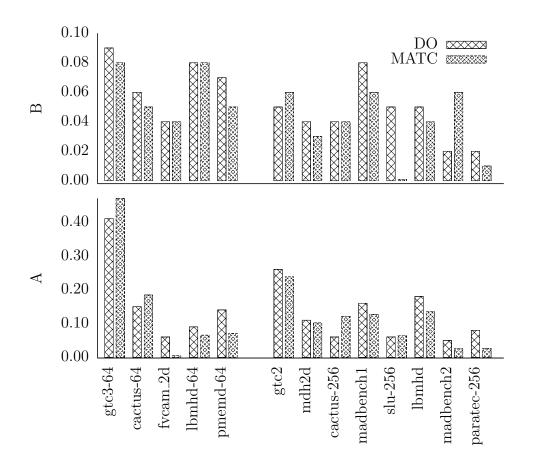

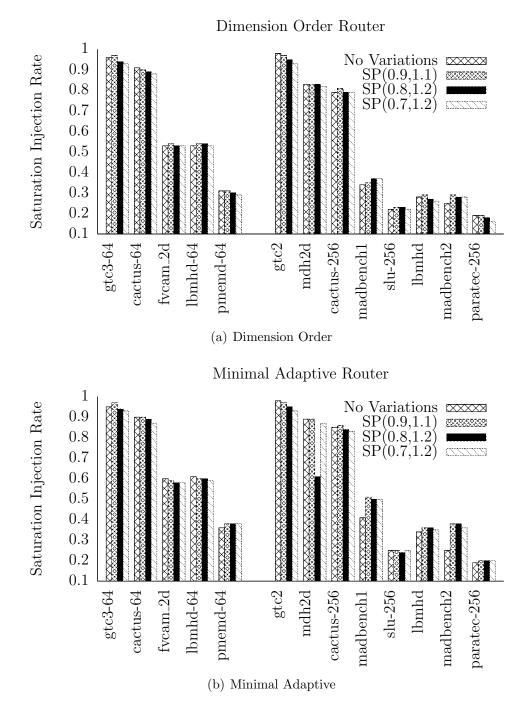

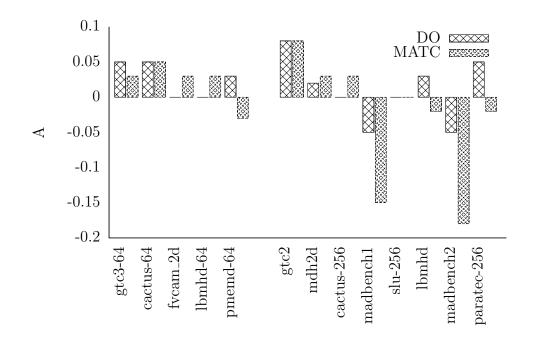

| 7.6          | Results summary for Dimension Order router                                                                                                                                                    | 212        |

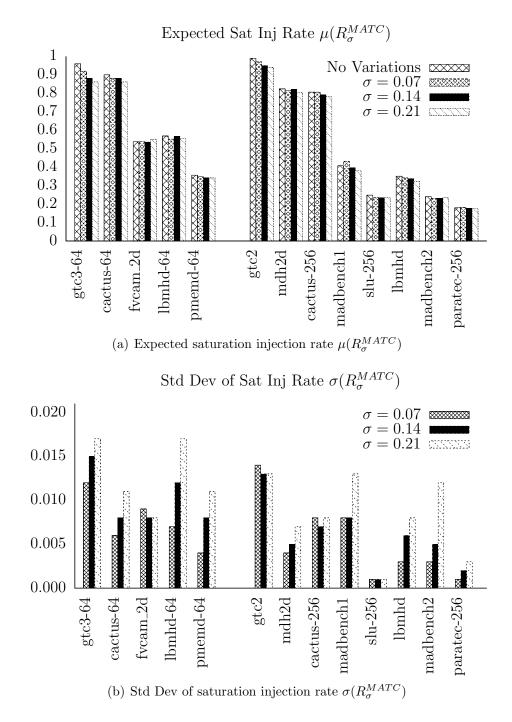

| 7.7          | Results summary for Minimal Adaptive router                                                                                                                                                   | 213        |

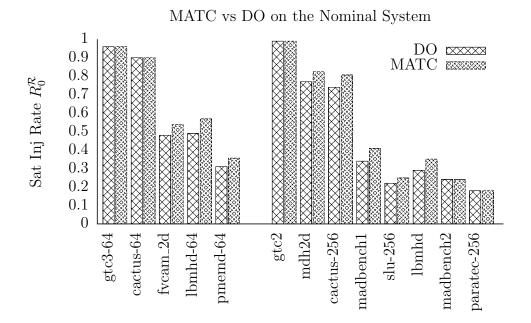

| 7.8    | Saturation bandwidth for MATC and DO on the nominal NoC.                                                  | 215 |

|--------|-----------------------------------------------------------------------------------------------------------|-----|

| 7.9    | Routing algorithm variation sensitivity parameters A and B                                                | 216 |

| 7.10   | An example of a Systematic Performance Gradient.                                                          | 218 |

| 7.11   | MATC completely compensates the bandwidth degradation                                                     | 219 |

| 7.12   | Results summary for a systematic performance gradient                                                     | 220 |

| 7.13   | Parameter $A$ is the slope of the degradation of the saturation in-                                       |     |

| jectio | on rate on a NoC with the performance gradient                                                            | 221 |

| 7.14   | MATC vs DO improvements in saturation injection rate                                                      | 226 |

| 7.15   | Guard-band reduction with MATC adaptive routing with stochas-                                             |     |

| tic va | ariations $C_{0.21}$ .                                                                                    | 229 |

| 7.16   | From improvements in saturation bandwidth to reduced design                                               |     |

|        | gins.                                                                                                     | 230 |

| 7.17   | Advantages of heterogeneous $vs$ homogeneous architectures: $40\%$                                        |     |

| gains  | s in saturation bandwidth, and $50\%$ in unloaded latency                                                 | 233 |

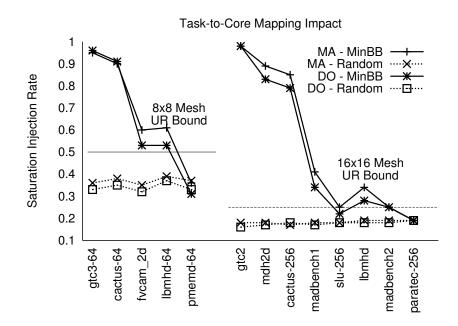

| 7.18   | Network saturation injection rate comparison with Min BB and                                              |     |

| Rand   | lom task mappings                                                                                         | 240 |

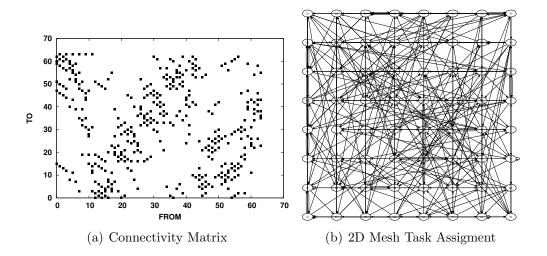

| 8.1    | Spatial communication properties of 1bmhd-64 application                                                  | 248 |

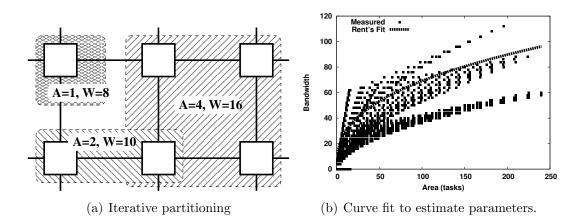

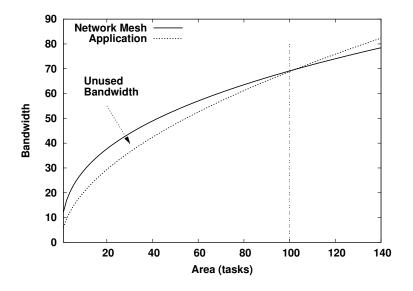

| 8.2    |                                                                                                           | 251 |

| 8.3    | Mismatch between network and application Rent's parameters re-                                            | -01 |

|        |                                                                                                           | 255 |

| 8.4    | $V_{(u,v)}^{\mathcal{R}}$ and $E_{(u,v)}^{\mathcal{R}}$ for Dimension Order and Minimal Adaptive routers. |     |

| 9.1    | The relationship between die area and yield                                                               | 270 |

| 9.2    | Relationship between the mapping quality and routing results                                              | 272 |

# List of Tables

| perm<br>1.2   | Every layer of a multi-core NoC system plays a role in dealing with<br>anent and dynamic variations                                                                                                                                                                           | 17<br>18                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| selves<br>2.2 | Semiconductor process steps and physical effects manifest them-<br>s as functional and parametric variations on multiple levels<br>Techniques to limit faults and PVT variations on every design level.<br>Summary of $N_{cp}$ and $L_{cp}$ parameters in the FMAX model [68] | 44<br>44<br>58                            |

| tectu         | Functionality and performance dimensions of a multi-core archi-<br>re                                                                                                                                                                                                         | 81<br>91                                  |

| thesis        | Parameters used in the models. Default values shown in paren-<br>s are based on ITRS 2005 [1] and used to obtain the experimental<br>ts                                                                                                                                       | 106                                       |

|               | 1                                                                                                                                                                                                                                                                             | $\begin{array}{c} 131 \\ 161 \end{array}$ |

| nicat<br>6.2  |                                                                                                                                                                                                                                                                               | 173<br>184<br>190                         |

| and I         |                                                                                                                                                                                                                                                                               | 206<br>236                                |

| 7.3  | Simulation result comparison for Minimal BB vs Random task         |     |

|------|--------------------------------------------------------------------|-----|

| map  | pping                                                              | 238 |

| 8.1  | Synthetic, characteristic communication patterns for routing algo- |     |

| rith | m research                                                         | 246 |

| 8.2  | A summary of HPC kernels and their Rent's parameters               | 248 |

| 8.3  | Routing and topology bound vs simulation results                   | 262 |

| 8.4  | The expected saturation bandwidth improvement for Minimal Adap-    |     |

| tive | vs Dimension Order routing algorithm.                              | 263 |

# Acknowledgements

This work is the result of generosity and support of many colleagues and friends who have made my experience in U.C. Berkeley a memorable one.

I would like to acknowledge the old SCORE gang, my friends Randy Huang, Eylon Caspi, Joe Yeh, Nick Weaver who have influenced me immeasurably, showed me what research is all about. I would like to thank André DeHon, whose drive for the scientific truth always served as my inspiration. Enormous debt of gratitude goes to my friends Yatish Patel, Mark Whitney, Sonesh Surana, Nemanja Isailovic for wonderful conversations, exchange of ideas, and helping hands. I am very grateful to my friend Michelle Bird who has helped enormously to communicate my ideas through this manuscript.

I am indebted to my adviser John Wawrzynek for the continuing support, encouragement and freedom to explore many interesting ideas throughout my graduate work. My dissertation committee Jan Rabaey, Paul Wright and Borivoje Nikolic have inspired and motivated the theme of this research effort.

MPI application traces, used in this work, were kindly provided by Shoaib Kamil and John Shalf from Future Technologies Group at the National Energy Research Scientific Computing Center (NERSC) at Lawrence Berkeley National Laboratory. The data traces were collected as a part of DOE/LBNL funded research. My work was supported by the GSRC Focus Center, one of five research centers funded under the Focus Center Research Program, a Semiconductor Research Corporation program, and by Berkeley Wireless Research Center (BWRC).

And most importantly, none of this work would even be possible without love, support and encouragement of my parents Mark and Irina, my brother Igor, and my wonderful wife Carmen, to whom this is dedicated.

# Curriculum Vitæ

### Yury Markovskiy

### Education

2004 Masters of Science in Computer Science, University of California, Berkeley

2000 Bachelor of Science in Computer Science and Electrical Engineering, University of California, Berkeley

### Experience

- Graduate Student Instructor, UC Berkeley (Spring and Fall 2002)

- Programmer Analyst II, UC Berkeley (2000 2001)

- Software Development Engineer, ProxiNet, Inc., Emeryville, CA (1999)

- Software Development Engineer, Canary Technology, Fremont, CA (1997 1998)

### Selected Publications

- Yury Markovsky, Yatish Patel, John Wawrzynek. "Using Adaptive Routing to Compensate for Performance Heterogeneity" in International Symposium on Networkson-Chip (NOC), San Diego CA, May 2009

- Yury Markovsky, John Wawrzynek. "On the opportunity to improve system yield with multi-core architectures" in IEEE International Workshop on Design for Manufacturability and Yield (DFM&Y, Santa Clara, CA, October 2007).

- Jana van Greunen, Yury Markovsky, Christopher R. Baker, Jan Rabaey, John Wawrzynek, Adam Wolisz. "A Platform for Smart Home Environments: The Case for Infrastructure" in Proc. of the 2nd International Conf. on Intelligent Environments (IE06, Athens, Greece, July 2006).

- Christopher R. Baker, Yury Markovsky, Jana van Greunen, Jan Rabaey, John Wawrzynek, Adam Wolisz. "ZUMA: A Platform for Smart-Home Environments" in Proc. of the 2nd International Conf. on Intelligent Environments (IE06, Athens, Greece, July 2006).

- André DeHon, Yury Markovsky, Eylon Caspi, Michael Chu, Randy Huang, Stylianos Perissakis, Laura Pozzi, Joseph Yeh, John Wawrzynek. "Stream Computations Organized for Reconfigurable Execution" in the Journal of Microprocessors and Microsystems 30 (2006) 334-354.

- Nicholas Weaver, Yury Markovskiy, Yatish Patel, and John Wawrzynek. "Post Placement C-slow Retiming for the Xilinx Virtex FPGA" in Proc. of the Eleventh ACM International Symposium on Field-Programmable Gate Arrays (FPGA 2003, Monterey, CA, Feb. 2003).

- Yury Markovskiy, Eylon Caspi, Randy Huang, Joseph Yeh, Michael Chu, André DeHon and John Wawrzynek. "Analysis of Quasi-Static Scheduling Techniques in a Virtualized Reconfigurable Machine" in Proc. of the Tenth ACM International Symposium on Field- Programmable Gate Arrays (FPGA 2002, Monterey, CA, Feb. 2002).

Eylon Caspi, Randy Huang, Yury Markovskiy, Joseph Yeh, André DeHon and John Wawrzynek. "A Streaming Multi-Threaded Model" in Third Workshop on Media and Stream Processors (MSP-3, Austin, TX, Dec 2001).

With the field of semiconductor manufacturing entering its sixth decade, many industry observers have anticipated exponential growth in chip performance to follow the gains in transistor and interconnect miniaturization. The reality is, however, that these gains have not yet been realized in the submicron process nodes. To state the problem in simple terms, additional efforts in miniaturization have resulted in disproportionately reduced die yield and increased manufacturing costs. We have reached diminished rates of return. Both the reduced yield and increased cost result from the fact that the smaller the transistor size, the more susceptible it is to an array of problems. Those problems include manufacturing faults, performance degradation and parametric variations.

The problems arising from semiconductor process scaling can be divided into two related categories: (1) limitations of on-chip power distribution and dissipation, and (2) Process-Voltage-Temperature induced variations.

The power consumption problems have been addressed in circuits through a variety of power management techniques that include Dynamic Voltage and Frequency scaling, power shutoff to inactive circuit modules, and transistors with different threshold voltages on a die. Reaching the power consumption ceiling has forced a more fundamental change—a movement from high clock frequency single core processors to lower frequency multi-core systems that exploit parallelism to scale overall performance.

Addressing PVT variations and faults in deep sub-micron processes has proven to be a significant challenge. Currently, attempts to minimize their impact amounts to large design margins that effectively push the technology back to larger geometries. As critical transistor sizes approach only tens of atoms and the process engineers can no longer control their manufacturing parameters accurately, these efforts hit the diminishing rate of returns. A solution is needed that would minimize over-engineering and extend performance scaling further. In other words, the solution that would tolerate and even take advantage of PVT variations in smaller geometry transistors.

# 1.1 Moore's Law: a blessing and a curse.

### 1.1.1 End to Moore's Law scaling?

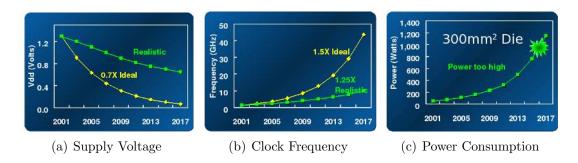

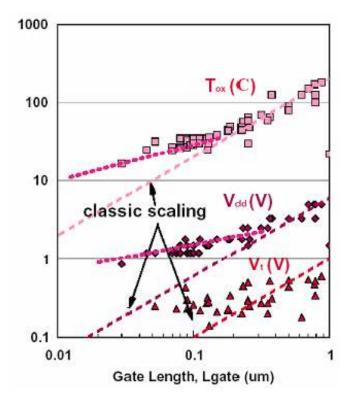

In 1965, Gordon Moore observed the number of transistors that can be placed cost-effectively on a die doubles approximately every two years [100]. Traditionally, this decrease in on-chip transistor size was accompanied by a corresponding reduction in circuit cycle time and power consumption. Originally, this trend was expected to continue without a limit. In what may have become a self-fulfilling prophesy, transistor sizes decreased over the years, and in fact, the number of transistors on a modern die exceeds two billion [129]. Unlike transistor count, however, scaling of many other critical transistor parameters has stalled as shown on Figures 1.1 and 1.2 [19, 55]. As modern sub-32nm processes are pushing against the physical manufacturing limits and properties of the silicon substrate, transistor gate oxide thickness  $T_{ox}$ , supply  $V_{dd}$  and threshold  $V_{th}$  voltages are most affected. Critical device sizes are approaching tens of atoms and can no longer be reproduced *accurately* on a die. The result is significant parametric variations in saturation and static currents, and capacitances that directly impact circuit performance. Small devices exacerbate the scaling problem further as they are more susceptible to faults and performance degradation due to aging (e.q. NBTI [117]).

In other words, although many small transistors fit on a die, each of those transistors is now less reliable, less performant, and more power-hungry.

In the prevalent synchronous circuit design style, device parametric variations reduce performance predictability. This translates into uncertainty in the circuit delay at the design time, which unduly inflates the clock cycle time. Growing power consumption and limits on heat dissipation present an additional constraints for clock frequency scaling.

Clock frequency has been the main VLSI performance scaling vehicle for more than 30 years; but now, to overcome power and parametric variation challenges, the industry is turning toward spatial parallelism with multi-core architectures such as Sun Niagara [102] and Intel Merom [116]. Even if an ideal compiler could extract all application parallelism, and a multi-core architecture could exploit and realize it, then the uncertainty of variations would still impose limits on power efficiency and system performance. The result would be a multi-billion transistor die that cannot deliver on its full potential.

As semiconductor devices shrink further, the increase in variations and faults makes it increasingly difficult to produce a reliable working system that meets the specification target under a range of dynamic operating conditions including different cross chip activity levels, temperature gradients and supply voltage distributions. For example, [4] demonstrated that a 35nm bulk transistor modeled

Figure 1.1: Ideal Moore's Law vs the actual and projected scaling [19].

Figure 1.2: Ideal Moore's Law vs the actual  $T_{ox}$ ,  $V_{dd}$ , and  $V_t$  scaling [55].

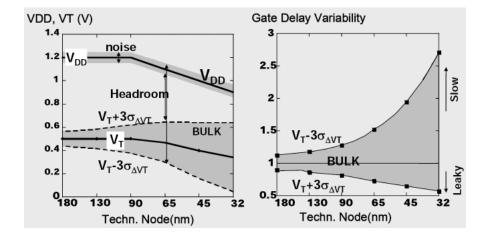

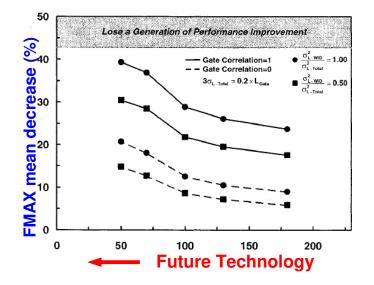

after a published Toshiba device [69], has more than 200mV of threshold voltage variation, and 100x leak current variation solely due to random dopant fluctuations at a single operating point. If you consider this transistor over the complete range of supply voltages and temperatures, its saturation and static current would vary widely and render some devices completely unusable due to high leakage or high threshold voltage. These large device parametric variations adversely affect transistor performance in a typical operating regime. As Figure 1.3 shows, supply voltage scaling is severely limited by transistor threshold voltage variations that are widening primarily due to random dopant fluctuations and line edge roughness (LER). Both effects are stochastic, difficult to control, and their impact worsens in smaller devices [39]. The transistor variations translate into asymmetric gate delay variations ranging from low delay, high leakage gates to high delay, low leakage gates. FMAX circuit performance model [22] and ITRS 2005 [1] predictions point to the maximum operating frequency varying by more than 70% from the mean in sub-32nm processes. Figure 1.4 illustrates the degrading effect that transistor size scaling has on the expected maximum circuit frequency.

### **1.1.2** Minimizing Variations

Faced with a collection of devices with very diverse performance, the semiconductor industry challenges designers to produce reliable systems out of very

Figure 1.3: Variations and scaling effect on transistor and gate performance [39].

Figure 1.4: Decreasing device sizes result in parametric variations that degrade maximum circuit operating frequency FMAX [22].

unreliable and unpredictable components. Alternative post-Silicon technologies, such as dense carbon nanotubes [40], do not solve but exacerbate this problem further as they require stochastic assembly. Most likely all future systems must be built out of components whose performance and fault model can best be described as stochastic.

In an attempt to mitigate faults and variations, designers rely on Design for Manufacturing (DFM) techniques in VLSI layout, circuit "rules of thumb," and other established safe design practices. Since the sources of process variations cannot be accurately controlled due to the very small device sizes, DFM rules take a *safe* approach and force design margins that grow as devices shrink, *i.e.* larger device sizes, spacings, metal fills, and other layout modifications that the original circuit designer may not be aware of.

As yield is the main concern for fabrication engineers, they impose increasingly restrictive and complex layout design rules. In spite of their complexity, these rules do not effectively convey the nature of underlying physical processes and cannot be applied selectively by the circuit designers. They increase device feature sizes and effectively push transistors back to a previous semiconductor process generation, surrendering the expected improvements from scaling.

In addition to DFM layout rules, circuit design techniques, such as adaptive body biasing [133] and adaptive supply voltage [29], can be applied to most circuits

because they simply realign device parameters from different dice to minimize variations. Other techniques, such as error correction, can be used efficiently only in some domains, *e.g.* memory arrays and communication circuits [109, 137].

As these layout and circuit techniques are applied to a specific design, their individual benefits on the parametric yield are hard to quantify. Their benefits may overlap and thus result in wasted power and performance. Fundamentally, there is a disconnect between the problem and the available solutions. The variations arise at the molecular level. DFM and circuit techniques, however, attempt to *minimize* the problem applying large margins and guardbands at the layout and circuit levels. It is similar to using a sledge hammer where a scalpel is needed, but a molecular scalpel does not exist. The result is that they reduce system performance to the worst-case operating point that accomodates all components including the outliers.

Due to trade secrets, very few published efforts have quantified the area, power, and performance losses due to DFM "over-engineering." Anecdotal evidence, however, suggests that DFM has a significant impact. One such effort has demonstrated 12% area reduction in 90nm and 65nm standard cell designs when the performance guard-bands are reduced (narrowed) by 40% [74]. The authors developed a die yield model containing area dependent and area agnostic components to illustrate the trade-off between guard-bands and the die area, which naturally corresponds to power consumption and performance.

If we had techniques that instead of narrowing the guardbands could dynamically embrace the heterogeneity and manage system components with wider performance variations, we could further reduce the area beyond these 12% and increase the die yield.

# 1.2 Our Novel Approach

This work's focus is the development and analysis of *system-level techniques* for dealing with faults and variations. Instead of attempting to narrow the spread of transistor and interconnect performance variations, is there a solution that tolerates a wider range of fluctuations? Can we compensate for rather than minimize parametric variations?

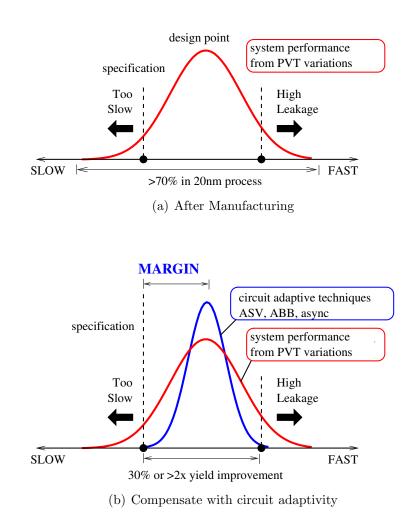

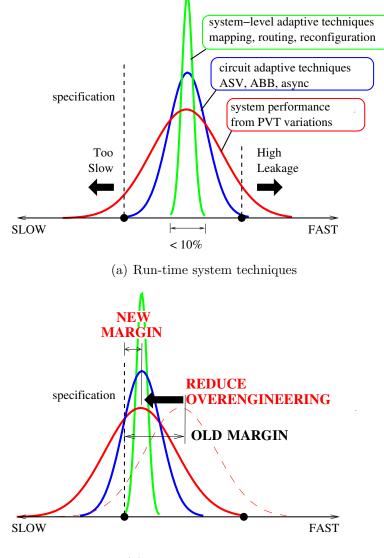

Figures 1.5 and 1.6 illustrate our common understanding of *system* performance variations as resilience techniques are applied. After DFM driven manufacturing, the dice and their components have a wide performance variance (Figure 1.5(a)). Some components may be considered faulty if they fall outside of the specified operating bounds. Circuit adaptive techniques narrow the variance to

Figure 1.5: PVT variations impact performance distribution on the current state of the art VLSI.

(b) Smaller design margins

**Figure 1.6:** The impact of PVT variations is reduced with multi-level techniques and translated in smaller design guardbands.

meet the targeted parametric yield and bring many outliers within the specification bounds (Figure 1.5(b)).

This work demonstrates that with run-time application mapping, network routing and reconfiguration, architects can further reduce the performance variance in multi-core systems and benefit from the proportionally smaller design margins (Figure 1.6(a)). Theoretically, with these high level techniques, the observed core-to-core variance can be reduced to 0% if the unit of resiliency management is small [118]. In practice, the improvements are limited by reconfiguration granularity and mapping quality. This work investigates resilience management at the core level, and thus small simple cores with independent clock and voltage domains that expose on-chip variations can reap the most benefit.

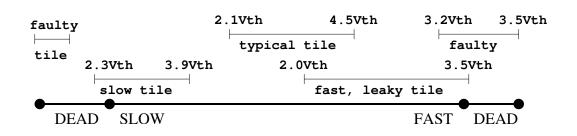

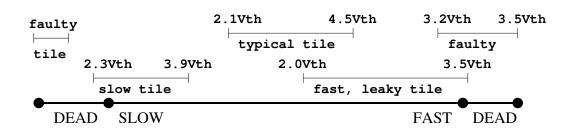

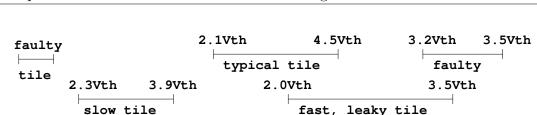

Traditionally, reliability has been treated as a binary problem: a component is either functional or not due to hard faults. However, every die and its components actually fall within a performance continuum: faulty, slow, nominal, fast, or leaky — where the last two may exceed the acceptable static leakage bound and be considered faulty. With respect to the execution model with core state check pointing, a faulty core is no different from a very slow processor that makes little forward progress, or a very fast but leaky processor. The advantage of our highlevel approach is to treat faults as a special case of Process-Voltage-Temperature (PVT) induced performance variations, rather than as separate effect.

This systematic, consistent approach to resiliency simplifies high-level mapping and routing algorithm implementation, eliminates special corner cases, and allows designers to focus on converting the performance gains from quality mapping and routing into smaller design margins or guard-bands. It is not possible in practice to eliminate all DFM rules that result in over-engineering, lost performance, area, and power. However, as we show our high level techniques can reduce the " $6\sigma$ " guard-bands, which can simplify and eliminate a number of DFM rules, improve system power efficiency and cost as illustrated on Figure 1.6(b). The resulting system can operate closer to its nominal performance point instead of the worst case point dictated by the underlying semiconductor process.

# **1.3** Multi-core and Reliability

Clock frequency scaling is no longer a practical tool for processor performance growth. The move to multi-core architectures and the desire to tolerate high memory latency are pushing the industry toward simpler and smaller in-order cores that time-multiplex multiple threads and operate on relatively low clock frequencies, such as Sun Niagara [102]. This means that cores are becoming cheaper. Cores are growing in numbers, and most importantly, are becoming a viable unit of reliability, power and performance management.

Figure 1.7: An illustration of core performance ranges controlled by DVS/DFS.

PVT variations turn a nominally homogeneous processor array into a collection of cores with heterogeneous performance [68], where the optimal power / performance point of each core is determined by its process variations and aging effects — discussed in detail in Chapter 2. A designer can choose to reduce clock frequency of some cores to match it to the slowest one on chip to create uniform on-die performance, wasting considerable resources to achieve the required system performance. This approach forces a  $3\sigma$  margin between the nominal design point and the target specification. The alternative is to expose the PVT variations to the run-time system by allowing each core to run at its own power/performance operating point dictated by the process corner. In practice, the voltage and temperature variations combined with the hardware controls such as Dynamic Voltage and Frequency Scaling (DVS/DFS), turn an operating point into a *range* as shown on Figure 1.7. The run-time system can use the hardware controls to select the core's operating point from that range to accommodate core-specific computation and communication demands in a power efficient manner.

Even without PVT variations, a nominally homogeneous multi-core system is a system where every core has different performance. First, consider that a multicore die is a highly complex system. Its behavior will only become more complex as it exceeds 100 cores and moves toward a more scalable memory and communication fabric organization, such as distributed memory blocks and stylized networks. As a result of contention for resources, cores suffer from unpredictable cache behavior, limited memory bandwidth and widely varying communication latency. Second, every application task may have very different computation and communication resource requirements and correspondingly affect every core. The problem is difficult to remedy, as parallelizing compilers are still relatively immature and cannot deliver the fine-grained parallelism needed for near-optimal load balance. Balancing and scheduling of communication traffic, memory and I/O accesses, in addition to the traditional processor scheduling, makes the compiler parallelization problem even more intractable.

An attempt at a performance homogeneous multi-core architecture would result in an inherently inefficient and slow implementation. Such an architecture would contain a uniform access memory structure, no caches, and require *a priori* optimally scheduled and balanced loads, which is not suitable for a system with large number of cores. To efficiently utilize massively parallel hardware, it must be heterogeneous to deliver on the architecture performance potential.

| System Layers | Permanent faults, variations          | Dynamic variations                      |  |

|---------------|---------------------------------------|-----------------------------------------|--|

| Application   |                                       | Error tolerance                         |  |

| Mapping       | Run-time Adaptive Routing and Mapping |                                         |  |

| Routing       |                                       | itun-time Adaptive flouting and Mapping |  |

| Topology      | Redundancy and Scalability            |                                         |  |

| Link          | Fault-tolerant control flow           | Adaptive links [137]                    |  |

| Circuit       | Self-checking circuits [146, 62]      | ABB, DVS [59, 132]                      |  |

Table 1.1: Every layer of a multi-core NoC system plays a role in dealing with permanent and dynamic variations

Presently, the performance of a realistic scalable system is typically best described with stochastic predictive models [70], which accommodate a number of factors given a probability distribution of critical events in an application. At the same time, PVT variations result to a significant degree from the inability to control stochastic semiconductor processes. The variations create a complex core performance profile that itself can most effectively be described with stochastic models. Therefore, why not combine both stochastic models together and simply treat *any* multi-core system as a distributed stochastic system?

A comprehensive resilience solution has to come from a complete cross-layer approach outlined in Table 1.1. Every layer has the potential to deliver an efficient solution to its part of the problem. For example, power-adaptive error resilient communication links may be most efficiently implemented at the circuit link layer. They require a retransmission scheme that should ideally be a part of an application or router implementation and not built into the circuit implementation

| Design Time                                                   | Run time                                                                               |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <ul> <li>circuits to <i>detect</i> fault/variations</li></ul> | <ul> <li>Map and route around faults and</li></ul>                                     |

| and <i>adapt</i> <li>layout to minimize impact of vari-</li>  | "slow" components <li>Optimize latency and B/W</li> <li>Degrade power/performance</li> |

| ations <li>provide run-time knobs</li>                        | gracefully                                                                             |

**Table 1.2:** Variation compensation techniques must be judiciously applied at design and run time.

to avoid wasting buffer resources for a relatively infrequent event. Applications or routers are better suited to handle retransmission because they are aware of system-wide communication QoS requirements. The challenge is to understand how to minimize the overlap between techniques from different system layers and reduce "over-engineering." The overall strategy is a combination of design time architecture and circuit decisions with the run-time adaptive techniques, outlined on Table 1.2.

Our answer to fault and performance variation resilience is run-time resource management: adaptive task-to-core mapping and routing, which ultimately is a solution to any performance heterogeneous configurable platform. If an architecture also provides hardware mechanisms for core-level fault detection and component reconfiguration, the multi-core system can also operate closer to its optimal power / performance regime. The run-time environment, *e.g.* an operating system or a hyper-visor, can manage resources using these hardware mechanisms.

#### Chapter 1. Introduction

It can reduce the impact of PVT variations better than disparate ad hoc point solutions because it is simultaneously aware of application resource *requirements* together with the hardware *utilization* and its on-chip performance profile. Overperforming cores and interconnect can compensate for under-performing ones to result in average rather than worst-case system performance.

The run-time management can be driven by analytical models or system introspection or a combination of the two. The analytical models may give insight into system behavior but lack practical applicability due to their limited accuracy, as is the case with PVT variation modeling. With process scaling, the contribution of hard-to-quantify and hard-to-model effects is likely to grow in comparison to systematic, modelable ones. Additionally, the criticality of different PVT variation sources changes with applications, chip architectures, and semiconductor process maturity. Thus, predicting and compensating for different variations with a model is inefficient and intractable.

This work focuses on introspection. Introspection is the dynamic process in which the run-time system observes behavior and performance of individual cores, network routers, and the system as a whole. It then attempts to modify task mapping and routing to improve overall system performance. The introspective approach has scalability and flexibility advantages over modeling by encompassing all inter-dependent factors into relatively simple observable metrics. With performance counters and control knobs, the run-time layer can form a closed-loop system with the architecture and thus converge toward the optimal operating point for an implementation and its particular process corner.

## **1.4** Research Contributions

This work identifies implementation requirements for a multi-core architecture with independent processor core clock and voltage domains. This architecture enables core and NoC router performance to abstract PVT variations and to guide introspective run-time adaptive mapping and routing (Chapter 3). The adaptive techniques thus simultaneously compensate for load imbalance resulting from static process and dynamic voltage and temperature induced performance variations as well as the application specific load imbalance. Based on this architecture, the following two techniques are investigated: core sparing and adaptive network routing.

**Core sparing** is a strategy of implementing extra cores that are reserved to replace cores that are defective due to manufacturing and/or dynamic faults (Chapter 4). The work develops an analytical model to demonstrate that this technique asymptotically reduces the die cost from the traditional "no spares"  $O(A^3)$  down to  $O(A^{\frac{1}{2}})$ , where A is die area. Additionally, the developed die cost models for DFM layout margins and circuit modular redundancy compare these established techniques with core sparing. These analytical models open a discussion about the trade-offs between over-engineering of individual cores, *i.e.* hardening and protecting circuits within a core vs relying solely on core redundancy to achieve system fault and variation resiliency. Our analysis shows that a die with many small unreliable cores is more cost effective than a die with fewer larger hardened reliable cores. To use core sparing dynamically, the core must detect faults and report them to the run-time system that can relocate tasks with a check-point and restart mechanism.

Adaptive network routing is the key to realizing the potential of a globally asynchronous tiled multi-core architecture to deliver average rather than worst case network performance (Chapters 6 and 7). The architecture exposes PVT induced performance variations as network router congestion, and allows an adaptive routing algorithm to compensate for the variation by balancing communication load across the network. A congestion-aware router simultaneously compensates for static manufacturing faults and process variation, dynamic voltage and temperature variations, aging, and application load imbalance. This simple and yet effective approach is necessary in an environment where the system component performance can best be described as stochastic or unpredictable. Adaptivity to the environment and operating conditions is essential to dealing with uncertainty in the future semiconductor processes, where detailed characterization and modeling is intractable.

As a result of this research effort, we have developed a flexible, discrete event Network-on-Chip simulation infrastructure targeted at investigating the impact of PVT-induced performance variations. The configurable simulator accommodates a range of routing algorithms and permits the simulation of communication patterns from *real* applications (Chapter 5).

# 1.5 Related Works

The subject of this research spans a great number of topics including low level PVT variations and their sources, task mapping, network routing, and design space exploration frameworks. The following discusses many relevant efforts and their relationship to this investigation. Although several efforts discuss their proposed architectures and systems as tolerant of PVT variability, faults and heterogeneity, none has addressed or compensated for these on the system level, which is the main contribution of this work.

Variability Modeling As technology moved to sub-micron dimensions, the interest in variability modeling has dramatically increased. The published research ranges from modeling the magnitude and range of manufacturing effects such as random dopant fluctuations (RDF) [89], line edge roughness (LER) [104] that directly affect threshold voltage and saturation current in transistors, to modeling gate parameters affected by the process variations: static leakage current [60] and delay [91]. The models identify that logic gate performance is most sensitive to RDF and LER, but also is heavily dependent on the supply and threshold voltage ratio [28].

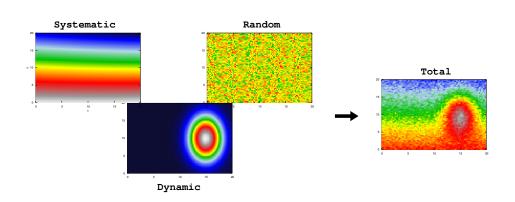

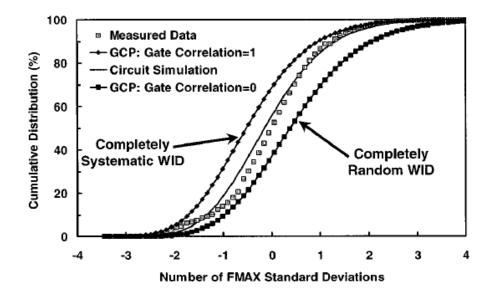

The FMAX model [22] offers a concise and intuitive way to analyze the expected critical path delay and its variance for a general circuit comprising a large number of logic gates and near critical paths. The FMAX model led to [68] that identified that the impact of within die and die-to-die variations on multi-core die is determined by the *systematic* on die variations, while stochastic effects are contained through longer critical path delay averaging within a core. The merits of the Globally Asynchronous architecture described in Chapter 3 are based on these conclusions, which also shaped our thinking about variation modeling within our simulation framework.

Adaptive circuits Although the thrust of this work is on core-level adaptivity, low level adaptive circuits can have a dramatic impact on power savings when used in certain appropriate domains, such as communication. [137] discusses a low power adaptive transmission scheme for NoC that trades off power consumption for error rate. This scheme requires a voltage controller and retransmission logic to recover from sudden changes in error rates. The supply voltage controller attempts to keep retransmissions very infrequent. This type of scheme must be tightly integrated with the NoC router logic for maximum efficiency to accommodate real time and QoS constraints in the minimal power envelope. For example, consider the case where a packet should be dropped instead of retransmitted to meet the constraints. This decision ideally must be made by the routing logic or the application.

This work also relies on different adaptation techniques such as Adaptive Body Biasing [133], voltage and frequency scaling [52]. Unlike adaptive communication schemes, these techniques are orthogonal to the functionality of a core or a router, but they dramatically impact its performance. Body biasing can realign the core performance to reduce the variance, and voltage and frequency scaling can navigate the performance operating range resulting from process variation impacts on a particular cores.

**Redundancy** and **Checkers** The only mechanism to combat faults and improve PVT variation resilience is redundancy. The examples of spatial redundancy include Triple Modular Redundancy (TMR) [131], row and column spares in DRAM [130], core spares in Sun Niagara [102] and Cell [77], and many others.

A simple example of temporal redundancy is Razor latch [53] that registers the value from a combinational path twice: first, on the clock edge, and second,

#### Chapter 1. Introduction

on the delayed clock edge. By comparing the latched values, the Razor latch can detect small changes in critical path delay as setup time violations and alert the system of an error. This technique saves 20–40% of power in a manufactured Alpha processor, that implemented dynamic voltage scaling and micro-architecture error state recovery controlled by the error-rate reported by Razor latches. Similar to our work, Razor is an introspective technique that smoothly adapts to changes in voltage and temperature, as well as aging and application instruction stream, which permits the processor to run closer to the average rather than the worst-case power consumption regime.

GALS Architectures Multiple clock and voltage systems, similar to the architecture described in Chapter 3 have been proposed and hailed for their potential in fault and PVT variation tolerance [92]. However, application implementation and study of actual performance of these systems has been scarce. [103] presents an application-specific partitioning scheme of the multi-core architecture into voltage-frequency islands (VFI) comprising core clusters to optimize energy consumption. The authors experimented with one small media application comprising fewer than 10 tasks, and showed approximately 35% energy reduction. The power/performance benefits of VFIs will be more significant in systems with greater number of processor cores. This work investigates network performance

#### Chapter 1. Introduction

for larger 64 and 256 core systems, and instead of clustering cores into VFIs, allows *each* core to select its own voltage / frequency operating regime.

Task Mapping is among the two critical run-time processes necessary to ensure computation load balance and to meet the expected performance of multicore system. Datta *et al* showed that even small scale, four and eight core systems with Non-Uniform Memory Access (NUMA) require "location" aware task-to-core assignment for maximum performance [38]. Mapping a communicating task graph onto a system with a large number of cores requires even more considerations than NUMA optimizations, which only considers data set partition and its affinity with the computation. The mapping problem is essentially a task communication graph embedding into the network topology graph given a set of bandwidth and latency constraints. It has been tackled in different environments from the Blue Gene/L super computers with 3D network topology [143] to a heterogeneous NoC [84].

Heterogeneous architectures are gaining popularity in the multi-core research community primarily for their power-efficiency due to core specialization. Asymmetric architectures with a single common ISA shared by all cores but different complexity, heterogeneous core implementations seems to be preferred. This configuration simplifies compilation but complicates and constrains run-time task scheduling [121, 11, 30, 12]. What these efforts have not considered yet is network topology and locality aware task mapping, which is among the most critical factors for high network performance.

This work does not focus on task-to-core mapping, but offers a cursory investigation of its performance impact in Section 7.5. For the network routing experiments, we use an existing Simulated Annealing FPGA placement algorithm to compute locality preserving task-to-core mappings [16].

Network Topology determines the most basic bounds of application network performance as discussed in Chapter 6. Its on-die implementation is critically important, and thus the VLSI layout, simplicity of implementation and verification must all play a central role in topology selection. Although many sources discuss complex but asymptotically high-throughput and low latency topologies, such as Leiserson's Fat Tree or Mesh of Trees [72], this work focuses on a regular simple mesh. Mesh and its derivative Torus have been studied extensively to identify the optimal dimensionality given fixed on-chip interconnect resources [35]. As on-chip interconnect throughput scales, a delay-optimal topology implementation points to a high dimensional meshes and tori [80]. This work, however, focuses on a low radix 2D mesh because the power consumption of a high-speed on-chip interconnect can be prohibitive. A low dimensional mesh with *slower* but wider inter-router channels should be preferred. A higher radix topology maybe more appropriate for inter-chip communication, since the pin count does not scale as fast as on-die transistor and interconnect density.

A regular mesh topology can be augmented with special long range links and customized for a particular application running on a multi-core system [113]. It is not clear how to apply this technique in general. Perhaps, one can insert *regular* long range links into a 2D mesh to increase its "global" reach and improve performance for applications with non-local communication pattern as is done in FPGA configurable interconnect [124].

Although every topology can be evaluated with performance and power metrics, this work is also interested in network path diversity to enable flexible compensation for PVT variations and faults as discussed in Section 3.2.

**Traffic Modeling** Application traffic pattern ultimately determines whether communication resource requirements match resources delivered by the network topology and routing algorithm. A complete but costly performance analysis can only be performed on an actual implemented multi-core system, which precludes any efficient design space exploration. Modeling and synthesis of communication patterns, some of which may be unknown, is critical in order to perform large design space exploration of novel architectures. Typically, network research is performed with a set of synthetic communication patterns ranging from easy and

#### Chapter 1. Introduction

load balanced (e.g. local, neighbor-to-neighbor) to global unbalanced patterns (e.g. tornado).

To meet the necessity for a more complex and realistic traffic patterns, Soteriou *et al* have proposed statistical traffic model that captures both temporal and spatial communication behavior [126]. The difficulty with that model spawns from the fact that the actual applications contain a combination of several communication patterns. Our work analyzes communication traces of High Performance Computing multitask kernels, and synthesizes the identical spatial traffic patterns in the developed NoC simulation framework (Chapter 5). These application traces were generated and previously analyzed by Shalf *et al* in the context of large multiprocessor supercomputers [119].

Adaptive Routing Although adaptive routing is not a novel concept, this work applies it to compensate for PVT variations across the die and deliver average rather than worst case network performance. Two published adaptive routing algorithms had a significant influence on this work: Dynamic Adaptive/Deterministic DyAD [66] and Channel Queue Routing CQR [122]. Although they apply to different topologies, both algorithm use flit buffer utilization as congestion metrics that drive distributed routing decisions. Additionally, both algorithms dynamically switch between different modes of operation: DyAD selects between deterministic and adaptive routing based on statically set congestion threshold; CQR uses a heuristic to detect network load imbalance and adjusts between a minimal and mis-routing path selections.

Fault Tolerant Routing This work focuses on adaptive routing as a vehicle to compensate for load imbalance resulting from PVT variations, but does not explicitly consider fault-tolerant routing. A congestion aware router behaves correctly with faulty nodes and routes traffic away or around them because the faulty, zero throughput nodes quickly become congested. At the same time, the routers around the faulty router also become congested. This growing congestion region would eventually result in a deadlock unless resolved externally because more buffers would contain packets waiting to be routed, but no forward progress can be made.

The way to resolve this problem is orthogonal to a routing algorithm or its ability to adapt. Detecting a fault and recovering from a fault is similar in principle to deadlock detection and recovery. It is an implementation specific decision that depends on the communication fabric guarantees. For example, if a fabric does not guarantee delivery, then simply dropping a packet on a time-out and marking unresponsive output channel as unavailable can solve the problem. This time-out and retransmit scheme must be supported by the run-time environment or the application if lossless delivery is required. A routing algorithm itself cannot make these decisions, but it simply has to adapt when an output router channel becomes unavailable.

A different approach to network fault-tolerance is stochastic routing [50], where to packets are replicated and propagated with certain probability in multiple directions, thus increasing their chances of not being dropped. This very interesting idea nonetheless requires support from the run-time system to handle arrival of multiple copies of the same packet, out of order arrivals, and a remote chance that no copy of a packet arrives to its destination at all.

Deterministic Routing using Safety Levels is an alternative to stochastic routing [139]. The algorithm consists of two components. The first one marks all nodes around a faulty node as unsafe according to special rules that logically modify network topology and guide packets away from *unsafe regions*. The latter part of the routing algorithm is adaptive. A packet is always forwarded to a safe node, if it is available, and an unsafe node otherwise.

**Design Exploration Frameworks** As a part of this research work, we have a developed a highly configurable Network on Chip simulation framework. The discrete event simulator easily incorporates the effects of PVT variations on NoC router components. To the best of our knowledge, no other framework that accommodates on-chip performance variations is currently available. A cycle-stepping simulator such as ORION [136] is an effective and widely used tool to evaluate routing algorithm performance and estimate its power consumption. The value of the simulator stems from integrated tools such as Garnet [5] that provides a detailed network model of a NoC implementation or Polaris [125] that performs MPSoC/NoC design space exploration. Unfortunately, ORION models globally synchronous systems and is valuable primarily for routing algorithm research. In contrast, Beigne *et al* developed an asynchronous NOC architecture design framework [10] that can produce GALS chip implementations, but has not demonstrated power/performance advantages over the equivalent, globally synchronous architecture. Our research effort bridges the gap, providing the infrastructure to study GALS network systems with real workloads, routing algorithms, switching schemes and other architectural parameters.

# **1.6** Dissertation Organization

This dissertation is organized as follows.

Chapter 2 discusses the sources and modeling of on-chip performance variations and their impact on multi-core die performance. The chapter highlights both the impact and limitations of a range of existing Design-for-Manufacturing (DFM) and circuit techniques designed to mitigate PVT variations. Chapter 3 presents the salient features of a core-level Voltage Frequency Island (VFI) architecture and globally asynchronous Network-on-Chip motivated by the on-die variation models.

Chapter 4 discusses the use of redundancy for fault tolerance at several system levels and develops analytical models for die yield and cost. The models demonstrate that core sparing is the most cost effective spatial redundancy as compared to larger layout margins and circuit module redundancy within a core.

Chapter 5 presents our Network-on-Chip simulation infrastructure used to investigate the network performance impact of PVT variations and the ability of adaptive routing algorithms to compensate.

Chapter 6 discusses network performance bounds and develops several adaptive routing algorithms and output channel selection heuristics to identify the overall best router for our set of High Performance Computing benchmarks.

Chapter 7 presents a new PVT variation network performance bound to provide a theoretical foundation for the network performance impact of PVT variations. It continues to demonstrate that a simple adaptive routing algorithm effectively compensates for the performance degradation. The chapter concludes by presenting a method to convert the performance gains of adaptive routing into reduced design margins and evaluates the impact of task-to-core mapping on network performance. Chapter 8 presents two analytical models that enable a designer to efficiently evaluate real application performance on 2D planar network topologies and compares the analysis results to those obtained from NoC simulation.

Chapter 9 summarizes this work and highlights critical lessons and trends that dominate the results obtained.

Chapter 10 discusses some unanswered questions and interesting research directions that are based on this investigation.

# Chapter 2 Performance Variations

Many researches have attempted to characterize parametric variations that result from modern semiconductor processes, and suggest appropriate actions that would reduce these variations and improve die parametric yield. These techniques are aggregated into a set of guidelines known as Design-for-Manufacturing (DFM). DFM rules grow in number and complexity with device scaling, but collectively remain inadequate to compensate for the variations, since they are applied ad hoc and solve a limited problem without any regard for other factors [79]. The impact of parametric variations continues to increase.

Attempts to characterize the performance impact of process variations at transistor and gate level resulted in detailed performance models [26, 18]. It suffices to say these models are inadequate because their authors out of necessity make simplifying assumptions on device parametric distributions. In practice, this limits applicability of these models to predicting trends and making design recommendations. They are not able to accurately estimate system performance, which is something that architects need.

The complete variability picture is significantly more complicated than useful models can describe or DFM can address. No one but the experts in the semiconductor fabrication facilities have a good understanding of the variations in the current and future processes. The ability to control stochastic processes such as etching, chemical deposition or lithography is fundamentally limited by physics. Therefore, DFM guard-bands and margins, or simply a lot of "over-engineering" remain the method employed to produce state of the art designs today.