## 17.1 A System-on-Chip EPC Gen-2 Passive UHF RFID Tag with Embedded Temperature Sensor

Jun Yin, Jun Yi, Man Kay Law, Yunxiao Ling, Man Chiu Lee, Kwok Ping Ng, Bo Gao, Howard Cam Luong, Amine Bermak, Mansun Chan, Wing-Hung Ki, Chi-Ying Tsui, Matthew Ming-Fai Yuen

Hong Kong University of Science and Technology, Hong Kong, China

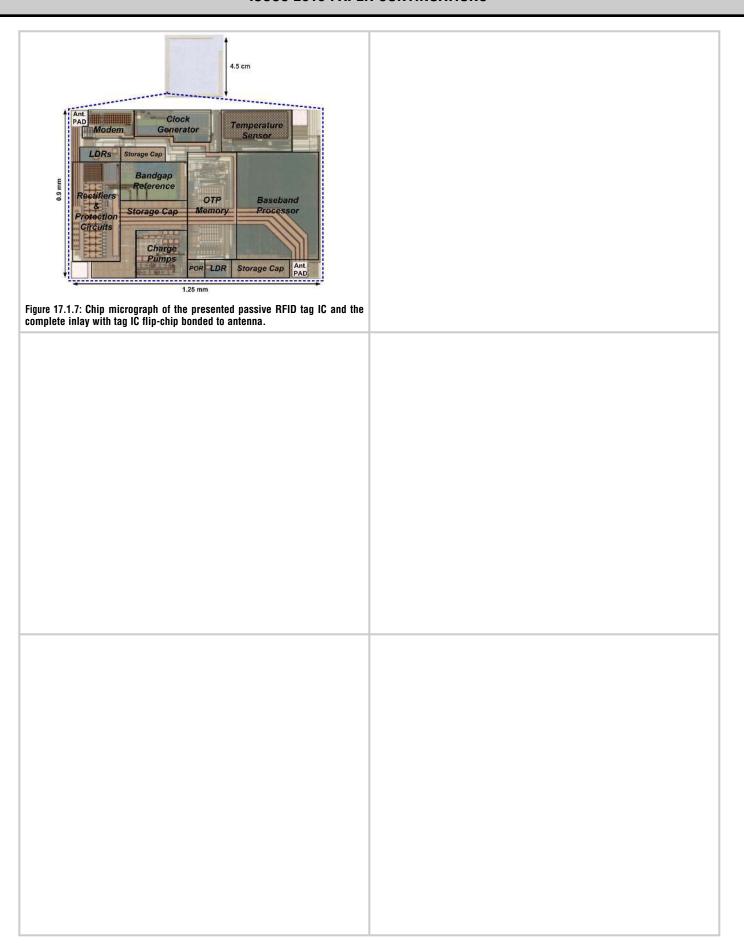

A system-on-chip passive UHF RFID tag with embedded temperature sensor is developed in a standard 0.18 $\mu$ m CMOS process for the EPC Gen-2 protocol from 860-960MHz [1]. Flip-chip technology is used to bond the developed tag IC to an antenna to realize a complete tag inlay, which is successfully demonstrated and evaluated in real-time wireless communications with commercial RFID readers.

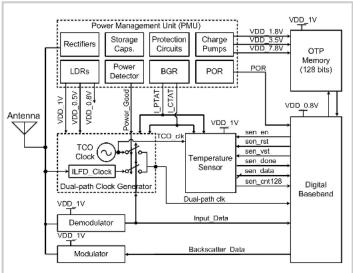

Figure 17.1.1 shows the block diagram of the tag IC. Multiple supply voltages, generated by a power management unit (PMU) using a separate-storage-capacitor technique to save area, are employed to optimize the performance of individual building blocks, while minimizing the total power consumption. A dual-path clock generator is used to generate on-chip clocks for signal processing to support both applications with either very accurate link frequency or very low power consumption. A low-power temperature sensor is also embedded with a gain-compensation technique that makes use of current correlation from the same bandgap reference (BGR) for the clock generator to reduce the temperature sensing error due to process variations.

Figure 17.1.2 shows the PMU. The rectifier (RECT1) supplies the 670nA BGR while the core RF-DC conversion is performed by a triple-output rectifier (RECT2). Further supply regulation is done using low-dropout regulators (LDRs). For the duration of PW (=Tari/2) [1], as the RF input is significantly attenuated due to the data modulation, the rectifier becomes inactive, and a storage capacitor C<sub>S</sub> is employed to supply both the load current I<sub>1</sub> and the reverse leakage current I<sub>leak</sub> that flows back to the rectifier, which results in a ripple voltage of  $VR_{CS}=(I_L+I_{leak})\times PW/C_S$ . In existing work [2], all the blocks share one single capacitor C<sub>s</sub>, which needs to be large enough to meet the ripple voltage requirement of the most noise-sensitive block. To provide a highly stable current for the dual-path clock generator, the BGR is required to have a small supply ripple of 0.1V, and, as a result, the single C<sub>s</sub> would need to be at least 1.75nF to supply the nominal total  $I_1$  of 14 $\mu$ A when Tari=25 $\mu$ s. In our work, three separate capacitors,  $C_{\text{Sx}}$  (x=1,2,3), are employed for different blocks with different optimal ripple voltages (0.4V, 0.25V, 0.1V, respectively), which helps to significantly reduce the total capacitance to 805pF, even with >10% margins. The switches  $S_x$  (x=1,2,3) are controlled by the demodulator's output to cut off  $I_{leak}$  during PW, which helps further reduce both the sizes of C<sub>Sx</sub> and the required input power for replenishing. M<sub>ST1</sub> and M<sub>ST2</sub> are used for start-up. High voltages of 3.5V and 7.8V, used for programming the OTP memory, are generated by three charge pumps (QPs). During the WRITE operation, a VCO is activated to regulate the QP\_VPP's output at 7.8V with an output current up to 20µA. With sufficient input power, the power detector (PD) sends a Power-Good (PG) signal to turn on S<sub>4</sub> to power up LDR<sub>3</sub> for the injection-locked frequency divider (ILFD) in the dual-path clock generator.

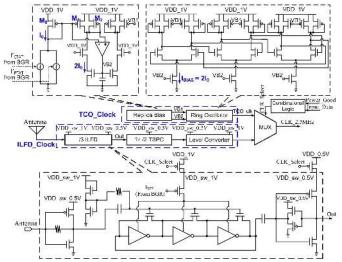

Figure 17.1.3 shows the dual-path clock generator. In the first path, to achieve the stringent link frequency accuracy (<±4%) over PVT variations specified by the EPC Gen-2 protocol, a proposed 19.5µW divide-by-3 ILFD followed by a cascade of divide-by-2 dividers is employed to derive an on-chip clock (~2.3MHz) directly from the RF input. A 1V current-starved ring oscillator with 300MHz selfoscillation frequency is used as the divider core, which is biased by a temperature-independent current  $I_{\text{REF}}$  from BGR to reduce frequency sensitivity due to temperature variations. A voltage limiter is inserted between the antenna and the ILFD input to handle large input signals. The output swing of the first ILFD and the supply voltages of the succeeding lower-frequency dividers are designed to be 0.5V to minimize power consumption. However, the ILFD working at the RF frequency consumes relatively large power. For applications that require better sensitivity, a low-power temperature-compensated oscillator (TCO) is also employed in a second clock path to trade off power dissipation with frequency accuracy. Different from [3], the TCO frequency is made to be proportional to the BGR current, which allows a co-design with the temperature sensor for gain compensation. Moreover, a temperature-independent frequency can be obtained by adjusting the temperature coefficient of the bias current  $I_{\text{BJAS}}$ . As shown in Figure 17.1.5, the measured TCO's frequency variation is within  $\pm 2.65\%$  with a much smaller power (1.5 $\mu$ W) than existing solutions [3][5]. Clock-path selection is automatically done by the power detector to turn the ILFD clock path ON or OFF depending on the available input power.

Existing solutions for embedded temperature sensors in passive RFID tags mainly suffer from a severe trade-off between accuracy and power. The sensor in [4] achieves an error of +2.4/-2.0°C by using a  $\Sigma\Delta$  ADC readout with onepoint calibration but consumes 9.2µW, which is 80% of the whole tag's power. In [5] and [6], the sensors consume merely 1.6µW and 0.22µW, respectively, but both require 2-point calibration to achieve errors of ±2.4°C and +3.0/-1.6°C, respectively. Figure 17.1.4 shows the presented embedded sensor using only 1point calibration to achieve good sensing accuracy. Time-domain readout is employed to eliminate the power-hungry ADCs. A temperature-modulated pulsewidth signal sen\_PW is generated by integrating the PTAT and the CTAT currents and is then quantized using the TCO clock. The sensor and the TCO use the PTAT and CTAT currents generated from the same BGR in PMU so that the current changes due to process variations in the two blocks track each other. The sensor gain, which is defined as the digitized difference of sen PW at the maximum and minimum temperature divided by the temperature range, is inversely proportional to the BGR current while the TCO clock frequency is proportional to the BGR current, which allows gain compensation due to current variation. Flicker noise is reduced by resetting the current signals after each conversion, and is averaged out together with wideband noise using on-chip averaging. At room temperature, the power of the sensor block is 104nW at 25S/s. The measured results of three samples demonstrate an accuracy of +0.4/-1.1°C after 1-point calibration (Fig. 17.1.5), which is small enough for food-monitoring applications. The ENOB of the sensor is 8b, and the corresponding resolution is about 0.35°C.

A 16×8b one-time-programmable (OTP) memory array based on gate-oxide anti-fuse technology in a standard CMOS process with no extra mask, is also embedded. The baseband implements an EPC-compliant custom command to perform the complete SENSE-WRITE-READ operation (Fig. 17.1.4) in addition to all the mandatory commands required by the EPC Gen-2 protocol.

The complete tag chip with 1.1mm² area is fabricated in a standard 0.18µm CMOS process. As shown in Figure 17.1.7, the tag IC is aligned and bonded onto the antenna printed on PET film using flip-chip technology with Au stud bumps for low cost. Tested with an RFID tester and commercial RFID handheld readers, the tag inlay shows a sensitivity of –6dBm and a sensing error of +0.4/–1.1°C with 1-point calibration. The measured performance is summarized in Figure 17.1.6.

## Acknowledgements:

This work was supported by the grant ITP/027/07LP funded by Hong Kong Innovation and Technology Fund (ITF) with support from the Hong Kong R&D Center for Logistic Supply Chain Management.

## References:

[1] EPCGlobal, "EPC Radio-Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860 MHz – 960 MHz - Version 1.0.9," 2004.

[2] R. Barnett, et. al., "A Passive UHF RFID Transponder for EPC Gen 2 with - 14dBm Sensitivity in 0.13µm CMOS," *ISSCC Dig. Tech. Papers*, pp. 582-583, Feb., 2007.

[3] K. Sundaresan, P. E. Allen, and F. Ayazi, "Process and Temperature Compensation in a 7-MHz CMOS Clock Oscillator," *IEEE J. Solid-State Circuits*, vol. 41, pp. 433-442, Feb., 2006.

[4] K. Opasjumruskit, et al, "Self-Powered Wireless Temperature Sensors Exploit RFID Technology," *IEEE Pervasive Computing*, vol. 5, pp. 54-61, Mar., 2006.

[5] N. Cho, et al., "A  $5.1\mu$ W UHF RFID Tag Chip Integrated with Sensors for Wireless Environmental Monitoring," *Proc. ESSCIRC*, pp. 279-282, Sept., 2005. [6] Y.-S. Lin, D. Sylvester, and D. Blaauw, "An ultra low power 1V, 220nW temperature sensor for passive wireless applications," *Proc. CICC*, pp. 507-510, Sept., 2008.

Diagram of Power Management Unit (PMU) 22-stage RECT1 (105pF)▼ Circuits VCO POR QP-VPP VDD\_1V  $\nabla$ LDR2 ± C52 (390pf VDB\_1V RF N limiter PD 22-stage RECT2 & Sotio LDR1 GND 후 c². (310pt Circuits LDR3 Power Detector (PD)

Figure 17.1.1: Block diagram of the developed passive RFID tag IC.

Figure 17.1.2: Block diagram and schematics of the proposed power-management unit.

VDD 1V

VDD VDD 1V sen\_data sen\_rst sen\_cnt128 CH ACK on Reg RN Select cw Query RN16 RN18 Tag Reply EPC Cw Sensing ow Req\_RN ow Write ow Read Tag Reply T\_Dələ RN16 T\_Data Success

from BGR

Figure 17.1.3: Block diagram and schematics of the proposed dual-path clock generator.

Figure 17.1.4: Simplified schematic of the integrated temperature sensor and the SENSE-WRITE-READ working flow.

| Supply Voltage (V)<br>0.5 1.0 1.5 2.0 2.5 3.0 3.5 a.c |

|-------------------------------------------------------|

| 2.36 Freq Variation (@20°C): 4                        |

|                                                | This work                                            | [4]                                     | [5]                                      | [6]                       |

|------------------------------------------------|------------------------------------------------------|-----------------------------------------|------------------------------------------|---------------------------|

| Process                                        | 0.18μm CMOS                                          | Not available                           | 0.25 μm CMOS                             | 0.18 μm CMOS              |

| Tag chip Area                                  | 1.1 mm <sup>2</sup>                                  | 1.4 mm <sup>2</sup>                     | 0.42 mm <sup>2</sup>                     | Not applicable            |

| Frequency range                                | 860-960MHz                                           | 100-150kHz                              | 860-960MHz                               | Not applicable            |

| Commercial standard<br>supported               | EPCglobal Gen 2<br>Compliant                         | Not available                           | Not available                            | Not applicable            |

| Tag Type                                       | Passive                                              | Passive                                 | Passive                                  | Not applicable            |

| Tag Loading Power<br>Consumption               | 12μW (only TCO elock<br>activated)                   | 12 µW<br>(10µA/Assuming<br>1.2V supply) | 5.1µW                                    | Not applicable            |

| Sensitivity                                    | -6 dBm (only TCO clock<br>activated)                 | Not available                           | Not available                            | Not applicable            |

| Reading and Temperature<br>Sensing Distance    | 4 m<br>(Reader EIRP 4W, only<br>TCO clock activated) | 10-25cm                                 | Not available                            | Not applicable            |

| Internal Clock Frequency<br>(local oscillator) | 2.2MHz                                               | 100-150kHz                              | 330kHz                                   | 100kHz                    |

| Sensor                                         | Temperature sensor                                   | Temperature<br>sensor                   | Temperature and<br>photo sensors         | Temperature<br>sensor     |

| Power Consumption of<br>Temperature Sensor     | (0.104 +0.8 +1.5)μW<br>(Sensor+BGR+ΓCO) <sup>1</sup> | 9.6 µW<br>(8µA/Assuming<br>1.2V supply) | (1.2+1.8)μW<br>(Sensor+TCO) <sup>1</sup> | 0.22 μW                   |

| Temperature Sensing<br>Range                   | -20°C to 30°C                                        | 0°C to 100°C                            | 0°C to 80°C                              | 0°C to 100°C              |

| Sensing Error                                  | +0.4/-1.1 °C 2                                       | +2.5/-2 °C 2                            | +/-2.4°C3                                | +3/-1.6 °C 3              |

| ENOB                                           | 8 bits<br>@25 samples/s                              | Not available                           | Not available                            | 6.5 bits<br>@100 samples/ |

Figure 17.1.5: Measured TCO frequency variation and temperature sensing error after one-point calibration.

Figure 17.1.6: Measured tag performance and comparison with other tags and temperature sensors.

The BGR and TCO are also required by other functions of tag, and are not dedicated for temperature sensor

<sup>&</sup>lt;sup>2</sup> After one-point calibration.

<sup>&</sup>lt;sup>3</sup> After two-point calibration

## **ISSCC 2010 PAPER CONTINUATIONS**