# A Technique for Reducing Rectifier Reverse-Recovery-Related Losses in High-Power Boost Converters

Milan M. Jovanović, Senior Member, IEEE

Abstract—A circuit technique that reduces the boost-converter losses caused by the reverse-recovery current of the rectifier is described. The losses are reduced by inserting an inductor in the series path of the boost switch and rectifier to control the di/dt rate of the rectifier during its turn off. The energy from the inductor after the boost switch turn off is returned to the input or delivered to the output via an active snubber.

*Index Terms*—Active snubber, boost converter, power factor correction, reverse-recovery loss, zero-voltage switching.

# I. INTRODUCTION

N RECENT years, significant research and development efforts have been made to come up with a cost-effective soft-switching technique to improve the performance of the boost converter. The main reason for such a keen interest in the boost topology stems from the fact that the continuous-conduction-mode (CCM) boost converter is the preferred topology for implementing the front-end converter for active input-current shaping at higher power levels.

When the boost converter is used as an input-current shaper, its input is the rectified mains voltage, which, depending on applications, can be in the 90–480-Vac range. Since the dcoutput voltage of the boost converter must be higher than the peak input voltage, the output voltage of the boost input-current shaper is generally high. Due to the high-output voltage, the converter requires the use of a fast-recovery boost rectifier. At high-switching frequencies, fast-recovery rectifiers produce significant reverse-recovery-related losses when switched under "hard-switching" conditions [1]. These losses can be significantly reduced, and, therefore, a high-conversion efficiency can be maintained even at higher switching frequencies by employing a soft-switching technique.

So far, a number of soft-switched boost converters and their variations have been proposed [2]–[5]. All of them employ an auxiliary active switch with a few passive components (inductors and capacitors) to form an active snubber [6] that is used to control the di/dt rate of the rectifier current and to create conditions for zero-voltage switching (ZVS) of the main switch and rectifier.

Manuscript received January 3, 1997; revised December 17, 1997. Recommended by Associate Editor, N. Femia.

The author is with the Power Electronics Laboratory, DELTA Products Corporation, Research Triangle Park, NC 27709-2173 USA.

Publisher Item Identifier S 0885-8993(98)06484-9.

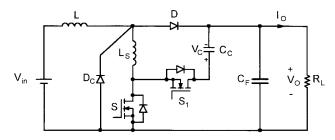

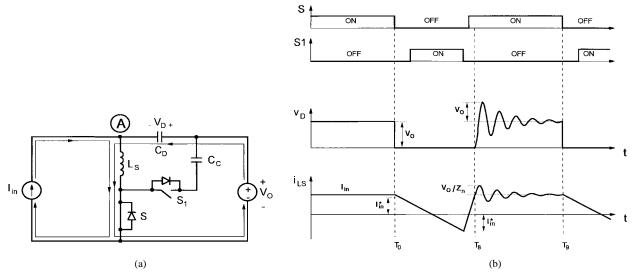

Fig. 1. Proposed boost power stage.

The technique described in this paper reduces the reverserecovery related losses of the boost rectifier by controlling the di/dt rate of the rectifier current with a snubber inductor connected in series with the boost switch and rectifier in the same way as in [4] and [5]. The series connection of the auxiliary switch and the clamp capacitor, which is used to provide the discharging path of the snubber inductor current (energy) when the main switch is turned off, can be connected to any dc point such as output, input, or ground. The connection to the converter input or output requires an n-type MOSFET, while the ground connection needs to be implemented with a p-type MOSFET. The parasitic ringings caused by the interaction of the junction capacitance of the rectifier and the snubber inductor used to control its di/dtrate are eliminated by a clamp diode connected between the anode of the boost rectifier and ground. As a result, the voltage stress on the rectifier in the proposed technique is limited to the output voltage. The operation of the proposed circuit is similar to the operation of active-clamp circuits which are in isolated converters mainly used to optimize the transformer reset, recover leakage-inductance energy, and achieve soft switching [7]-[9] and which have also been employed as active snubbers in nonisolated converters [6].

# II. PRINCIPLE OF OPERATION

The circuit diagram of the boost converter which employs the new technique for reverse-recovery-loss reduction is shown in Fig. 1. The circuit in Fig. 1 uses n-type MOSFET auxiliary switch S1 and clamp capacitor  $C_C$  connected in series to discharge the energy stored in snubber inductor  $L_S$  to the output after S1 is turned off. Diode  $D_C$  is employed to eliminate the parasitic ringings between the junction capacitance of D and inductor  $L_S$  by clamping the anode of D to ground.

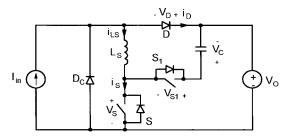

Fig. 2. Simplified circuit diagram of boost power stage showing reference directions of currents and voltages.

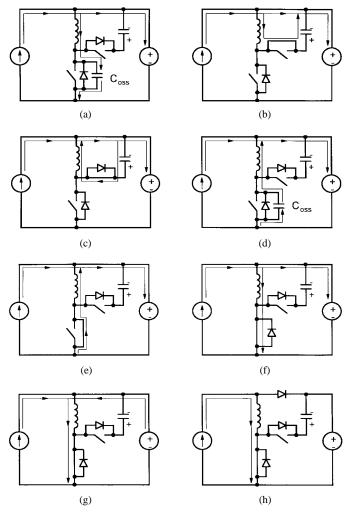

To simplify the analysis of operation, it is assumed that the inductance of boost inductor L is large so that it can be represented by constant current source  $I_{\rm in}$  and that the output-ripple voltage is negligible so that the voltage across the output filter capacitor can be represented by constant voltage source  $V_O$ . The circuit diagram of the simplified converter is shown in Fig. 2. In addition, it is assumed that in the on state, semiconductors exhibit zero resistances, i.e., they are short circuits. However, the output capacitances of the MOSFET's and the reverse-recovery charge of the rectifier are not neglected in this analysis. To further facilitate the explanation of operation, Fig. 3 shows topological stages of the circuit in Fig. 2 during a switching cycle, whereas Fig. 4 shows the power-stage key waveforms. It should be noted that because the junction capacitance of boost rectifier D has been neglected for the time being, clamp diode  $D_C$  is not shown in Fig. 3 since it never conducts.

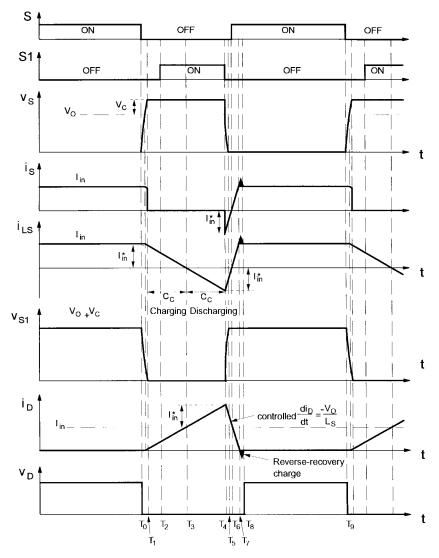

As can be seen from the timing diagrams for the boost and auxiliary switches in Fig. 4, the switches never conduct simultaneously. In fact, the proper operation of the power stage requires appropriate dead times between the turn off of boost switch S and turn on of auxiliary switch S1 and vice versa.

Before boost switch S is turned off at  $t=T_O$ , the entire input current  $I_{\rm in}$  flows through inductor  $L_S$  and switch S. At the same time, rectifier D is off with a reverse voltage across its terminals equal to output voltage  $V_O$ . Auxiliary switch S1 is also off, blocking the voltage  $V_O + V_C$ , where  $V_C$  is the voltage across the clamp capacitor.

After switch S is turned off at  $t = T_0$ , the current which was flowing through the channel of the MOSFET is diverted to the output capacitance of the switch,  $C_{oss}$ , as shown in Fig. 3(a). As a result, the voltage across switch S starts linearly increasing due to the constant charging current  $I_{\rm in}$ . During this stage, auxiliary-switch voltage  $v_{S1}$  decreases from  $V_O + V_C$ toward zero, while boost-switch voltage  $v_S$  increases from zero toward  $V_O + V_C$  (Fig. 4). When voltage across switch S reaches  $V_o$ , rectifier D starts conducting and the current through inductor  $L_S$  starts decreasing due to a negative voltage across its terminals, as shown in Fig. 4. This topological stage ends at  $t = T_1$ , when voltage  $v_S$  reaches  $V_O + V_C$  and the antiparallel diode of switch S1 starts conducting. At that moment, the remaining inductor current  $i_{LS}$  is diverted into clamp capacitor  $C_C$ , and switch voltage  $v_S$  is clamped to  $V_O + V_C$ , as shown in Fig. 3(b).

During the topological stage shown in Fig. 3(b), inductor current  $i_{LS}$  continues to decrease as it discharges to clamp

Fig. 3. Topological stages of boost power stage. (a)  $[T_0,\ T_1]$ , (b)  $[T_1,\ T_3]$ , (c)  $[T_3,\ T_4]$ , (d)  $[T_4,\ T_5]$ , (e)  $[T_5,\ T_6]$ , (f)  $[T_6,\ T_7]$ , (g)  $[T_7,\ T_8]$ , and (h)  $[T_8,\ T_9]$ .

capacitor  $C_C$  (Fig. 4). If the capacitance of  $C_C$  is large, capacitor voltage  $v_C$  is almost constant and inductor current  $i_{LS}$  decreases linearly. Otherwise,  $i_{LS}$  decreases in a resonant fashion. As  $i_{LS}$  decreases, rectifier current  $i_D$  increases at the same rate because the sum of  $i_L+i_D$  is equal to constant input current  $I_{\rm in}$ . This topological stage ends at  $t=T_3$  when  $i_{LS}$  reaches zero and the antiparallel diode of auxiliary switch S1 stops conducting. To achieve ZVS of S1, it is necessary to turn on the transistor of switch S1 before  $t=T_3$ , i.e., while its antiparallel diode is conducting. In Fig. 4, the MOSFET of switch S1 is turned on at  $t=T_2$ .

If the transistor of switch S1 is turned on prior to  $t=T_3$ , inductor current  $i_{LS}$  will continue to flow after  $t=T_3$  in the opposite direction through the closed transistor, as shown in Fig. 3(c). At the same time, rectifier current  $i_D$  will continue to increase at the same rate, exceeding the input-current level  $I_{\rm in}$  (Fig. 4). During this topological stage, the energy stored in clamp capacitor  $C_C$  during interval  $[T_1-T_3]$  is returned to the inductor in the opposite direction. This interval ends at  $t=T_4$  when auxiliary switch S1 is turned off.

After S1 is turned off, inductor current  $i_{LS}$  cannot flow anymore through clamp capacitor  $C_C$ . Instead, it continues to

Fig. 4. Key waveforms of boost power stage.

flow through output capacitance  $C_{oss}$  of boost switch S, as shown in Fig. 3(d). Since  $i_{LS}$  discharges  $C_{oss}$ , boost-switch voltage  $v_S$  decreases from  $V_O + V_C$  toward zero. At the same time,  $i_{LS}$  increases toward zero and  $i_D$  decreases toward  $I_{\rm in}$ , as shown in Fig. 4.

Whether  $v_S$  will decrease all the way to zero depends on the energy stored in inductor  $L_S$  at  $t=T_4$ . If this energy is larger than the energy required to discharge  $C_{oss}$  from  $V_O+V_C$  down to zero, i.e., if

$$\frac{1}{2}L_S[i_L(t=T_4)]^2 \ge \frac{1}{2}C_{oss}(V_O + V_C)^2 \tag{1}$$

then  $v_S$  will reach zero. Otherwise,  $v_S$  will not be able to fall to zero and will tend to oscillate around the  $V_O$  level if boost switch S is not turned on immediately after  $v_S$  reaches its minimum.

Assuming that inductor energy is more than enough to discharge  $C_{oss}$  to zero,  $v_S$  will reach zero at  $t=T_5$ , while inductor current  $i_{LS}$  is still negative. As a result, the antiparallel diode of S will start conducting as shown in Fig. 3(e). Because of the simultaneous conduction of the antiparallel diode of S and rectifier D, constant output voltage

$V_O$  is applied to inductor  $L_S$  so that inductor current  $i_{LS}$  increases linearly toward zero (Fig. 4). To achieve ZVS of switch S, it is necessary to turn on the transistor of switch S during the time interval  $[T_5 - T_6]$  when the antiparallel diode of S is conducting. If the transistor of S is turned on during this interval,  $i_{LS}$  will continue to increase linearly after  $t = T_6$ , as shown in Fig. 3(f). At the same time, rectifier current  $i_D$  will continue to decrease linearly. The rate of  $i_D$  decrease is determined by the value of  $L_S$  inductance because

$$\frac{di_D}{dt} = -\frac{V_O}{L_S}. (2)$$

To reduce the rectifier-recovered charge and the associated losses, a proper  $L_S$  inductance needs to be selected. Generally, a larger inductance, which gives a lower  $di_D/dt$  rate, results in a more efficient reduction of the reverse-recovery-associated losses [1].

The linear increase of  $i_{LS}$  should stop at  $t=T_7$  when  $i_{LS}$  reaches the input-current level  $I_{\rm in}$  and rectifier current  $i_D$  falls to zero (Fig. 4). However, due to the residual stored charge, rectifier current  $i_D$  starts flowing in the reverse direction, as

Fig. 5. Effect of junction capacitance of rectifier D: (a) topological stage of converter immediately after  $t = T_8$  ( $[T_8, T_9]$ ) and (b) rectifier voltage  $v_D$  and inductor current  $i_{LS}$  waveforms.

shown in Fig. 3(g), producing an overshot of the switch current over the  $I_{\rm in}$  level, as shown in Fig. 4. Without  $L_S$ , this reverserecovery current would be many times larger. Once the rectifier has recovered at  $t = T_8$ , the entire input current  $I_{in}$  flows through switch S [Fig. 3(h)] until the next switching cycle is initiated at  $t = T_9$ .

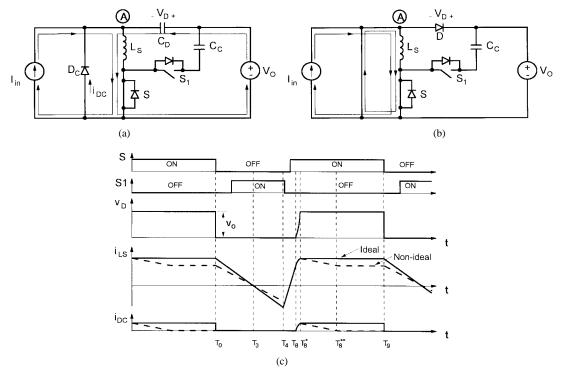

Besides the stored charge that needs to be recovered before a fast-recovery rectifier can block voltage, the rectifier possesses a junction capacitance. This capacitance was neglected in the previous analysis of operation. However, in a practical boost circuit, this undesirable, parasitic capacitance has a detrimental effect on the characteristics of the circuit because it increases the voltage stress of the rectifier [5]. As reported in [5], even with a heavy RCD snubber across the rectifier, the voltage stress of the rectifier is more than 600 V for a converter with a 400-V output. As a result, the implementation in [5] requires a rectifier with a higher voltage rating, which has a detrimental effect on the conversion efficiency and cost.

The junction capacitance of the rectifier affects the circuit operation after rectifier D in Fig. 2 has recovered at  $t=T_8$ (Fig. 4). Namely, after stored charge has been removed from D, junction capacitance  $C_D$  of D needs to be charged to the steady-state voltage  $V_O$ . However, because  $C_D$  and  $L_S$  form a series-resonant circuit, as shown in Fig. 5(a), the voltage across  $C_D$  (rectifier voltage) and the current trough  $L_S$  will resonate as shown in Fig. 5(b). The resonance is dampened by the on resistance of the MOSFET of switch S and losses in inductor  $L_S$ . The amplitudes of the voltage and current oscillations are given by

$$V_{D(nk)}^{osc} = V_O \tag{3}$$

$$V_{D(pk)}^{osc} = V_O$$

$$I_{L(pk)}^{osc} = \frac{V_O}{Z_n} = \frac{V_O}{\sqrt{L_S/C_D}}$$

$$(3)$$

where  $Z_n = \sqrt{L_S/C_D}$  is the characteristic impedance of the  $L_S$ - $C_D$  resonant circuit. Generally, the characteristic impedance is large because of a relatively small  $C_D$ , which is typically in a 10-pF range. As a result, the energy stored in the  $L_S$ - $C_D$  resonant circuit is also small. However, the resonance doubles the voltage stress of the rectifier because it pulls node A in Fig. 5(a) to  $-V_O$ .

The parasitic resonance of the  $L_S$ – $C_D$  circuit can be eliminated by clamping the voltage of node A to the ground by diode  $D_C$ , as shown in Fig. 6(a). In Fig. 6(a), when the voltage of node A reaches zero, i.e., when the reverse voltage on rectifier D reaches  $V_O$  at  $t = T_8^*$ , diode  $D_C$  clamps the voltage of node A to zero by taking over current flowing through  $L_S$ , as shown in Fig. 6(b). In an ideal (lossless) power stage, current  $i_{LS}$ , which circulates in the  $L_S$ - $D_C$  loop, will stay constant at the value given by (4) until the main switch is turned off at  $t = T_9$ , Fig. 6(c). However, in a practical converter, current  $i_{LS}$  will decay according to

$$di_{L}/dt = -\frac{[V_{F(DC)} + (R_{DS(on)} + R_{LS})i_{L}]}{L_{S}}$$

(5)

where  $V_{F(DC)}$  is the forward voltage drop of clamp diode  $D_C$ ,  $R_{DS(on)}$  is the on resistance of the MOSFET of switch S, and  $R_{LS}$  is the winding resistance of inductor  $L_S$ . Generally, the power dissipated during  $i_{LS}$  circulation through the  $L_{S}$ - $D_{C}$ loop is small because of a relatively small value of the circulating current. With diode  $D_C$ , the reverse voltage of main rectifier D is the same as in the "hard-switched" converter, i.e., it is equal to output voltage  $V_O$ .

## III. DESIGN CONSIDERATIONS

As described in the previous section, to achieve ZVS of switches S and S1, it is necessary to turn on the transistors of the switches during the intervals in which their antiparallel diodes are conducting. To make the antiparallel diode of S1conduct after switch S is turned off at  $t = T_O$  in Fig. 4, voltage  $v_S$  needs to increase to  $V_O + V_C$ . Since  $C_{oss}$  of switch S is charged through a series connection of a large boost inductor (represented by current source  $I_{\rm in}$ ) and inductor  $L_S$  (Fig. 1), there is a plenty of energy to charge  $C_{oss}$  up to  $V_O + V_C$ even for very low-input currents. However, to discharge  $C_{oss}$

Fig. 6. Elimination of junction-capacitance effect of rectifier D. (a) Topological stage of converter with clamp diode  $D_C$  during  $[T_8-T_8^*]$  interval ( $[T_8, T_8^*]$ ). (b) Topological stage of converter with clamp diode  $D_C$  during  $[T_8^*-T_8^{**}]$  interval ( $[T_8^*, T_9]$ ). (c) Rectifier voltage  $v_D$ , inductor current  $i_{LS}$ , and clamp-diode current  $i_{DC}$  waveforms.

to zero and subsequently achieve ZVS of switch S after S1is turned off ( $t = T_4$  in Fig. 4), only energy stored in  $L_S$  is available because the boost inductor current  $I_{\rm in}$  at  $t=T_4$ flows through rectifier D. According to (1), the energy in the inductor can be increased by increasing the inductance of  $L_S$  or inductor current  $i_L(t=T_4)$ . Since  $i_L(t=T_4)=$  $i_L(t=T_1)=I_{

m in}^*$  due to the required charge balance on clamp capacitor  $C_C$  and since  $i_L(t=T_1)=I_{\rm in}^*\approx I_{\rm in}$  if duration of the commutation interval  $[T_0-T_1]$  is short compared to the offtime interval  $[T_O-T_6]$ , the only design variable for the stored energy is  $L_S$ . The minimum  $L_S$  is determined from the desired  $di_D/dt$  rate to control the rectifier recovered charge according to (2). Therefore, to achieve ZVS at light loads, i.e., for small  $I_{in}$ , a relatively large value of  $L_S$  is required. If  $L_S$  is too large, the di/dt rate of the inductor current will be very slow, which will limit the maximum switching frequency and/or maximum output power. Therefore, in a practical design,  $L_S$  should be selected to be larger than the minimum  $L_S$  which gives the desired  $di_D/dt$  rate, but not too large to limit the switching frequency and/or maximum output power. Although, for such an  $L_S$  selection, no ZVS of S may be possible, the switching loss of S would be reduced because S would be turned on with a voltage lower than  $V_O + V_C$ .

To reduce the reverse-recovery-induced losses, the di/dt turn-off rate of the majority of today's fast-recovery rectifiers should be kept below 100 A/ $\mu$ s [1]. Generally, a greater reduction of the losses is obtained by reducing the rectifier's di/dt turn-off rate well below 100 A/ $\mu$ s. Moreover, slower rectifiers, i.e., those with longer reverse-recovery times, require slower di/dt turn-off rates than faster rectifiers to achieve the same level of reduction of the reverse-recovery-related

losses. In addition, since the speed of a rectifier depends on the magnitude of the forward current it conducts prior to the turn off, lower di/dt turn-off rates are required at higher conduction currents. Specifically, for boost converters delivering 1 kW or a lower power from a 400-Vdc output, the practical di/dt turn-off range is from 100 A/ $\mu$ s down to 20 A/ $\mu$ s. Therefore, according to (2), for a boost converter with a 400-Vdc output, the practical range of snubber inductance  $L_S$  is from 4 to 20  $\mu$ H.

As can be seen from Fig. 4, the voltage stresses of switches S and S1 are the same and equal to  $V_O + V_C$ . Compared to the "hard-switched" boost converter, the boost-switch stress in the proposed converter is higher for the amount of clamp voltage  $V_C$ . To keep the voltage stress of switches S and S1 within reasonable limits, it is necessary to select properly clamp-voltage level  $V_C$ .

From Fig. 4, it can be seen that during the time interval from  $t=T_1$  to  $t=T_3$ , current  $i_{LS}$  decreases linearly to zero because during this time interval clamp-capacitor voltage  $V_C$  appears across inductor  $L_S$ , as shown in Fig. 3(b). Since  $i_L(t=T_1)=I_{\rm in}^*\approx I_{\rm in}$  and the duration of the time interval  $[T_1-T_3]$  is approximately one half of the off time of main switch S, the relationship between clamp voltage  $V_C$  and inductor current  $i_{LS}$  can be expressed as

$$V_C = L_S \frac{I_{\rm in}}{(1-D)T_S/2} = \frac{2L_S f_S I_{\rm in}}{1-D}$$

(6)

where D is the duty cycle of main switch S,  $T_S$  is the switching period, and  $f_S$  is the switching frequency. Since for a lossless boost power stage

$$\frac{V_O}{V_{\rm in}} = \frac{I_{\rm in}}{I_O} = \frac{1}{1 - D}.$$

(7)

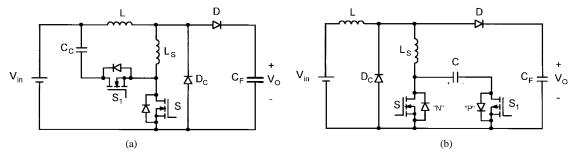

Fig. 7. Variations of boost converter implementations: (a) clamp circuit connected to input and (b) clamp circuit connected to ground.

Equation (6) can be expressed as

$$V_C = 2L_S f_S I_O \left(\frac{V_O}{V_{\rm in}}\right)^2. \tag{8}$$

According to (8),  $V_C$  is maximum at full load  $I_O^{\max}$  and low line  $V_{\mathrm{in}}^{\min}$ . Therefore, for given input and output specifications, i.e., for given  $I_O^{\max}$ ,  $V_{\mathrm{in}}^{\min}$ , and  $V_O$ , the clamp-capacitor voltage can be minimized by minimizing the  $L_S f_S$  product.

The peak-to-peak voltage ripple of the clamp capacitor  $\Delta V_C$  can be determined from the capacitor charging interval  $[T_1-T_3]$  as

$$\Delta V_C = \frac{1}{C_C} \int_{T_1}^{T_3} i_{LS} dt$$

$$= \frac{1}{C_C} \int_0^{[(1-D)/2]T_S} i_{LS} dt$$

$$= \frac{I_{\text{in}}(1-D)T_S}{4C_C}$$

$$= \frac{I_O}{4C_C f_S}$$

(9)

where the last expression in (9) is obtained by using relationship between  $I_{\rm in}$  and  $I_O$  given in (7). As can be seen from (9), the maximum voltage ripple occurs at full load current  $I_O^{\rm max}$ .

For proper operation of the circuit, the voltage ripple of the clamp capacitor should be kept below ten to 20% of maximum capacitor dc voltage  $V_C^{\rm max}$  calculated from (8) at low line  $V_{\rm in}^{\rm min}$  and full load  $I_O^{\rm max}$ , i.e.,

$$\Delta V_C = kV_C^{\text{max}} \tag{10}$$

where  $k \leq 0.2$ .

Substituting (8) and (9) in (10), the value of clamp-capacitor capacitance is obtained as

$$C_C = \frac{(V_{\text{in}}^{\text{min}})^2}{8kL_S f_S^2 V_O^2}.$$

(11)

Finally, in input-current-shaping applications, the input voltage of the boost power stage is the rectified line voltage, while the output voltage is a dc voltage greater than the peak of the line voltage. Due to the varying input voltage and constant output voltage, the duty cycle of a boost converter used in these applications varies in a wide range. It is maximum at close to 100% when line voltage is low (around zero), and it is minimum at the peak of the line voltage. However, when the line voltage is around zero, the energy in the boost inductor is small even with the switch duty cycle close to 100%. As a result, after switch S in Fig. 1 is turned off, the stored energy in the boost inductor is insufficient to charge

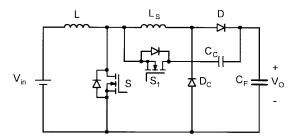

Fig. 8. Boost converter implementations with inductor  $L_S$  shifted from switch S branch (lead) to rectifier D branch (lead).

output capacitance  $C_{oss}$  of S up to  $V_O + V_C$  and conduct the antiparallel diode of auxiliary switch S1. Consequently, when the MOSFET of switch S1 is turned on, clamp capacitor  $C_C$ discharges to  $C_{oss}$ . Because  $C_C \gg C_{oss}$ ,  $C_C$  discharge is small during a switching cycle. However, the voltage of  $C_C$ can discharge significantly if the described conditions persist for many switching cycles. Since the proper operation of the circuit in Fig. 1 requires that clamp voltage  $V_C$  be always positive so that it can reset the core of  $L_S$ , voltage  $V_C$  must be prevented from becoming negative. To accomplish this, a diode (typically the Schottky type) may need to be added across clamp capacitor  $C_C$ . Finally, it should be noted that in input-current-shaping applications, the selection of the values of the snubber components  $L_S$  and  $C_C$  is also done using (8) and (11) with the dc low-line input voltage replaced by the peak low-line ac voltage.

# IV. TOPOLOGY VARIATIONS

Generally, the series connection of auxiliary switch S1 and clamp-capacitor  $C_C$  can be connected to any dc-voltage point in the circuit. As a result, the proposed technique for reduction of the reverse-recovery-related losses can be incorporated in a number of different ways. Fig. 7(a) shows the implementation with the clamp circuit connected to the input, whereas Fig. 7(b) shows the implementation with the clamp circuit connected to the ground. Both implementations in Fig. 7 control the reverse-recovery-related losses by controlling the  $di_D/dt$  rate of rectifier D in the same fashion as the implementation in Fig. 1. However, the implementation in Fig. 7(a) returns the energy of inductor  $L_S$  to the input and also reduces the current stress of the filter capacitor  $C_F$  because current  $i_{LS}$  does not flow through  $C_F$ .

The implementation in Fig. 7(b) uses a P-type MOSFET for auxiliary switch. Since this MOSFET is referenced to the

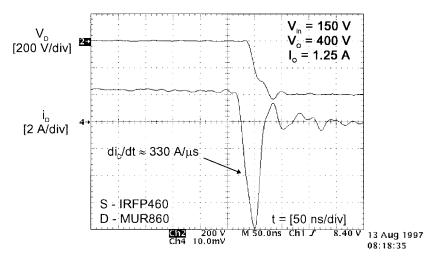

Fig. 9. Measured boost-rectifier current and voltage waveforms of experimental converter with MUR860 rectifier and without active snubber at  $P_O = 500$  W and  $V_{\rm in} = 150$  Vdc.

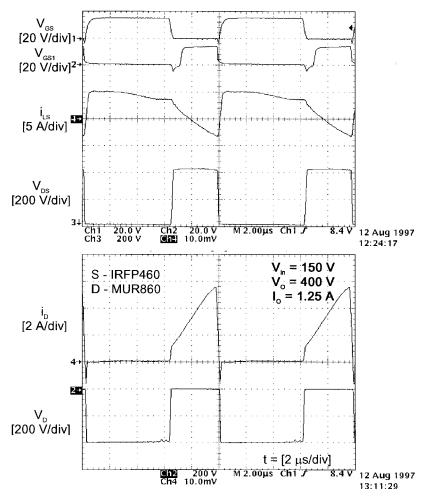

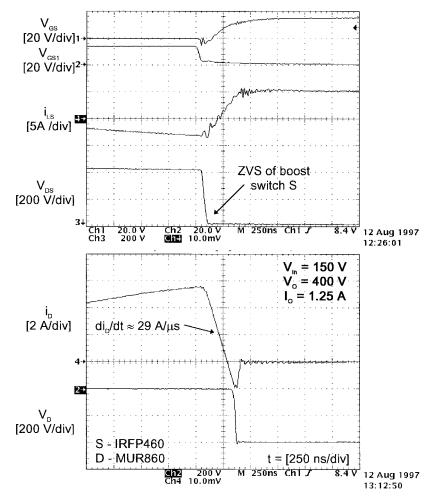

Fig. 10. Measured key waveforms of experimental converter with MUR860 rectifier and with active snubber at  $P_O = 500$  W and  $V_{\rm in} = 150$  Vdc.

ground, a nonisolated gate drive can be used for both switches. However, this implementation requires a clamp capacitor with a substantially higher voltage rating than the implementations in Figs. 1 and 7(a). Namely, if the maximum voltage across capacitor  $C_C$  in N-type MOSFET implementations in Figs. 1

and 7(a) is  $V_C$ , the corresponding voltage in the P-type implementation in Fig. 7(b) is  $V_C + V_C$ .

Fig. 8 shows the boost converter implementation with inductor  $L_S$  in the rectifier D branch (lead) instead of in the switch S branch (lead) as in Fig. 1. The operation of this

Fig. 11. Waveforms of Fig. 10 shown on expanded time base.

circuit is the same as that of Fig. 1 except that inductor current  $i_{LS}$  is the same as rectifier current  $i_D$  (when D is conducting) instead of being the same as  $i_S$  (when S is conducting), as in the circuit in Fig. 1. The circuit in Fig. 8 can also be implemented with the clamp circuit connected to the input or ground, as in Fig. 7.

## V. EXPERIMENTAL RESULTS

To verify the operation and evaluate the performance of the proposed technique, a 500-W (400-V/1.25-A) 100-kHz prototype dc–dc converter for an input-voltage range from 120 to 350 Vdc was built using the following components: switch S—IRFP460 (Harris); rectifier D—MUR860 (Motorola) or RHRP860 (Harris); auxiliary switch S1—BUZ80A (Motorola); boost inductance L=0.475 mH (Philips 783E-608 core, 3F3 material, 4-mm gap, 80 turns of AWG#17); snubber inductance  $L_S=14~\mu{\rm H}$  (Micrometal T106-2 toroidal core, 31 turns of AWG#17), and clamp capacitance  $C_C=2\times0.47~\mu{\rm F}/400~{\rm V}$  (polypropylene); and output filter capacitance with the UC3842 IC PWM controller and the Harris HIP2500 driver which is used to provide the proper gate-drive signals for the main and auxiliary switches.

With the selection of  $L_S=14~\mu\mathrm{H}$ , the di/dt turn-off rate of the boost rectifier was limited to  $di_D/dt=V_O/L_S=400$

V/14  $\mu H = 29$  A/ $\mu s$ . Similarly, by selecting  $C_C = 0.94$   $\mu F$ , the peak-to-peak ripple of the clamp-capacitor voltage was 3.3 V, which is less than 10% of  $V_C^{\rm max} \approx 40$  V at low line ( $V_{\rm in}^{\rm min} = 120$  Vdc) and full load ( $I_O^{\rm max} = 1.25$  Adc).

The measured boost-rectifier current and voltage waveforms of the experimental circuit, at full power and  $V_{\rm in}=150$  Vdc, for the implementation with the MUR860 rectifier and without the active snubber ( $L_S$ ,  $S_1$ , and  $C_C$  removed from the circuit) are shown in Fig. 9. As can be seen from Fig. 9, the di/dt turn-off rate of the rectifier is approximately 330 A/ $\mu$ s, whereas its peak reverse-recovery current is 8 A.

Fig. 10 shows the measured key waveforms of the experimental circuit with the active snubber at full power and  $V_{\rm in}=150$  Vdc, whereas Fig. 11 shows the same waveforms on an expanded time scale. From the  $i_D$  waveform in Fig. 11, it can be seen that at turn on, the peak reverse-recovery current of the rectifier is reduced to approximately 2 A. Also, from the  $V_{DS}$  waveform, it can be seen that the switch is turned on at zero voltage. The maximum voltage of the main switch is approximately 425 V, implying that the clamp-capacitor voltage at  $V_{\rm in}=150$  Vdc is approximately 25 V. It also should be noted that rectifier voltage waveform  $v_D$  is ringing free because of the effective clamping action of clamp diode  $D_C$ . As a result, the maximum reverse voltage across rectifier D is equal to the output voltage, i.e., 400 V. Generally, due to the

#### **EFFICIENCY [%]** with active RHRP860 99 snubber 98 97 96 **MUR860** 95 94 Vo = 400 Vdc w/o active lo = 1.25 Ado 93 snubber Po = 500 W 92 100 175 200 225 250 275 300 325 350 125 150 INPUT VOLTAGE [Vdc]

Fig. 12. Measured full-power efficiencies of experimental converter with (solid lines) and without (dashed lines) active snubber as functions of output power for implementations with MUR860 and RHRP860 rectifiers.

absence of ringings and abrupt transitions in the semiconductor voltage and current waveforms, the conducted electromagnetic interference (EMI) performance of the converter is expected to be improved, as documented in [10].

The solid lines in Fig. 12 show the measured efficiencies of the experimental, boost power stage at full power as functions of the input voltage for implementations with two rectifiers with different reverse-recovery characteristics. The RHRP860 (Harris) rectifier exhibits a faster reverse-recovery characteristic than the MUR860 (Motorola) rectifier. For comparison purposes, Fig. 12 shows the measured efficiencies for the two rectifiers without the active snubber (dashed lines). As can be seen from Fig. 12, without the active snubber, the efficiency of the implementation with the MUR860 rectifier is the lowest, ranging from 92.4% at low line to 98% at high line. The corresponding efficiency of the implementation with the faster RHRP860 rectifier is slightly higher, i.e., it is in the 94.2%–98.3% range. For both implementations, the efficiency at low line, where the input current is maximum, is the lowest because the reverse-recovery-related losses as well as conduction losses of components are the highest. With the active snubber, the efficiencies of both implementations are significantly improved (96%-99% range). Moreover, the differences between the efficiencies with the two rectifiers are less than 0.4% throughout the entire input-voltage range. In fact, with the active snubber, the effect of the reverse-recovery speed of the rectifier on the efficiency is practically eliminated.

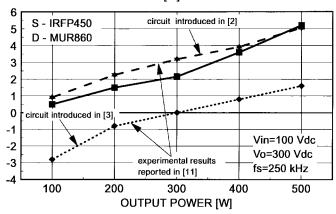

Finally, Fig. 13 presents the comparisons of the efficiency improvements of the boost circuit with the active snubber shown in Fig. 1, the boost circuit proposed in [2], and the boost circuit proposed in [3] with respect to the efficiency of the conventional "hard-switched" boost converter. The experimental data for the circuits proposed in [2] and [3] (dashed lines) were taken from [11]. Since the experimental data reported in [11] were measured at  $V_{\rm in}=100$  Vdc for the boost converters operating at the switching frequency of 250 kHz and with  $V_O=300$  Vdc, the experimental converter with the active snubber was redesigned to operate under the same conditions so that a direct performance comparison could be performed. Specifically, to achieve a 250-kHz operation

## **EFFICIENCY IMPROVEMENT [%]**

Fig. 13. Comparisons of efficiency improvements of proposed boost circuit with active snubber (solid line), boost circuit proposed in [2], and boost circuit proposed in [3] with respect to efficiency of conventional "hard-switched" boost converter. Experimental data for circuits proposed in [2] and [3] (dashed lines) were taken from [11].

of the boost converter with the active snubber in the full power range from 100 to 500 W at  $V_{\rm in} = 100$  Vdc, snubber inductance  $L_S$  had to be decreased to approximately 6  $\mu$ s by decreasing the number of turns from 31 to 21 ( $L_S$ —Micrometal T106-2 toroidal core, 21 turns of AWG#17). In addition, to use the same type semiconductor devices as in [11], in the 250-kHz implementation of the experimental circuit with the active snubber, a IRFP450 MOSFET was used for the boost switch, and a MUR860 diode was used for the boost rectifier. Furthermore, to minimize the errors between the efficiency measurements reported in [11] and the measured efficiencies of the boost converter with the active snubber due to measurement-equipment differences, the efficiency comparisons presented in Fig. 13 were done on a relative basis. As can be seen from Fig. 13, the efficiency performance of the boost converter with the active snubber (solid line) is similar to that of the circuit introduced in [2]. Namely, at full power of  $P_O = 500$  W, the boost converter with the active snubber and the circuit proposed in [2] show approximately the same efficiency improvement of around 5%, although at lower power levels, the circuit introduced in [2] operates with slightly higher efficiencies. The efficiency improvement of the boost circuit introduced in [3] is significantly lower than the corresponding efficiency improvements of the circuit introduced in [2] and the boost converter with active snubber. In fact, for the output power levels below 300 W, the efficiency of the circuit in [3] is less than the efficiency of the corresponding "hard-switched" converter. Finally, it should be noted that the measured results for the boost converter with the active snubber presented in Fig. 13 can be also used for comparisons with other softswitched boost circuits discussed in [11].

## VI. SUMMARY

Operation and design guidelines for an active-snubber technique which reduces the reverse-recovery-related losses in high-voltage high-power boost converters are presented. The technique employs a snubber inductor connected in series with

the boost switch and rectifier to control the di/dt rate of the rectifier current during its turn off. The energy from the snubber inductor after the boost switch turn off is returned to the input or delivered to the output via the active snubber. By connecting a clamp diode between the anode of the boost rectifier and ground to eliminate the parasitic ringing between the junction capacitance of the rectifier and the snubber inductor, the stress of the rectifier is minimized. The proposed technique was verified on a 500-W (400-V/1.25-A) prototype boost converter.

## ACKNOWLEDGMENT

The author wishes to thank Dr. Y. Jang of Delta Power Electronics Laboratory for his help in collecting a part of the experimental data.

#### REFERENCES

- Y. Khersonsky, M. Robinson, and D. Gutierrez, "New fast recovery diode technology cuts circuit losses, improves reliability," *Power Conversion & Intelligent Motion (PCIM) Magazine*, vol. 18, no. 5, pp. 16–25, May 1992.

- [2] R. Streit and D. Tollik, "High efficiency telcom rectifier using a novel soft-switched boost-based input current shaper," in *Int. Telecommunica*tion Energy Conf. (INTELEC) Proc., Oct. 1991, pp. 720–726.

- [3] G. Hua, C. S Leu, and F. C. Lee, "Novel zero-voltage-transition PWM converters," in *IEEE Power Electronics Specialists' Conf. (PESC) Rec.*, June 1992, pp. 55–61.

- June 1992, pp. 55–61.

[4] J. Bassett, "New, zero voltage switching, high frequency boost converter topology for power factor correction," in *Int. Telecommunication Energy Conf. (INTELEC) Proc.*, 1995, pp. 813–820.

- Conf. (INTELEC) Proc., 1995, pp. 813–820.

[5] C. M. C. Duarte and I. Barbi, "A new family of ZVS-PWM active-clamping dc-to-dc boost converters: Analysis, design, and experimentation," in Int. Telecommunication Energy Conf. (INTELEC) Proc., 1996, pp. 305–312.

- [6] K. Harada and H. Sakamoto, "Switched snubber for high frequency switching," in *IEEE Power Electronics Specialists' Conf. (PESC) Rec.*, June 1990, pp. 181–188

- June 1990, pp. 181–188.

[7] P. Vinciarelli, "Optimal resetting of the transformer's core in single ended forward converters," U.S. Patent 4441146, Apr. 3, 1984.

- [8] B. Carsten, "Design techniques for transformer active reset circuits at high frequencies and power levels," in *High Frequency Power Conversion (HFPC) Conf. Proc.*, 1990, pp. 235–246.

- Conversion (HFPC) Conf. Proc., 1990, pp. 235–246.

[9] R. Watson, F. C. Lee, and G. C. Hua, "Utilization of an active-clamp circuit to achieve soft switching in flyback converters," *IEEE Trans. Power Flectron*, vol. 11, pp. 162–169, 1996.

- Power Electron., vol. 11, no. 1, pp. 162–169, 1996.

[10] M. van der Berg and J. A. Ferreira, "A family of low EMI, unity power factor correctors," in IEEE Power Electronics Specialists' Conf. (PESC) Rec., June 1996, pp. 1120–1127.

[11] K. M. Smith and K. M. Smedley, "A comparison of voltage mode

- [11] K. M. Smith and K. M. Smedley, "A comparison of voltage mode soft switching methods for PWM converters," in *IEEE Applied Power Electronics Conf. (APEC) Proc.*, Mar. 1996, pp. 291–298.

Milan M. Jovanović (S'86-M'89-SM'89), for a photograph and biography, see this issue, p. 834.