## University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

5-2020

# A Novel Three-Level Isolated AC-DC PFC Power Converter Topology with Reduced Number of Switches

Obaid Aldosari University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Geometry and Topology Commons, and the Power and Energy Commons

## Citation

Aldosari, O. (2020). A Novel Three-Level Isolated AC-DC PFC Power Converter Topology with Reduced Number of Switches. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3592

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

## A Novel Three-Level Isolated AC-DC PFC Power Converter Topology with Reduced Number of Switches

## A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Obaid Aldosari Western Michigan University Bachelor of Science in Electrical Engineering, 2013 Western Michigan University Master of Science in Electrical Engineering, 2014

> May 2020 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

Juan C. Balda, Ph.D. Dissertation Director

Zhao Yue, Ph.D. Committee Member Roy A. McCann, Ph.D. Committee Member

Mark E. Arnold, Ph.D. Ex-officio Member

#### ABSTRACT

The three-level isolated AC-DC power factor corrected (PFC) converter provides safe and more efficient power conversion. In comparison with two-level, three-level PFC converter has the advantages of low total harmonic distortion, low device voltage rating, low  $d_i/d_t$ , better output performance, high power factor, and low switching losses at higher switching frequencies. The high frequency transformer (HFT) grants galvanic isolation, steps up or down secondary voltage, and limits damage in case of a fault current.

The existing three-level converter based on solid-state transformer (SST) topologies convert ac power from the electrical grid to a dc load while maintaining at least the minimum requirements set by the international standards (i.e., high power factor and low total harmonic distortion). The SST topologies with the capability of controlling intermediate dc-bus and output voltage simultaneously require two full bridges at the primary and secondary side of the HFT. As the power level increases, the number of cascaded bridges increases accordingly, and the price associated with these semiconductor devices becomes highly expensive. As result, the demand of converting high power level led to emphasis on high performance and cost-effective power conversion topology.

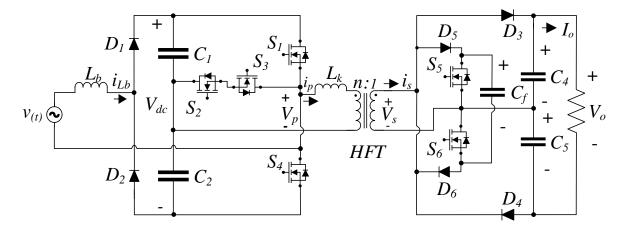

The aim of this dissertation is to develop a new low-cost and high-performance three-level isolated AC-DC (PFC) converter topology. The proposed topology replaces the conventional three-level inverter in the secondary side of the HFT by only two switches and four diodes while still maintaining the basic functionality of a three-level converter (i.e., regulating the output voltage, controlling the dc-bus voltage to be within desired limits). The advantages of this new topology are: (1) low conduction losses; (2) low-cost; (3) no need to consider the issue of the

power backflow; (4) zero-voltage switching (ZVS) and zero-current switching (ZCS) at turn ON are inherently guaranteed without any extra control effort.

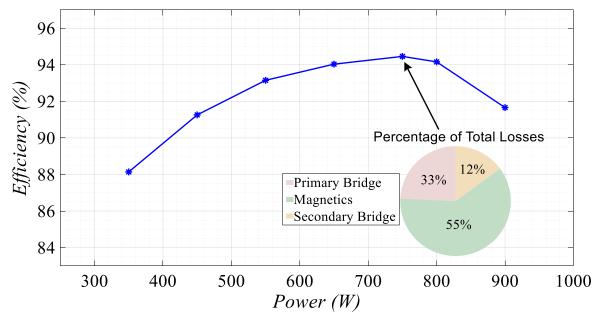

Two isolated three-level AC-DC power converter topologies are developed and investigated through the dissertation. First topology is based on the neutral point clamping (NPC) converter, and the second topology composed of the T-type converter. Two scale-down prototypes rated at 900-W and 1kW, 200 V are built to test the overall performance of the proposed topologies. The first and second topologies exhibit 94.5 % and 95.8 % efficiency scaled at a nominal power, respectively. The secondary bridge (novel circuit) in both topologies, which consists of two switches and four diodes, has 99.34 % practical efficiency.

© 2020 Obaid Aldosari All Rights Reserved

#### ACKNOWLEDGMENTS

I would like to acknowledge everyone who support my academic accomplishments. First, and foremost, I would like to thank Prof. Juan C. Balda, for his expertise, guidance, assistance, and contributions to my research work. Thank you, Prof. Balda, for given me the chance to work in your lab and thank you for your financial support. Without your help, this dissertation would not have been possible.

Besides my advisor, I would like to thank the rest of my dissertation committee members, Dr. Roy A. McCann, Dr. Yue Zhao, and Dr. Mark E. Arnold for valuable suggestions and helpful conversation during my Ph.D. years of study.

I thank all my fellow labmates in ENRC 1961: special thanks go to Luciano Garcia, Vinson Jones, Dr. Oggier German, David Carballo Rojas, Edgar Escala, and Waleed Alhosaini for their help and support.

Finally, and most importantly, I would like to thank my beloved wife Najla Aldawsari, and my kids Joory, Muhammad, Umar, Leen for their full support during my Ph.D. journey.

## DEDICATION

This dissertation is dedicated to my parents, Martha Aldosari and Haia Aldosari. You have been with me in every step of the way, through good and bad ones. Thank you for the unconditional love, guidance, and support you have given me.

| Chapter 1                                                                                                                     | 1       |

|-------------------------------------------------------------------------------------------------------------------------------|---------|

| INTRODUCTION AND BACKGROUND                                                                                                   | 1       |

| 1.1 Solid-State Transformer Converter Background                                                                              | 1       |

| 1.2 Existing Isolated Single-Phase AC-DC (PFC) Topologies                                                                     | 2       |

| 1.2.A Two-Level Topologies                                                                                                    |         |

| 1.2.B Three-Level Topologies                                                                                                  | 5       |

| 1.3 Research Focus and Objectives                                                                                             | 9       |

| 1.4 Proposed Isolated Single-Phase AC-DC PFC Topologies                                                                       | 10      |

| 1.4.A Proposed Topology Based on NPC Inverter                                                                                 |         |

| 1.4.B Proposed Topology Based on T-type Inverter                                                                              |         |

| 1.5 High Frequency Transformer Design                                                                                         |         |

| 1.5.A Conventional Design                                                                                                     | 14      |

| 1.5.B Proposed Design                                                                                                         | 15      |

| 1.6 Organization of This Dissertation                                                                                         | 16      |

| 1.7 References                                                                                                                | 17      |

| Chapter 2                                                                                                                     |         |

| NEW ISOLATED AC-DC POWER CONVERTER TOPOLOGY WITH REDUCE<br>OF SWITCHES FOR HIGH-INPUT VOLTAGE AND HIGH-OUTPUT<br>APPLICATIONS | CURRENT |

| Abstract                                                                                                                      |         |

| 2.1 Introduction                                                                                                              |         |

| 2.2 Proposed Topology                                                                                                         |         |

| 2.2.A Circuit Configuration                                                                                                   |         |

| 2.2.B Steady-State Waveforms                                                                                                  |         |

| 2.2.C Operational Principles                                                                                                  |         |

| 2.3 Existing AC-DC Converters vs Proposed Topology Comparison                                                                 |         |

| 2.3.A Topology #1                                                                                                             |         |

| 2.3.B Topology #2                                                                                                             |         |

| 2.3.C Proposed Topology                                                                                                       |         |

| 2.4 Simulation and Experimental Results                                                                                       |         |

| 2.4.A Simulation Results for a Case-Study                                                                                     |         |

| 2.4.B Scaled-Down Prototype                                                                                                   |         |

## TABLE OF CONTENTS

| 2.5 Conclustions                                                                            | 40 |

|---------------------------------------------------------------------------------------------|----|

| 2.6 References                                                                              |    |

| APPENDIX 2.A                                                                                | 44 |

| Chapter 3                                                                                   |    |

| A THREE-LEVEL ISOLATED AC-DC PFC POWER CONVERTER TOPOLOG<br>REDUCED NUMBER OF SWITCHES      |    |

| Abstract                                                                                    |    |

| 3.1 Introduction                                                                            |    |

| 3.2 Proposed Isolated AC-DC Topology                                                        | 49 |

| 3.2.A Circuit Configuration                                                                 |    |

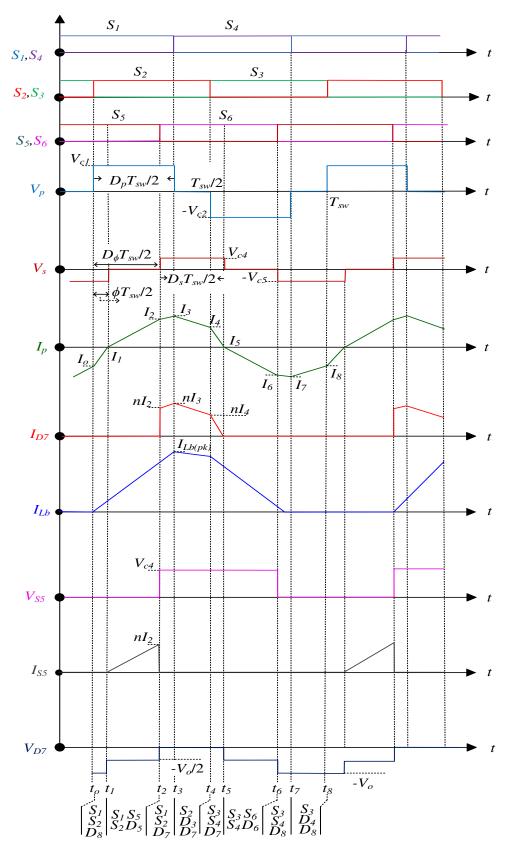

| 3.2.B Steady-State Waveforms                                                                | 49 |

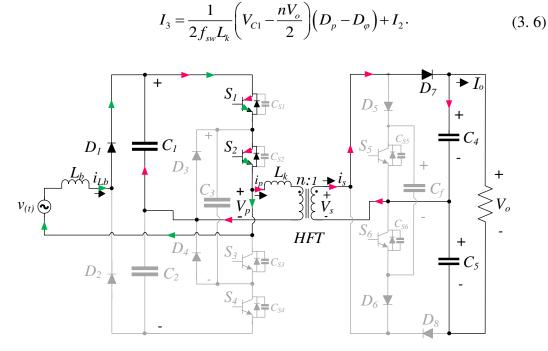

| 3.2.C Operational Principles                                                                | 52 |

| 3.3 Soft-Switching Analysis                                                                 | 59 |

| 3.3.A Primary-Side Switches                                                                 | 59 |

| 3.3.B Secondary-Side Switches                                                               | 60 |

| 3.4 Converter Design Procedure                                                              |    |

| 3.4.A Boost Inductor Design                                                                 |    |

| 3.4.B DC-Bus Capacitor Selection                                                            |    |

| 3.4.C High-Frequency Transformer Design                                                     | 64 |

| 3.4.D Output Capacitor Selection                                                            | 66 |

| 3.5 Simulation and Experimental Results                                                     | 67 |

| 3.5.A Simulation Results for Case Study                                                     | 67 |

| 3.5.B Scaled-Down Prototype                                                                 | 73 |

| 3.6 Conclusions                                                                             | 79 |

| 3.7 References                                                                              | 80 |

| APPENDIX 3.A                                                                                |    |

| Chapter 4                                                                                   |    |

| A BOOST-BASED T-TYPE PFC UNIDIRECTIONAL SOLID-STATE TRANSFORMEDIUM-LEVEL POWER APPLICATIONS |    |

| Abstract                                                                                    |    |

| 4.1 Introduction                                                                            | 84 |

| 4.2 Steady-State Analysis                                                                   | 87 |

| 4.2.A Steady-State Waveforms                                                                |    |

| 4.2.B Steady-State Operational Principles                                                   | 89 |

|                                                                                             |    |

| 4.2.C Output Power and DC-Bus Calculations                                                                                   |     |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3 Soft-Switching Analysis                                                                                                  |     |

| 4.3.A Primary Switches                                                                                                       | 99  |

| 4.3.B Secondary Switches                                                                                                     | 100 |

| 4.4 Converter Losses                                                                                                         | 100 |

| 4.4.A Conduction Losses                                                                                                      | 100 |

| 4.4.B Switching Losses                                                                                                       | 103 |

| 4.5 Experimental Results                                                                                                     | 104 |

| 4.6 Conclusion                                                                                                               | 110 |

| 4.7 References                                                                                                               | 111 |

| APPENDIX 4.A                                                                                                                 | 114 |

| Chapter 5                                                                                                                    | 115 |

| DESIGN TRADE-OFFS FOR MEDIUM- AND HIGH-FREQUENCY TRANSFORME<br>ISOLATED POWER CONVERTERS IN DISTRIBUTION SYSTEM APPLICATIONS |     |

| Abstract                                                                                                                     | 115 |

| 5.1 Introduction                                                                                                             | 116 |

| 5.2 Materials Suitable for High-Power MFTs/HFTs                                                                              | 117 |

| 5.2.A Core Material Review                                                                                                   | 117 |

| 5.2.B Temperature Rise Considerations                                                                                        | 118 |

| 5.3 Design Methodology for High-Power MFTs/HFTs                                                                              | 121 |

| 5.3.A Magnetizing and Leakage Inductance Requirements                                                                        | 121 |

| 5.3.B MFTs/HFT Design Steps                                                                                                  | 123 |

| 5.4 High-Power Case Study Design Results                                                                                     | 127 |

| 5.5 HFT Scale-Down Prototype and Results                                                                                     | 128 |

| 5.6 Conclusions                                                                                                              | 134 |

| ACKNOWLEDGMENTS                                                                                                              | 134 |

| 5.7 References                                                                                                               | 135 |

| APPENDIX 5.A                                                                                                                 | 137 |

| Chapter 6                                                                                                                    | 138 |

| RESEARCH CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE WORK                                                                     | 138 |

| 6.1 Research Conclusions                                                                                                     | 138 |

| 6.2 Recommendations for Future Work                                                                                          | 142 |

| 6.3 References                                                                                                               | 142 |

## LIST OF FIGURES

| Figure 1.1: Solid-State Transformer (SST) configuration.    2                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Classification of two-level isolated AC-DC PFC converter family                                                                                                                                                                                                                                 |

| Figure 1.3: Isolated buck forward AC-DC converter                                                                                                                                                                                                                                                           |

| Figure 1.4: Network representation of isolated three-level AC-DC power converter                                                                                                                                                                                                                            |

| Figure 1.5: Isolated three-level AC-DC power converter with minimum power devices [1.32] 7                                                                                                                                                                                                                  |

| Figure 1.6: Boost-based three-level SST topology [1.33]                                                                                                                                                                                                                                                     |

| Figure 1.7: Proposed three-level isolated AC-DC PFC topology based on NPC inverter                                                                                                                                                                                                                          |

| Figure 1.8: Proposed three-level isolated AC-DC PFC topology based on T-type inverter 12                                                                                                                                                                                                                    |

| Figure 1.9: Ideal electrical transformer and induction law representation                                                                                                                                                                                                                                   |

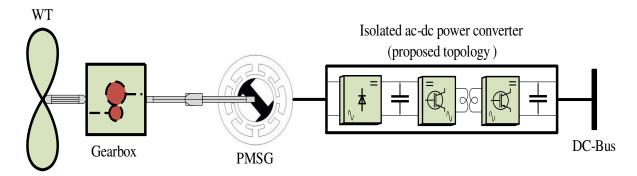

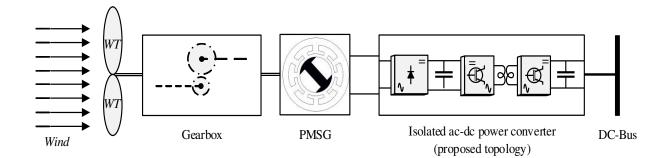

| <b>Figure 2.1</b> : Type 4 wind turbine configuration, wind turbine blades, gearbox, PMSG, ac-dc power converter, and DC-bus                                                                                                                                                                                |

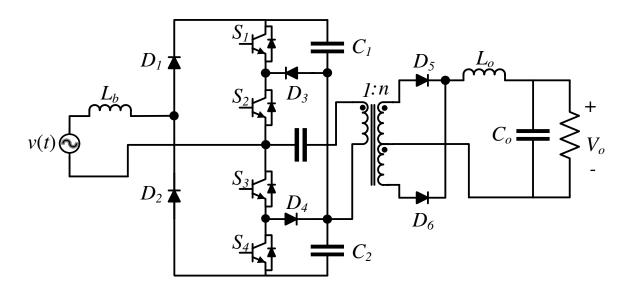

| Figure 2.2: Proposed isolated ac-dc power converter topology                                                                                                                                                                                                                                                |

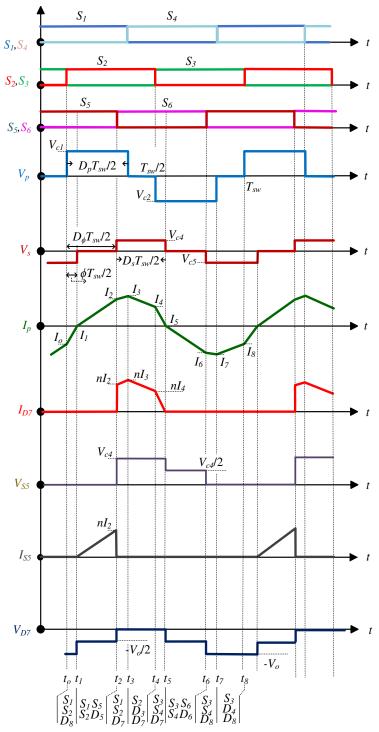

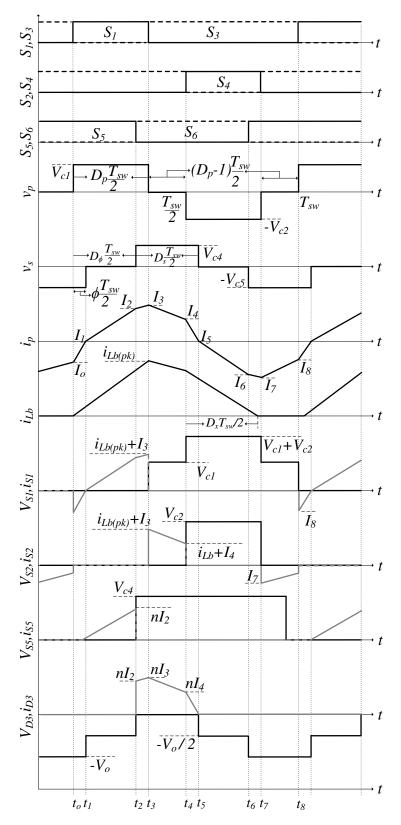

| Figure 2.3: Steady-state waveforms of the proposed topology                                                                                                                                                                                                                                                 |

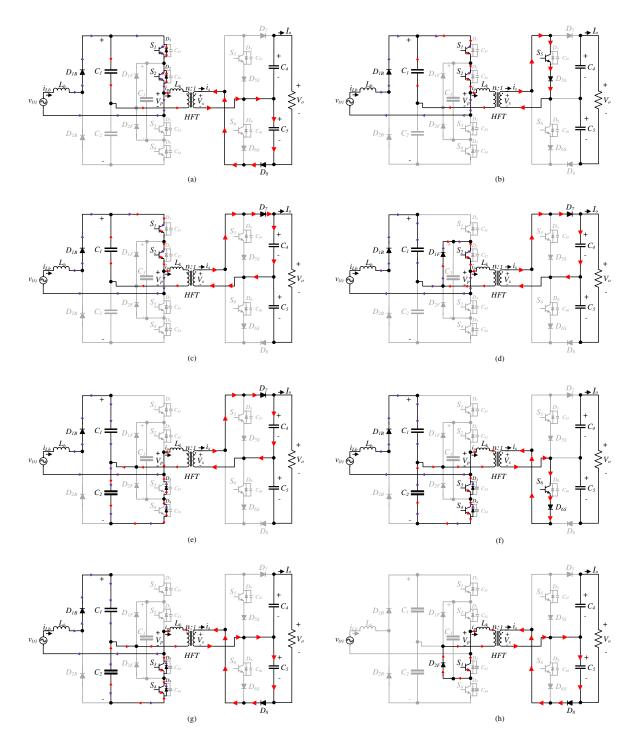

| <b>Figure 2.4</b> : Steady-state equivalent operating circuits of the proposed topology, (a) $[t_0-t_1]$ Interval, (b) $[t_1-t_2]$ Interval, (c) $[t_2-t_3]$ Interval, (d) $[t_3-t_4]$ Interval, (e) $[t_4-t_5]$ Interval, (f) $[t_5-t_6]$ Interval, (g) $[t_6-t_7]$ Interval, and (h) $[t_7-t_8]$ Interval |

| Figure 2.5: Topology #1 bidirectional ac-dc power converter                                                                                                                                                                                                                                                 |

| <b>Figure 2.6</b> : Topology #2 unidirectional ac-dc power converter                                                                                                                                                                                                                                        |

| <b>Figure 2.7</b> : Proposed topology connected in series (high side) and in parallel (low side) for high power applications                                                                                                                                                                                |

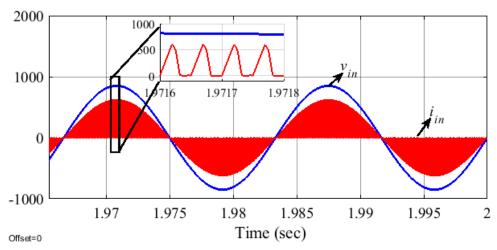

| Figure 2.8: Input voltage and current from the wind turbine                                                                                                                                                                                                                                                 |

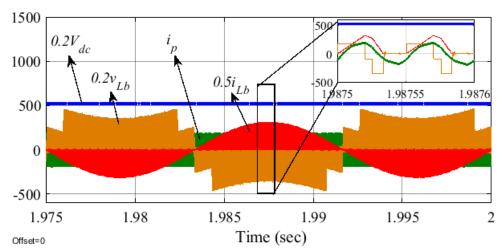

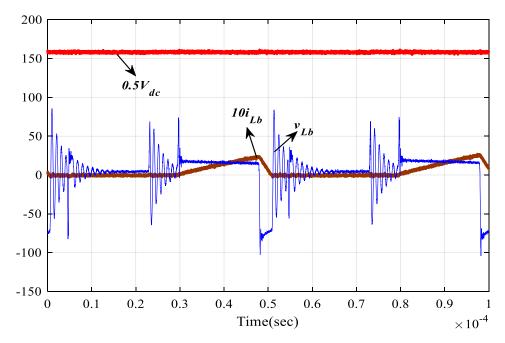

| <b>Figure 2.9</b> : Simulations waveforms of the dc-bus voltage $V_{dc}$ , boost inductor (voltage $v_{Lb}$ , current $i_{Lb}$ ) primary current $i_p$            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

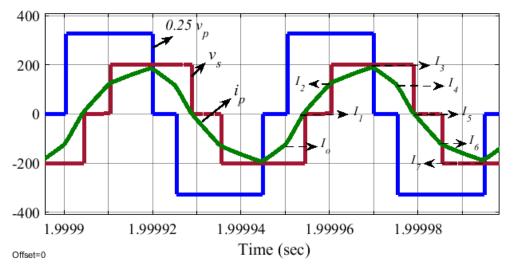

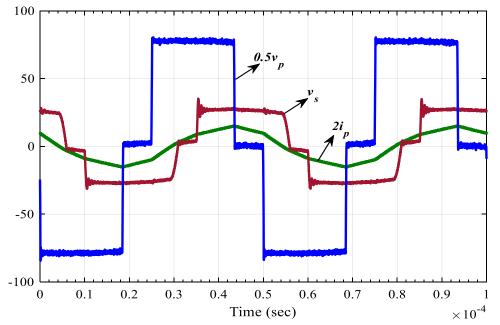

| <b>Figure 2.10</b> : Simulated waveforms of the transformer primary-side voltage $v_p$ , secondary-side voltage $v_s$ , and primary current $i_p$                 |

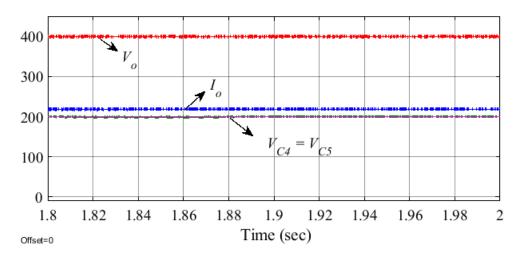

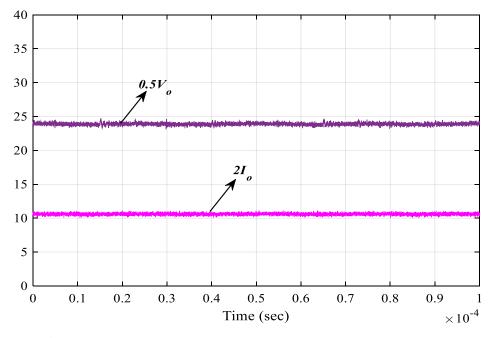

| <b>Figure 2.11</b> : Output voltage $V_o$ , output current $I_o$ , capacitors voltages $V_{c4}$ , and $V_{c5}$                                                    |

| <b>Figure 2.12</b> : Topology high-side dc-bus voltage (red), boost inductor current (brown), and boost inductor voltage (blue)                                   |

| Figure 2.13: Primary voltage (blue), secondary voltage (brown), and primary current (green). 40                                                                   |

| Figure 2.14: Output voltage (purple), and output current (pink)                                                                                                   |

| Figure 3.1: Proposed isolated ac-dc power converter topology                                                                                                      |

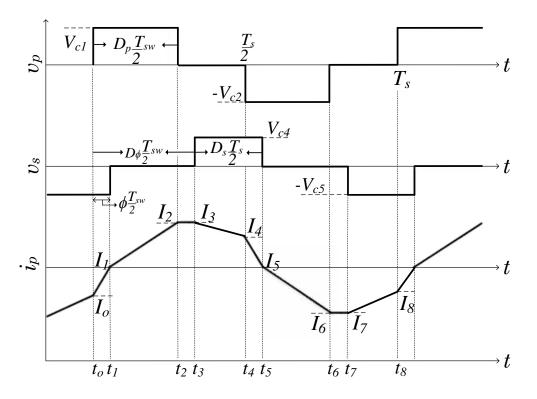

| Figure 3.2: Steady-state waveforms of the proposed topology                                                                                                       |

| <b>Figure 3.3</b> : [ <i>t</i> <sub>0</sub> - <i>t</i> <sub>1</sub> ] Interval, steady-state equivalent operating circuits of the proposed topology. 52           |

| <b>Figure 3.4</b> : $[t_1-t_2]$ Interval, steady-state equivalent operating circuit of the proposed topology. 53                                                  |

| <b>Figure 3.5</b> : $[t_2-t_3]$ Interval, steady-state equivalent operating circuits of the proposed topology. 54                                                 |

| <b>Figure 3.6</b> : [ <i>t</i> <sub>3</sub> - <i>t</i> <sub>4</sub> ] Interval, steady-state equivalent operating circuits of the proposed topology. 55           |

| Figure 3.7: [ <i>t</i> <sub>4</sub> - <i>t</i> <sub>5</sub> ] Interval, steady-state equivalent operating circuits of the proposed topology. 56                   |

| Figure 3.8: [t5-t6] Interval, steady-state equivalent operating circuits of the proposed topology. 57                                                             |

| Figure 3.9: [t <sub>6</sub> -t <sub>7</sub> ] Interval, steady-state equivalent operating circuits of the proposed topology. 58                                   |

| <b>Figure 3.10</b> : [ <i>t</i> <sub>7</sub> - <i>t</i> <sub>8</sub> ] Interval, steady-state equivalent operating circuits of the proposed topology. 58          |

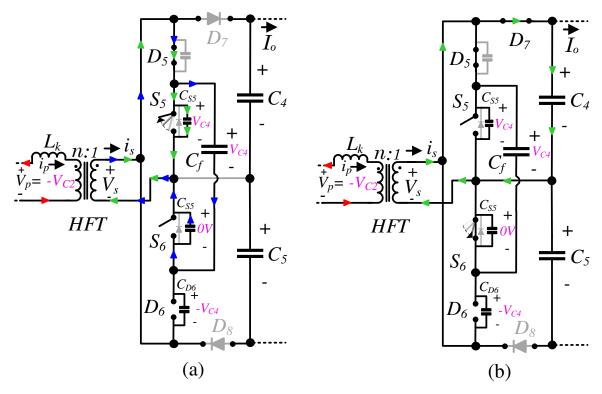

| <b>Figure 3.11</b> : Equivalent secondary side circuit showing charging and discharging $C_{S5}$ and $C_{S6}$ . (a) At turning $S_5$ OFF, (b) at turning $S_6$ ON |

| Figure 3.12: Simulation waveforms of the soft-switched proposed topology (secondary side) 63                                                                      |

| <b>Figure 3.13</b> : Type-4 wind turbine configuration, wind turbine blades, gearbox, PMSG, ac-dc power converter, and DC-bus                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

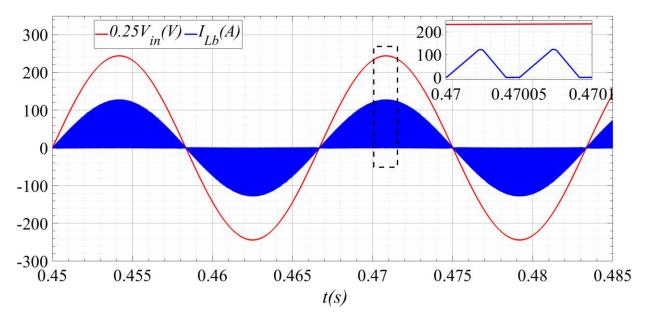

| Figure 3.14: Simulation waveforms of the input voltage and current                                                                                                                                                              |

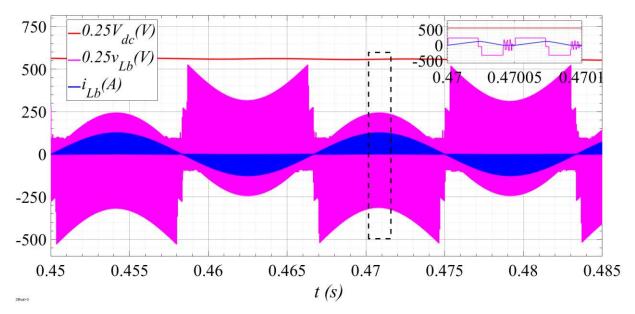

| <b>Figure 3.15</b> : Simulation waveforms of the dc-bus voltage $V_{dc}$ , boost inductor (voltage $v_{Lb}$ , current $i_{Lb}$ )                                                                                                |

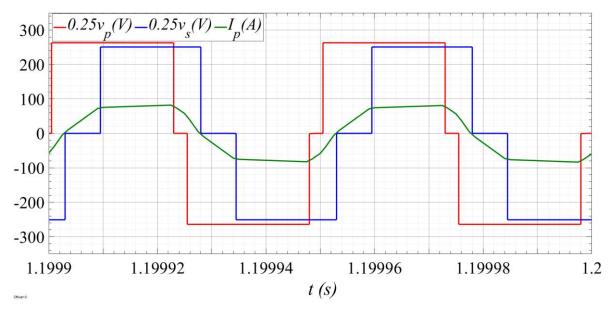

| <b>Figure 3.16</b> : Simulation waveforms of the transformer primary-side voltage $v_p$ , secondary-side voltage $v_s$ , and primary current $i_p$                                                                              |

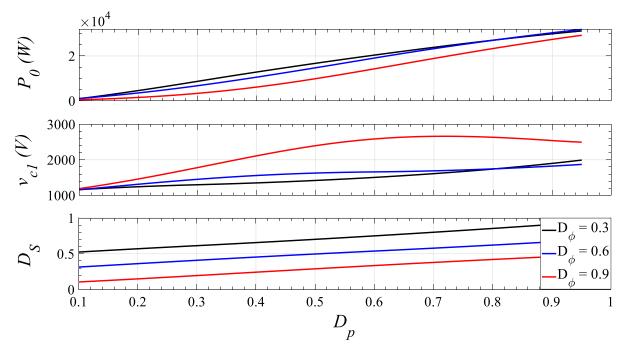

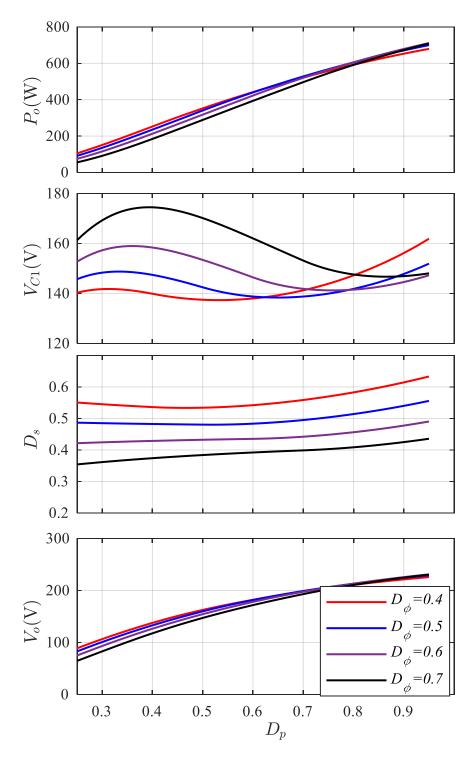

| <b>Figure 3.17</b> : Output power $P_o$ , dc bus voltage $v_{Cl}$ and secondary duty cycle $D_s$ as a function of the primary duty cycle $D_p$ with $D_{\phi}$ as a parameter                                                   |

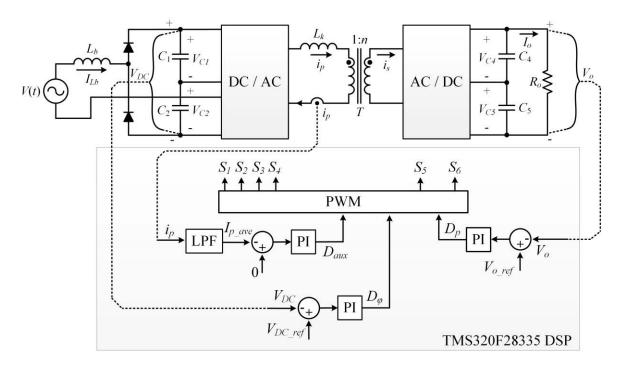

| Figure 3.18: Block diagram of the implemented hardware and close-loop control setup                                                                                                                                             |

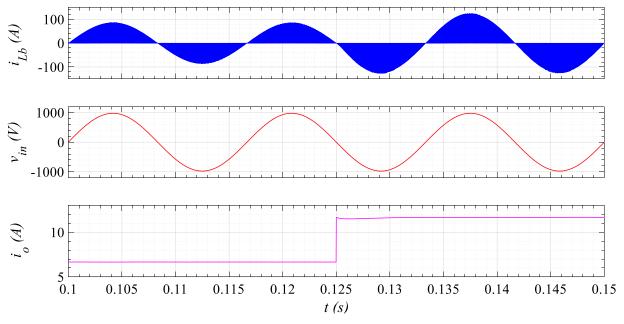

| <b>Figure 3.19</b> : Boost inductor current $i_{Lb}$ and input voltage $v_{in}$ response to a load change                                                                                                                       |

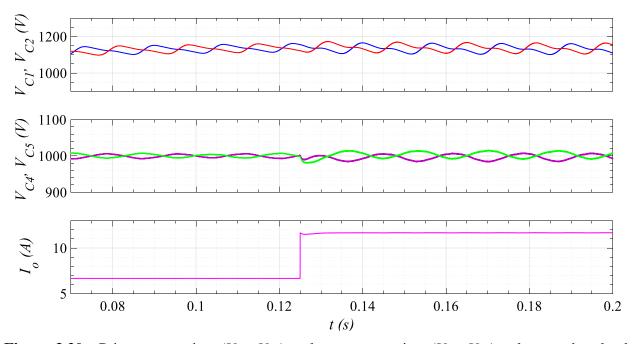

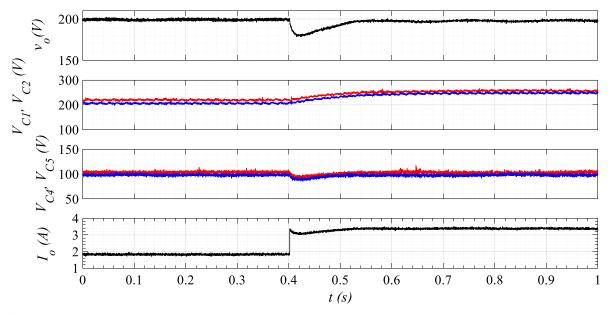

| <b>Figure 3.20</b> : Primary capacitor ( $V_{C1}$ , $V_{C2}$ ) and output capacitor ( $V_{C4}$ , $V_{C5}$ ) voltages when load change                                                                                           |

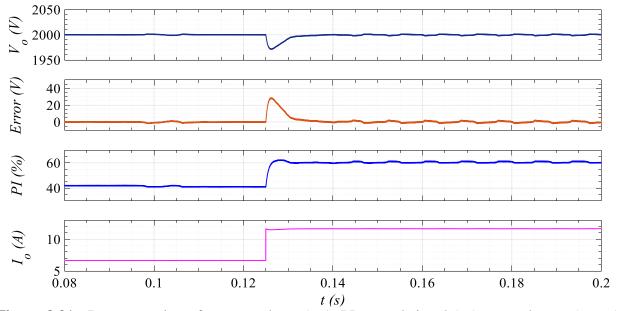

| <b>Figure 3.21</b> : Representation of output voltage ( <i>Vo</i> ), PI control signal ( <i>PI</i> ), control error ( <i>Error</i> ) at a load change                                                                           |

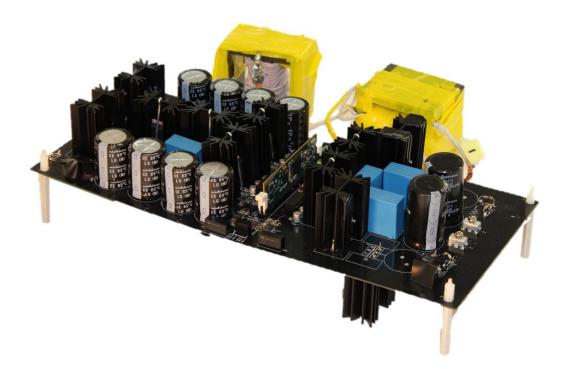

| <b>Figure 3.22</b> : Proposed scaled-down prototype topology including AC-DC converter, DSP card, sensors, leakage inductance, and high frequency transformer (PCB dimensions 380mm x 170mm) "Photo by author"                  |

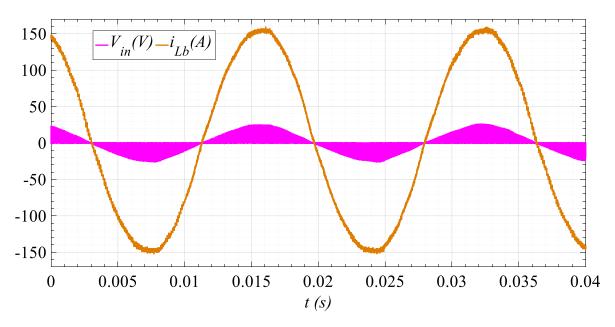

| <b>Figure 3.23</b> : Experimental waveform of input voltage $v_{in}$ , and boost inductor current $i_{Lb}$                                                                                                                      |

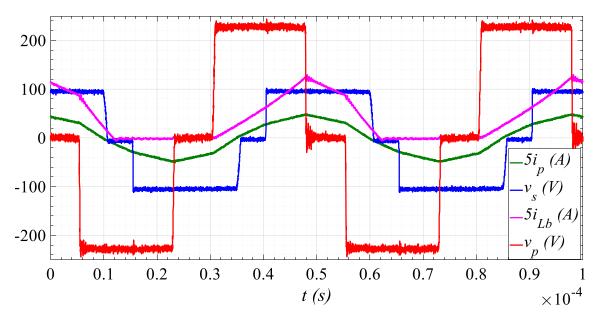

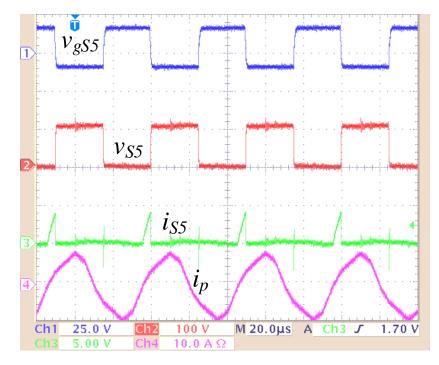

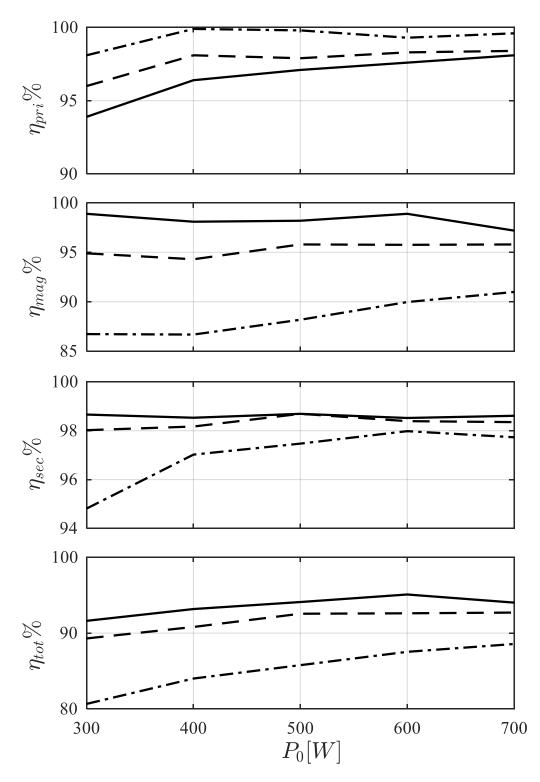

| <b>Figure 3.24</b> : Experimental waveforms of the primary voltage $(v_p)$ , secondary voltage $(v_s)$ , boost inductor current $(i_{Lb})$ and primary current $(i_p)$                                                          |

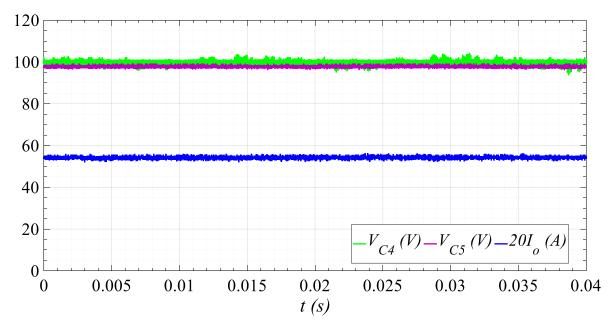

| <b>Figure 3.25</b> : Experimental waveforms of the output capacitors voltages ( $V_{C4}$ , $V_{C5}$ ), and output current ( $I_o$ )                                                                                             |

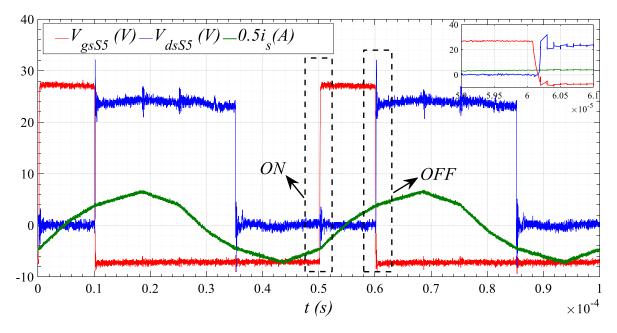

| <b>Figure 3.26</b> : Experimental waveforms representing the soft switching transitions of $S_5$ (ZCS, ZVS) at turning ON and (ZVS) at turning OFF                                                                              |

| <b>Figure 3.27</b> : Converter transient closed-loop response: Output voltage $V_o$ , dc bus capacitor voltages $V_{C1}$ and $V_{C2}$ , and output capacitor voltages $V_{C4}$ and $V_{C5}$ when a sudden load increase occurs. |

| <b>Figure 3.28</b> : Efficiency representation of the proposed ac-dc converter over a wide range of output power                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

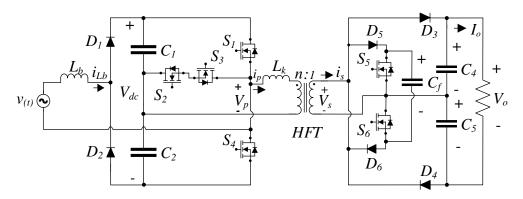

| <b>Figure 4.1</b> : Circuit configuration of the proposed boost-based three-level isolated AC-DC PFC topology                                                                                                                                                    |

| Figure 4.2: Steady-state waveforms of the proposed topology                                                                                                                                                                                                      |

| <b>Figure 4.3</b> : Proposed topology equivalent circuit for $(t_0-t_1)$ interval                                                                                                                                                                                |

| <b>Figure 4.4</b> : Proposed topology equivalent circuit for $(t_1-t_2)$ <i>interval</i>                                                                                                                                                                         |

| <b>Figure 4.5</b> : Proposed topology equivalent circuit for $(t_2-t_3)$ <i>interval</i>                                                                                                                                                                         |

| <b>Figure 4.6</b> : Proposed topology equivalent circuit for $(t_3-t_4)$ <i>interval</i>                                                                                                                                                                         |

| <b>Figure 4.7</b> : Proposed topology equivalent circuit for $(t_4-t_5)$ <i>interval</i>                                                                                                                                                                         |

| <b>Figure 4.8</b> : Proposed topology equivalent circuit for ( <i>t</i> <sub>5</sub> - <i>t</i> <sub>6</sub> ) <i>interval</i>                                                                                                                                   |

| <b>Figure 4.9</b> : Proposed topology equivalent circuit for ( <i>t</i> <sub>6</sub> - <i>t</i> <sub>7</sub> ) <i>interval</i>                                                                                                                                   |

| <b>Figure 4.10</b> : Proposed topology equivalent circuit for ( <i>t</i> <sub>7</sub> - <i>t</i> <sub>8</sub> ) <i>interval</i>                                                                                                                                  |

| <b>Figure 4.11</b> : Steady-state waveforms representation for $[D_{\varphi} > D_p]$                                                                                                                                                                             |

| <b>Figure 4.12</b> : Theoretical waveforms representing the output power $P_o$ , the input capacitor voltage $V_{C1}$ , the secondary duty cycle $D_s$ , and the output voltage $V_o$ as a function of the primary duty cycles $D_p$ and $D_\phi$ is a parameter |

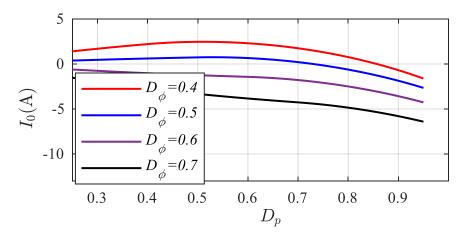

| <b>Figure 4.13</b> : Theoretical waveforms representing $I_0$ ( $i_p$ when $t = t_o$ ) as a function of the primary duty cycle $D_p$ while $D_{\phi}$ is a parameter                                                                                             |

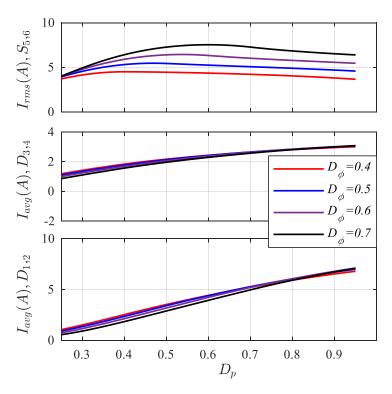

| <b>Figure 4.14</b> : Theoretical waveforms representing <i>RMS</i> ( <i>S</i> <sub>5,6</sub> ) and <i>average</i> ( <i>D</i> <sub>1,2,3,4</sub> ) currents as a function of primary duty cycle $D_p$ and $D_{\phi}$ is a parameter                               |

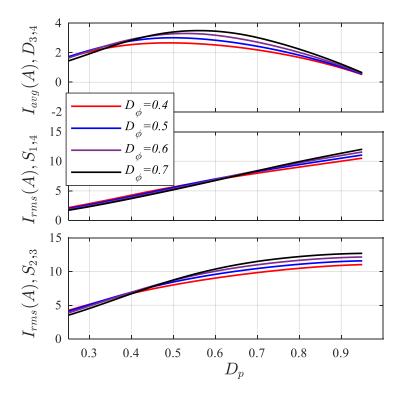

| <b>Figure 4.15</b> : Theoretical waveforms representing <i>RMS</i> ( $S_{1,4,2,3}$ ) and <i>average</i> ( $D_{,3,4}$ ) currents as a function of primary duty cycle $D_p$ and $D_{\phi}$ is a parameter                                                          |

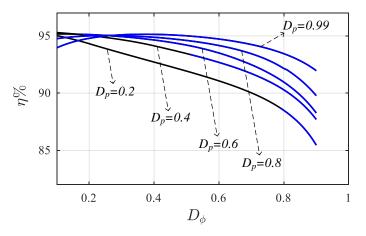

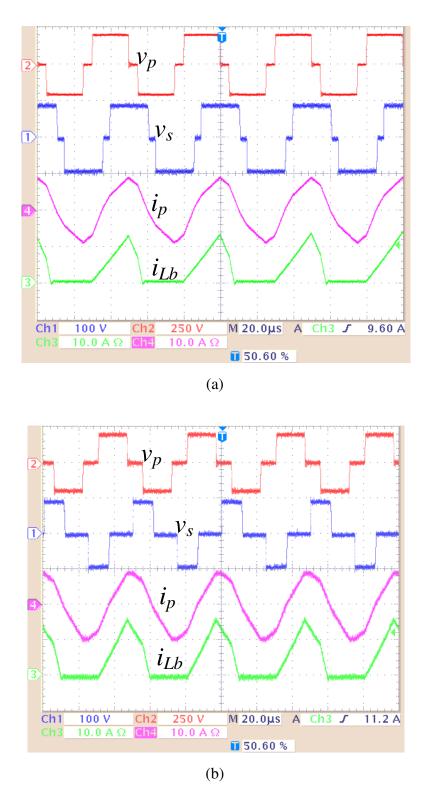

| <b>Figure 4.16</b> : Efficiency as a function of the phase shift $D_{\phi}$ where primary duty cycle $D_p$ is a parameter (blue line: soft-switching, black line: hard-switching)                                                                                |

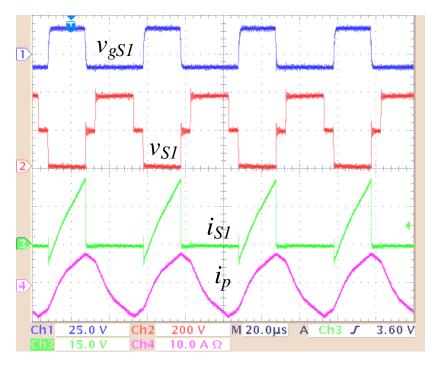

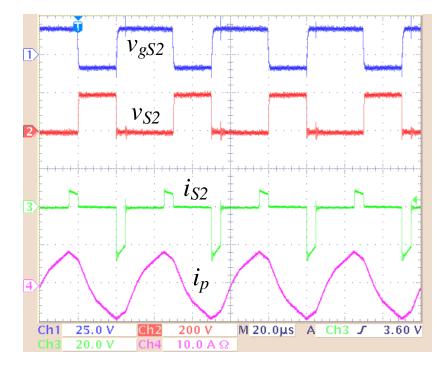

**Figure 4.17**: Experimental waveforms showing ZVS at turn ON switch  $S_1$ , gate-source signal (blue), drain-source voltage (red), current through the switch (green), and primary current (pink). 105

**Figure 4.18**: Experimental waveforms showing ZVS at turn ON for switch  $S_2$ , gate-source signal (blue), drain-source voltage (red), current through the switch (green), and primary current (pink). 105

**Figure 4.19**: Experimental waveforms showing ZVS at turn ON for switch *S*<sub>5</sub>, gate-source signal (blue), drain-source voltage (red), current through the switch (green), and primary current (pink).

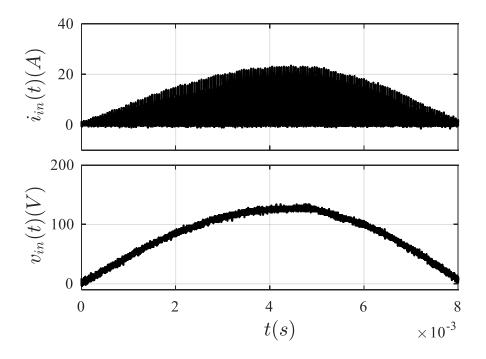

**Figure 4.22**: Input current  $i_{in}(t)$  and voltage  $v_{in}(t)$  for half of the fundamental frequency. ...... 109

| Figure 4.23: Experimental results of the average input current $I_{(AV)}$ , voltage $V_{(AV)}$ , and power $P_{(AV)}$ |  |

|-----------------------------------------------------------------------------------------------------------------------|--|

| over half of the fundamental frequency                                                                                |  |

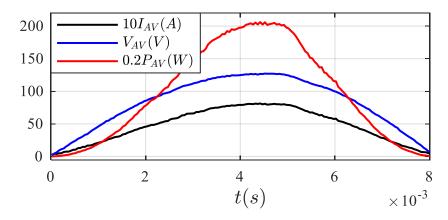

| Figure 4.24: Experimental measurements presenting power factor (PF) as function of primary duty | r |

|-------------------------------------------------------------------------------------------------|---|

| cycle $(D_p)$ for different phase shift $(D_{\phi})$                                            | ) |

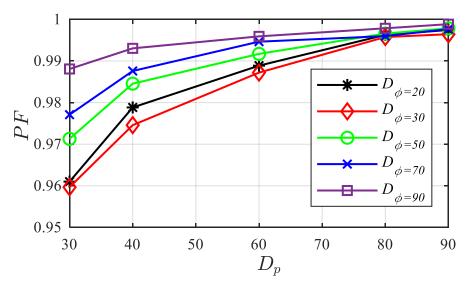

| <b>Figure 5.1</b> : Estimated temperature rise $\Delta T$ as a function of rated power using nanocrystalline |

|--------------------------------------------------------------------------------------------------------------|

| (blue) and amorphous (red) core materials                                                                    |

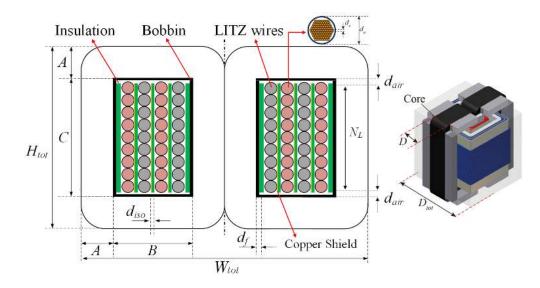

| Figure 5.2: Main physical parameters of a MFT/HFT |  |

|---------------------------------------------------|--|

|---------------------------------------------------|--|

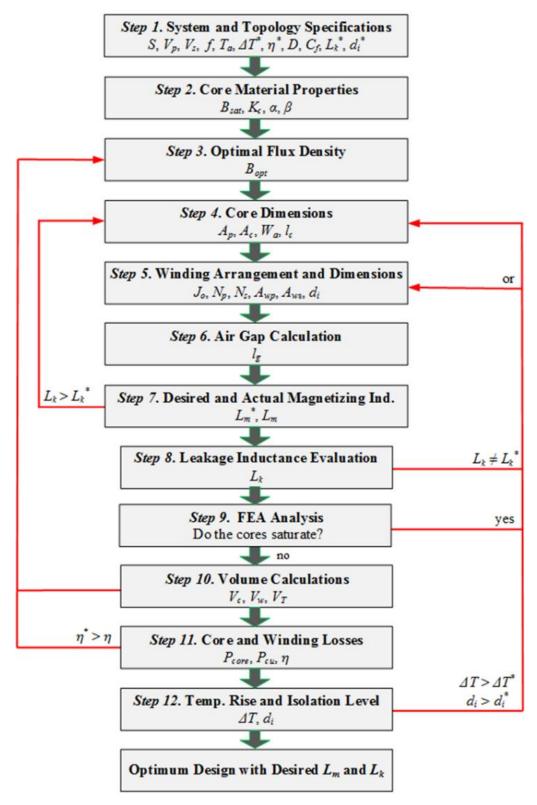

| Figure 5.3: MFTs/HFTs design flow chart | 6 |

|-----------------------------------------|---|

|                                         |   |

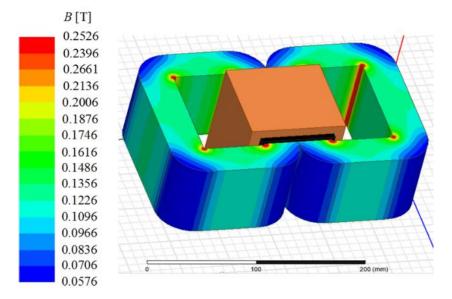

| <b>Figure 5.4</b> : ANSYS <sup>TM</sup> flux density values inside the cores |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

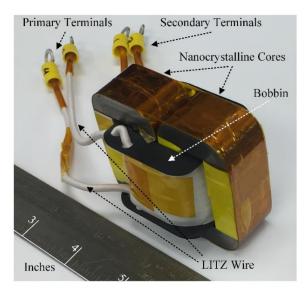

| Figure 5.5: Prototype of 1020 kW, | 120 V <sub>rms</sub> and 100 k | kHz high frequincy transformer | "Photo by |

|-----------------------------------|--------------------------------|--------------------------------|-----------|

| author"                           |                                |                                |           |

| <b>Figure 5.7</b> : Leakage inductance $L_k$ as function of the frequency                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 5.8</b> : Primary-to-secondary stray capacitance $C_{ps}$ as function of the frequency                                                     |

| Figure 5.9: Flyback converter experimental setup "Photo by author"                                                                                   |

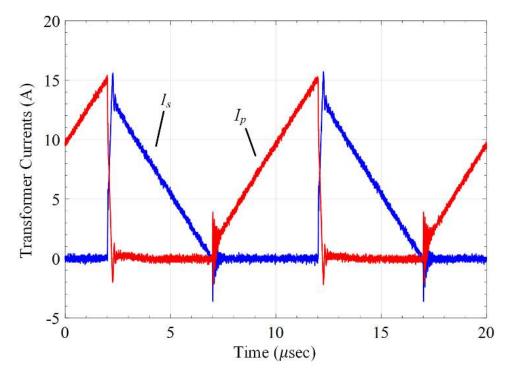

| <b>Figure 5.10</b> : Primary $I_p$ and secondary $I_s$ flyback transformer currents when the input voltage $V_{in}$ is 120 V                         |

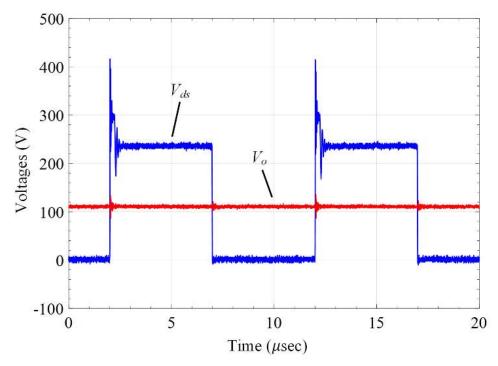

| <b>Figure 5.11</b> : SiC MOSFET drain-to-source voltage $V_{ds}$ and flyback converter output voltage $V_o$ when the input voltage $V_{in}$ is 120 V |

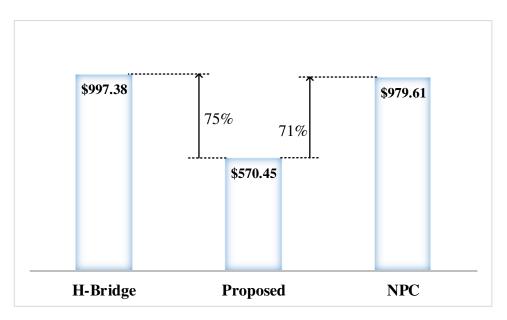

| Figure 6.1: Total cost comparison for the H-Bridge, Proposed, and NPC converters                                                                     |

## LIST OF TABLES

| Table 2-I: Qualitative Topology Comparison                    |     |

|---------------------------------------------------------------|-----|

| Table 2-II: Simulation Parameters                             |     |

| Table 2-III: Experimental Parameters                          |     |

| Table 3-I: Simulation Specifications                          | 68  |

| Table 3-II: Experimental Parameters                           | 74  |

| Table 3-III: Experimental Prototype Devices Selection         | 74  |

| Table 3-IV: Qualitative Topology Comparison.                  |     |

| Table 4-I: Symbols and Unit Abbreviations                     | 89  |

| Table 4-II: Switches and Diodes Conducting Forward Current    | 101 |

| Table 5-I: Core Material Comparison [5.6]                     |     |

| Table 5-II: Constant Values of Optimal Flux and Area Product  |     |

| Table 5-III: Material Coefficients [5.10]                     | 120 |

| Table 5-IV: Specifications and Results For MFT/HFT            | 127 |

| Table 5-V: Specified Parameters of The HFT Prototype          |     |

| <b>Table 5-VI</b> : Physical Parameters for The HFT Prototype | 129 |

| Table 6-I: Components Used for Cost Comparison                | 139 |

## LIST OF PUBLISHED PAPERS

## Chapter 2:

[2.1] O. Aldosari, L. A. Garcia Rodriguez, D. C. Rojas and J. C. Balda, "A New Isolated AC-DC Power Converter Topology with Reduced Number of Switches for High-Input Voltage and High-Output Current Applications," 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia), Busan, Korea (South), 2019, pp. 1-8. Published.

## Chapter 3:

[3.1] O. Aldosari, L. A. Garcia Rodriguez, G. G. Oggier and J. C. Balda, "A Three-Level Isolated AC-DC PFC Power Converter Topology with Reduced Number of Switches," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*. doi: 10.1109/JESTPE.2019.2962704. Published.

## Chapter 4:

[4.1] O. Aldosari, L. A. Garcia Rodriguez, G. G. Oggier and J. C. Balda, "A Boost-Based T-Type PFC Unidirectional Solid-State Transformer for Medium-Level Power Applications," *IEEE Trans. on industrial electronics*, Submitted in (04-25-2020).

## Chapter 5:

[5.1] O. Aldosari, L. A. Garcia Rodriguez, J. C. Balda and S. K. Mazumder, "Design Trade-Offs for Medium- and High-Frequency Transformers for Isolated Power Converters in Distribution System Applications,"2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, 2018, pp. 1-7. Published.

#### INTRODUCTION AND BACKGROUND

#### 1.1 Solid-State Transformer Converter Background

The solid state transformer (SST) technology has gained much attention in the field of power distribution systems [1.1] since its early-developed concept in the 1970s [1.2]. In the last decades, the number of renewable energy resources connected to the electrical networks has increased [1.3]. The SST converters play significant role of interfacing these renewable resources with numerous industrial applications [1.4]. The need to offer high-power quality to customers encourage utilities to employ the SST topologies in their power networks. A review of SST technologies and their applications in power distribution system is presented in [1.5]. The SST converter has three main functionalities: 1) galvanic isolation between the main source and the load; 2) ability to step up or down the voltage to meet specific application requirements; and 3) controlling the power flow and fault current limitation [1.1].

Nowadays, the advancement in reliable wide bandgap semiconductor devices technology increases the demand for more efficient SST converter topologies to replace the large volume and bulky conventional transformer [1.6]. The latest developments in semiconductor technology (i.e., 10 kV SiC MOSFET) promotes SST converters to be used in high-voltage applications; i.e., 7 kV/400 V DC data center [1.7]. However, the devices ratings are still the limitation for employing such converters in high-voltage levels. Hence, multi-level converters, for example, three-level converters (i.e., neutral point clamped (NPC)), are preferred over the two-level ones especially for high-power applications.

As the rated power of an application increases, the price associated with the SST topology increases as well. That is because, active switches do not support a high-voltage or current and

there is a need to connect the switches in parallel or in series to sustain the application current and voltage ratings. In high-power applications where modular multilevel AC-DC converters are required, the issue of unbalancing power in each module presents instability problem [1.8].

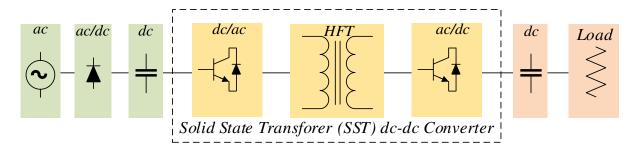

The basic structure of a single-phase isolated ac-dc converter is composed of ac-dc rectifier and SST dc-dc converter that includes a high frequency transformer (HFT) and power electronic converters as shown in Fig. 1.1. The operating frequency of the HFT is one of the parameters that defines the size of the magnetic cores [1.9]. For that reason, the primary and secondary converters operate at higher frequency resulting in much compact sizes when compared to the conventional 60/50 Hz transformer.

The remainder of this chapter is organized as follows: Section 1.2 provides an overview of the existing single-phase isolated AC-DC power factor corrected (PFC) converters including two- and three-level topologies; Section 1.3 presents the research focus and objectives; Section 1.4 gives a brief description of the proposed two topologies; Section 1.5 shows the conventional and the proposed design steps of HFT; and Section 1.6 describes how this dissertation is organized.

## 1.2 Existing Isolated Single-Phase AC-DC (PFC) Topologies

The isolated AC-DC PFC converters operate at high power factors (PF) to comply with international standards, such as IEC 1000-3-2 [1.10].

Figure 1.1: Solid-State Transformer (SST) configuration.

One method to guarantee a high PF is to connect passive filter components (inductor and capacitors) at the input terminals to shape the input current to a sine waveform and in phase with the input voltage [1.11]. However, the overall system becomes bulky and difficult to handle due to the size of the passive elements. Another method is to insert a boost inductor between the input and the front end rectifier to boost the intermediate dc-bus voltage to a high level (i.e.,  $[V_{dc} > 2V_{in(pk)}]$ ) [1.12].

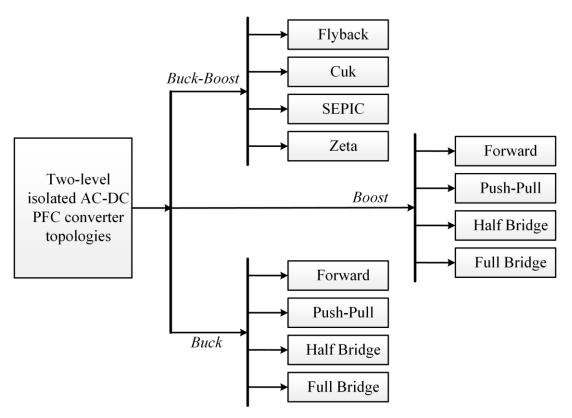

Isolated single-phase AC-DC PFC topologies can be characterized into two categories: mainly, two- and three-level isolated AC-DC PFC converters. Developed two-level topologies are constructed from buck, boost and buck-boost converters. These types of converters are suitable for low-power applications (i.e., few Watts to several kW) [1.13]. The three-level topologies based on the neutral-point-clamped (NPC) converter [1.14] and the three-level T-type converter (3LT<sup>2</sup>C) are used for higher power applications.

#### 1.2.A Two-Level Topologies

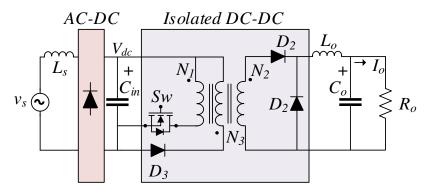

The two-level topologies are classified into three major circuit structures (i.e., buck, boost, and buck-boost). These types of converters are suitable for low-power applications such as medical equipment, small rating ASDs in fans, and telecommunication applications. Fig. 1.2 shows the classification of the two-level converter family [1.15] that depends on the circuit topology. Some of these converters are used for low-power applications; and other can be used for higher power applications. For instance, isolated buck forward AC-DC converter shown in Fig. 1.3 is appropriate for low-power application i.e., 1-kW, 48-V isolated battery charger. At the front end, the AC-DC stage rectifies the AC source to an uncontrolled dc-bus voltage.

Figure 1.2: Classification of two-level isolated AC-DC PFC converter family.

Figure 1.3: Isolated buck forward AC-DC converter.

The intermediate dc-capacitance  $C_{in}$  supplies the output through an isolated forward dc-dc converter. During the ON state, primary current makes the secondary current to flow through  $D_2$  and energy is transferred directly to the output load. Unlike the flyback converter which stores the energy in the primary windings during the ON state and then transfers the power to the load during the OFF time [1.16]. The parameters needed to control the output voltage of the isolated buck

forward converter are the switch duty cycle, transformer turn ratio, and input voltage. Usually, the output voltage of the isolated buck forward, push-pull, half-bridge, and full-bridge AC-DC converters is controlled by adjusting the duty cycle of the primary switch [1.15]. Previous researchers provided many different control strategies to operate this type of converters [1.17][1.19].

The main advantages of utilizing the two-level converters are as follows:

- 1. Cost-effective (few devices).

- 2. Less control effort.

- 3. Small size.

The drawbacks of two-level converters are:

- 1. Higher switching losses at higher switching frequencies (poor efficiency) [1.20].

- 2. Adverse acoustic noise [1.20].

- 3. Unable to regulate dc-bus while controlling the output voltage.

## 1.2.B Three-Level Topologies

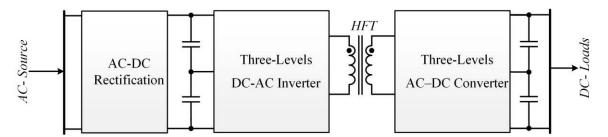

The isolated three-level AC-DC power converters are extensively used in many high-power applications; for example, uninterrupted power supplies (UPS), battery charging systems, induction heater, hybrid (AC-DC) microgrids or offshore wind farms, etc. [1.21]-[1.24]. It converts the alternating current (AC) from the utility grid or renewable source (i.e., wind turbine) to a direct current (DC) to supply a dc-load through a HFT. Fig. 1.4 shows an illustration of the overall network structure of these types of converters.

Figure 1.4: Network representation of isolated three-level AC-DC power converter.

These converters must operate while complying with international standard requirements [1.25], [1.26] to improve the power quality at the grid (i.e., the AC source) and deliver reliable energy to the costumers. The AC-DC rectification consists of a full or half diode bridge rectifier and/or controlled rectifier to convert the ac input to a dc voltage. The three-level DC-AC inverter (i.e., NPC, T-type, and H-bridge) lies between the intermediate dc-bus capacitor and the primary terminals of the HFT and inverts the dc-current to ac-current at high frequency. The last stage (i.e., three-level AC-DC converter) rectifies the secondary AC-current of the transformer to a DC-current to supply the output capacitors.

For high-power applications in the range of megawatt levels, the inverter at the primary side of the HFT must be cascaded in a series configuration (multilevel converter) to reduce the voltage stress on the semiconductor devices. At the secondary side for low output voltage applications, the converters are connected in parallel to share current between switches. A comprehensive study on multilevel inverters, a survey of topologies, control strategy, and applications are presented in many previous publications [1.27], [1.28], and [1.29]. The NPC converter is the most wildly used multilevel converter since its invention in 1981 [1.30].

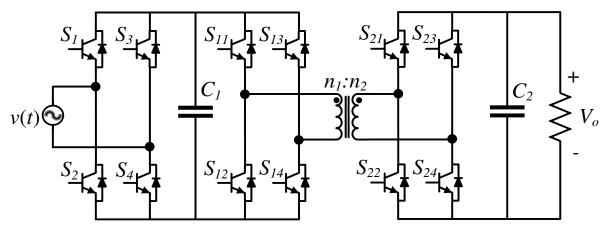

The existing three-level isolated AC-DC converter topologies capable of controlling dc-bus and output voltages consist of at least eight active switches to deliver power at high input PF. The most well-known topology is the H-bridge circuit in each stage, as presented in [1.31]. The main advantages of this topology are bidirectional power-flow capability and full control of the dc-bus and output voltages. However, even this topology has three voltage-levels at the primary terminals  $(+V_{dc}, 0, -V_{dc})$  and at the secondary terminals  $(+V_o, 0, -V_o)$ , the switches sustain the full dc-bus and output voltage which is a major drawback when compared to NPC converter that sustain only half of the dc-bus and output voltages. Another disadvantage is the price associated with the multiple number of switches within this topology especially at high-power levels, which requires cascading multiple converters in parallel or in series. More details regarding this topology will be provided in Chapter 2, section 2.3.1.

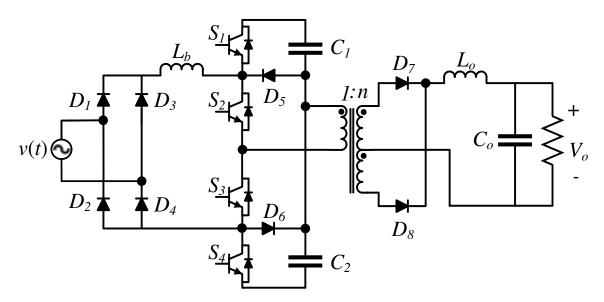

Another topology is a unidirectional three-level isolated single-stage PFC converter presented in [1.11]. The advantages of this topology are: 1) low-cost because there are only four active switches; 2) the switches sustain half of the dc-bus voltage; 3) high PF. The main disadvantage is that there is no way to control the dc-bus and output voltages, simultaneously. The pros and cons of this topology will be presented in more detail in Chapter 2, section 2.3.2.

To reduce the number of the devices further, the full diode rectifier is replaced by a half-bridge diode rectifier, as presented in [1.32] and shown in Fig. 1.5.

Figure 1.5: Isolated three-level AC-DC power converter with minimum power devices [1.32].

Essentially, this is another version of the NPC converter with a different connection of the dcbus capacitors. Furthermore, this topology is not capable of regulating the dc-bus voltage and controlling the output voltage at the same time.

To overcome the issue of controlling the dc-bus and output voltages simultaneously, a new solid-state transformer (SST) three-level isolated AC-DC converter was proposed in [1.33] and shown in Fig. 1.6. The benefits of adopting this topology are few power conversions stages, lower voltage stresses on the primary switches and lower currents through the secondary switches. However, the secondary side switches sustain a full output voltage, which is a major drawback of this topology.

Furthermore, the soft-switching region is depending on the mode of operation; that is, the primary duty cycle  $D_p$  and the secondary duty cycle  $D_s$  may overlap, or partially overlaps, and or fully overlap. For example, at partial overlap, the phase shift  $D_{\varphi}$  between the primary and secondary voltages should be less than  $[(D_p + D_s)/2]$ ,  $D_s$  should be larger than or equal to  $[2(1-D_p/2)-D_{\varphi}]$ , and  $D_s$  should be larger or equal to  $[1-D_p]$ .

Figure 1.6: Boost-based three-level SST topology [1.33].

These restrictions add more complicity to the control technique and limit the control functionality when the load suddenly increases or decreases. Another disadvantage is the issue of power back-flow between the primary and secondary bridges adding more restrictions and more control effort. Power back-flow happens when current and voltage have different polarities at the same time [1.34]. The source of all the mentioned issues is the secondary-side bridge that needs to be replaced with a new cost-effective and reliable circuit.

#### **1.3 Research Focus and Objectives**

This research work focus on developing two novel unidirectional isolated three-level AC-DC PFC topologies. The first topology is based on NPC inverter and the second topology is based on T-type inverter. With only six active switches, both topologies must achieve the following objectives:

- 1) Shaping the input current to be a sine waveform and in phase with the input voltage to obtain a high PF.

- 2) Regulating the dc-bus voltage while controlling the output voltage.

- 3) Operating the converter under soft-switching within a wide range of operation.

- 4) Achieving all the above objectives with a minimum number of active switches.

This dissertation will focus on defining the steady-state analysis, obtaining the design equations for all the passive components (inductors, capacitors, and HFT), realizing the softswitching, and recognizing the full characteristic of the propose converters. As a part of this research work, a control strategy of the proposed topology should be introduced. In addition, this dissertation should cover the trade-offs when designing a high-frequency transformer for a specific power converter. The main objective of designing a HFT is to obtain a high efficient HFT and optimize the selection of its magnetic material.

#### **1.4 Proposed Isolated Single-Phase AC-DC PFC Topologies**

From the above, it can be concluded that there is a need for a power converter topology that has the following capabilities:

- 1) Regulating the dc-bus and output voltages at the same time.

- 2) Controlling the power flowing from the source to the dc-load.

- 3) Correcting the input PF.

In addition, the operation of the system is nonlinear due to the presence of the semiconductor devices, and converters inject harmonics back into the grid. For that reason, the total harmonics distortion (THD) should be less than a specific value set by international standards. Furthermore, the proposed topologies should achieve the above listed requirements with only six active switches, which is a great contribution work adding to the state of art.

The research motivation is to fill the gap between existing topologies that have a complete functionality of a three-level AC-DC converter, which may be expensive, and those ones that may be cost-effective but not satisfying the above listed capabilities. The above topics are addressed by the following new topologies.

#### 1.4.A Proposed Topology Based on NPC Inverter

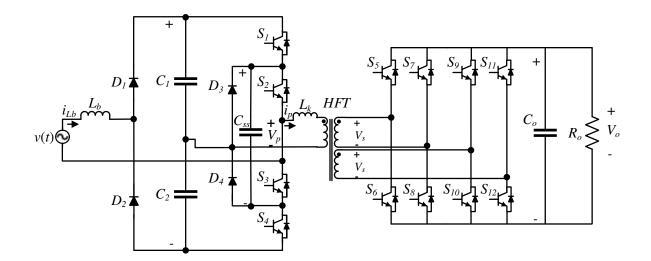

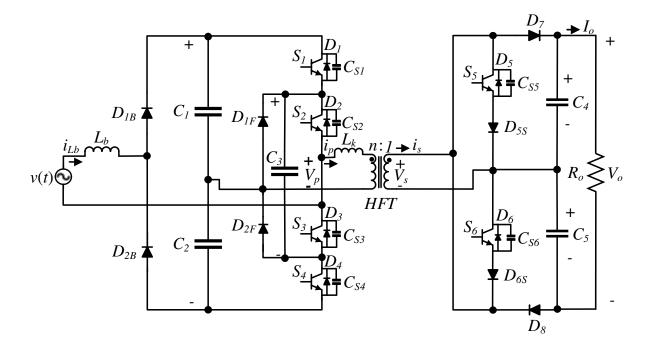

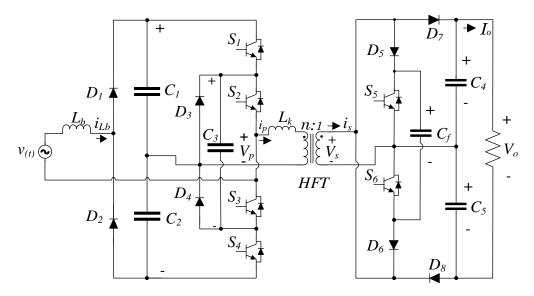

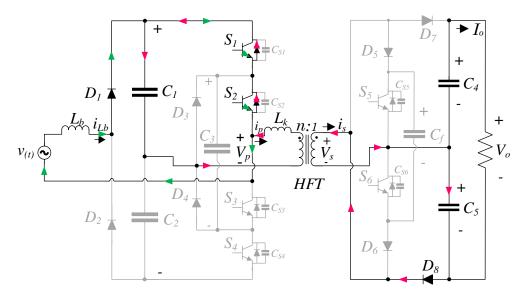

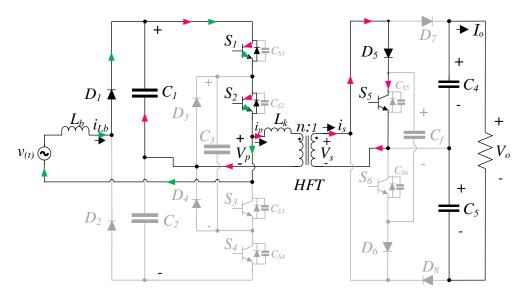

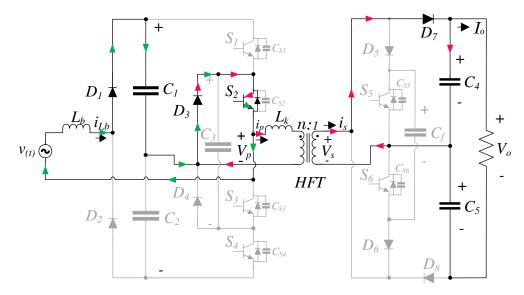

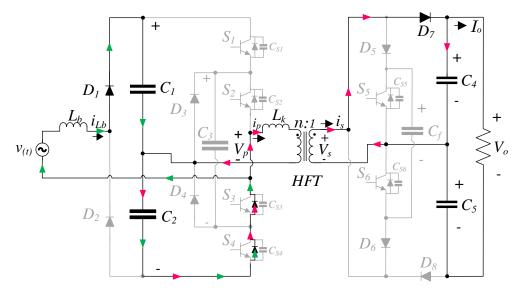

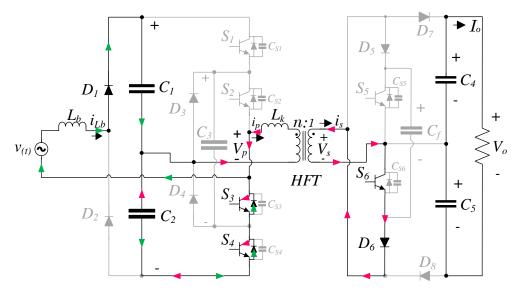

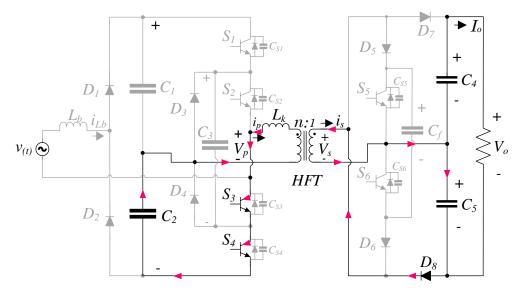

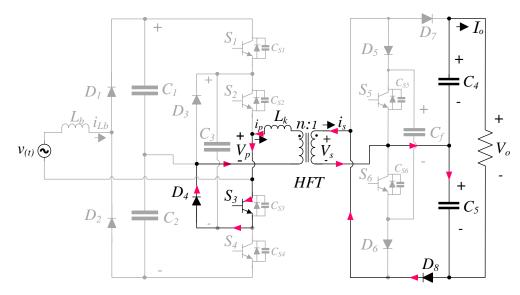

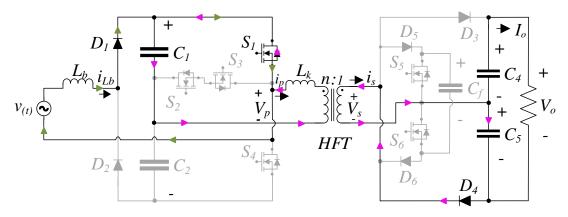

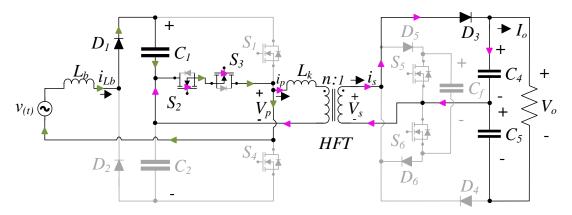

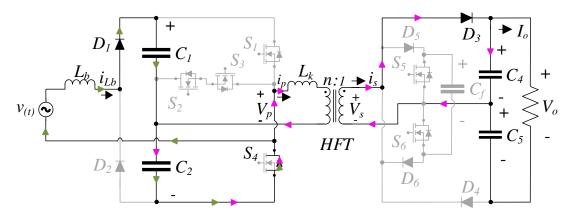

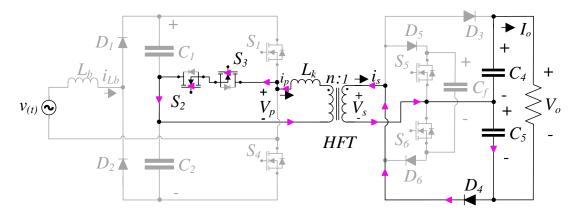

The first proposed three-level unidirectional isolated AC-DC PFC converter topology is based on the NPC inverter as shown in Fig. 1.7. The secondary switches ( $S_5$ ,  $S_6$ ) and series diodes ( $D_5$ ,  $D_6$ ) sustain half of the output voltage, which makes a difference in terms of the cost and the freedom of having a high output voltage without adding series devices. The main function of ( $S_5$ ,  $S_6$ ) is to control the phase shift between the primary and secondary voltages.

Figure 1.7: Proposed three-level isolated AC-DC PFC topology based on NPC inverter.

The diode  $(D_5, D_6)$  is connected in series with the switch  $(S_5, S_6)$  to block the secondary current when one of the anti-parallel diodes of  $(S_5, S_6)$  is forward bias. The diode  $(D_7, D_8)$  prevents shorting the output capacitors  $(C_4, C_5)$ .

During the (positive or negative) half cycle of the secondary voltage, only one diode ( $D_7$  or  $D_8$ ) conducts, which reduces the conduction losses and improves the overall efficiency. The flying capacitor  $C_f$  connected between the nodes of ( $D_5$ ,  $S_5$ ) and ( $S_6$ ,  $D_6$ ) acts as a charging and discharging bank of the parasitic capacitances ( $C_{S5}$ ,  $C_{S6}$ ) to allow soft-switching action at turning ON. More details about the soft-switching technique of the secondary switches will be given in Chapter 3. This topology is suitable for high-power high-voltage applications because all the primary and secondary switches sustain half of the dc-bus and output voltages.

## 1.4.B Proposed Topology Based on T-type Inverter

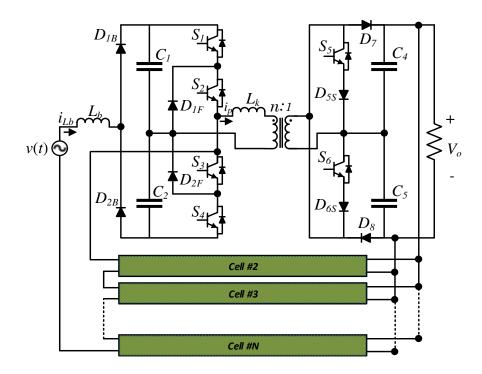

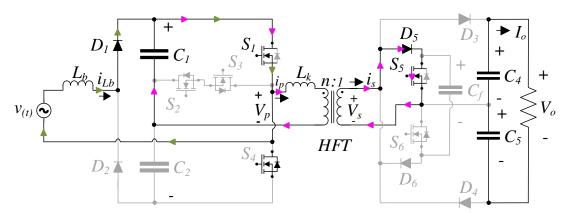

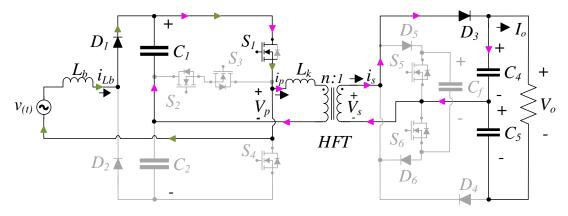

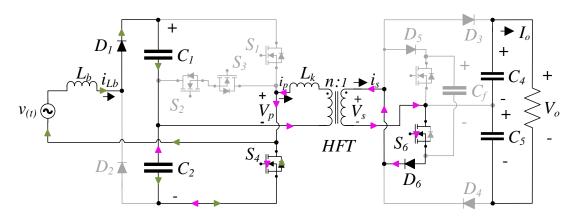

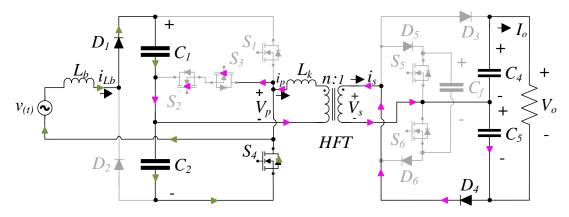

The second topology is a modification of the first topology where the NPC circuit is replaced with a T-type inverter as shown in Fig. 1.8.

The main advantages of T-type topology when compared to the NPC topology are listed below:

- Cost-effective.

- Low conduction losses at higher primary and phase shift duty cycles, only one switch (*S*<sub>1</sub> or *S*<sub>4</sub>) conducts the primary and boost currents.

- Possibility of generating PWM singles based on the proposed modulation scheme to conduct primary and boost currents through  $S_2$  and  $S_3$  instead of body diodes.

- Compact size.

However, there are disadvantages associated with T-type topology when compared to NPC topology.

•  $S_1$  and  $S_4$  block the full dc-bus voltage  $V_{dc}$  where in the NPC converter same switches block half of  $V_{dc}$ .

Figure 1.8: Proposed three-level isolated AC-DC PFC topology based on T-type inverter.

- During the circulation of the primary current through the HFT winding,  $S_2$  and  $S_3$  conduct the primary and boost inductor currents. However, the NPC switches  $S_2$ ,  $S_3$  conduct the primary current only.

- Suitable for high-power and low-voltage applications.

The T-type based topology shows a higher efficiency when compared to the NPC based topology. In both topologies, most of the converter losses are associated with the magnetic components which makes the design of a HFT is an essential part to complete this dissertation. The next section will present the conventional and the proposed steps for designing HFT.

## **1.5 High Frequency Transformer Design**

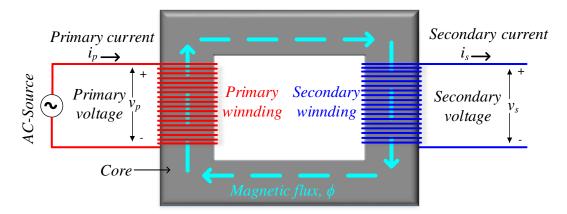

The basic structure of an ideal transformer consists of a core and two independent windings (primary, secondary) which transfer energy between two isolated circuits by means of electromagnetic induction process as shown in Fig. 1.9 [1.35], [1.36]. Once an alternative current flow through a coil (primary), it produces a magnetic flux, which in return induces an electromotive force across the other coil (secondary).

Figure 1.9: Ideal electrical transformer and induction law representation.

For an ideal electrical transformer, Faraday's induction law states that, since the same magnetic flux  $\phi$  flows through primary and secondary windings, it induces voltages proportional to the number of turns.

### **1.5.A Conventional Design**

The main concept and designing steps of HFT have been detailed in many previous publications; e.g., [1.37], [1.38]. These steps are:

- 1. Specifications of the application: output power, desired efficiency, primary and secondary voltages, primary and secondary currents, required leakage inductance, duty cycle, operating frequency of the converter, expecting temperature rise, and isolation level.

- 2. Material selection: Steinmetz coefficients, flux saturation density, and isolation material properties including, safety margin and dielectric strength.

- 3. Optimized flux density calculation: the optimized flux depends on:

- The typical values of the dimensionless coefficient  $k_a = 40$ ,  $k_c = 5.6$ , and  $k_w = 10$  [1.39].

- The type of cooling, i.e., the heat transfer  $h_c=10W/m^2$  for natural convection.

- The window utilization factor which depends on winding tightness.

- The stacking factor that relates the effective cross section area to the physical core area.

- The waveform factor i.e.,  $k_{\nu}$ =4.44 for a sinusoidal and  $k_{\nu}$ =4 for a square waveform [1.40].

- 4. Physical core dimensions which can be calculated as in [1.37].

- 5. Wire selection based on the current density.

- 6. Required isolation distance.

- 7. Leakage inductance calculation. If the calculated leakage is not met, then designer should either go back to step 5 and changes the selected wire or modifies the isolation distance.

- 8. Volume calculation.

- 9. Total loss calculation.

- 10. Efficiency and temperature rise calculations.

As the operating frequency increases, the loss density increases as well, making the selection of soft-magnetic material a critical step when designing HFT. At medium frequency operation, the nanocrystalline and amorphous materials show high efficiency due to reduced eddy current losses [1.41].

#### **1.5.B** Proposed Design

The new power electronic converter topologies and different applications' requirements have an impact upon the design steps of the HFT. For instant, the dual active bridge (DAB) requires specific leakage inductance and very large magnetizing inductance where a topology based on the flyback converter working principle requires very low leakage inductance and specific value of magnetizing inductance. The new proposed design counts for these two specifications and include them in the first step of designing the HFT. More explanation regarding how to take into consideration these two parameters will be provided in section 5.3A.

In addition, the proposed design includes finite-element analysis (FEA) using ANSYS<sup>TM</sup> in the design steps to measure and visualize the distribution of magnetic flux inside the core. If the core is saturated, then the designer should stop and go back to choose different core size or change the way the windings are arranged around the core. Furthermore, the proposed design will present a new method which estimates the losses of different magnatic materials as a function of the output power.

#### **1.6 Organization of This Dissertation**

This dissertation is organized as follows:

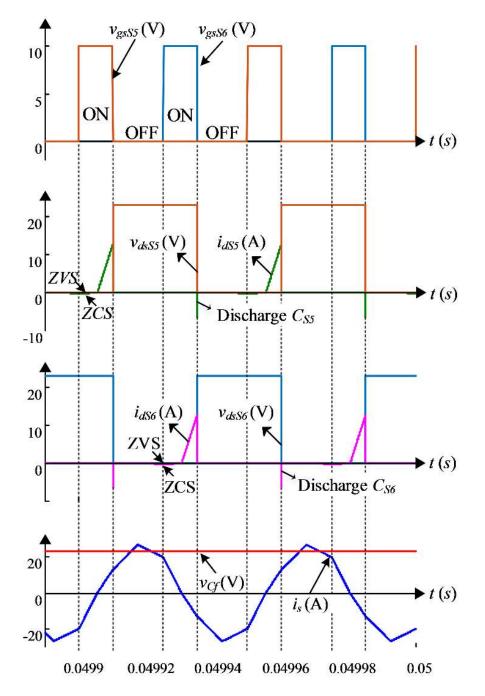

- Chapter 2 introduces the first proposed topology including circuit configuration, steady-state analysis (waveforms and operational principle), a comparison between existing topologies and the proposed topology, a simulation case study on a 87.5-kW, as well as a 250-W experimental prototype. All the results of this chapter were obtained under open-loop conditions (that is, there is no closed loop applied). In this chapter, the drain-source capacitances  $C_{ds}$  of secondary switches charge up to half of the output voltage and do not discharge during the OFF time, which drives the secondary switches to operate under hard-switching. Therefore, Chapter 3 proposes a new technique to overcomes the hard-switching issue.

- Chapter 3 continues with the investigation into the proposed topology. The new study includes modifying the secondary-side circuit by adding a flying capacitor to achieve soft-switching, steady-state analysis, soft-switching analysis (primary and secondary switching), and proposed converter design procedure (boost inductor, dc-bus capacitor selection, HFT design, and output capacitor selection). As a proof of concept, the theoretical analysis was evaluated through a 25-kW case study simulation as well as a 900-W experimental prototype. Furthermore, three closed-loop PI controllers were applied to the proposed topology to investigate how the converter response to a load change.

- Chapter 4 is a modification of the previously proposed topology where the primary side NPC bridge is replaced with a T-type three-level inverter. In contrast to NPC based topology (Chapter 3), T-type based topology (Chapter 4) has less devices (cost-

effective) and low conduction losses (high efficiency). Chapter 4 includes steady-state analysis (circuit configuration, steady-state waveforms with a new pulse-width modulation scheme, and operational principles), soft-switching analysis for primary and secondary switches, and experimental results. Mainly, chapter 4 focus on the full-characterizations of ac-dc converter based on T-type topology.

- Chapter 5 addresses for completeness the design procedures of a HFT including magnetic material selection, in particular, nanocrystalline, amorphous, and ferrite. In addition, it includes temperature rise consideration, design methodology (e.g., magnetizing and leakage inductances, design steps), simulation of a 120-kVA case study obtained using finite-element analysis (FEA), and demonstrating the feasibility of the ideas by building a scale-down 1-kW prototype.

- Chapter 6 provides the conclusions and contributions of this doctoral work. In addition, possible future works that can be done on this topology to improve the overall efficiency.

## **1.7 References**

- [1.1] X. She, A. Q. Huang and R. Burgos, "Review of Solid-State Transformer Technologies and Their Application in Power Distribution Systems," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 3, pp. 186-198, Sept. 2013.

- [1.2] W. McMurray, "Power converter circuits having a high-frequency link," U.S. Patent 3 517 300, Jun. 23, 1970.

- [1.3] X. She, X. Yu, F. Wang, and A. Q. Huang, "Design and demonstration of a 3.6-kV-120-V/10-kVA solid-state transformer for smart grid application," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 3982–3996, Aug. 2014.

- [1.4] E. R. Ronan, S. D. Sudhoff, S. F. Glover and D. L. Galloway, "A power electronic-based distribution transformer," in *IEEE Trans. on Power Delivery*, vol. 17, no. 2, pp. 537-543, April 2002.

- [1.5] X. She, A. Q. Huang and R. Burgos, "Review of Solid-State Transformer Technologies and Their Application in Power Distribution Systems," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 3, pp. 186-198, Sept. 2013.

- [1.6] D. G. Shah and M. L. Crow, "Stability design criteria for distribution systems with solidstate transformers," *IEEE Trans. Power Del.*, vol. 29, no. 6, pp. 2588–2595, Dec. 2014.

- [1.7] D. Rothmund, T. Guillod, D. Bortis and J. W. Kolar, "99% Efficient 10 kV SiC-Based 7 kV/400 V DC Transformer for Future Data Centers," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 2, pp. 753-767, June 2019.

- [1.8] J. Shi, W. Gou, H. Yuan, T. Zhao and A. Q. Huang, "Research on voltage and power balance control for cascaded modular solid-state transformer," in *IEEE Trans. on Power Electronics*, vol. 26, no. 4, pp. 1154-1166, April 2011.

- [1.9] L. Keke and L. Lin, "Analysis of favored design frequency of high-frequency transformer with different power capacities," 2014 International Conference on Power System Technology, Chengdu, 2014, pp. 2272-2278.

- [1.10] D. D. C. Lu, D. K. W. Cheng, and Y. S. Lee, "Single-stage AC–DC power-factor-corrected voltage regulator with reduced intermediate bus voltage stress," *Proc. Inst. Elect. Eng.*— *Elect. Power Appl.*, vol. 150, no. 5, pp. 506–514, Sep. 2003.

- [1.11] S. Dusmez, X. Li and B. Akin, "A Fully Integra ted Three-Level Isolated Single-Stage PFC Converter," in IEEE *Trans. on Power Electronics*, vol. 30, no. 4, pp. 2050- 2062, April 2015.

- [1.12] P. M. Barbosa, F. Canales, J. M. Burdio and F. C. Lee, "A three-level converter and its application power factor correction," in *IEEE Trans. on Power Electronics*, vol. 20, no. 6, pp. 1319-1327, Nov. 2005.

- [1.13] B. Singh, S. Singh, A. Chandra and K. Al-Haddad, "Comprehensive Study of Single-Phase AC-DC Power Factor Corrected Converters With High-Frequency Isolation," in *IEEE Trans. on Industrial Informatics*, vol. 7, no. 4, pp. 540-556, Nov. 201

- [1.14] A. Nabae, I. Takahashi, and H. Akagi, "A neutral-point clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. 1A-17, no. 5, pp. 518–523, Sep. 1981.

- [1.15] B. Singh, S. Singh, A. Chandra and K. Al-Haddad, "Comprehensive Study of Single-Phase AC-DC Power Factor Corrected Converters With High-Frequency Isolation," in *IEEE Trans. on Industrial Informatics*, vol. 7, no. 4, pp. 540-556, Nov. 2011.

- [1.16] N. Coruh, S. Urgun and T. Erfidan, "Design and implementation of flyback converters," 2010 5th IEEE Conference on Industrial Electronics and Applications, Taichung, 2010, pp. 1189-1193.

- [1.17] N. Mohan, T. Udeland, and W. Robbins, *Power Electronics: Converters, Applications and Design,* 3rd ed. New York: Wiley, 2002.

- [1.18] J. C. Bennett, *Practical Computer Analysis of Switched Mode Power Supplies*. New York: CRC Press, 2006.

- [1.19] Yen-Wu Lo and R. J. King, "High performance ripple feedback for the buck unity-powerfactor rectifier," in *IEEE Trans. on Power Electronics*, vol. 10, no. 2, pp. 158-163, March 1995.

- [1.20] A. Choudhury, P. Pillay and S. S. Williamson, "Comparative Analysis Between Two-Level and Three-Level DC/AC Electric Vehicle Traction Inverters Using a Novel DC-Link Voltage Balancing Algorithm," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 529-540, Sept. 2014.

- [1.21] S. Jeong, J. Kwon and B. Kwon, "High-Efficiency Bridgeless Single-Power-Conversion Battery Charger for Light Electric Vehicles," *IEEE Trans. on Industrial Electronics*, vol. 66, no. 1, pp. 215-222, Jan. 2019.

- [1.22] B. Whitaker et al., "A High-Density, High-Efficiency, Isolated On-Board Vehicle Battery Charger Utilizing Silicon Carbide Power Devices," *IEEE Trans. on Power Electronics*, vol. 29, no. 5, pp. 2606-2617, May 2014.

- [1.23] M. de Prada, L. Igualada, C. Corchero, O. Gomis-Bellmunt, A. Sumper, "Hybrid AC-DC Offshore Wind Power Plant Topology: Optimal Design," *IEEE Trans. on Power Systems*, Vol. 30, No. 4, July 2015, pp. 1868-1876.

- [1.24] C. Li and D. Xu, "Family of Enhanced ZCS Single-Stage Single-Phase Isolated AC-DC Converter for High-Power High-Voltage DC Supply," *IEEE Trans. on Industrial Electronics*, vol. 64, no. 5, pp. 3629-3639, May 2017.

- [1.25] *IEEE Recommended Practices and Requirements for Harmonics Control in Electric Power Systems*, IEEE Standard 519, 1992.

- [1.26] Electromagnetic Compatibility (EMC) Part 3: Limits- Section 2: Limits for Harmonic Current Emissions (equipment input current 16 A per phase), IEC1000-3-2 Document, 1st ed., 1995.

- [1.27] J. Rodriguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications," in *IEEE Trans. on Industrial Electronics*, vol. 49, no. 4, pp. 724-738, Aug. 2002.

- [1.28] S. Kouro *et al.*, "Recent Advances and Industrial Applications of Multilevel Converters," in *IEEE Trans. on Industrial Electronics*, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [1.29] Jih-Sheng Lai and Fang Zheng Peng, "Multilevel converters-a new breed of power converters," in *IEEE Trans. on Industry Applications*, vol. 32, no. 3, pp. 509-517, May-June 1996.

- [1.30] Y. Jiao and F. C. Lee, "New Modulation Scheme for Three-Level Active Neutral-Point-Clamped Converter With Loss and Stress Reduction," in *IEEE Transa. on Industrial Electronics*, vol. 62, no. 9, pp. 5468-5479, Sept. 2015.

- [1.31] J. Everts, F. Krismer, J. Van den Keybus, J. Driesen and J. W. Kolar, "Optimal ZVS Modulation of Single-Phase Single-Stage Bidirectional DAB AC–DC Converters," in *IEEE Trans. on Power Electronics*, vol. 29, no. 8, pp. 3954-3970, Aug. 2014.

- [1.32] W. Choi, J. Choi and J. Yoo, "Single-stage bridgeless three-level AC/DC converter with current doubler rectifier," 8th International Conference on Power Electronics ECCE Asia, Jeju, 2011, pp. 2704-2708.

- [1.33] L. A. Garcia Rodriguez, V. Jones, A. R. Oliva, A. Escobar-Mejía and J. C. Balda, "A New SST Topology Comprising Boost Three-Level AC/DC Converters for Applications in Electric Power Distribution Systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 2, pp. 735-746, June 2017

- [1.34] B. Zhao, Q. Yu and W. Sun, "Extended-Phase-Shift Control of Isolated Bidirectional DC– DC Converter for Power Distribution in Microgrid," in *IEEE Trans. on Power Electronics*, vol. 27, no. 11, pp. 4667-4680, Nov. 2012.

- [1.35] L. M. Faulkenberry and W. Coffer, Electrical Power Distribution and Transmission Englewood Cliffs, NJ: Prentince Hall, 1996.

- [1.36] T. Gonen, Electric Power Distribution System Engineering, Second Edition. Boca Raton, FL: CRC Press Taylor & Taylor Group, 2008.

- [1.37] W. G. Hurley, W.H. Wölfle, Transformers and Inductors for Power Electronics: Theory, Design and Applications, 1st ed., Wiley, 2013.

- [1.38] C. William, T. McLyman, Transformer and Inductor Design Handbook, 4th ed., Taylor & Francis Group, 2011.

- [1.39] W.G. Hurley, W. H. Wöfle, J. G. Breslin, "Optimized transformer design: Inclusive of highfrequency effects," in *IEEE Trans. on Power Electronics*, vol. 13, no. 4, pp. 651-659, July 1998

- [1.40] G. Ortiz, J. Biela, J. W. Kolar, "Optimized design of medium frequency transformers with high isolation requirements," in *Proceeding of the 36th IEEE Industrial Electronics Society Conference*, IECON 2010, pp. 631-638, Nov. 2010.

- [1.41] T. Kauder and K. Hameyer, "Performance Factor Comparison of Nanocrystalline, Amorphous, and Crystalline Soft Magnetic Materials for Medium-Frequency Applications," in *IEEE Trans. on Magnetics*, vol. 53, no. 11, pp. 1-4, Nov. 2017.

# NEW ISOLATED AC-DC POWER CONVERTER TOPOLOGY WITH REDUCED NUMBER OF SWITCHES FOR HIGH-INPUT VOLTAGE AND HIGH-OUTPUT CURRENT APPLICATIONS

O. Aldosari, L. A. Garcia Rodriguez, D. C. Rojas and J. C. Balda, "A New Isolated AC-DC Power Converter Topology with Reduced Number of Switches for High-Input Voltage and High-Output Current Applications," *2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia)*, Busan, Korea (South), 2019, pp. 1-8.

### Abstract

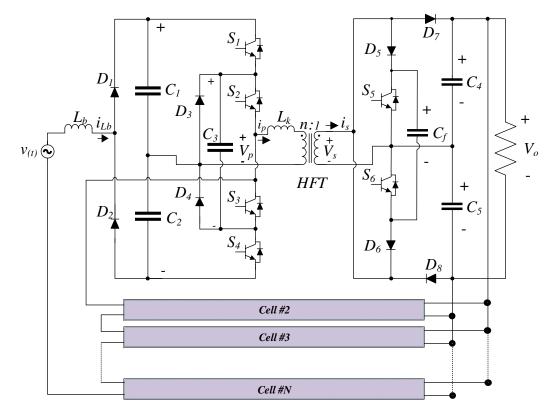

The main objective of this research work is to develop a new low-cost isolated three-level acdc power converter topology that is suitable for applications having high input ac voltages and high output currents; for example, hybrid (ac-dc) microgrids or offshore wind farms. Existing three-level converter topologies convert ac power to dc power while maintaining requirements set by international standards for power conversion. These types of converters have significant conduction losses due to high currents in the low-voltage side and high costs, particularly when using several devices in series or in parallel to achieve high-voltage and high-power levels. The proposed topology replaces the conventional three-level converters in the low-voltage side by only two controlled devices and four diodes while still maintaining the basic functionality of a threelevel converter. Simulation results for a 87.5-kW case study and experimental results on a 250-W scale-down prototype demonstrate the feasibility of the proposed ideas.

# **2.1 Introduction**

Isolated ac-dc unidirectional power converters are commonly used to convert distribution-level ac currents and voltages to supply dc loads such as electric vehicle battery charger systems [2.1],

hybrid ac-dc wind farms [2.2], telecommunication systems [2.3], dc-powered datacenters, and uninterrupted power supply (UPS). Unidirectional and bidirectional power converters are widely used in hybrid microgrid, where the input sources of these converters are usually interfaced with ac/dc loads through high frequency transformer [2.4]. Input power factor correction (PFC), low total harmonic distortion (THD) and output voltage regulations are usually the minimum requirements for isolated ac-dc power converters [2.3]. The international standard IEC 61000-3-2:2018 [2.5] requires that the harmonic contents of the input current should be reduced to specified levels; these are normally achieved by implementing the so-called PFC techniques [2.5],[2.6].

Preferred features are also symmetrical voltage distribution across semiconductors devices on the high-voltage side, and current sharing between devices on the low-voltage side to minimize power conduction losses and reduce current and voltage ratings [2.7]. However, preserving high efficiency and high power density along with the previous requirements continues to be a top challenge among the scientific community [2.7].

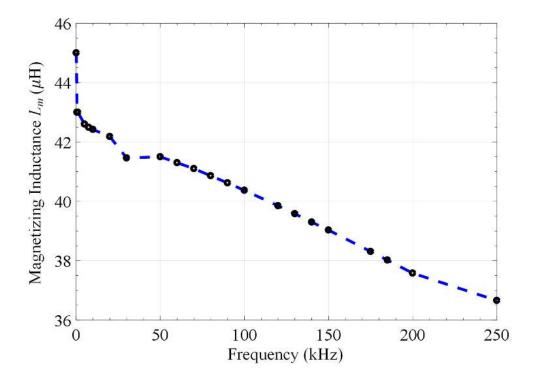

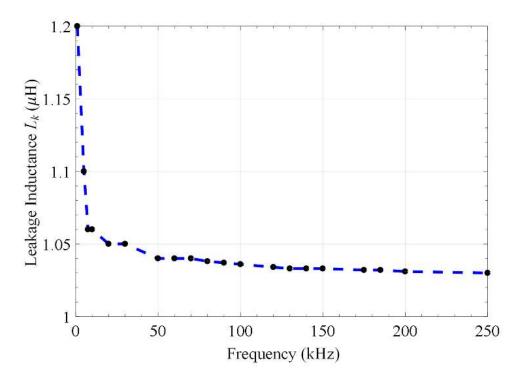

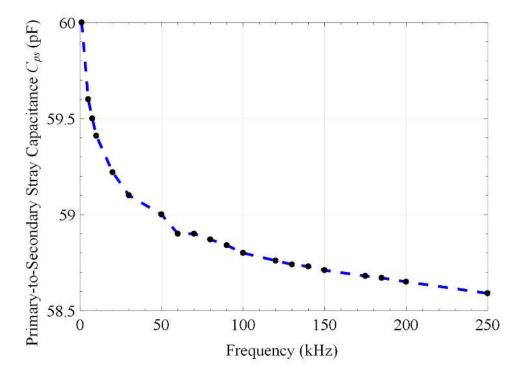

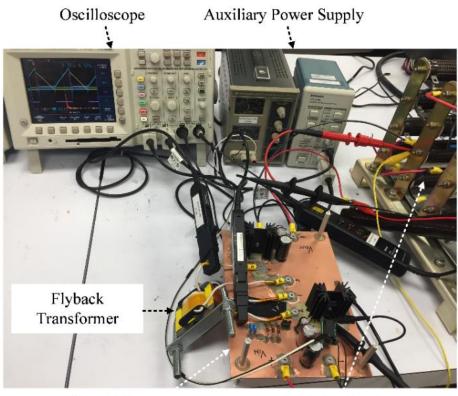

Converter applications with high-voltage ac inputs and low-voltage dc outputs (load side), such as chargers for electrical vehicles [2.8], requires multiple converters connected in series at the high-voltage side and in parallel at the low-voltage side. The controlled switches in the high- and low-voltage sides are used to maintain the primary dc-bus voltage within a certain tolerance, regulate the output voltage and control the delivered output power [2.9].