# A Three-Phase Active Rectifier Topology for Bipolar DC Distribution

Yitong Li, Adrià Junyent-Ferré, Member, IEEE, and Joan-Marc Rodriguez-Bernuz, Student Member, IEEE

Abstract-A new three-phase active rectifier topology is proposed for bipolar dc distribution, which can achieve the independent dc-pole control, with only one two-level voltage source converter and an ac-side grounding inductor. The averaged large-signal model and linearized small-signal model of the rectifier are derived in the stationary reference frame. Moreover, a control system is proposed with proper controller parameters. Besides, the rectifier is tested on an experiment platform. Comprehensive experiment results are given and analyzed to validate the function of the proposed rectifier under different operation conditions, including the rectifier start-up performance, rectifier dynamics with unbalanced dc loads for two poles, and rectifier dynamics with asymmetrical dc voltages for two poles. Finally, the proposed rectifier is compared with other two existing ac-dc conversion approaches, in terms of required number and rating of components as well as power losses with different load imbalance levels, which further highlight some potential benefits of the proposed topology.

*Index Terms*—AC-DC power converters, current control, inductors, modeling, power distribution.

### I. INTRODUCTION

The use of dc in high power applications is growing over the years as better power semiconductors become available and potential solutions to the main technical challenges of dc power systems (e.g. efficient ac-dc [1] and dc-dc [2] conversion, fault dc current interruption [3]). For example, the voltage-source-converter high-voltage dc (VSC-HVDC) transmission technology has undergone a rapid growth over the past decade [1], and low-voltage dc (LVDC) is used in kilowatt-scale applications for power trains [4] and charging systems in electric vehicles [5]. With the number of power-electronic-interfaced loads and generation systems increasing over the years, the idea of using dc in low-voltage distribution is gaining interest. Some of the potential benefits of the dc distribution are [6]-[13]: (a) no need for reactive current; (b) easier interfacing of certain loads such as LED lighting, battery storage, variable speed drives, and photovoltaic; (c) more power-dense converters; and (d) simpler voltage regulation and power balancing control.

1

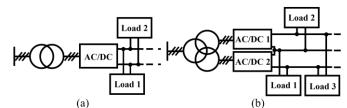

Fig. 1. Examples of dc distribution systems. (a) Unipolar dc systems. (b) Bipolar dc systems.

Fig. 2. Two-level voltage-source converter with a voltage balancer.

There are two types of dc distribution systems [13]: unipolar distribution and bipolar distribution, as shown in Fig. 1. This paper focuses on the bipolar system due to its prominent advantages. A bipolar dc system can provide different voltage levels to loads in a similar way as a three-phase ac system does [13]. Meanwhile, the reliability is increased due to the two available poles [9], [11]. Moreover, the grounding for bipolar distribution is also better and simpler than that of the unipolar distribution, because the faults can be easily detected and quickly cleared, and an unambiguous pole-to-ground voltage can be defined [13], [14].

However, as shown in Fig. 1(b), a bipolar dc system is normally implemented using two rectifiers in series at dc side in order to handle possible unbalanced loads. This in turns requires double secondary windings in the transformer rated to withstand a dc voltage offset caused by the series connection. Some novel ideas have been proposed to solve this problem in [5], [11], [15], [16]. For these approaches, one converter is used only, however, with the help of a voltage balancer (or the forth bridge), which still requires extra power switches, as shown in Fig. 2. Besides, the voltage balancer also consumes power and needs extra auxiliary systems. Here, a new rectifier topology is proposed, which is constructed based on a two-level voltage-source converter (VSC) with an ac-side grounding reactor, as shown later in Section II.

This paper is organized as follows: Section II introduces the proposed rectifier topology. Section III gives the detailed

This work was supported by the Engineering and Physical Sciences Research Council under Grant EP/N034570/1.

The authors are with the Department of Electrical and Electronic Engineering, Imperial College London, South Kensington Campus, London SW7 2AZ, UK. (e-mail: yitong.li15@imperial.ac.uk; adria.junyent-ferre@ imperial.ac.uk; j.rodriguez15@imperial.ac.uk).

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

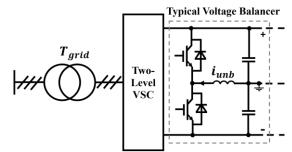

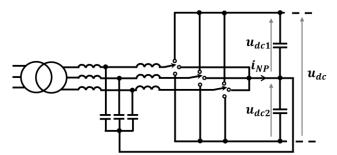

Fig. 3. Proposed rectifier topology.

derivation of the rectifier large- and small-signal models, followed by a proposed control system. The experiment results of the proposed rectifier are illustrated and analyzed in Section IV. Then in Section V, the proposed rectifier is compared with other two existing ac-dc conversion approaches for bipolar dc distribution.

#### II. RECTIFIER TOPOLOGY OVERVIEW

The proposed rectifier topology is shown in Fig. 3. The basic idea is to provide a current-injection path from the ac side to the dc-side neutral line by a grounding inductor (i.e.  $L_g$ ), so that the dc bus voltages for positive and negative poles (i.e.  $u_{dc1}$  and  $u_{dc2}$ ) can be controlled independently. When the loads are perfectly balanced, the rectifier behaves like a conventional active rectifier and no dc current is injected through the grounding reactor. When the loads are unbalanced, zero-sequence dc current flows through the grounding reactor in order to maintain the voltage balance between two dc poles.

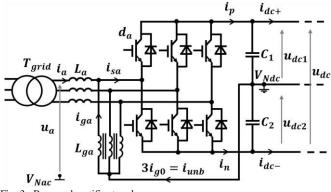

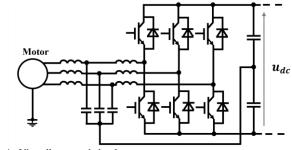

It is worth noting that the proposed topology has certain similarities with the one proposed in [17], [18], as shown in Fig. 4, where the ac side is connected to the middle point of dc bus by using capacitors. This topology provides a path for the high-frequency current in order to alleviate the dv/dt stress at motor terminals. Besides, the grounding capacitors can also be used to help with the balance of dc-bus capacitors in a three-level neutral-point-clamped (NPC) VSC [19], as shown in Fig. 5. However, when feeding unbalanced dc loads, compared with the dc path given by the grounding inductor (Fig. 3), the dc current in the NPC VSC (Fig. 5) cannot flow through the virtually-grounded path due to the blocking of capacitors, and has to be injected through the clamped-neutral point (i.e.  $i_{NP}$ ). But as discussed in [5], [20], [21], for ensuring a high modulation index and avoiding the over modulation, the unbalanced power provided by  $i_{NP}$  is quite limited, which makes the NPC VSC only possible to handle the imbalance of dc-bus capacitors, but unfit for the bipolar operation with unbalanced dc loads, unless a forth bridge is added.

#### III. RECTIFIER MODEL AND CONTROL SYSTEM

Pulse width modulation (PWM) is widely used to generate the switching signals in VSCs, which is also used for the

Fig. 4. Virtually-grounded voltage-source converter.

Fig. 5. Virtually-grounded three-level voltage-source converter.

proposed rectifier topology in this paper. Different modelling techniques for three-phase two-level PWM VSCs have been discussed in the past [22]-[24]. These approaches are often originally meant for VSCs where the zero-sequence current could be considered to be zero. However, the proposed rectifier in Fig. 3 has an ac-side grounding reactor connected to the dc bus, which enables the zero-sequence current to flow from the branches of the rectifier. This makes the aforementioned models unfit. Hence, the large- and small-signal models of the proposed rectifier are derived next.

# A. Stationary Reference Frame

Three variable reference frames are normally used when analyzing the dynamics of three-phase VSCs and designing their controllers [25]: natural (*abc*) frame, stationary reference ( $\alpha\beta\theta$ ) frame, and synchronous rotating (*dq* $\theta$ ) frame. The operation of the proposed rectifier requires zero-sequence current control through a grounding reactor, which benefits the use of the  $\alpha\beta\theta$  and *dq* $\theta$  variables over *abc*. Further, *dq* $\theta$  control requires the cross decoupling of currents in *d*-axis and *q*-axis, but the zero-sequence current in *dq* $\theta$  frame is exactly same to that of  $\alpha\beta\theta$  frame. This gives no superiority but more complexities to *dq* $\theta$  frame. Therefore,  $\alpha\beta\theta$  frame will be used for the current control. A *PR* controller can be used to eliminate the tracking error of the sinusoidal current in  $\alpha\beta\theta$  frame [26].

#### B. Voltage Equations for Source Inductors

The reference directions of currents and voltages are displayed in Fig. 3. (For the ac side, only the physical quantities of phase a are demonstrated.)

If the source inductors for three phases are exactly same, i.e.  $L_a = L_b = L_c = L$  and  $R_a = R_b = R_c = R$ , then the average voltage equations for them are

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

$$\begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix} = R \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + \begin{bmatrix} d_a \\ d_b \\ d_c \end{bmatrix} u_{dc} - \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} u_{dc2} + \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} V_N$$

(1)

where  $d_a$ ,  $d_b$ , and,  $d_c$  are the duty cycles for three-phase high-side power switches;  $V_N = V_{Ndc} - V_{Nac}$  is the voltage difference between the neutral points of dc and ac sides. By adding the three-phase equations together, the following expression is found:

$$\sum_{k=a,b,c} u_{k} = R \sum_{k=a,b,c} i_{k} + L \frac{d}{dt} \sum_{k=a,b,c} i_{k} + u_{dc} \sum_{k=a,b,c} d_{k} - 3u_{dc2} + 3V_{N}$$

(2)

Further, if the grid-interface transformer is in delta connection (or in star connection with a floating neutral) on the converter side, the transformer will not have the zero-sequence current, i.e.  $i_0 = 0$ , which leads to

$$V_N = -u_{dc}d_0 + u_{dc2} + u_0 \tag{3}$$

where  $d_0$  is the zero-sequence duty cycle for each high-side power switch; and  $u_0$  is the zero-sequence grid voltage. The voltage equations for source inductors can be re-written by combining (1) and (3):

$$\begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix} = R \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} + \begin{bmatrix} d_a - d_0 \\ d_b - d_0 \\ d_c - d_0 \end{bmatrix} u_{dc} + \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} u_0$$

(4)

By applying the Clarke transformation to this equation, voltage equations in  $\alpha\beta\theta$  frame are obtained as

$$\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = R \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} d_{\alpha} \\ d_{\beta} \end{bmatrix} u_{dc}$$

(5)

where the zero-sequence equation is removed as  $i_0 = 0$ .

## C. Voltage Equations for Grounding Inductors

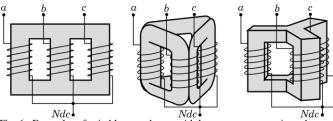

Clearly, grounding inductors would see the full ac voltages and hold sustained ac currents, which would incur unnecessary losses. Increasing the inductance value is a natural idea to limit these currents. However, large inductance also results in very slow response of the zero-sequence current, which has negative effects for the current injection and the control of the two dc poles. Besides, if three independent inductors were used, the need to carry high dc current would make their core sizing costly due to the high dc flux. Alternatively, a coupled structure is used for the grounding reactor, i.e. the three-phase windings are wound at a balanced three-phase magnetic core, as shown in Fig. 6 [27]. In this case, the inductor core cannot carry the

3

Fig. 6. Examples of suitable core shapes with low zero-sequence impedance.

zero-sequence dc flux, which reduces the chances for core saturation, similarly to what happens in the design of cores for dc chokes. Meanwhile, the inductance of the zero sequence can be much lower than those of  $\alpha$  and  $\beta$  sequences. The inductance matrix for the coupled reactor is of the form:

$$L_{g,abc} = \begin{bmatrix} L_g & -M_g & -M_g \\ -M_g & L_g & -M_g \\ -M_g & -M_g & L_g \end{bmatrix}$$

(6)

By applying the Clarke transformation,

$$L_{g,\alpha\beta0} = \begin{bmatrix} L_{g\alpha} & 0 & 0\\ 0 & L_{g\beta} & 0\\ 0 & 0 & L_{g0} \end{bmatrix} = \begin{bmatrix} L_g + M_g & 0 & 0\\ 0 & L_g + M_g & 0\\ 0 & 0 & L_g - 2M_g \end{bmatrix}$$

(7)

Similarly, the winding resistors in *abc* and  $\alpha\beta\theta$  frames are represented by  $R_{g,abc}$  and  $R_{g,\alpha\beta0}$ , respectively.

The average voltage equations for coupled grounding inductors are

$$\begin{bmatrix} 0\\0\\0 \end{bmatrix} = R_{g,abc} \begin{bmatrix} i_{ga}\\i_{gb}\\i_{gc} \end{bmatrix} + L_{g,abc} \frac{d}{dt} \begin{bmatrix} i_{ga}\\i_{gb}\\i_{gc} \end{bmatrix} + u_{dc} \begin{bmatrix} d_a - \frac{1}{2}\\d_b - \frac{1}{2}\\d_c - \frac{1}{2} \end{bmatrix} + \frac{1}{2} \Delta u \begin{bmatrix} 1\\1\\1 \end{bmatrix}$$

(8)

with

$$\Delta u = u_{dc1} - u_{dc2} \tag{9}$$

By applying the Clarke transformation,

$$\begin{bmatrix} 0\\0\\0 \end{bmatrix} = R_{g,\alpha\beta0} \begin{bmatrix} i_{g\alpha}\\i_{g\beta}\\i_{g0} \end{bmatrix} + L_{g,\alpha\beta0} \frac{d}{dt} \begin{bmatrix} i_{g\alpha}\\i_{g\beta}\\i_{g0} \end{bmatrix} + u_{dc} \begin{bmatrix} d_{\alpha}\\d_{\beta}\\d_{0} - \frac{1}{2} \end{bmatrix} + \begin{bmatrix} 0\\0\\\frac{1}{2}\Delta u \end{bmatrix}$$

(10)

When ignoring the switching harmonics of  $i_{g0}$  and the

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

TABLE I

AVERAGED LARGE-SIGNAL EQUATIONS IN STATIONARY REFERENCE FRAME

Voltage Equations for

$\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = R \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} d_{\alpha} \\ d_{\beta} \end{bmatrix} u_{dc}$

Source Inductors

$\begin{bmatrix} i \\ i_{\beta} \end{bmatrix} = \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} i_{\alpha} \\ d_{\beta} \end{bmatrix} \begin{bmatrix} u_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} i_{\alpha} \\ d_{\beta} \end{bmatrix} \begin{bmatrix} u_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} \begin{bmatrix} u_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} \begin{bmatrix} u_{\alpha} \\ i_{\beta} \end{bmatrix} + \begin{bmatrix} i_{\alpha} \\ i_{\alpha} \end{bmatrix} +$

| Source Inductors                             | $\begin{bmatrix} u_{\beta} \end{bmatrix} \xrightarrow{i} \begin{bmatrix} i_{\beta} \end{bmatrix} \xrightarrow{i} \begin{bmatrix} d_{t} \end{bmatrix} \xrightarrow{i} \begin{bmatrix} d_{t} \end{bmatrix} \xrightarrow{i} \begin{bmatrix} d_{t} \end{bmatrix} \xrightarrow{i} \begin{bmatrix} d_{t} \end{bmatrix}$                                                   |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage Equations for<br>Grounding Inductors | $\begin{bmatrix} 0\\0\\0\end{bmatrix} = R_{g,\alpha\beta0} \begin{bmatrix} i_{g\alpha}\\i_{g\beta}\\i_{g0}\end{bmatrix} + L_{g,\alpha\beta0} \frac{d}{dt} \begin{bmatrix} i_{g\alpha}\\i_{g\beta}\\i_{g0}\end{bmatrix} + u_{dc} \begin{bmatrix} d_{\alpha}\\d_{\beta}\\d_{0} - \frac{1}{2} \end{bmatrix} + \begin{bmatrix} 0\\0\\\frac{1}{2}\Delta u \end{bmatrix}$ |

| Current Equations for<br>High-Side Capacitor | $C_1 \frac{du_{dc1}}{dt} = i_p - i_{dc+}$ with $i_p = 3d_0 i_{s0} + \frac{3}{2} (d_\alpha i_{s\alpha} + d_\beta i_{s\beta})$                                                                                                                                                                                                                                        |

|                                              |                                                                                                                                                                                                                                                                                                                                                                     |

| Current Equations for                        | $-C_2 \frac{du_{dc2}}{dt} = i_n - i_{dc-}$ with $i_n = 3i_{g0} - i_p$                                                                                                                                                                                                                                                                                               |

| Low-Side Capacitor                           | $\frac{dt}{dt}$                                                                                                                                                                                                                                                                                                                                                     |

TABLE II Linearized Small-Signal Equations in Stationary Reference Frame

|                                              | LINEARIZED SMALL-SIGNAL LQUATIONS IN STATIONART REFERENCE FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Voltage Equations for<br>Source Inductors    | $ \begin{bmatrix} \hat{u}_{\alpha} \\ \hat{u}_{\beta} \end{bmatrix} = \begin{bmatrix} R_{\alpha} & 0 \\ 0 & R_{\beta} \end{bmatrix} \begin{bmatrix} \hat{i}_{\alpha} \\ \hat{i}_{\beta} \end{bmatrix} + \begin{bmatrix} L_{\alpha} & 0 \\ 0 & L_{\beta} \end{bmatrix} \frac{d}{dt} \begin{bmatrix} \hat{i}_{\alpha} \\ \hat{i}_{\beta} \end{bmatrix} + U_{dc} \begin{bmatrix} \hat{s}_{\alpha} \\ \hat{s}_{\beta} \end{bmatrix} + \hat{u}_{dc} \begin{bmatrix} S_{\alpha} \\ S_{\beta} \end{bmatrix} $                                                                                                                                                          |  |  |  |

| Voltage Equations for<br>Grounding Inductors | $\begin{bmatrix} 0\\0\\0 \end{bmatrix} = \begin{bmatrix} R_{g\alpha} & 0 & 0\\0 & R_{g\beta} & 0\\0 & 0 & R_{g0} \end{bmatrix} \begin{bmatrix} \hat{i}_{g\alpha} + I_{g\alpha}\\\hat{i}_{g\beta} + I_{g\beta}\\\hat{i}_{g0} + I_{g0} \end{bmatrix} + \begin{bmatrix} L_{g\alpha} & 0 & 0\\0 & L_{g\beta} & 0\\0 & 0 & L_{g0} \end{bmatrix} \frac{d}{dt} \begin{bmatrix} \hat{i}_{\alpha}\\\hat{i}_{\beta\beta}\\\hat{i}_{g0} \end{bmatrix} + U_{dc} \begin{bmatrix} S_{\alpha}\\S_{\beta}\\S_{0} \end{bmatrix} + U_{dc} \begin{bmatrix} S_{\alpha}\\S_{\beta}\\S_{0} \end{bmatrix} + \begin{bmatrix} 0\\0\\\frac{1}{2}(\Delta\hat{u} + \Delta U) \end{bmatrix}$ |  |  |  |

| Current Equations for<br>High-Side Capacitor | $C_{1}\frac{d\hat{u}_{dc1}}{dt} = \hat{i}_{p1} + \hat{i}_{p2} - \hat{i}_{dc+} \text{ with } \begin{cases} \hat{i}_{p1} = 3(S_{0} + \frac{1}{2})\hat{i}_{g0} + \frac{3}{2}\left[S_{\alpha}(\hat{i}_{\alpha} + \hat{i}_{g\alpha}) + S_{\beta}(\hat{i}_{\beta} + \hat{i}_{g\beta})\right] \\ \hat{i}_{p2} = 3\hat{s}_{0}I_{g0} + \frac{3}{2}\left[\hat{s}_{\alpha}(I_{\alpha} + I_{g\alpha}) + \hat{s}_{\beta}(I_{\beta} + I_{g\beta})\right] \end{cases}$                                                                                                                                                                                                         |  |  |  |

| Current Equations for<br>Low-Side Capacitor  | $-C_2 \frac{d\hat{u}_{dc2}}{dt} = \hat{\iota}_{n1} + \hat{\iota}_{n2} - \hat{\iota}_{dc-}  \text{with}  \begin{cases} \hat{\iota}_{n1} = 3\hat{\iota}_{g0} - \hat{\iota}_{p1} \\ \hat{\iota}_{n2} = 0 - \hat{\iota}_{p2} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

zero-sequence inner resistance  $R_{g0}$  of the grounding inductor, the steady-state relationship between  $d_0$  and  $\Delta u$  can be derived as

$$d_0 = \frac{1}{2} - \frac{\Delta u}{2u_{dc}} \tag{11}$$

which leads to  $d_0 = 0.5$  at steady state if no dc voltage imbalance is desired (i.e.  $\Delta u = 0$ ).

## D. Current Equations for DC Capacitors

The average current equation for the high-side capacitor is

$$C_1 \frac{du_{dc1}}{dt} = i_p - i_{dc+}$$

(12)

with

$$i_p = d_a i_{sa} + d_b i_{sb} + d_c i_{sc} \tag{13}$$

For transferring this current equation in  $\alpha\beta 0$  frame, we note that

$$i_{p} = \begin{bmatrix} d_{a} \\ d_{b} \\ d_{c} \end{bmatrix}^{T} \cdot \begin{bmatrix} i_{sa} \\ i_{sb} \\ i_{sc} \end{bmatrix} = \begin{bmatrix} d_{a} \\ d_{b} \\ d_{c} \end{bmatrix}^{T} \left( C_{3s \to 2s}^{-1} C_{3s \to 2s} \right) \begin{bmatrix} i_{sa} \\ i_{sb} \\ i_{sc} \end{bmatrix}$$

(14)

where  $C_{3s \rightarrow 2s}$  is the matrix for the Clarke transformation. By investigating the matrix  $C_{3s \rightarrow 2s}^{-1}$ , we get

$$\left\{ (C_{3s \to 2s}^{-1})^T \begin{bmatrix} d_a \\ d_b \\ d_c \end{bmatrix} \right\}^T = \frac{3}{2} \begin{bmatrix} d_a \\ d_\beta \\ 2d_0 \end{bmatrix}^T$$

(15)

Therefore, the current equation in  $\alpha\beta 0$  frame is

$$C_{1} \frac{du_{dc1}}{dt} = \frac{3}{2} \begin{bmatrix} d_{\alpha} \\ d_{\beta} \\ 2d_{0} \end{bmatrix}^{T} \cdot \begin{bmatrix} i_{s\alpha} \\ i_{s\beta} \\ i_{s0} \end{bmatrix} - i_{dc+}$$

$$= 3d_{0}i_{s0} + \frac{3}{2} (d_{\alpha}i_{s\alpha} + d_{\beta}i_{s\beta}) - i_{dc+}$$

(16)

Similarly, the current equation for low-side capacitor can be derived as

$$-C_2 \frac{du_{dc2}}{dt} = i_n - i_{dc-} \tag{17}$$

with

$$i_n = 3i_{g0} - i_p = 3i_{g0} - d_a i_{sa} - d_b i_{sb} - d_c i_{sc}$$

(18)

and in  $\alpha\beta\theta$  frame,

$$-C_{2} \frac{du_{dc2}}{dt} = 3i_{g0} - \frac{3}{2} \begin{bmatrix} d_{\alpha} \\ d_{\beta} \\ 2d_{0} \end{bmatrix}^{T} \cdot \begin{bmatrix} i_{s\alpha} \\ i_{s\beta} \\ i_{s0} \end{bmatrix} - i_{dc-}$$

$$= 3(1 - d_{0})i_{s0} - \frac{3}{2} (d_{\alpha}i_{s\alpha} + d_{\beta}i_{s\beta}) - i_{dc-}$$

(19)

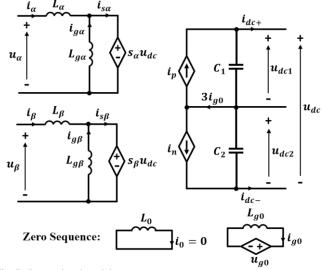

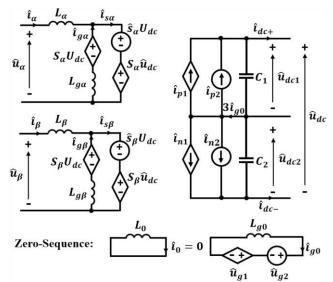

# E. Conclusions of Rectifier Modelling

The averaged large-signal equations in (5), (10), (16), and (19) are re-summarized in Table I. By applying the perturbation and linearization [28] to these equations, the linearized small-signal equations can be obtained, as summarized in Table

Fig. 7. Large-signal model.

## II.

In order to facilitate the control system design and the rectifier analysis, the zero-biased duty cycle s (i.e. with a range from -0.5 to 0.5) is used to replace the duty cycle d (i.e. with a range from 0 to 1). The relationship between them is

$$\begin{cases} d_a = s_a + 0.5 \\ d_b = s_b + 0.5 \\ d_c = s_c + 0.5 \end{cases} \quad \text{and} \quad \begin{cases} d_a = s_a \\ d_\beta = s_\beta \\ d_0 = s_0 + 0.5 \end{cases}$$

(20)

Based on the derived equations, the large- and small-signal models in  $\alpha\beta0$  frame are constructed, as shown in Fig. 7 and 8, respectively, where

$$i_{p} = 3\left(s_{0} + \frac{1}{2}\right)i_{g0} + \frac{3}{2}\left[s_{\alpha}(i_{\alpha} + i_{g\alpha}) + s_{\beta}(i_{\beta} + i_{g\beta})\right]$$

$$i_{n} = 3i_{g0} - i_{p}$$

$$u_{g0} = s_{0}u_{dc} + \frac{1}{2}\Delta u$$

(21)

and

$$\hat{i}_{p1} = 3\left(S_{0} + \frac{1}{2}\right)\hat{i}_{g0} + \frac{3}{2}\left[S_{\alpha}(\hat{i}_{\alpha} + \hat{i}_{g\alpha}) + S_{\beta}(\hat{i}_{\beta} + \hat{i}_{g\beta})\right]$$

$$\hat{i}_{p2} = 3\hat{s}_{0}I_{g0} + \frac{3}{2}\left[\hat{s}_{\alpha}(I_{\alpha} + I_{g\alpha}) + \hat{s}_{\beta}(I_{\beta} + I_{g\beta})\right]$$

$$\hat{i}_{n1} = 3\hat{i}_{g0} - \hat{i}_{p1}$$

$$\hat{i}_{n2} = 0 - \hat{i}_{p2}$$

$$\hat{u}_{g1} = S_{0}\hat{u}_{dc} + \frac{1}{2}\Delta\hat{u}$$

$$\hat{u}_{g2} = S_{0}U_{dc} + \frac{1}{2}\Delta U + \hat{s}_{0}U_{dc}$$

(22)

# F. Proposed Control Structure

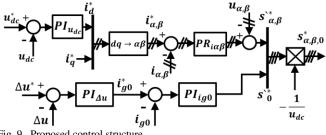

Based on the linearized small-signal model, a control structure is proposed, as shown in Fig. 9, which includes: (a) an

Fig. 8. Small-signal model.

Fig. 9. Proposed control structure.

outer loop for the dc-bus voltage control, with an inner loop for the ac-inductor current control, which generate the duty cycles in  $\alpha$  and  $\beta$  sequences; and (b) an outer loop for the voltage difference control of two dc poles, with an inner loop for the zero-sequence current control of the grounding inductor, which give the duty cycle in zero sequence. For the  $\alpha\beta$ -sequence current control, a controller with sufficient gain at both dc and ac-grid frequency should be used to eliminate the steady-state error for tracking the current reference. This can be achieved either with a PR [26] or a PIR controller. As for the zero-sequence current control, a non-zero resonant part should be added into a PI controller for the more reliable rectifier performance in practice, as shown later in Section IV.

In addition to that, a conventional phase locked loop (PLL) is used, for measuring the phase angle and angular frequency of the ac-grid voltages [29].

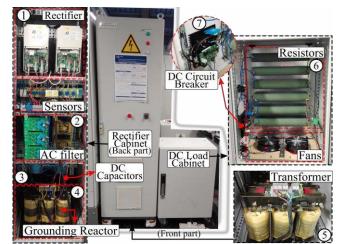

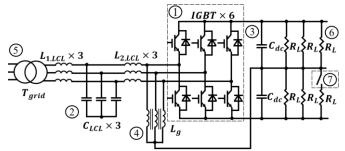

## IV. EXPERIMENT TEST

The experiment platform shown in Fig. 10 is used to test the proposed rectifier topology. A transformer is used to implement the coupled grounding inductor, due to its appropriate coupled structure. The schematic of the platform is shown in Fig. 11. For reducing the volume of the filter and improve the ac-grid power quality, an LCL filter rather than an L filter is used at the ac side. The parameters of the controllers and the test equipment are illustrated in Tables III and IV, respectively.

The rectifier is tested under three scenarios: (A) start-up with

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

Fig. 10. Experiment platform for the proposed rectifier test.

Fig. 11. Schematic of the experiment platform.

| TABLE III         |                                                                       |                                          |  |  |

|-------------------|-----------------------------------------------------------------------|------------------------------------------|--|--|

|                   | CONTROL PARAMETERS                                                    | 8                                        |  |  |

|                   | $PR_{i\alpha\beta}$ Alpha/Beta Sequence                               | PI <sub>ig0</sub> Zero Sequence          |  |  |

| Current           | $K_p = 10; K_r = 100;$                                                | $K_p = 30; K_i = 300$                    |  |  |

| Controller        | $K_{i} = 10$                                                          | $K_r = 10$                               |  |  |

| controller        | $\omega_r = 2\pi \cdot 50 \text{ rad/s}$                              | $\omega_r = 2\pi \cdot 50 \text{ rad/s}$ |  |  |

|                   | $\omega_c = 8 \text{ rad/s}$                                          | $\omega_c = 8 \text{ rad/s}$             |  |  |

|                   | $PI_{u_{dc}}$ DC Bus Voltage                                          | PlAu Voltage Balance                     |  |  |

| Voltage           | Regulation                                                            | for Two DC Poles                         |  |  |

| Controller        | $K_p = 0.8; K_i = 1.2$                                                | $K_p = 0.3; K_i = 0.6$                   |  |  |

| PLL<br>Controller | $PI_{PLL}$ : $K_p = 8.9, K_i = 1336$                                  |                                          |  |  |

| Others            | Switching Frequency $f_s = 10$ kHz<br>Sample Frequency $F_s = 10$ kHz |                                          |  |  |

| TABLE IV |  |   |  |   |  |  |  |  |

|----------|--|---|--|---|--|--|--|--|

|          |  | - |  | - |  |  |  |  |

| EXPERIMENT EQUIPMENT PARAMETERS |                                                                                                                                                                              |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AC-Grid Voltage                 | Line-to-Line RMS Voltage 415V                                                                                                                                                |  |  |  |

| AC-Grid<br>Transformer          | Tap Ratio 415V – 330V                                                                                                                                                        |  |  |  |

| LCL Filter                      | $ \begin{array}{l} L_{1,LCL} = 0.93  \mathrm{mH}, R_{1,LCL} = 0.3 \Omega \\ L_{2,LCL} = 2.3  \mathrm{mH}, R_{2,LCL} = 0.4 \Omega \\ C_{LCL} = 8.8  \mathrm{uF} \end{array} $ |  |  |  |

| Grounding Reactor               | $ \begin{array}{l} L_{g\alpha} = L_{g\beta} = 1.362H; \ L_{g0} = 13.231mH \\ R_{g\alpha} = R_{g\beta} = 644.013\Omega; \ R_{g0} = 1.281\Omega \end{array} $                  |  |  |  |

| DC Bus Capacitor                | $C_{dc} = 5305 \mu F$                                                                                                                                                        |  |  |  |

| DC Bus Rated<br>Voltage         | $V_{dc} = 600 \mathrm{V}$                                                                                                                                                    |  |  |  |

| DC Load                         | $R_L = 220\Omega$                                                                                                                                                            |  |  |  |

balanced dc loads; (B) dynamics with unbalanced dc loads; and (C) dynamics with asymmetrical dc voltages. The test results

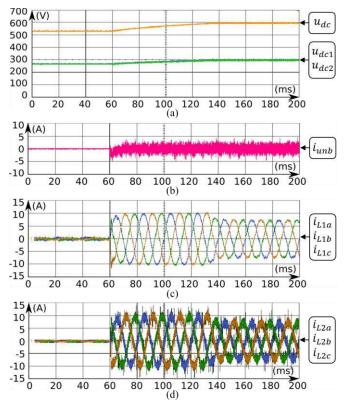

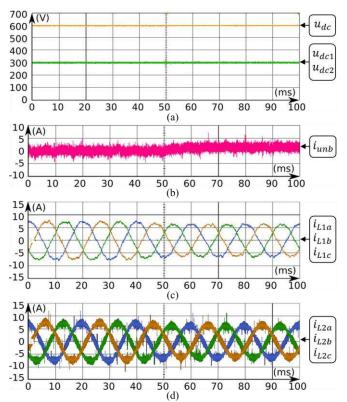

Fig. 12. Rectifier start-up performance with balanced dc loads. (a) DC bus voltages. (b) Total of injected three-phase zero-sequence currents. (c) Transformer-side inductor currents. (d) Converter-side inductor currents.

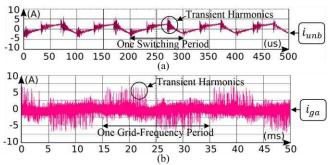

Fig. 13. Close-up plots of the currents flowing through the grounding inductor. (a) Total of three-phase currents. (b) One-phase current.

are presented and discussed next.

## A. Rectifier Start-Up with Balanced DC Loads

Fig. 12 displays the rectifier start-up performance with balanced dc loads. The starting sequence of the proposed rectifier is same as a conventional VSC: (a) the dc bus is pre-charged through diodes with current limiting resistors, followed by a controlled boost up to the rated dc voltage; and (b) the ac-side capacitors of the *LCL* filter are pre-charged by the grid transformer in order to track the transformer voltages before switching the IGBTs.

As shown in Fig. 12(a), at a certain point in time, the rectifier starts to boost the dc bus voltage from the pre-charged value (about 530V) to the rated value (600V). The voltages for two poles increase concurrently and they are balanced all the time. Besides, it is noticeable that the PWM switching of the IGBTs

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

Fig. 14. Rectifier dynamics with a step change of load imbalance from 0% to 20% by disconnecting one dc load of the negative pole. (a) DC bus voltages. (b) Total of injected three-phase zero-sequence currents. (c) Transformer-side inductor currents. (d) Converter-side inductor currents.

also causes ripples flowing through the grounding inductor, as shown in Fig. 12(b).

In Fig. 12(c) and (d), both the transformer- and converter-side inductor currents are controlled to their upper limits, so that the dc bus voltage can be boosted as fast as possible, while maintaining the current below the maximum rating of the converter. When finishing the voltage boost, ac currents fall back to their rated values quickly. Remarkably, the transformer-side currents hold much less harmonics than the converter-side currents, due to the *LCL* filter, which contributes to the high ac-grid power quality.

The neutral current flowing through the grounding inductor is illustrated in Fig. 13(a), which is the summation of three-phase currents and holds zero-sequence dc component and high-frequency harmonics only. Transient harmonics appear due to the switching event of each IGBT. All zero-sequence harmonics can be filtered easily due to their low magnitude and high frequency. The one-phase current of the grounding inductor is also displayed in Fig. 13(b), where the grid-frequency sinusoidal component can barely be seen because of the large inductance in  $\alpha\beta$  sequence.

# B. Rectifier Dynamics with Unbalanced DC Loads

The rectifier dynamics with a step change of dc loads are illustrated in Fig. 14 and 15. Initially, the rectifier operates with balanced dc loads. At a certain point in time in Fig. 14, one load of the negative dc pole is disconnected and a load imbalance of 20% is given. As for Fig. 15, all loads of the negative pole are

7

Fig. 15. Rectifier dynamics with a step change of load imbalance from 0% to 100% by disconnecting all dc loads of the negative pole. (a) DC bus voltages. (b) Total of injected three-phase zero-sequence currents. (c) Transformer-side inductor currents. (d) Converter-side inductor currents.

disconnected leading to a load imbalance of 100%. Upon removing the loads in both Fig. 14 and 15, the voltages of two dc poles are going to split because of the unbalanced dc-load current. Owing to the voltage balancing controller and zero-sequence current controller, the zero-sequence current is quickly regulated to its new steady state and makes the dc voltages balanced again (about 10ms in Fig. 14(b) and 15(b)). The voltage fluctuations in Fig. 14(a) and 15(a) are small enough to be hard to see in the figures. This not only shows the good dynamics of zero-sequence voltage and current controllers, but also validates the high voltage quality ensured by the proposed control structure. In Fig. 14(b) and (c) as well as Fig. 15(b) and (c), ac currents reduce and reach their new steady states within one sinusoidal period, which shows good performance of the  $\alpha\beta$ -sequence current controller.

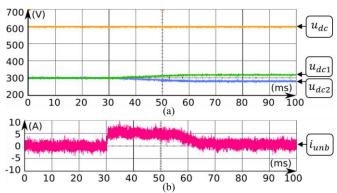

## C. Rectifier Dynamics with Asymmetrical DC Voltages

The proposed rectifier can work with asymmetrical dc voltages, by simply changing the value of  $\Delta u^*$  in the control structure in Fig. 9. Based on (11), a non-zero steady-state  $\Delta u$  requires a non-zero dc offset (i.e.  $s_0 = d_0 - 0.5 \neq 0$ ) of there-phase duty cycles. Hence, the over-modulation should be carefully avoided for this operation mode. As displayed in Fig. 16, at a certain instant, the value of  $\Delta u^*$  is changed from 0V to 40V. As a result, the outer-loop voltage balancing controller makes the inner-loop zero-sequence current controller absorb the current from the dc-side neutral line actively, which causes the voltage difference between two poles to increase steadily

This work is licensed under a Creative Commons Attribution 3.0 License. For more information, see http://creativecommons.org/licenses/by/3.0/.

Fig. 16. Rectifier operation with unbalanced dc voltages. (a) DC bus voltages. (b) Total of injected three-phase zero-sequence currents.

| TABLE V                       |  |  |  |  |  |  |

|-------------------------------|--|--|--|--|--|--|

| REQUIRED NUMBER OF COMPONENTS |  |  |  |  |  |  |

| Item Case 1 Case 2 Case 3     |  |  |  |  |  |  |

| Itelli       | Cube I     | 0400 =    | Cube b |

|--------------|------------|-----------|--------|

| Transformer  | 1 or 2     | 1         | 1      |

| Inductor     | 2          | 2         | 2      |

| Power Switch | 6 + 6 = 12 | 6 + 2 = 8 | 6      |

|              |            |           |        |

for around 35ms.

This operation is a natural generalization of the voltage balancing control and can obviously provide three different voltage levels and more flexibilities to the loads. The fourth rail system currently used in the London Underground is a typical application of the asymmetrical dc-bus voltage distribution [30].

## V. COMPARISON OF AC-DC CONVERSION APPROACHES

In previous sections, the proposed rectifier was analyzed and tested. Nevertheless, as mentioned earlier, two other existing ac-dc topologies are also available for the bipolar dc distribution, as shown in Fig. 1(b) and 2. In order to show the benefits of the proposed rectifier further, all three cases are compared in detail next: (a) Case 1 – two two-level VSCs; (b) Case 2 - one two-level VSC with a voltage balancer; (c) Case 3 - one two-level VSC with a grounding inductor, i.e. the topology proposed in this paper.

# A. Comparison of Required Number of Components

The characteristics of required number of components for all three cases are organized in Table V.

Cases 2 and 3 require one transformer each, while case 1 requires one transformer with two secondary windings and the insulation rated to withstand a dc voltage offset.

Regarding the inductors required in the converters, two three-phase inductors are needed in the two rectifiers of case 1. For case 2, besides the three-phase grid inductor, an extra balancing inductor is required by the voltage balancer. As for case 3, an extra three-phase grounding inductor is necessary.

As for the number of power switches, the proposed topology, i.e. case 3, only needs six power switches, which are less than the requirements for case 2 (eight power switches) and case 1 (twelve power switches). The ratings of these components are discussed next.

| TABLE VI                                                           |                                                                                                                 |                                                    |                                                                                                                                |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| REQUIRED RATING OF COMPONENTS                                      |                                                                                                                 |                                                    |                                                                                                                                |  |  |

| Item                                                               | Case 1                                                                                                          | Case 2                                             | Case 3                                                                                                                         |  |  |

| Grid Voltage:<br>$U_{ph,RMS}$                                      | $M\frac{u_{dc}}{4}\frac{1}{\sqrt{2}}$                                                                           | $M \frac{u_{dc}}{2} \frac{1}{\sqrt{2}}$            |                                                                                                                                |  |  |

| Current Rating of<br>Power Switch with<br>Balanced Loads: <i>I</i> |                                                                                                                 | $\frac{2\sqrt{2}}{3Mu}$                            | S <sub>ac</sub><br>Idc                                                                                                         |  |  |

| Voltage Rating of<br>Power Switch: U                               | 11                                                                                                              |                                                    |                                                                                                                                |  |  |

| Current Rating of L<br>Filter with Balanced<br>Loads: I            |                                                                                                                 | $\frac{2\sqrt{2}}{3Mu}$                            | S <sub>ac</sub><br>I <sub>dc</sub>                                                                                             |  |  |

| Sizing of <i>L</i> Filter: <i>L</i>                                | $\frac{u_{dc}}{4} \frac{\Delta t}{\Delta i_{ac}} \qquad \qquad \frac{u_{dc}}{2} \frac{\Delta t}{\Delta i_{ac}}$ |                                                    |                                                                                                                                |  |  |

| Current Rating of<br>Balancing/Grounding<br>Inductor: I            | -                                                                                                               | i <sub>unb</sub>                                   | $i_{unb} + i_{lphaeta}$                                                                                                        |  |  |

| Sizing of<br>Balancing/Grounding<br>Inductor: L                    | -                                                                                                               | $\frac{u_{dc}}{2} \frac{\Delta t}{\Delta i_{unb}}$ | $L_0 = \frac{u_{dc}}{2} \frac{\Delta t}{\Delta i_{g0}}$ $L_{\alpha\beta} = \frac{U_{ph,RMS}}{2\pi f_{ac} I_{\alpha\beta,RMS}}$ |  |  |

8

Note: *M* is the modulation index;  $S_{ac}$  is the total ac-side apparent power;  $u_{ac}$  is the positive-to-negative dc bus voltage;  $\Delta i$  indicates the corresponding current ripple; and  $f_{ac}$  is the ac-grid frequency.

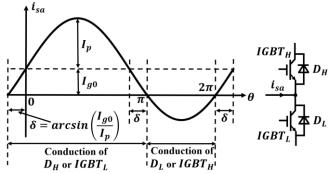

Fig. 17. Current flow analysis for phase a of the proposed rectifier.

#### B. Comparison of Required Rating of Components

The component ratings for all three cases are summarized in Table VI. The voltage and current ratings for case 2 are equivalent to those of a conventional two-level active rectifier. As for case 1, each rectifier requires almost half ac-grid voltage but same current as case 2, which leads to a worse conversion efficiency as shown later in Subsection V.C. By contrast in case 3, the ac-grid voltage might be around 15% lower than that of case 2 because of the inapplicability of third harmonics injection [31], which results in slightly higher currents in case 3 as well.

The inductor sizing equations for all three cases are also organized in Table VI. Regarding to L filters, the inductance value required by case 1 is only the half of that for case 2 or 3, due to its lower PWM voltages. As for the grounding inductor in case 3, the total zero-sequence current flowing through it is simply the unbalanced load current (i.e.  $i_{unb}$ ), which equals to the current of the balancing inductor of case 2. Besides, the zero-sequence grounding inductance of case 3 is also sized similarly to the balancing inductance of case 2. However,

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

9

|                        | I ABLE VII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                        | IGBT POWER LOSSES CALCULATIONS OF THE PROPOSED RECTIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                        | $P_{C,ph} = P_{C,IGBT,ph} + P_{C,D,ph}$ with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Conduction             | $\begin{cases} P_{C,IGBT,ph} = u_{CE0}(\underbrace{I_{IGBT,H,avg} + I_{IGBT,L,avg}}_{I_{IGBT,ph,avg}}) + r_{IGBT}(\underbrace{I_{IGBT,H,rms}^{2} + I_{IGBT,L,rms}^{2}}_{I_{IGBT,ph,rms}}) \\ P_{C,D,ph} = u_{D0}(\underbrace{I_{D,H,avg} + I_{D,L,avg}}_{I_{D,ph,avg}}) + r_{D}(\underbrace{I_{D,H,rms}^{2} + I_{D,L,rms}^{2}}_{I_{D,ph,rms}^{2}}) \\ I_{D,ph,avg} = \frac{I_{p}}{\pi} \sqrt{1 - \frac{I_{p}^{2}}{I_{p}^{2}}} + \frac{I_{g0}}{\pi} \arcsin\left(\frac{I_{g0}}{I_{p}}\right) - \frac{I_{p}M\cos(\phi)}{4} \\ I_{D,ph,avg} = \frac{I_{p}}{\pi} \sqrt{1 - \frac{I_{g0}^{2}}{I_{p}^{2}}} + \frac{I_{g0}}{\pi} \arcsin\left(\frac{I_{g0}}{I_{p}}\right) + \frac{I_{p}M\cos(\phi)}{4} \end{cases}$ |  |  |  |  |

| Losses                 | $\begin{cases} I_{IGBT,ph,rms}^{2} = I_{p}^{2} \left( \frac{1}{4} - \frac{2M\cos(\phi)}{3\pi} \sqrt{1 - \frac{I_{g0}^{2}}{l_{p}^{2}}} \right) + I_{g0}^{2} \left( \frac{1}{2} - \frac{M\cos(\phi)}{3\pi} \sqrt{1 - \frac{I_{g0}^{2}}{l_{p}^{2}}} \right) - \frac{I_{p}I_{g0}M\cos(\phi)}{\pi} \arcsin(\frac{I_{g0}}{l_{p}}) \\ I_{D,ph,rms}^{2} = I_{p}^{2} \left( \frac{1}{4} + \frac{2M\cos(\phi)}{3\pi} \sqrt{1 - \frac{I_{g0}^{2}}{l_{p}^{2}}} \right) + I_{g0}^{2} \left( \frac{1}{2} + \frac{M\cos(\phi)}{3\pi} \sqrt{1 - \frac{I_{g0}^{2}}{l_{p}^{2}}} \right) + \frac{I_{p}I_{g0}M\cos(\phi)}{\pi} \arcsin(\frac{I_{g0}}{I_{p}}) \end{cases}$                                                        |  |  |  |  |

|                        | $\frac{\left(\begin{array}{ccc} B_{p}B_{p}B_{p}B_{p}B_{p}B_{p}B_{p}B_{p}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Switching<br>Losses    | $P_{sw,ph} = P_{on,IGBT,ph} + P_{off,IGBT,ph} + 2P_{sw,D} \text{ with } \begin{cases} P_{off,IGBT,ph} = \frac{V_{cc}t_{fN}f_s}{12I_{CN}} \left( 2I_{g0}^2 + I_p^2 + \frac{8I_{CN}I_p}{\pi} \sqrt{1 - \frac{I_{g0}^2}{I_p^2}} + \frac{8I_{CN}I_{g0}}{\pi} \arcsin\left(\frac{I_{g0}}{I_p}\right) \right) \\ P_{sw,D} = \frac{1}{4}Q_{rr}V_{cc}f_s \end{cases}$                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Total Power            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Losses                 | $P_{loss,ph} = P_{C,ph} + P_{sw,ph};$ $P_{loss,total} = 3P_{loss,ph}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Auxiliary<br>Equations | $i_{sa} = I_p \sin(\theta) + I_{g0}$ and $s_a = \frac{1}{2}M\sin(\theta + \phi)$ or $d_a = \frac{1}{2}(M\sin(\theta + \phi) + 1)$ with $\theta = \omega t = 2\pi f_{ac}t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

TABLE VII

TABLE VIII PARAMETERS OF CM75TJ-24F TRENCH GATE DESIGN SIX IGBT MOD TM 75 AMPEPES/1200 VOLTS

| AMPERES/1200 VOL1S                                      |                                   |  |  |

|---------------------------------------------------------|-----------------------------------|--|--|

| Item                                                    | Value                             |  |  |

| IGBT on-state zero-current<br>collector-emitter voltage | $u_{CE0} = 1.3V$                  |  |  |

| IGBT on-state resistance                                | $r_{IGBT} = 6.7 \mathrm{m}\Omega$ |  |  |

| Diode on-state zero-current voltage                     | $u_{D0}=1.7V$                     |  |  |

| Diode on-state resistance                               | $r_D = 11.2 \mathrm{m}\Omega$     |  |  |

| Rated collector current                                 | $I_{CN} = 75A$                    |  |  |

| IGBT rated rise time                                    | $t_{rN} = 50ns$                   |  |  |

| IGBT rated fall time                                    | $t_{fN} = 300 ns$                 |  |  |

| Diode reverse recovery charge                           | $Q_{rr} = 3.1 \mu C$              |  |  |

TABLE IX PATED COMPARISON CONDITIONS

| RATED COMPARISON CONDITIONS         |                                                             |  |  |

|-------------------------------------|-------------------------------------------------------------|--|--|

| Item                                | Value                                                       |  |  |

| Positive-to-Negative DC-Bus Voltage | $U_{dc} = 600 \mathrm{V}$                                   |  |  |

| AC-Grid Frequency                   | $f_{ac} = 50$ Hz                                            |  |  |

| Switching frequency                 | $f_s = 10 \mathrm{kHz}$                                     |  |  |

| DC-Side Balanced Load Current       | $I_{bal} = 30A$                                             |  |  |

| DC-Side Unbalanced Load Current     | $I_{unb} = 0A$                                              |  |  |

| Modulation Index                    | M = 0.8                                                     |  |  |

| Active Power                        | $P_{ac,rated} \approx P_{dc,rated} = 600V \cdot 30A = 18kW$ |  |  |

| Reactive Power                      | $Q_{ac,rated} = 0$ Var                                      |  |  |

| Apparent Power                      | $S_{ac,rated} = 18$ kVA                                     |  |  |

compared with the balancing inductor in case 2 (e.g. a dc choke), the grounding inductor of case 3 should be three-phase coupled and the  $\alpha\beta$ -sequence inductance is required to be large enough to limit the  $\alpha\beta$ -sequence current and power losses, as explained earlier in Subsection III.C. As for the dc bus capacitors for all three cases, they can be sized similarly based on the ripple analysis in [32]-[34].

## C. Comparison of Power Losses

Based on [35], [36], the power losses of case 1 and case 2 can be obtained directly. For case 3, by analyzing the current flow in Fig. 17 and adapting the formulation in [35], [36], the power losses equations of IGBTs are derived and organized in Table VII.

For calculating the power losses, the parameters of "CM75TJ-24F Trench Gate Design Six IGBTMOD<sup>™</sup> 75 Amperes/1200 Volts" [37] are used, as summarized in Table VIII, which is also the IGBT used in the experiment test.

Further, the assumed rated comparison conditions are organized in Table IX.

For getting more reliable results, the losses of inductors (including ac-side L filters of three cases, the balancing inductor of case 2, and the grounding inductor of case 3) are also considered. The equivalent inner resistance for an L filter in one phase is evaluated with a rated efficiency of around 99%, as shown in Table X. Remarkably, the inner resistance of the L filter for case 1 is only the half of that for case 2 or 3, due to the lower inductance value and the probably shorter conductor, as explained in Subsection V.B and Table VI earlier. Besides, for case 2, it is assumed that the inner resistance of the balancing inductor equals to that of an L filter, according to the similar PWM voltages faced by both of them. Moreover, the losses of dc-bus capacitors are omitted. Further, it is temporarily assumed that the zero-sequence inner resistance (i.e.  $R_{in,Lq0}$ ) of the grounding inductor equals to  $R_{in,bal}$  of the balancing inductor, i.e. k = 1 in Table X, and the losses caused by the  $\alpha\beta$ -sequence currents are small enough to be ignored. These

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2017.2681740, IEEE Transactions on Power Electronics

| IABLE X           EQUIVALENT INNER RESISTORS OF INDUCTORS |                        |                                                                         |  |  |  |

|-----------------------------------------------------------|------------------------|-------------------------------------------------------------------------|--|--|--|

|                                                           | Item Value             |                                                                         |  |  |  |

| Case 1                                                    | For One-Phase L Filter | $R_{in,L,case1} = 0.015 \Omega$                                         |  |  |  |

| Case 2                                                    | For One-Phase L Filter | $R_{in,L,case2} = 0.03 \Omega$                                          |  |  |  |

|                                                           | For Balancing Inductor | $R_{in,Lbal} = 0.03 \Omega$                                             |  |  |  |

| Case 3                                                    | For One-Phase L Filter | $R_{in,L,case3} = 0.03 \Omega$                                          |  |  |  |

|                                                           | For Grounding Inductor | $R_{in,Lg0} = k \cdot R_{in,Lbal}$<br>where k is a positive coefficient |  |  |  |

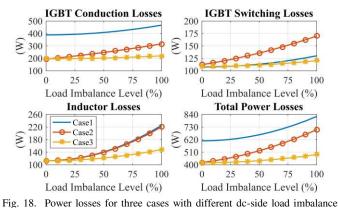

Fig. 18. Power losses for three cases with different dc-side load imbalan levels when modulation index M = 0.8 and  $R_{in,Lg0} = R_{in,Lbal}$ .

two assumptions will be discussed in detail later.

With the fixed modulation index value of 0.8, the power losses for all three cases with different dc-load imbalance levels are shown in Fig. 18. When the load imbalance increases (e.g. more and more dc loads are connected to the positive pole), the power losses of both cases 1 and 2 grow considerably. Specifically, 100% of load imbalance causes the power losses increase of 35.1% (213.6W) and 68.6% (287.8W) for cases 1 and 2, respectively. For case 1, the losses of two *L* filters and IGBT conduction losses contribute to the increase of power losses mainly. As for case 2, the switching losses and balancing inductor losses increase dramatically, caused by the rising current flowing through the voltage balancer. By contrast, for case 3, only a slight change of 17.1 % (71.4W) is noticed and the total power losses are lower than those of cases 1 and 2 for an almost arbitrary load imbalance.

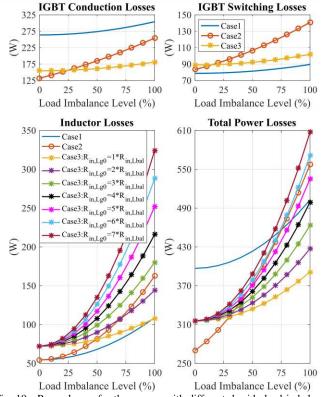

However, the third harmonics injection is not applicable for the proposed rectifier in case 3 due to the grounding reactor, which makes the maximum modulation index value of case 3 (i.e. " $M_{max} = 1$ ") lower than those of cases 1 and 2 (i.e. " $M_{max} = 1.15$ ") [31]. Besides, as explained in Subsection III.C, the  $\alpha\beta$ -sequence grounding inductance of case 3 should be large enough and would probably lead to a longer conductor, and therefore, a larger zero-sequence inner resistance than the balancing inductor in case 2, i.e.  $R_{in,Lg0} \ge R_{in,Lbal}$  and  $k \ge 1$ in Table X. Hence, the power losses with maximum modulation index values and different values of zero-sequence resistance of the grounding inductor are compared in Fig. 19. For balanced loads, the improved ac-grid voltage of case 2 makes its losses lower than case 3. By contrast, for the increase of the load imbalance, case 3 is found to be better under some conditions. Noticeably, the total IGBT losses of case 3 are lower than those

10

Fig. 19. Power losses for three cases with different dc-side load imbalance levels when modulation index  $M = M_{max}$  and  $R_{in,Lg0} \ge R_{in,Lbal}$ .

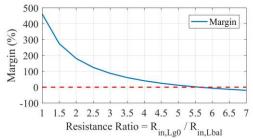

Fig. 20. Margin for  $\alpha\beta$ -sequence losses of the grounding inductor of case 3.

of both cases 1 and 2 when the load imbalance is over about 25%. But the inductor losses of case 3 are higher than other two cases in most cases: one reason is the lower modulation index of case 3, which leads to lower ac voltages, higher ac currents, and consequently higher *L* filter losses; the other is the higher zero-sequence grounding resistance that results in higher losses. Noticiably, when  $R_{in,Lg0} \ge 6 \times R_{in,bal}$ , case 3 is worse than case 2 in power losses. Hence, for a better effciency of case 3, the zero-sequence resistance of the grounding inductor should be designed as small as possible.

Next, the losses caused by  $\alpha\beta$ -sequence current of the grounding inductor will be discussed. The margin of power losses of case 3 when compared with case 2 is calculated, which is defined as

$$Margin = \left(\frac{P_{Tol,Loss,Case2} - P_{Tol,Loss,Case3}}{P_{Lg0,Loss,Case3}}\right)_{100\% \ Load \ Imbalance}$$

(23)

11

i.e. the margin gives the upper limit of the  $\alpha\beta$ -sequence losses of the grounding inductor, if the efficiency of case 3 is required to be better than that of case 2 with 100% load imbalance, as shown in Fig. 20. Remarkably, the larger zero-sequence resistance, the lower margin for the  $\alpha\beta$ -sequence losses, and consequently the lower  $\alpha\beta$ -sequence current and larger  $\alpha\beta$ -sequence inductance required for the grounding inductor. Therefore, in addition to the design requirement of low zero-sequence resistance, the  $\alpha\beta$ -sequence inductance should be large enough for a good efficiency of case 3. These two design requirements might increase the system costs of case 3. But as long as the grounding inductor in case 3 costs less than the voltage balancer in case 2 (mainly including one balancing inductor, two IGBTs, and corresponding gate-driving signals given by an auxiliary control system), case 3 is still cost-benefit with a satisfactory conversion efficiency.

## VI. CONCLUSION

A new three-phase active rectifier topology for bipolar dc distribution has been proposed and analyzed. This topology has the ability to feed two dc poles independently and control two dc-pole voltages actively, by using an ac-side three-phase coupled grounding inductor to achieve the current injection to the dc neutral line. The proposed rectifier has been tested on an experiment platform. Compared with other two existing ac-dc conversion approaches for bipolar low-voltage dc distribution, the proposed topology uses less IGBTs and potentially holds less power losses when feeding unbalanced dc loads. But meanwhile, the coupled grounding inductor is required with high  $\alpha\beta$ -sequence inductance and low zero-sequence resistance, which closely influence the efficiency of the proposed topology.

#### REFERENCES

- Y. Wang and R. Marquardt, "Future HVDC-grids employing modular multilevel converters and hybrid DC-breakers," in *Power Electronics and Applications (EPE), 2013 15th European Conference on, Lille,* pp. 1-8, 2013.

- [2] X. Zhang, T. C. Green and A. Junyent-Ferré, "A new resonant modular multilevel step-down DC–DC converter with inherent-balancing," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 78-88, Jan. 2015.

- [3] Callavik, Magnus, et al. "The hybrid HVDC breaker." *ABB Grid Systems Tech. Paper*, 2012.

- [4] C. C. Chan, "The state of the art of electric, hybrid, and fuel cell vehicles," *Proc. IEEE*, vol. 95, no. 4, pp. 704–718, Apr. 2007.

- [5] S. Rivera, B. Wu, S. Kouro, V. Yaramasu, and J. Wang, "Electric vehicle charging station using a neutral point clamped converter with bipolar DC bus," *IEEE Trans. Ind. Electron.*, vol. 62, no. 4, pp. 1999–2009, Apr. 2015.

- [6] D. J. Hammerstrom, "AC versus DC distribution systems-did we get it right?" in Proc. IEEE Power Eng. Soc. Gen. Meet., pp. 1–5, Jun. 2007.

- [7] M. E. Baran and N. R. Mahajan, "DC distribution for industrial systems: Opportunities and challenges," *IEEE Trans. Ind. Appl.*, vol. 39, no. 6, pp. 1596–1601, Nov. 2003.

- [8] T. Dragicevic, X. Lu, J. Vasquez, and J. Guerrero, "DC Microgrids-Part I: A Review of Control Strategies and Stabilization Techniques," *IEEE Trans. Power Electron.*, vol. 8993, no. c, pp. 1–1, 2015.

- [9] T. Dragicevic, X. Lu, J. C. Vasquez, and J. M. Guerrero, "DC microgrids—Part II: A review of power architectures, applications, and standardization issues," *IEEE Trans. Power Electron.*, vol. 31, no. 5, pp. 3528–3549, May 2016.

- [10] T. Dragicevic, J. C. Vasquez, J. M. Guerrero, and D. Skrlec, "Advanced LVDC electrical power architectures and microgrids: A step toward a new generation of power distribution networks," *IEEE Electrif. Mag.*, vol. 2, no. 1, pp. 54–65, Mar. 2014.

- [11] H. Kakigano, Y. Miura, and T. Ise, "Low-voltage bipolar-type DC microgrid for super high quality distribution," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 3066–3075, Dec. 2010.

- [12] D. Salomonsson and A. Sannino, "Low-voltage DC distribution system for commercial power systems with sensitive electronic loads," *IEEE Trans. Power Del.*, vol. 22, no. 3, pp. 1620–1627, Jul. 2007.

- [13] P. Salonen, T. Kaipia, P. Nuutinen, P. Peltoniemi, and J. Partanen, "An LVDC distribution system concept," in *Proc. Nordic Workshop Power Ind. Electron. (NORPIE)*, 2008, pp. A3-1–A3-16.

- [14] D. Salomonsson, L. Soder, and A. Sannino, "Protection of low-voltage DC microgrids," *IEEE Trans. Power Del.*, vol. 24, no. 3, pp. 1045–1053, Jul. 2009.

- [15] J. Lago, J. Moia, and M. L. Heldwein, "Evaluation of power converters to implement bipolar dc active distribution networks—DC–DC converters," in *Proc. Energy Convers. Congr. Expo.*, 2011, pp. 985–990.

- [16] Y. Gu, W. Li, X. He, "Analysis and control of bipolar LVDC grid with DC symmetrical component method," *IEEE Trans. on Power Syst.*, vol. 31, no. 1, pp. 685-694, Jan. 2016.

- [17] D. A. Rendusara and P. N. Enjeti, "An improved inverter output filter configuration reduces common and differential modes dv/dt at the motor terminals in PWM drive systems," *IEEE Trans. Power Electron.*, vol. 13, pp. 1135–1143, Nov. 1998.

- [18] Y. He, H. S. Chung, C. N. Ho, and W. Wu, "Modified cascaded boundary-deadbeat control for a virtually-grounded three-phase grid-connected inverter with LCL filter," *IEEE Trans. Power Electron.*, to be published.

- [19] G. Escobar, N. Ho, and S. Pettersson, "Method and apparatus for zero sequence damping and voltage balancing," US Patent, No. US9030854 B2, 12/05/2015.

- [20] A. Yazdani and R. Iravani, "A generalized state-space averaged model of the three-level NPC converter for systematic DC-voltage-balancer and current-controller design," *IEEE Trans. Power Del.*, vol. 20, no. 2, pp. 1105–1114, Apr. 2005.

- [21] J. Moia, J. Lago, A. J. Perin, and M. L. Heldwein, "Comparison of three phase PWM rectifiers to interface ac grids and bipolar DC active distribution networks," in Proc. Power Electron. Distrib. Generation Syst., 2012, pp. 221–228.

- [22] M. P. Kazmierkowski, R. Krishnan, and F. Blaabjerg, *Control in Power Electronics*. New York: Academic, 2002.

- [23] R. Wu, S. B. Dewan, and G. R. Slemon, "A PWM ac-dc converter with fixed switching frequency," *IEEE Trans. Ind. Applicat.*, vol. 26, pp. 880– 885, Sept./Oct. 1990.

- [24] S. Hiti, D. Borojevic, and C. Cuadros, "Small-signal Modeling and control of three-phase PWM converters," in *Conf. Rec. IAS*'94, 1994, pp. 1143–1150.

- [25] F. Blaabjerg, R. Teodorescu, M. Liserre, and A. V. Timbus, "Overview of control and grid synchronization for distributed power generation systems," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1398–1409, Oct. 2006.

- [26] D. Zmood and D. G. Holmes, "Stationary frame current regulation of PWM inverters with zero steady-state error," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 814–822, May 2003.

- [27] A. Junyent-Ferre, P. Clemow, M. Merlin, and T. Green, "Operation of hvdc modular multilevel converters under dc pole imbalances," in 16th European Conf. on Power Electron. and Applicat. (EPE'14-ECCE Europe), 2014, Aug 2014, pp. 1–10.

- [28] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA: Kluwer, 2001.

- [29] S.-K. Chung, "A phase tracking system for three phase utility interface inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 431–438, May 2000.

- [30] J. Jin, J. Allan, C. Goodman, and K. Payne, "Single pole-to-earth fault detection and location on a fourth-rail dc railway system," *Proc. Inst. Elect. Eng., Electr. Power Appl.*, vol. 151, no. 4, pp. 498–504, Jul. 2004.

- [31] D. G. Holmes and T. Lipo, Pulse Width Modulation for Power Converters: Principles and Practice. Piscataway, NJ: IEEE Press, 2003.

- [32] A. M. Hava, U. Ayhan, and V. V. Aban, "A DC bus capacitor design method for various inverter applications," in *Proc. IEEE Energy Convers. Congr. Expo.*, pp. 4592–4599, 2012.

- [33] H. Wen, W. Xiao, X. Wen, and P. Armstrong, "Analysis and evaluation of DC-Link capacitors for high-power-density electric vehicle drive

systems," IEEE Trans. Veh. Technol., vol. 61, no. 7, pp. 2950–2964, Sep. 2012.

- [34] A. Mariscotti, "Analysis of the DC-link current spectrum in voltage source inverters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 49, no. 4, pp. 484–491, Sep. 2002.

- [35] D. Graovac, M. Purschel, "IGBT power losses calculation using the data-sheet parameters," Infineon Technol., Dresden, Germany, Jan. 2009, Appl. note.

- [36] F. Casanellas, "Losses in PWM inverters using IGBTs," Proc. Inst. Elect. Eng.-Electr. Power Appl., vol. 141, no. 5, pp. 235–239, Sep. 1994.

- [37] Datasheet, "CM75TJ-24F Trench Gate Design Six IGBTMOD<sup>™</sup> 75 Amperes/1200 Volts" Powerex, Inc., Pennsylvania.

**Yitong Li** received the B.Eng degrees from Huazhong University of Science and Technology, Wuhan, China, and the University of Birmingham, Birmingham, UK, in 2015. He received his M.Sc degree in Future Power Networks from Imperial College London, London, UK, in 2016, where he is currently pursuing his Ph.D.

degree. His current research interests include power electronic converters for dc grids and sustainable energy systems.

Adrià Junyent-Ferré (S'09-M'11) received the degree in Industrial Engineering from the School of Industrial Engineering of Barcelona (ETSEIB), Technical University of Catalonia (UPC), in 2007, and the PhD in Electrical Engineering from the UPC in 2011. He was a researcher at Centre d'Innovació Tecnològica en Convertidors Estàtics i

Accionaments (CITCEA-UPC) from 2006 to 2012 and a Lecturer at the Barcelona College of Industrial Engineering (EUETIB) in 2012. He joined the Department of Electrical and Electronic Engineering of Imperial College London as a Research Associate in 2013 and became a Lecturer in September 2014. His field of expertise is the design and control of power electronic converters for generation, transmission and distribution applications, with specific interest in wind power, VSC-HVDC and microgrids.

Joan-Marc Rodriguez-Bernuz (S'16) received the degree in Energy Engineering from the Barcelona College of Industrial Engineering (EUETIB), Technical University of Catalonia (UPC), Barcelona, Spain, in 2013, and the master's degree in Energy Engineering from the UPC in 2015. He was a research assistant at Centre d'Innovació Tecnològica en Convertidors

12

Estàtics i Accionaments, (CITCEA-UPC) from 2013 to 2015 where he worked in smart grids, energy storage and control of power electronic converters. In 2015, he joined the Department of Electrical and Electronic Engineering of Imperial College London where he is currently pursuing his Ph.D. degree in electrical engineering. His current research areas include control of power electronic converters for renewable energy technologies and HVDC power transmission.

This work is licensed under a Creative Commons Attribution 3.0 License. For more information, see http://creativecommons.org/licenses/by/3.0/