Received 17 July 2020; accepted 10 August 2020. Date of publication 20 August 2020; date of current version 15 September 2020. The review of this article was arranged by Associate Editor Tommaso Caldognetto.

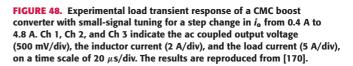

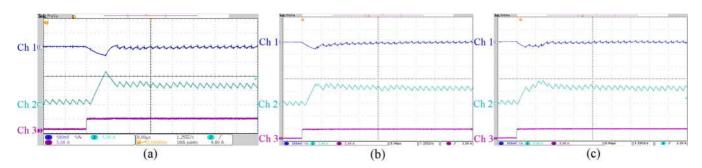

Digital Object Identifier 10.1109/OJPEL.2020.3018311

# A Tutorial and Review Discussion of Modulation, Control and Tuning of High-Performance DC-DC Converters Based on Small-Signal and Large-Signal Approaches

SANTANU KAPAT<sup>1</sup> (Senior Member, IEEE), AND PHILIP T. KREIN<sup>1</sup>, (Fellow, IEEE)

<sup>1</sup>Department of Electrical Engineering, IIT Kharagpur, West Bengal 721302, India

<sup>2</sup>Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, USA

<sup>3</sup>Zhejiang University/University of Illinois at Urbana-Champaign Institute, Haining, China

CORRESPONDING AUTHOR: PHILIP KREIN (e-mail: krein@illinois.edu)

This work was supported in part by the Grainger Center for Electric Machinery and Electromechanics at the University of Illinois at Urbana-Champaign, in part by the Zhejiang University/University of Illinois at Urbana-Champaign Institute, and in part by the Embedded Power Management Lab at the Indian Institute of Technology (IIT) Kharagpur.

**ABSTRACT** Many commercial controller implementations for dc-dc converters are based on pulse-width modulation (PWM) and small-signal analysis. Increasing switching frequencies, linked in part to wide bandgap devices, provide the opportunity to increase operating bandwidth and enhance performance. Fast processors and digital signal processing offer new computational techniques for power converter control. Conventional control techniques rarely make full use of operating capability. The objectives of this paper are to present an overview and link to literature on conventional modulation and control techniques for hard-switched dc-dc converters, identify performance limits associated with conventional small-signal-based design, discuss geometric control approaches, and compare strategies for control tuning. The discussion shows how current mode controls have alternative state feedback implementations, and describes unusual opportunities for large-signal control tuning. Considerations for minimum response time are described. Comparisons among tuning methods illustrate how geometric controls can achieve order of magnitude dynamic performance increases. The paper is intended as a baseline tutorial reference for future work on power converter control.

**INDEX TERMS** Current mode control, dc-dc converters, feedback control, feedback tuning, fixed frequency pulse-width modulation, sliding mode control, switching boundary control, time optimal control, variable frequency modulation.

#### I. INTRODUCTION

This paper seeks to review control and modulation methods for dc-dc switching power converters, as well as approaches for controller tuning. Most controllers use sawtooth-based pulse-width modulation (PWM) and small-signal-based feedback controls, but this paper explores a wider range and extends into large-signal approaches. The emergence of fast wide bandgap switches, combined with continuing advances in digital signal processing and sensors, motivates faster, more sophisticated controls. The emphasis here is on highperformance converters — a growing market segment. In this review, converter topology acts as a control constraint. In concept, the right constraints allow a given control method to work with many circuits. One example is the converter output objective. Digital electronics usually seek tight load voltage regulation. LED lighting motivates currentregulated loads. Battery chargers usually employ both voltage and current regulation modes. Digital loads, and dc sources and loads in microgrids, benefit from droop relationships. The review addresses non-isolated buck and boost converters, but there is no loss of generality, and methods can be applied across dc-dc converter families. The coverage emphasizes

| Type of objective | Typical examples                                                      | Related examples                | Additional examples       |

|-------------------|-----------------------------------------------------------------------|---------------------------------|---------------------------|

|                   | Output voltage value                                                  | Voltage regulation              | Power range               |

| Static operation  | Output voltage tolerance band                                         | Load/line regulation            | Temperature effects       |

|                   | Output impedance                                                      | Ripple limits, percentage error | Dynamic voltage scaling   |

|                   | Response to step changes                                              | Rise time, settling time        | Start-up time             |

| Dynamic operation | Load current slew rate                                                | Peak overshoot/undershoot       | Phase margin, gain margin |

|                   | Audio susceptibility                                                  | Disturbance rejection           | Control bandwidth         |

| Operating         | FCC radiated EMI rules                                                | Power-up sequencing,            | Hot plugging              |

| requirements      | Input current THD, efficiency                                         | Interactive redundancy          | Light load efficiency     |

| Fault management  | ault management Current limit or foldback Inrush/start-up current lim |                                 | Mean time to failure      |

| and protection    | Thermal protection                                                    | Packaging and cooling methods   | Recovery time             |

| TABLE 1. | Converter | Objectives | With | Control | Implications |

|----------|-----------|------------|------|---------|--------------|

|----------|-----------|------------|------|---------|--------------|

hard-switched converters. New results linked to state feedback control and large-signal tuning are included.

Controls for dc-dc converters must address at least four types of objectives, summarized in Table 1. These include static and dynamic operating requirements. Other operating requirements such as electromagnetic interference (EMI), efficiency, and reliability are not always associated with control. Fault management and protection requirements are usually addressed separately. Many requirements in Table 1 seem independent, but some large-signal controllers can manage them directly. The full set of requirements represented by Table 1 is linked to converter design. Slew rate limits and ripple bands are determined by inductor and capacitor choices. EMI is linked to parasitics and influenced by layout. Even so, it is possible in principle to define a cost function J(x) linked to all operating variables and parameters in a converter, such that

$$J(x) = \sum_{i=1}^{N} \alpha_i f_i(x), \tag{1}$$

where functions  $f_i(x)$  are various functions of the variables xand parameters, and  $\alpha_i$  are weights. Examples include RMS currents and fluxes (linked to losses), output voltage error and ripple, load current rise time, peak device voltage stresses, peak junction temperature, switching frequency variation, and so on. In [1], multi-objective optimization of power converters is formulated as a geometric program, a type of convex optimization problem, in which multiple operating points, converter topologies, and components can be considered. Thermal management and electromagnetic effects also can be embedded in the electrical design for optimizing power density of dc-dc converters [2]. A performance index, the opposite of a cost function, could have been defined similarly. The cost function is to be minimized, and a design or control problem can be formulated into an optimization problem.

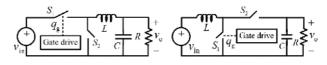

Consider the basic converters shown in Fig. 1, which could include synchronous operation. The dc-dc converter control problem can be conceptualized at a high level. In the broadest sense, the question is: Given a cost function (1) that reflects specifications of a converter, and given suitable design choices and layout, find a set of turn-on times and turn-off times for switches  $S_1$  and  $S_2$  that minimizes the cost function. This

FIGURE 1. Dc-dc buck converter (left) and boost converter (right).

control optimization problem is distinct from the circuit design optimization problem [3], because here we seek to get the best performance from a given converter.

The timing problem, although easy to pose, is not tractable in general. It might be possible to solve for simple converters given simplified specifications. However, as specification details and uncertainty are added, the problem grows in complexity. It does motivate certain approaches. Trajectory-based controls [4], [5], seek to change the timing problem into a state-variable formulation. In constrained time optimal control [6], [7], [8], the question of when to switch for fastest rejection of a step load change, given constraints on a converter and its operation, is posed and solved. Prior work on fast response used separate circuits such as clamps [9]. In [10], [11], even faster disturbance rejection is obtained by altering a converter with additional switches and devices. An alternative based on steering inductor energy was presented in [12]. Other efforts are discussed in Section VI.

Since the generic switch timing problem is intractable, a designer must settle for accessible approaches. Typically, this imposes at least two constraints beyond those in Table 1:

- 1) The converter operating regimes are constrained. A classic example is to enforce a fixed switching frequency.

- 2) A simplified model of the converter is used as the basis for control design and operation. A classic example is to use a small-signal linearization of an averaged model.

The first of these limits timing flexibility, turning the problem into a cycle-by-cycle duty ratio. The second gives rise to *model limited control*, in which the full dynamic capabilities of the converter might not be attainable.

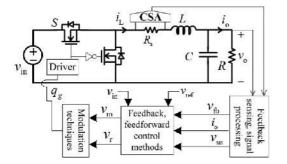

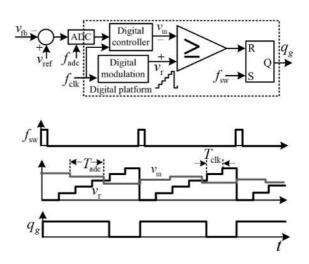

Fig. 2 shows the block diagram of a basic feedback and feedforward buck converter control system. The feedback sensing block is band limited to avoid ripple effects. For digital control, additional signal conditioning and

TABLE 2. Parameter Set for dc-dc Buck and Boost Converters

| Converter       | Input Voltage | Output Voltage | Inductor     | Capacitor     | Switching Frequency | Load current |

|-----------------|---------------|----------------|--------------|---------------|---------------------|--------------|

| Buck converter  | 12 V          | 3.3 V          | $10 \ \mu H$ | 470 $\mu$ F   | 200 kHz             | 1 to 20 A    |

| Boost converter | 8 V           | 12 V           | $4 \mu H$    | $150 \ \mu F$ | 500 kHz             | 0.5 to 5 A   |

**FIGURE 2.** Feedback control of a buck converter:  $v_{in}$  and  $v_o$  are the input and output voltages;  $v_{fb}$ ,  $v_{ref}$ , and  $v_{sn}$  are the feedback voltage, reference voltage, and voltage associated with the sensed inductor current, respectively;  $v_m$  and  $v_r$  are the modulating and ramp signals;  $q_g$  is the gate signal for the controllable MOSFET S; "CSA" represents a current sense amplifier.

analog-to-digital converters (ADCs) are needed. Output feedback is required for precise output regulation or tracking. Inductor current feedback can be used for control or for current-regulated loads. A converter can be controlled using output feedback or state feedback. Feedforward action, using input voltage, load current, or other information, can reduce audio susceptibility or output impedance, or provide better disturbance rejection. The controller drives a modulator to generate gate signal  $q_g$  for the controllable switch. In a boost converter, the modulator requires a limiter function.

Table 2 provides a set of converter design parameters that will be used here for simulation and comparison. These converters have been built and are used here for experimental testing as well.

The discussion is organized as follows. Section II presents an overview of various modulation techniques and shows how they differ in operation. Control methods based on feedback interconnections such as in Fig. 2 are discussed in Section III. Various large-signal and small-signal modeling techniques along with the associated dynamics of PWM dc-dc converters are presented in Section IV. Small-signal control and tuning methods are summarized in Section V. Section VI presents large-signal control and tuning methods. Section VII presents a comparative performance analysis using small-signal and large-signal approaches along with some design case studies. This includes experimental validation of the work. Section VIII concludes the paper.

# II. CONTROL TECHNIQUES BASED ON FUNDAMENTAL MODULATION PRINCIPLES A. FIXED FREQUENCY PWM

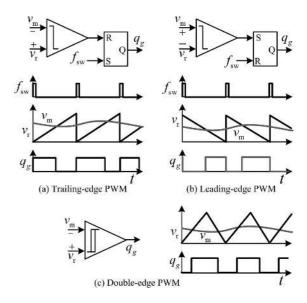

In a typical converter, the combination of a carrier signal at fixed frequency  $f_{sw}$ , comparator, and latch implement gate

FIGURE 3. Three PWM carriers for dc-dc converters.

signal  $q_g$  of the controllable switch. For synchronous operation or bidirectional current, the other switch would be in complement to  $q_g$  except for a dead time. As shown in Fig. 3, a rising sawtooth, falling sawtooth, or triangle  $v_{\rm r}(t)$  can be used as the carrier, and the comparator can set or reset the latch based on modulation signal  $v_{\rm m}(t)$ . Fixed  $f_{\rm sw}$  can be enforced with a clock signal. The latch should be reset dominant in Fig. 3(a) (otherwise 0% duty cycle is avoided) and set dominant for Fig. 3(b) (otherwise 100% duty cycle is avoided). The latch prevents "double-pulsing," as the switch can act only once per cycle. Without it, the control can produce chaotic operation [13], [14], [15]. The rising sawtooth produces trailingedge modulation. The falling sawtooth produces leading-edge modulation. The triangle produces *double-edge* modulation. Double-edge modulation corresponds to naturally sampled PWM. It has technical advantages in time-domain performance that are helpful in precision applications such as class-D audio amplifiers [16]. Trailing-edge modulation can impose a time delay  $t_d$  up to (1 - D)T, where D is the active switch duty ratio and  $T = 1/f_{sw}$ , to respond to a step-up transient. For leading-edge modulation,  $t_d$  can be up to DT during a step-down transient.

The delay distinctions of leading-edge and trailing-edge modulation have been employed to alter phase behavior of closed-loop controllers. In [17], leading-edge modulation phase characteristics tend to compensate for non-minimum phase dynamics. The effect is not really general, and more detail is provided in [18]. As shown there, combinations of

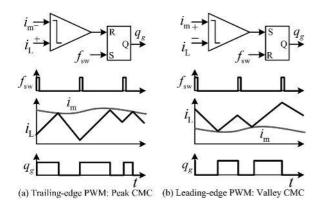

FIGURE 4. Two PWM current mode control techniques.

FIGURE 5. Block diagram of average CMC under trailing edge PWM.

sampling times and modulation ramp types can alter controlto-output responses. Non-minimum phase behavior is a physical property of boost and other indirect converters. Controller changes might avoid immediate impacts of a disturbance, but do not eliminate the physical behavior.

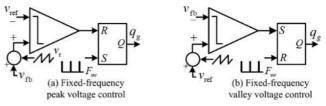

In general, voltage mode control (VMC) refers to dc-dc converter controls that employ output voltage feedback. In current mode control (CMC) [19], the sensed inductor current replaces the sawtooth waveform. Trailing-edge modulation becomes analogous to peak CMC and leading-edge modulation becomes analogous to valley CMC. The CMC arrangements are shown in Fig. 4, in which an equivalent current modulating signal  $i_m$  and the inductor current  $i_L$  are used instead of  $v_{\rm m}$  and the sawtooth signal  $v_{\rm r}$  in Fig. 3. In flux mode control (also termed sensorless current mode control) [20], a voltage integral that tracks inductor flux replaces the sawtooth instead. Current or flux used in place of a ramp produces instability for half of the duty ratio range, but this can be avoided by retaining a sawtooth and subtracting it as a stabilizing ramp [21], [22]. Stabilizing ramps are less suitable for precise average current control applications because of varying ripple current for varying duty ratio. Average CMC or flux mode controls are preferred in those cases.

Fig. 5 shows a block diagram of average CMC, consisting of a voltage compensator  $G_{vc}$  with the (output) error voltage  $v_e$  as the input and a current compensator  $G_{cc}$  with the error current  $i_e$  (relative to the average value) as the input. For current regulated loads,  $i_{ref}$  is set to the desired current; otherwise, it is generated by the voltage controller  $G_{vc}$ . Low pass filter  $G_{LPF}$  attenuates ripple and extracts the average inductor current value  $i_{av}$ . A proportional-integral (PI) controller is typical for  $G_{cc}$  to drive  $i_e$  to zero for average current tracking. Average CMC [23] does not suffer from current

FIGURE 6. Fixed-frequency (trailing-edge) digital pulse width modulation.

loop instability for wide duty ratio operation. Although average CMC offers superior average current regulation, it is relatively slow. It remains difficult to deliver both fast performance and accurate current regulation using available CMC methods. Both are important for phase current balancing in multi-phase converters, as in many low-voltage high-current applications [24], [25], [26]. High conversion ratios impose current sensing and stability constraints on fixed-frequency CMC methods. A more comprehensive version was presented in [27].

#### **B. FIXED-FREQUENCY DIGITAL PWM**

Based on trailing-edge PWM in Fig. 3(a), digital versions can be implemented using an ADC and a digital controller, as shown in Fig. 6. The resolution of digital PWM must be finer than that of the ADC to avoid quantization effects which may lead to limit cycle oscillations [28], [29]. Typical approaches use a counter to create a ramp, which is then compared to a digital signal. With a counter, the digital clock governs the internal time resolution of the pulse width. For example, if 1,000 distinct pulse widths are desired in a converter switching at 100 kHz, a 100 MHz clock must drive the counter. An extreme example is a class-D amplifier switching at 352.8 kHz, with a desired pulse width resolution of 24 bits [30]. The time resolution should be 0.17 ps. This corresponds to a counter clock rate of 5.92 THz. Such an extreme clock rate is implausible. Other techniques use tapped delay-line PWM [31], [32], ring oscillator implementations [33], hybrid digital PWM [34] or noise shaping [16] to allow the same effective output resolution with coarser time resolution. Even so, counter-based PWM implementations are ubiquitous, and are the basis of output ports in many processor families.

The sampling frequency  $f_{adc}$  of the ADC is usually an integer multiple of  $f_{sw}$ , i.e.,  $f_{adc} = N f_{sw}$  (most often N = 1). This practice seeks to allow nearly a full switching cycle for computation. For example, if a dc-dc converter switching and sampling at 500 kHz is implemented with a microcontroller

**FIGURE 7.** Effect of  $\tau_d$  in peak CMC on the reference transient performance of a buck converter using a PI voltage controller and an analog current loop with 12 V input and  $R = 1 \Omega$ . Traces (a) and (d) correspond to analog PWM with  $\tau_d = 0$  and  $\tau_d = T$ , respectively. Traces (b) and (c) correspond to digital PWM with  $f_{adc} = f_{sw}$  and  $f_{adc} = 20f_{sw}$ , respectively.

FIGURE 8. Current controlled variable frequency modulation techniques.

clocked at 200 MHz, there are about 400 clock pulses per switching cycle available for computation. The controller can alter tuning parameters or other attributes on a cycle-by-cycle basis. Limits or fault conditions can be enforced as soon as they are detected.

Compared to analog PWM, sampling introduces a delay  $\tau_d$  which increases with decreasing  $f_{adc}$ . A larger  $\tau_d$  can degrade large-signal recovery as shown in Fig. 7. Sampling with N > 1 has benefits in linear controllers with digital PWM, where an increase in sampling rate decreases the phase lag,  $1/(2N f_{sw})$ , associated with digital PWM [35]. Fig. 7 shows that a higher  $f_{adc}$  can achieve nearly the same performance as analog CMC without a delay. However, the performance of analog CMC degrades if there is a full cycle delay, even compared to  $f_{adc} = f_{sw}$ . A delay of a full cycle is the worst-case (transient) detection delay for extreme duty ratio operation using either trailing-edge or leading-edge modulation techniques, as discussed in Section II-A. Ever-decreasing costs of digital processors support increasing control complexity.

#### C. PHASE MODULATION

Fixed-frequency phase shift modulation is common in fullbridge isolated topologies for bidirectional power flow [36]. This often leads to high RMS current in the transformer in a dual active bridge converter under light load conditions. Dual phase shift modulation introduces the duty ratio as an additional degree of freedom [37]. A triple phase shift modulation technique can offer three degrees of freedom for further optimization [38]. A comprehensive review of various fixedfrequency control methods for dual active bridge converters is presented in [39], [40].

### D. VARIABLE FREQUENCY MODULATION TECHNIQUES

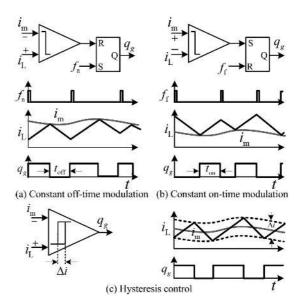

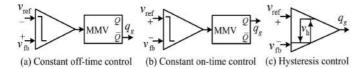

Variable frequency modulation most often takes one of three basic forms [3], [41]. These are (a) constant off-time, (b) constant on-time, and (c) hysteresis control. Hysteresis control is not usually considered a modulation approach, but the operational structure is about the same, so it is discussed here.

Typical current-controlled methods are shown in Fig. 8. For constant off-time and on-time modulators, timing parameters are loaded using monostable multivibrators to activate respective flag signals  $f_n$  and  $f_f$  after triggering. The latch set or reset terminals determine which is being controlled.

#### 1) CONSTANT OFF-TIME MODULATION

For constant off-time modulation [42], the active switch off interval is fixed, and the on time is modulated. In the example here, an equivalent modulation signal  $i_m$  varies. The current is compared to  $i_m$  as shown in Fig. 8(a), and the switch turns off when the current reaches the modulation signal. This is analogous to peak CMC in Fig. 4(a), but now with varying switching period. The perturbed current dynamics during the *n*th switching cycle can be written as

$$i_{n+1} = i_m - m_2 T_{\text{off}} \quad \Rightarrow \tilde{i}_{n+1} = \tilde{i}_m, \tag{2}$$

where  $m_2$  is the magnitude of the falling slope of  $i_L$ , and  $i_m$  is the modulating signal in Fig. 8. Unlike current-loop instability in peak CMC for D > 0.5, (2) shows that the control is inherently stable irrespective of the duty ratio.

In voltage controlled constant off-time modulation,  $i_L$  in Fig. 8(a) is replaced by a sawtooth waveform. This becomes analogous to trailing-edge PWM in Fig. 3(a). The steady-state switching frequency  $f_{sw}$  can be derived as

$$f_{\rm sw} = \begin{cases} (v_{\rm in} - v_{\rm o}) / (v_{\rm in} T_{\rm off}) & \text{buck converter} \\ v_{\rm in} / (v_{\rm o} T_{\rm off}) & \text{boost converter} \end{cases}$$

(3)

A constant switching frequency can be accomplished by adjusting the off time slowly and using an additional phase locked loop (PLL) to regulate  $f_{sw}$ . This adds a slow (frequency) control loop around a fast one. The slow loop will limit performance, although it can be argued that if the outer

loop merely makes a slow adjustment to the off time until the frequency locks in, the practical impact on dynamic performance is minimal. An early review of methods to enforce a fixed switched frequency under variable modulation approaches can be found in [43]. More recent results can be found in [44].

#### 2) CONSTANT ON-TIME MODULATION

Constant on-time operation was motivated initially by resonant pulses fixed in duration [45]. It has become more widely applicable to light load management [46]. The active switch on interval is fixed, and the off time is modulated by the control. A current-based method invoking a modulating signal  $i_m$  is shown in Fig. 8(b). This example is analogous to valley CMC in Fig. 4(b). The perturbed current dynamics during the  $n^{\text{th}}$  switching cycle can be written as

$$i_{n+1} = i_m + m_1 T_{on} \quad \Rightarrow \tilde{i}_{n+1} = \tilde{i}_m. \tag{4}$$

In contrast to valley CMC, which is unstable for D < 0.5, (4) implies that current-based constant on-time modulation avoids this problem.

In VMC constant on-time modulation,  $i_L$  in Fig. 8(b) is replaced by a sawtooth waveform, analogous to leading-edge PWM. The steady-state  $f_{sw}$  is

$$f_{\rm sw} = \begin{cases} (v_{\rm o} - v_{\rm in}) / (v_{\rm o} T_{\rm on}) & \text{boost converter} \\ v_{\rm o} / (v_{\rm in} T_{\rm on}) & \text{buck converter} \end{cases}$$

(5)

As with constant off-time modulation, a slow PLL-based outer loop can adjust the target on time until a desired switching frequency is achieved.

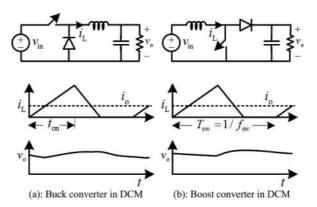

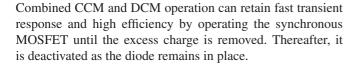

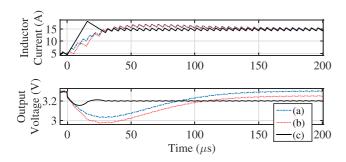

# 3) CONSTANT ON-TIME CONTROL IN DISCONTINUOUS CONDUCTION MODE

The dynamic behavior of constant on-time modulation alters if the converter inductance is below the critical value [47]. Switching converters are said to enter *discontinuous conduction mode* (DCM) when the inductor current drops to zero and switch action is no longer constrained to maintain a current path. A more comprehensive analysis can be found in [48]. DCM is typical under light load conditions. It is sometimes designed deliberately. For example, a flyback converter operating in DCM with a fixed duty ratio will track its input voltage [49], [50].

Fig. 9 shows conventional buck and boost converters in DCM given limited output voltage ripple and high inductor current ripple. For constant on time, in DCM, the steady-state switching frequency can be derived by enforcing charge balance in the output capacitor. The results are

$$f_{\rm sw} = \begin{cases} \frac{2Lv_{\rm o}}{(v_{\rm in} - v_{\rm o}) v_{\rm in}} \times \left(\frac{i_{\rm o}}{t_{\rm on}^2}\right) \text{ buck converter} \\ \frac{2L(v_{\rm o} - v_{\rm in})}{v_{\rm in}^2} \times \left(\frac{i_{\rm o}}{t_{\rm on}^2}\right) \text{ boost converter} \end{cases}$$

(6)

For a given set of power circuit parameters and operating input and output voltages, the switching frequency  $f_{sw}$  varies linearly with the load current  $i_0$  if the on time is fixed. The

FIGURE 9. Current and voltage waveforms of dc-dc converters in DCM.

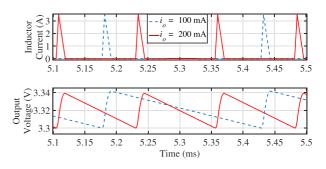

**FIGURE 10.** Output voltage-based constant on-time modulation in a DCM buck converter using the parameter set in Table 2 with 12 V input and 3.3 V output.

switching frequency drops as the load current decreases, as shown for a DCM buck converter in Fig. 10. This tends to improve light load efficiency, so the approach is applied in many commercial products. Many products shift from fixedfrequency modulation to constant on-time modulation when the load current falls below a threshold [51].

Under light load conditions deep in DCM, the inductor current ripple is much larger than the load current, and the output voltage ripple can be approximated as [52]

$$\Delta v_{\rm o} \approx \begin{cases} \frac{(v_{\rm in} - v_{\rm o}) v_{\rm in}}{v_{\rm o}} \times \frac{t_{\rm on}^2}{2LC} & \text{buck converter} \\ \frac{v_{\rm in}^2}{(v_{\rm o} - v_{\rm in})} \times \frac{t_{\rm on}^2}{2LC} & \text{boost converter} \end{cases}$$

(7)

For a given set of power circuit parameters and operating input and output voltages, the ripple  $\Delta v_0$  under constant ontime modulation remains more or less constant as the load decreases, which is consistent with Fig. 10. However,  $\Delta v_0$ increases with  $v_{in}^2$  and may violate ripple design constraints under high line conditions. This can be corrected by reducing  $t_{on}$  as  $v_{in}$  increases. An adaptive constant on-time modulator adjusts  $t_{on}$  as a function of  $v_{in}$  to keep  $\Delta v_0$  within a specified limit and to help regulate  $f_{sw}$  [51].

#### 4) HYSTERESIS CONTROL

Hysteresis determines switching times directly rather than adjusting a duty ratio or time interval, so it is not normally considered among modulation methods. However, the implementation can be similar, as shown in [53], so it is discussed here. Fig. 8(c) removes the latch to implement current hysteresis control. The inductor current  $i_L$  is constrained within a hysteresis band  $\Delta i$ . The band can be left to the specific implementation of the comparator, or can be treated as a separate control parameter. The steady-state switching frequency  $f_{sw}$ can be derived as

$$f_{\rm sw} = \begin{cases} \frac{(v_{\rm in} - v_{\rm o}) v_{\rm o}}{L v_{\rm in}} \times \frac{1}{\Delta i} & \text{buck converter} \\ \frac{(v_{\rm o} - v_{\rm in}) v_{\rm in}}{L v_{\rm o}} \times \frac{1}{\Delta i} & \text{boost converter} \end{cases}$$

(8)

For a given set of power circuit parameters and operating input and output voltages,  $f_{sw}$  is inversely proportional to  $\Delta i$  and *L*. Nonlinear magnetic inductor cores and saturation can lead to undesired frequency deviations. If frequency regulation is desired, one approach is to adjust  $\Delta i$  slowly and use a PLL to lock in a target frequency [54].

Voltage hysteresis can be realized by replacing  $i_{\rm L}$  in Fig. 8(c) by the feedback voltage  $v_{\rm fb}$  in Fig. 2 and  $\Delta i$  by  $\Delta v$ . However, voltage hysteresis control cannot be used directly in boost, buck-boost, and other cascaded converters because of non-minimum phase dynamics. In a boost converter, for example, a command to turn on the active switch (seeking to increase the output voltage) decouples the input and output energy flows and further decreases the output voltage. It is not difficult to overcome the problem — enforcement of a duty ratio or on-time limit is sufficient — but current hysteresis control is often preferred in commercial products.

A challenge in any hysteresis control is signal-to-noise ratio. Hysteresis controllers that seek tight ripple bands are affected by measurement noise. Lack of a latch can lead to chaotic dynamics [55]. Hysteresis control is a simple example of a geometric control, discussed in more depth below.

#### 5) OTHER MODULATION TECHNIQUES

Variable frequency modulation techniques for light load conditions include pulse skipping modulation (PSM) and burst mode control. A PSM technique [56], [57], skips switch action for entire cycles when the load is light enough. In effect, it makes discrete adjustments to reduce the switching frequency as the load decreases. The method can be derived from trailing-edge PWM in Fig. 3(a), in which the control output  $q_g$ is ANDed with a PSM logic signal  $q_{PSM}$  to generate the final gate signal  $q_f$ . The status is updated at every rising edge of the switching clock, and  $q_{PSM}$  is set high if the output voltage  $v_o$ is smaller than a reference value  $v_{ref}$ , i.e.,  $v_o < v_{ref}$ . A pulse is skipped if the output voltage is acceptable.

Burst mode control, in general, combines PWM and hysteresis control [58], [59]. The concept is to turn off the converter for a time when the load is light, turning it back on when the output voltage falls to a lower ripple limit. This seeks to

**FIGURE 11.** Current-based trailing-edge modulation in a buck converter with  $v_{in} = 6$  V and  $i_0 = 2$  A. Here only the inner current loop is closed.

maintain the output voltage within a hysteresis band  $\Delta v$ . The control logic enables the modulator if  $v_0 \leq (v_{ref} - \Delta v/2)$ . If  $v_0 \geq (v_{ref} + \Delta v/2)$ , modulation is disabled. When timing of the enable or disable decisions coincide with fixed switching period intervals, the approach is the same as PSM. Burst mode improves light load efficiency while holding ripple within a predefined limit. The general case has variable switching frequency and can impose EMI challenges [59]. It is easy to implement at the level of an integrated circuit (IC), and is relatively common in commercial power supplies.

Nonlinear carrier modulation, a variation on conventional PWM, has merit for applications with a wide duty ratio range. One example is active power factor correction (PFC), in which a converter such as a boost circuit is expected to operate with a duty ratio over nearly the full 0 to 1 range. Judicious adjustment of the carrier shape can facilitate operation of these converters [60], [61], [62], [63].

A pulse-train control method was described in [64]. This approach allows pulses with either a long on-time or a short on-time, using short pulses when voltage error is low and long pulses when it is high. This method for adapting to light loads has been implemented in a commercial IC.

# E. PERFORMANCE UNDER VARIOUS MODULATION TECHNIQUES

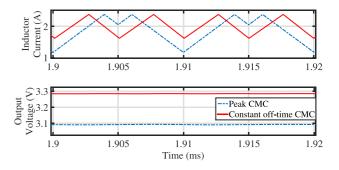

#### 1) CURRENT LOOP STABILITY

For CMC trailing-edge modulation, constant off-time control in Fig. 8 (a) offers inherent stability compared to its fixedfrequency counterpart in Fig. 4 (a). The latter is shown to exhibit fast-scale instability in Fig. 11 for duty ratio D > 0.5in the synchronous buck converter from Table 2. The peak current  $i_{\text{peak}}$  is set to achieve 3.3 V output. The unstable counterpart results in higher voltage error and larger current ripple compared to constant off-time control.

# 2) CONSTANT ON-TIME MODULATION IN A PFC BOOST CONVERTER

A boost converter is often used as a PFC circuit in ac-dc power conversion to achieve unity power factor and low linefrequency distortion. The primary control objective is to force the average inductor current to track a sinusoidal current

| Modulation       | Advantages and shortcomings                 | Primary applications                |  |  |

|------------------|---------------------------------------------|-------------------------------------|--|--|

| Trailing edge    | <i>VMC</i> - single loop control            | <i>VMC</i> - voltage regulators     |  |  |

| (TE) PWM         | Peak CMC - two-loop control, high           | CMC - voltage/current regulated     |  |  |

| [in Fig. 3  (a)] | bandwidth, but unstable for $D > 0.5$       | loads (VRM, LED, chargers, etc.)    |  |  |

| Leading edge     | <i>VMC</i> - single loop control            | <i>VMC</i> - boost converters [17]  |  |  |

| (LE) PWM         | Valley CMC - two-loop control, high         | CMC - high duty ratio voltage       |  |  |

| [in Fig. 3 (b)]  | bandwidth, but unstable for $D < 0.5$       | and current regulators              |  |  |

| Constant off-    | <i>VMC</i> - as in TE case                  | Not common                          |  |  |

| time modulation  | Peak CMC - analogous to TE CMC,             | CMC - wide duty ratio VR            |  |  |

| [in Fig. 8 (a)]  | no stability issue, but varying $f_{ m sw}$ | applications, LED drivers, etc.     |  |  |

| Constant on-     | VMC - as in LE case                         | <i>VMC</i> - Light-load in DCM, PFC |  |  |

| time modulation  | Valley CMC - similar to LE CMC,             | CMC - low duty ratio multi-phase    |  |  |

| [in Fig. 8 (b)]  | no stability issue, but varying $f_{ m sw}$ | buck VRM, battery chargers, etc.    |  |  |

TABLE 3. Summary of Various Modulation Techniques and Their Applications

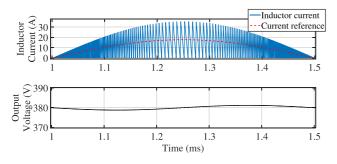

**FIGURE 12.** Constant on-time modulation in a PFC boost converter in critical conduction mode with  $V_{ac} = 230 \text{ V}$ ,  $V_{dc} = 380 \text{ V}$ , load resistance  $R = 50 \Omega$ , inductance  $L = 10 \mu$ H, capacitance  $C = 500 \mu$ F, and ac line frequency of 1 kHz.

FIGURE 13. Linear PWM (a) VMC and (b) CMC.

reference  $i_{ref}(t) = (V_{dc}/V_{ac})^2 \times |v_{in}(t)|/R$ . Here  $V_{dc}$  and  $V_{ac}$  are the output dc link voltage and input RMS voltage, R is the output load resistance, and  $v_{in}(t)$  is the instantaneous input ac voltage. Average CMC, as in Fig. 5, is suitable for this purpose, but constant on-time modulation can achieve near-perfect current tracking, especially in critical conduction mode as shown in Fig. 12. Critical conduction mode adjusts frequency to keep the inductor exactly at the critical value throughout converter operation. Here, the on time is set to  $T_{on} = 2L(P_{out}/V_{ac}^2)$ , where L and  $P_{out}$  are the inductance and output power of the boost converter. This technique is used in many commercial products [65], in which  $T_{on}$  needs to adapt to varying  $P_{out}$  or  $V_{ac}$ .

A comprehensive summary of modulation techniques along with their applications is presented in Table 3, and their impacts on stability and non-minimum phase characteristics of a digitally controlled CMC boost converter are discussed in [66].

### III. CONTROL METHODS BASED ON FEEDBACK AND FEEDFORWARD INTERCONNECTION

Overall feedback control can be classified into several categories. Most typical are (a) output feedback control, (b) state feedback control, (c) observer-based feedback control, and (d) predictive control. Feedforward control can supplement feedback control to further improve disturbance rejection and transient recovery to meet certain performance objectives, as discussed below. There are other designs that use energy sensing [67]. Output feedback control can be implemented with modulation. As in CMC, sometimes converter waveforms can be used directly, a method more broadly termed *ripple-based control* [68], [69]. It is also established that ripple can be demodulated to provide feedback information [70].

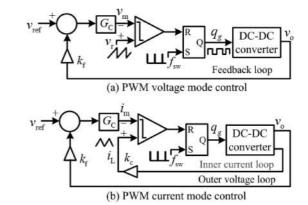

# A. OUTPUT FEEDBACK CONTROL LINKED TO MODULATION1) LINEAR OUTPUT FEEDBACK MODULATION CONTROL

Fig. 13(a) shows conventional VMC, in which the output voltage is sensed and filtered to limit the effects of ripple, and a function of the output voltage error signal  $v_{ref} - v_0$  serves as the modulation signal  $v_m$ . Conventional approaches use variants of PI control; these designs invoke linear system tools even though the implementations in Fig. 13 are nonlinear circuits. Terminology of linear control sometimes generates confusion. For example, an integral control is sometimes called a Type I compensator. A Type II compensator cascades an integrator with a phase-lead network. A Type III compensator cascades an integrator with two phase-lead networks. Any of

FIGURE 14. Voltage-ripple-based variable frequency control methods [69].

FIGURE 15. Voltage-ripple-based fixed-frequency control methods [69].

these four types (PI, Types I, II, III) can be implemented with a single operational amplifier or a single transconductance amplifier [71].

VMC operation in some sense is indirect, since voltage error must first drive a change in inductor current. The advantages of current sensing based on [19] have been considered compelling enough that CMC dominates dc-dc control implementations, but it is important to recognize that similar performance can be achieved using VMC if the loop transfer function can be matched to that with CMC. This requires perfect cancellation of complex poles and time scale separation. In practice, CMC treats the inductor as a controlled current source, which inherently achieves time scale separation and makes the design relatively robust. For example, charge-based controls [72], [73], and flux-based controls [20], use structures similar to VMC and achieve performance similar to CMC methods. It is also known that CMC has less favorable noise properties than VMC [74]. CMC alternatives employ output voltage error to generate a current reference signal, which in turn serves as the input for a current regulator.

#### 2) NONLINEAR PWM OUTPUT FEEDBACK CONTROL

In linear PWM control, analysis and design are carried out based on linearization around an operating point. The underlying assumption is that duty ratio perturbations (and others) must be small compared to steady-state values. Such methods may not be sufficient for wide operating ranges or nonlinear loads. An example is a dc-dc converter driving a constant power load — often another power converter [75], [76]. The negative incremental effect of a constant power load leads to a nonlinear output feedback loop. One alternative is inputoutput feedback linearization, in which the modulation voltage  $v_m$  is a suitable nonlinear function of  $v_o$  and the system parameters. Another is geometric control [77]. Constant power loads remain challenging [78], [79], [80].

#### **B. RIPPLE-BASED OUTPUT FEEDBACK CONTROL**

Ripple-based methods can be developed based on constant on-time, constant off-time, and hysteresis controls [68], [69]. Fig. 14 shows voltage-mode ripple-based control methods, in which the feedback voltage is compared directly to a reference voltage  $v_{ref}$  and the gate pulse  $q_g$  of the controllable switch is generated based on a modulation strategy. In constant on-time and off-time methods, a monostable multivibrator is added. The comparator output acts as the external trigger input. The monostable enters its astable state when the trigger input is activated, and returns to its stable state at the end of the constant timing interval. Hysteresis control is the same as before, switching based on a target ripple value  $\Delta v_0$ .

Voltage ripple-based constant on- or off-time control methods will have variable switching frequency, but can become unstable because of step ripple on the capacitor equivalent series resistance (ESR) [81]. For application of voltage-based constant off-time and hysteresis control methods to boost and buck-boost converters, an on-time or duty limiter is essential because of non-minimum phase behavior. Inductor current can be used instead as in CMC. Frequency variation for the methods in Fig. 14 can be addressed by synchronizing to an external clock as shown in Fig. 15.

Other ripple-based control methods include  $V^2$  control [62], [82], which attempts to extract capacitor current information using ESR-dominated voltage ripple. This method requires a larger ESR, which makes it susceptible to subharmonic instability and produces larger voltage ripple. Capacitor current feedback may be added to improve transient performance [83], although this method does not apply directly to non-minimum phase converters. Alternatively, direct capacitor current control can be used to achieve near-time-optimal performance [84], and this can be extended to boost converters [85].

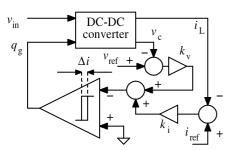

# C. STATE FEEDBACK CONTROL

State feedback in general implies sensing and control of capacitor voltages and inductor currents. In basic dc-dc converters with only two state variables, such controls share much in common with CMC. For example, if an external reference  $i_{ref}$ and current feedback are used explicitly in Fig. 13(a) and  $G_c$ is replaced with a proportional gain, the switching control law becomes

$$v_{\rm m} = k_i \left( i_{\rm ref} - i_{\rm L} \right) + k_{\rm v} \left( v_{\rm ref} - v_{\rm o} \right).$$

(9)

This is a state feedback control with gains on current and voltage. It becomes a PI control if the parameter  $i_{ref}$  is replaced with the function

$$i_{\rm ref} = k_{\rm p} (v_{\rm ref} - v_{\rm o}) + k_{\rm int} \int (v_{\rm ref} - v_{\rm o}) dt.$$

(10)

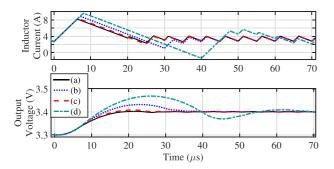

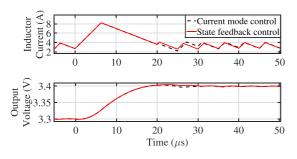

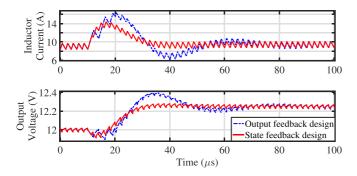

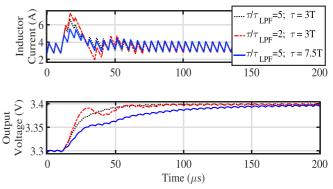

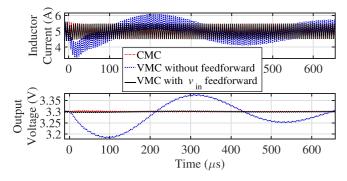

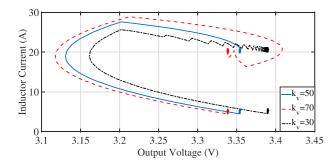

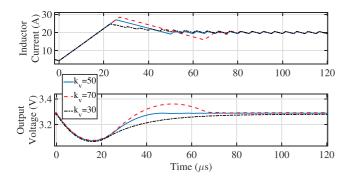

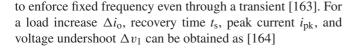

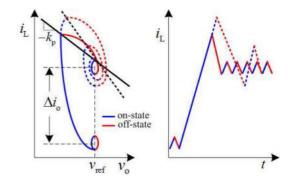

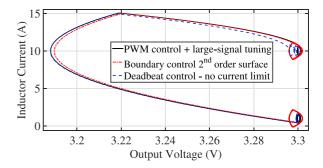

It is possible to use  $k_p = 0$ , given the proportional term in (9). The time domain performance details of peak CMC and of state feedback control are essentially the same. Fig. 16 shows the response of a buck converter from Table 2 to a step in the reference voltage. The converter switches at 200 kHz. For

**FIGURE 16.** Reference transient response of a buck converter using peak CMC and state feedback control. The parameter set is in Table 2.

peak CMC, as in Fig. 13(b), the converter uses a PI controller with  $k_v = 80$  and  $k_{int} = 100000$  to set the comparison signal for the current waveform. This converter reaches steady state in about eight switching cycles. The same transient performance can be achieved using trailing edge modulation with the state feedback laws in (9) and (10), as in Fig. 13(a), with  $k_p = 0$ ,  $k_i = 1$ ,  $k_v = 80$  and  $k_{int} = 100000$ . It is of interest that state feedback control imposes no limitations on duty ratio since action is governed by a fixed ramp.

Full state feedback is conventional and well known, and analysis and design of converters on the basis of state feedback was established relatively early [86], [87]. The equivalence between CMC and current feedback control is rarely discussed, and the near-exact equivalence demonstrated here seems to be a new result. State feedback control avoids the duty ratio instabilities and signal-to-noise ratio problems associated with current ripple. A state feedback law can be implemented as a single loop in a process structured like a VMC.

### D. OBSERVER-BASED CONTROL

As in any control system, the state variables can be sensed, or can be replaced or augmented with various observers. A basic example is *one-cycle control*, in which an integrator tracks an inductor voltage to allow the switching controller to force the inductor voltage average to zero [88]. A more complete example is to use inductor voltage integration as an observer for inductor current [20]. An example for an inverter is given in [89]. The methods are related to *model reference adaptive* control [90].

The connection between model reference adaptive controls and observer-based controls links to a larger family of modelbased controls and predictive controls. Low-cost digital processors are fueling application of predictive and adaptive control techniques in dc-dc converters. Model predictive control techniques are gaining attention in high power dc-dc converters switching up to a few hundred kHz, particularly for dc microgrid applications [91], [92].

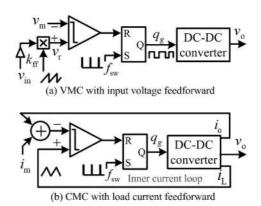

#### E. COMBINED FEEDFORWARD AND FEEDBACK CONTROL

An ideal converter has zero output impedance and infinite bandwidth so that the output voltage remains unaffected by

FIGURE 17. Linear PWM (a) VMC and (b) CMC.

transients in input voltage  $v_{in}$ , load current  $i_0$ , or parameters. Feedforward methods can supplement feedback control to approach ideal operation.

# 1) INPUT VOLTAGE FEEDFORWARD IN VMC

The output voltage will exhibit overshoot or undershoot for transients since bandwidth is limited. Feedforward action can reduce these effects. For example, the output of a buck or boost converter is proportional to  $v_{in}$ . If the input voltage is applied as a feedforward parameter, the converter control can be made insensitive to changes in  $v_{in}$  [93]. A similar approach can correct for the load current  $i_0$  [94]. Fig. 17(a) shows a feedforward process in a VMC with constant  $v_m$ . The feedback loop has been broken, and the ramp slope is  $m_c = k_{\rm ff}v_{\rm in}$  with feedforward gain  $k_{\rm ff}$ . The duty ratio can be obtained as  $d = v_{\rm m}/(m_cT)$ , and the average output voltage in the case of a buck converter becomes

$$\bar{v}_{\rm o} = d\,\bar{v}_{\rm in} = \frac{\bar{v}_{\rm m}\bar{v}_{\rm in}}{m_{\rm c}T} = \frac{\bar{v}_{\rm m}\bar{v}_{\rm in}}{k_{\rm ff}\bar{v}_{\rm in}T} = \frac{\bar{v}_{\rm m}}{k_{\rm ff}T}.$$

(11)

The average output voltage now is independent of the input voltage, and therefore insensitive to supply variation.

#### 2) LOAD CURRENT FEEDFORWARD IN CMC

Fig. 17(b) shows feedforward action in CMC with constant  $v_{\rm m}$ . The outer voltage feedback loop has been broken, and the sensed load current  $i_{\rm o}$  is added to  $v_{\rm m}$  to provide a load-tracking reference current for the inner current feedback loop. Any change in the load current automatically changes the reference current in such a way that the effective duty ratio remains constant. This reduces output voltage sensitivity to load variation. However, the finite slew rate of the inductor will limit the impact, since the inductor current must track any change in the load current.

The capacitor current can also be used for feedforward [84], [95], providing the effect of an output derivative, since the capacitor current reflects time rate of change of output voltage. Thus output capacitor current feedforward is nearly the same as output derivative feedback.

# IV. LARGE- AND SMALL-SIGNAL DYNAMICS OF PWM DC-DC CONVERTERS

Dc-dc converters are large signal nonlinear circuits by virtue of switch action. A general modeling framework can be created with piecewise-linear systems [96]. Given N possible circuit configurations determined by switching, the model becomes

$$\dot{\mathbf{x}} = \sum_{i=1}^{N} \left( \mathbf{A}_i \mathbf{x} + \mathbf{B}_i \mathbf{u} \right) q_i(\mathbf{x}, \mathbf{u}, t)$$

(12)

where  $\mathbf{x}$  is a vector of state variables,  $\mathbf{u}$  is a vector of inputs,  $A_i$  and  $B_i$  are matrices with various parameters, and the sequence of time and state-dependent switching functions  $q_i \in \{0, 1\}$  represents switch action. Formally, this is a hybrid system in which discrete events interact with continuous state variables [97]. Nonlinear elements, such as real inductors, can be brought into this framework by means of component-level piecewise models [98]. One difference between general hybrid systems and power converters is that state variables in power converters (inductor currents and capacitor voltages) are continuous and do not show jumps. The state variables are continuous, but as (12) shows, their derivatives are not. There is a growing literature on piecewise-linear systems and switched linear systems, although only a few authors have linked the work to dc-dc converters [99]. However, piecewiselinear system models are widely used for simulation of power converters [100], [101], [102].

The representation in (12) drives at least three large-signal approaches to dc-dc converter analysis and control:

- 1) Discrete-time formulations and control, based on *z* transforms and related concepts.

- 2) Switching boundary control, in which the Heaviside step function H(x) governs switch action as in

$$q_i(\mathbf{x}, \mathbf{u}, t) = H(f_i(\mathbf{x}, \mathbf{u}, t))$$

(13)

where  $f_i$  are sets of control laws.

Averaging, in which a new set of variables represents smoothed action with switching integrated out.

#### A. LARGE-SIGNAL PIECEWISE MODELING

As an example of direct piecewise models, consider a buck converter in Fig. 2 and its control waveforms in Fig. 3 while operating in continuous conduction mode (CCM). The overall piecewise-linear state-space model of a CCM buck converter can be written as

$$\dot{\mathbf{x}} = \mathbf{A}_i \mathbf{x} + \mathbf{B}_i v_{\text{in}}, \quad i \in \{\text{on, off}\},$$

(14)

where  $\mathbf{x} = [i_{\rm L}, v_{\rm cap}]^T$ ;  $i_{\rm L}$  and  $v_{\rm cap}$  are the inductor current and capacitor voltage, and the matrices are

$$A_{\rm on} = A_{\rm off} = \begin{bmatrix} 0 & \frac{-1}{L} \\ \frac{1}{C} & \frac{-1}{RC} \end{bmatrix}, B_{\rm on} = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}, B_{\rm off} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}.$$

The individual configurations for a given index i in (14), linked to gate signal  $q_g$ , have separate (stable) equilibrium

points. Neither of them alone can achieve the desired stepdown operation and switch action is required. Suitable logic for  $q_g$  implies a switched linear system,

$$\dot{\mathbf{x}} = \left[q_{g}A_{\text{on}} + \left(1 - q_{g}\right)A_{\text{off}}\right]\mathbf{x} + \left[q_{g}B_{\text{on}} + \left(1 - q_{g}\right)B_{\text{off}}\right]v_{\text{in}}.$$

(15)

Large-signal behavior of a dc-dc converter can be analyzed by considering the model in (15) along with a switching control law. Using the model in (14), the large-signal behavior can be characterized using state-plane geometry.

### **B. DISCRETE-TIME DETAILED MODELING**

Piecewise-linear systems lend themselves well to discretetime models, in which the system behavior is tracked at discrete intervals. From (12), at a set of discrete times  $t_k$ , a simplified version becomes the transition function

$$\mathbf{x}_{k+1} = \mathbf{A}_k \mathbf{x}_k + \mathbf{B}_k \mathbf{u}_k \tag{16}$$

where k indicates the particular switch configuration during the time interval and the derivatives are constant in each interval. Even if the behavior is more complicated, it is straightforward to generalize by solving (12) interval by interval and then piecing results together. The final condition of one interval becomes the initial condition for the next one. If time intervals are uniform, the model of (16) (or its generalization) can be written immediately in terms of z transforms. However, the *modified* z transform [103] does not require uniform intervals and applies to the broader problem.

A caveat when using z transforms is that the control is through the actual switch timing, so the time intervals linked to duty ratios are, in turn, linked to control action. This is distinct from a conventional discrete-time system, in which the time intervals are determined externally. Even with this limitation, several authors have applied sampled data and discrete time methods to power converter control successfully [104]-[108]. In [106], relationships among state-space averaging, Laplace-domain analysis, and z-domain analysis are discussed in depth. In [107], an extensive review of sampled data methods up to that time is included. More recent authors have applied these methods to high-performance dc-dc converters. In [109], response times below 5  $\mu$ s are achieved with a sampled data control. In [110], the authors show how to design a discrete-time dc-dc controller that delivers high-performance tracking with uncertain parameters. In [95], it is shown that a converter can respond to a disturbance with an effective bandwidth higher than the switching frequency.

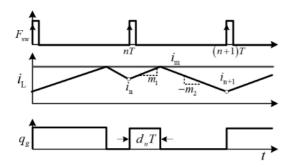

The model in (12) can be considered for a closed-loop system. Such models have been used to predict various nonlinear phenomena in dc-dc converters [111]. A model set up with uniform time intervals T, as in Fig. 18, will track the values  $i_k$  at the moment of switch turn on. The natural behavior of such a model is *envelope tracking* of the minimum current values. A discrete-time model set up to coincide with the moment of switch turn off will instead track the maximum current values.

FIGURE 18. Control waveforms of a dc-dc converter under peak CMC.

#### C. NONLINEAR AVERAGE MODELING

The discontinuous derivatives in (12) limit the applicability of many control methodologies. Many methods for nonlinear control require a system to satisfy a Lipschitz condition, but the piecewise-linear switch-based models for power converters in (12) do not meet this. This negates methods of nonlinear control found in classic work, such as [112]. Averaging is an approach that seeks to identify a time-invariant system that tracks the full piecewise system. The time-invariant model has continuous derivatives, and therefore lends itself to a broad range of control possibilities. Such a model can also be linearized, linking to conventional methods for linear time-invariant systems. Averaging can be applied either top down from the circuit [113], [114] or bottom up from the equations [115]. It has also been developed from an Euler-Lagrange perspective in [116].

From a mathematical point of view, averaging seeks to consider a general time-varying nonlinear system with an identifiable small parameter  $\epsilon$  [117], given by

$$\dot{\mathbf{x}} = \epsilon F(\mathbf{x}, \mathbf{u}, t). \tag{17}$$

This is mapped to a set of new variables  $\mathbf{y}$ , new inputs  $\mathbf{v}$ , and a function G, such that

$$\dot{\mathbf{y}} = \epsilon G(\mathbf{y}, \mathbf{v}), \tag{18}$$

in which G is defined in an averaged sense and  $\mathbf{y}$  tracks the behavior of  $\mathbf{x}$  in a well-defined manner. That is, we seek

$$G(\cdot) = \frac{1}{T} \int_{t-T}^{t} F(s, \cdot) \, ds \tag{19}$$

In a power converter, a typical choice for the small parameter is the switching period T. It is known that variables **y** track variables **x** in the limit of small  $\epsilon$ , provided inputs **v** are chosen to track the average behavior of actual inputs **u**. The agreement is not exact in general, and a procedure can be obtained to create refinements to the model [117]. The details were proved in [118]. Alternative extensions of averaging based on harmonic analysis have also been presented [119].

Variables **y** can be represented as the averages  $\bar{\mathbf{x}}$ , and new system matrices  $\bar{\mathbf{A}}$  and  $\bar{\mathbf{B}}$  are computed as weighted averages of the sum in (12). In state space averaging [113], [115], duty ratios substitute for switching functions and provide the

weights. For the CCM buck converter in (15), the average dynamics can be represented as

$$\begin{split} \dot{\bar{x}} &= A_{\mathrm{av}}\bar{x} + B_{\mathrm{av}}\bar{v}_{\mathrm{in}} \stackrel{\Delta}{=} F_{\mathrm{av}}\left(\bar{x}, \ \bar{v}_{\mathrm{in}}, \ d\right), \text{ where} \\ \bar{x} &= \frac{1}{T} \int_{t-T}^{t} x(s) ds; \quad \bar{v}_{\mathrm{in}} = \frac{1}{T} \int_{t-T}^{t} v_{\mathrm{in}}(s) ds, \\ A_{\mathrm{av}} &= dA_{\mathrm{on}} + (1-d)A_{\mathrm{off}}, \quad B_{\mathrm{av}} = dB_{\mathrm{on}} + (1-d)B_{\mathrm{off}}, \end{split}$$

$$(20)$$

and d is the duty ratio. The switching nonlinearity in (15) has been transformed into a smooth model in (20).

In general, models obtained with averaging are nonlinear, although without switching discontinuities. Methods of nonlinear control, including feedback linearization [120], synergetic control [121], sliding mode control [122], and many others [112] can be applied. In the case of sliding mode control, it is possible to use switching directly to form a sliding mode. Sliding mode controls can be designed directly from (12) [123]. Since averaged models do not include switching behavior — it is assumed to be fast — the controls become *model limited* and are valid for design only up to some fraction of  $f_{sw}$ . Fast slew rates associated with ripple are not in the model, so an averaging-based controller will have limits on fast dynamic performance.

#### D. MODEL LIMITS ON CONTROL

What about this issue of model-limited control? What ratio of switching frequency to control bandwidth is necessary for a workable result? This issue has been debated extensively in many forums. The details of averaging in [117] for dc-dc converters do not really limit the frequency, although too extreme a control bandwidth will interact with switching ripple and undermine the performance. It is self-evident that the phase of a sufficiently fast disturbance can interact with the switching function phase, leading to aliasing effects. Consider a unity-gain crossover frequency  $f_c$ . Sampling theory considerations [16] suggest that the ratio  $f_{sw}/f_c$  should be greater than  $\pi$  (not the Nyquist ratio of 2 since these systems do not involve ideal sampling). Theory of distortion for naturallysampled PWM [16] suggests that aliasing will be down more than 100 dB for ratios above about six. Most designers cite a rule of thumb for a ratio of about 10. It is important to remember that this ratio is for convenience in establishing a smooth averaged model and associated controls and does not represent a fundamental performance limit on the converter itself.

# E. LINEARIZATION AND SMALL-SIGNAL MODELING

# 1) SMALL-SIGNAL MODELING FROM AVERAGING

Consider small perturbations around a target steady-state operating point, written in terms of the averages as  $\bar{x} = \tilde{x} + X_{ss}$ ,  $d = \tilde{d} + D$ ,  $\bar{v}_{in} = \tilde{v}_{in} + V_{in}$ , where D is the steady-state duty

| Parameters         | $\omega_o$                                                                | Q                                                                                                            | $\omega_{ m z}$        | $\omega_{ m rhp}$                                                      | $\omega_{\mathrm{z}1}$     | $\omega_{\mathrm{z}2}$ | $V_{\rm e}$                                                        |

|--------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------|----------------------------|------------------------|--------------------------------------------------------------------|

| Ideal<br>Buck      | $\frac{1}{\sqrt{LC}}$                                                     | $\frac{R}{Z_{\rm C}}$                                                                                        | N.A.                   | N.A.                                                                   | $\frac{1}{RC}$             | 0                      | $V_{ m in}$                                                        |

| Ideal<br>Boost     | $\frac{D'}{\sqrt{LC}}$                                                    | $rac{RD'}{Z_{ m C}}$                                                                                        | N.A.                   | $\frac{R(D')^2}{L}$                                                    | $\frac{1}{RC}$             | 0                      | $\frac{V_{\rm o}}{D'}$                                             |

| Practical<br>Buck  | $\sqrt{\frac{(R+r_{\rm e})}{(R+r_{\rm C})}} \cdot \frac{1}{\sqrt{LC}}$    | $\alpha \left[ \frac{(r_{\rm C} + r_{\rm e})}{Z_{\rm c}} + \frac{Z_{\rm c}}{R} \right]^{-1}$                 | $\frac{1}{r_{\rm C}C}$ | N.A.                                                                   | $\frac{1}{(R+r_{\rm C})C}$ | $\frac{r_{\rm e}}{L}$  | $\frac{V_{\rm in}}{\alpha}$                                        |

| Practical<br>Boost | $\sqrt{\frac{(R+r'_{\rm e})}{(R+r_{\rm C})}} \times \frac{D'}{\sqrt{LC}}$ | $\alpha \left[ \frac{\left( r_{\rm C} + r_{\rm e}' \right)}{Z_{\rm c}'} + \frac{Z_{\rm c}'}{R} \right]^{-1}$ | $\frac{1}{r_{\rm C}C}$ | $\frac{\left[\left(D'\right)^2 \left(R - r'_{\rm e}\right)\right]}{L}$ | $\frac{1}{(R+r_{\rm C})C}$ | $\frac{r'_{\rm e}}{L}$ | $\frac{V_{\rm o} \left(R - r_{\rm e}'\right)}{D'(R + r_{\rm e}')}$ |

**TABLE 4.** Parameters for Buck and Boost Converters  $[D' = (1 - D), r'_e = r_e/D', \alpha = (R + r_e)/R$  (Buck),  $\alpha = (R + r'_e)/R$  (Boost),  $Z_c = \sqrt{L/C}, Z'_c = Z_c/D'$ ]

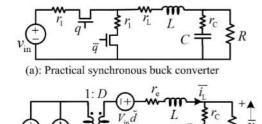

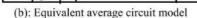

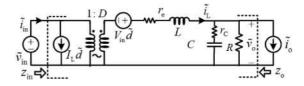

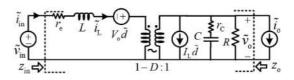

**FIGURE 19.** A synchronous buck converter and its average equivalent circuit. The equivalent resistance is  $r_e = r_1 + r_L$  and *D* is the steady-state duty ratio.

FIGURE 20. Small signal equivalent circuit of the buck converter in Fig. 19 (a).

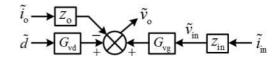

FIGURE 21. Small-signal block diagram of a PWM dc-dc converter.

ratio and  $V_{in}$  is the dc input voltage. A Taylor series representation of the averaged model in (20) yields the form

$$\dot{\tilde{x}} = \bar{\mathbf{A}}\tilde{x} + \bar{\mathbf{B}}\tilde{v}_{\text{in}} + \left.\frac{\partial F_{\text{av}}}{\partial d}\right|_{\text{ss}}\tilde{d} + \text{higher order terms.}$$

(21)

This requires well-defined derivatives, which is why it is useful with the averaged model but not the piecewise model. In steady state  $\dot{x} = 0$ . For a simplified buck converter, this can be solved to obtain

$$V_{\rm o} = DV_{\rm in}, \ I_{\rm L} = V_{\rm o}/R = I_{\rm o}.$$

(22)

Eq. (21) without higher order terms is a linear model, valid near the steady-state operating point. Its Laplace transform is

$$\tilde{\mathbf{x}}(s) = \left(sI - \bar{A}\right)^{-1} \bar{B} \left[ d\tilde{(s)}, \ \tilde{v}_{\rm in}(s) \right]^T, \tag{23}$$

where  $\bar{B}$  has been augmented to include derivatives  $\left[\frac{\partial F_{av}}{\partial \bar{d}}|_{ss}, \frac{\partial F_{av}}{\partial \bar{v}_{in}}|_{ss}\right]$ . Of particular interest are the control-to-output transfer

Of particular interest are the control-to-output transfer function  $G_{vd} = \tilde{v}_o/\tilde{d}$ , the input-to-output transfer function (audio susceptibility)  $G_{vg} = \tilde{v}_o/\tilde{v}_{in}$ , the input impedance  $z_{in} = \tilde{v}_{in}/\tilde{i}_{in}$ , and the output impedance  $z_o = \tilde{v}_o/\tilde{i}_o$ . For an ideal buck converter in CCM, some of these are

$$G_{\rm vd} = \frac{V_{\rm in}}{1 + \frac{s}{Q\omega_o} + \frac{s^2}{\omega_o^2}}, \ G_{\rm vg} = \frac{D}{1 + \frac{s}{Q\omega_o} + \frac{s^2}{\omega_o^2}}.$$

(24)

Here the radian frequency is  $\omega_o = 1/\sqrt{LC}$ , the characteristic impedance is  $Z_c = \sqrt{L/C}$ , and the quality factor is  $Q = R/Z_c$ . State space averaging and linearization, or equivalently circuit averaging, remain valid as parasitics and linear elements are added to the circuits, as in Fig. 19.

# F. DYNAMICS OF OPEN-LOOP PWM BUCK CONVERTERS UNDER CCM

Fig. 20 shows the small signal equivalent circuit of a CCM buck converter in Fig. 19, with the addition of "probing" current sources at the input and output to test the respective impedances. This gives rise to more complete transfer function expressions. The parameter values for buck and boost converters are listed in Table 4, but notice that many do not apply in the ideal case. Transfer functions for the converters are listed in Table 5. The output impedance  $z_0$  at the probing point in Fig. 20 requires careful attention to voltage and current polarities.

The ESR value  $r_C$  plays an important role in a practical converter. At low frequency, the output impedance  $z_0$  is the load in parallel with the equivalent resistance  $r_e$  in Fig. 19. At high frequency, the output impedance is the load in parallel with ESR. Fig. 21 shows the small-signal block diagram of a dc-dc converter. The poles in  $G_{vd}$  will be complex conjugate

| Transfer<br>functions | $G_{ m vd}\left(s ight)$                                                                                                                                                            | $G_{\mathrm{vg}}\left(s ight)$                                                                                                  | $z_{\mathrm{in}}\left(s ight)$                                                                                                                            | $z_{ m o}\left(s ight)$                                                                                                                                                                            |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ideal<br>Buck         | $\frac{V_{\rm in}}{\left(1 + \frac{sL}{R} + s^2 L C\right)}$                                                                                                                        | $\frac{D}{\left(1 + \frac{sL}{R} + s^2 LC\right)}$                                                                              | $\frac{R\left(1+\frac{sL}{R}+s^2LC\right)}{D^2(1+sRC)}$                                                                                                   | $\frac{sL}{\left(1 + \frac{sL}{R} + s^2LC\right)}$                                                                                                                                                 |

| Ideal<br>Boost        | $\frac{V_{\rm in} \left(1 - \frac{sL}{RD'^2}\right)}{\left(D'^2 + \frac{sL}{R} + s^2 LC\right)}$                                                                                    | $\frac{D'}{\left(D'^2 + \frac{sL}{R} + s^2 L C\right)}$                                                                         | $\frac{R\left(D'^2 + \frac{sL}{R} + s^2LC\right)}{(1 + sRC)}$                                                                                             | $\frac{sL}{\left(D'^2 + \frac{sL}{R} + s^2LC\right)}$                                                                                                                                              |

| Practical<br>Buck     | $\frac{V_{\rm e}\left(1+\frac{s}{\omega_{\rm z}}\right)}{\left(1+\frac{s}{Q\omega_{\rm o}}+\frac{s^2}{\omega_{\rm o}^2}\right)}$                                                    | $\frac{D\left(1+\frac{s}{\omega_z}\right)}{\alpha\left(1+\frac{s}{Q\omega_o}+\frac{s^2}{\omega_o^2}\right)}$                    | $\frac{\alpha R}{D^2} \frac{\left(1 + \frac{s}{Q\omega_{\rm o}} + \frac{s^2}{\omega_{\rm o}^2}\right)}{\left(1 + \frac{s}{\omega_{\rm z1}}\right)}$       | $\frac{r_{\rm e}}{\alpha} \frac{\left(1 + \frac{s}{\omega_z}\right) \left(1 + \frac{s}{\omega_{z2}}\right)}{\left(1 + \frac{s}{Q\omega_{\rm o}} + \frac{s^2}{\omega_{\rm o}^2}\right)}$            |

| Practical<br>Boost    | $V_{\rm e} \frac{\left(1 - \frac{s}{\omega_{\rm rhp}}\right) \left(1 + \frac{s}{\omega_{\rm z}}\right)}{\left(1 + \frac{s}{Q\omega_{\rm o}} + \frac{s^2}{\omega_{\rm o}^2}\right)}$ | $\frac{1}{\alpha D'} \frac{\left(1 + \frac{s}{\omega_z}\right)}{\left(1 + \frac{s}{Q\omega_o} + \frac{s^2}{\omega_o^2}\right)}$ | $\frac{\alpha R \left(D'\right)^2 \left(1 + \frac{s}{Q\omega_{\rm o}} + \frac{s^2}{\omega_{\rm o}^2}\right)}{\left(1 + \frac{s}{\omega_{\rm z1}}\right)}$ | $\frac{r_{\rm e}'}{\alpha} \frac{\left(1 + \frac{s}{\omega_{\rm z}}\right) \left(1 + \frac{s}{\omega_{\rm z2}}\right)}{\left(1 + \frac{s}{Q\omega_{\rm o}} + \frac{s^2}{\omega_{\rm o}^2}\right)}$ |

TABLE 5. Transfer Functions for Buck and Boost Converters

given a resistive load R if

$$Q > 1 \implies R > \left[\frac{(r_{\rm e} + r_{\rm c})R}{Z_{\rm c}} + Z_{\rm c}\right] - r_{\rm e}.$$

(25)

Ideally, the condition in (25) becomes  $R > Z_c$ , which will lead to underdamped behavior with low phase margin as the load power decreases. The dc gain of  $G_{vd}$  depends on input voltage, reflecting the fact that the open-loop output is proportional to input. A higher input voltage tends to increase the crossover frequency and control bandwidth, but at the cost of reduced phase margin. The ESR zero  $\omega_z$  might be near the double-frequency pole  $\omega_o$  if ESR is high, which would provide phase boost and may lead to overdamped behavior. However, high ESR imposes larger output voltage ripple.

At low frequency,  $G_{vg}$  in Table 5 shows that the duty ratio directly relates the input and output voltages. Any input disturbance impacts the output in proportion to *D*. It will be important to compensate for the input in a closed-loop control.

For practical converters, it is obvious enough that low output impedance is advantageous, but the values of  $r_e$  and ESR impose limiting cases. The form of  $z_0$  in Table 5 confirms that small  $r_e$  and ESR are beneficial, but also suggests that there could be a condition in which terms in *s* cancel and  $z_0$  becomes frequency independent. It is well known that frequency-independent output impedance is optimal, in some sense, for power converter transient response [124], [125]. Even though the converter will not regulate perfectly through a transient, if the output impedance is frequency independent and resistive, the converter will show simple droop response to transients at any speed.

#### G. DYNAMICS OF BOOST PWM CONVERTERS UNDER CCM

Fig. 22 shows the small-signal equivalent circuit of a CCM boost converter, which can be used to derive the control-tooutput transfer function  $G_{vd}$ , audio susceptibility  $G_{vg}$ , input impedance  $z_{in}$ , and output impedance  $z_0$ . The poles in  $G_{vd}$  in

FIGURE 22. Small signal equivalent circuit of a synchronous boost converter.

Table 5 will be complex conjugate for a resistive load if

$$Q > 1 \quad \Rightarrow \quad R > \left[\frac{\left(r'_{e} + r_{c}\right)R\left(1 - D\right)}{Z_{c}} + \frac{Z_{c}}{\left(1 - D\right)}\right] - r'_{e}.$$

(26)

This requires  $R > Z_c/(1 - D)$ , and leads to underdamped behavior and decreasing phase margin as the load power decreases, as in the buck case. The biggest difference is the right-half-plane (RHP) zero in  $G_{vd}$ . This reflects the non-minimum phase physics of the converter, in which energy can be delivered from input to output only with a two-step process in which energy is first stored in the inductor (as the output decays) and then transferred to the capacitor.

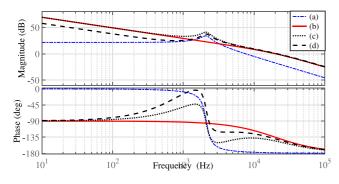

The RHP zero frequency,  $f_{\rm rhp}$ , effectively limits the achievable (model-limited) closed-loop small-signal bandwidth. The value is

$$f_{\rm rhp} = \frac{\omega_{\rm rhp}}{2\pi} = \frac{(1-D)^2 R}{2\pi L}.$$

(27)

This shows that  $f_{\rm rhp}$  varies with the load current and the duty ratio, with the slowest performance corresponding to the highest output power and highest duty ratio. The effective bandwidth can be raised by reducing *L*, but this trades off against higher ripple. Lighter loads reduce damping and phase margin, whereas heavier loads reduce achievable bandwidth as the RHP zero decreases. The combination makes it difficult for small-signal controls to cover a wide operating range. Active PFC converters are an application example, mitigated because the control dynamics are linked to mains frequency and switching frequency is much higher.

Converter $K_{\rm d}$  $\omega_{\rm d}$ MBuck $2V_ok_1/D$  $\frac{1}{k_1RC}$  $\frac{1}{2}\left(1+\sqrt{1+4D^2/K}\right)$ Boost $2V_ok_2/D$  $\frac{1}{k_2RC}$  $2/\left(1+\sqrt{1+4K/D^2}\right)$

**TABLE 6.** Parameters of (28); K = 2L/(RT),  $k_1 = (1 - M)/(2 - M)$  and  $k_2 = (M - 1)/(2M - 1)$

The audio susceptibility of a boost converter has D' = 1 - D in the denominator. Any disturbance at the open-loop converter input impacts the output immediately. As with a buck converter,  $z_0$  in Table 5 implies that low  $r_e$  and ESR will be beneficial. It is also possible to attempt cancellation of the *s*-dependent terms in  $z_0$ , potentially yielding a frequency-independent resistive output impedance. As in the buck case, this has advantages in transient response, since the output will show a simple resistive droop to a load transient.

#### H. DYNAMICS OF PWM DC-DC CONVERTERS IN DCM

During each switching cycle under DCM, the inductor current starts from zero and returns to zero, as shown in Fig. 9. The dual condition in boost-buck and other converters with capacitive transfer sources starts and returns the capacitor voltage to zero during a switching period. In DCM, an additional *duty ratio constraint* is needed to set up dynamic analysis. An extensive analysis can be found in [48]. Simplified control-tooutput transfer functions of buck and boost converters under DCM can be written as

$$G_{\rm vd} = \left. \frac{\tilde{v}_{\rm o}}{\tilde{d}} \right|_{\tilde{v}_{\rm in}=0} = K_{\rm d} / \left( 1 + \frac{s}{\omega_{\rm d}} \right), \tag{28}$$

where expressions for  $K_d$  and  $\omega_d$  are given in Table 6.

The small-signal model in (28) does not include the (fast) dynamics of the inductor current  $i_L$ . While accurately capturing low frequency behavior, this model is not sufficient for predicting high frequency dynamics. State-space averaging as in [126], and circuit averaging as in [127], can be used to improve accuracy. It is reported in [127] that the RHP zero in a non-minimum phase boost converter is not completely removed from the control-to-output transfer function  $G_{\rm vd}$  under DCM. However, its effect is reduced substantially compared to CCM as the RHP zero is pushed to the right in the s plane with decreasing load current. A discrete-time model can be used to improve accuracy and to predict bifurcation phenomena in a DCM boost converter [128]. Although high frequency dynamics are important, for a small-signal-based controller design, the simplified model in (28) suffices up to  $f_{\rm sw}/10.$

### **V. SMALL-SIGNAL BASED TUNING**

Frequency domain design tools are helpful for small-signalbased PWM control and are used in the majority of commercial power supply products. Primary design objectives are to

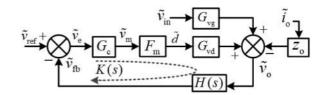

FIGURE 23. Block diagram of a closed-loop dc-dc converter, VMC.

meet a desired control bandwidth with acceptable phase margin. The unity-gain crossover frequency  $f_c$  is often used as the control bandwidth, and the concepts are used interchangeably in the following design case studies.

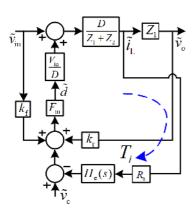

# A. DESIGN OF PWM VMC

Fig. 23 shows the block diagram of a closed-loop dc-dc converter set up for PWM VMC. The modulator is assigned a gain  $F_{\rm m} = f_{\rm sw}/m_{\rm c}$  where  $m_{\rm c}$  is the slope of the ramp signal. The feedback block H(s) comprises a voltage divider and a low pass filter. The objective is to design a suitable compensator  $G_{\rm c}(s)$  for shaping the closed loop gain K(s) at a target operating point to meet transient and steady-state specifications. High loop gain at low frequency ensures that the output voltage will be near the reference value. The closed-loop transfer function in Fig. 23 is

$$\frac{\tilde{v}_{\rm o}}{\tilde{v}_{\rm ref}} = \frac{1}{H(s)} \times \frac{K(s)}{1 + K(s)} \approx \frac{1}{H(s)}$$

(29)

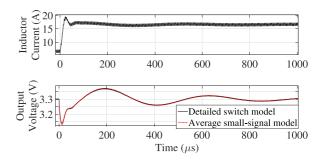

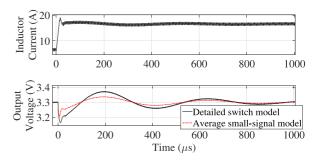

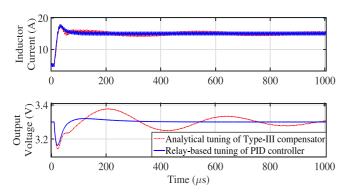

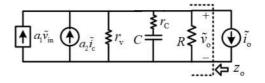

where  $K(s) = G_c(s)F_mG_{vd}(s)H(s)$ . With high gain, this is nearly independent of parameter variations in the open-loop plant  $G_{vd}$ . Since the gain is not unlimited, analysis must establish (1) robustness again parameter variations and unmodeled dynamics, (2) acceptable stability margins, (3) adequate transient performance, and (4) useful design guidelines.